JP2004096636A - アナログ−デジタル変換回路 - Google Patents

アナログ−デジタル変換回路 Download PDFInfo

- Publication number

- JP2004096636A JP2004096636A JP2002258058A JP2002258058A JP2004096636A JP 2004096636 A JP2004096636 A JP 2004096636A JP 2002258058 A JP2002258058 A JP 2002258058A JP 2002258058 A JP2002258058 A JP 2002258058A JP 2004096636 A JP2004096636 A JP 2004096636A

- Authority

- JP

- Japan

- Prior art keywords

- analog

- signal

- converter

- digital

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 238000006243 chemical reaction Methods 0.000 title claims abstract description 109

- 230000003321 amplification Effects 0.000 claims description 32

- 238000003199 nucleic acid amplification method Methods 0.000 claims description 32

- 102100040856 Dual specificity protein kinase CLK3 Human genes 0.000 abstract description 17

- 101000749304 Homo sapiens Dual specificity protein kinase CLK3 Proteins 0.000 abstract description 17

- 102100040862 Dual specificity protein kinase CLK1 Human genes 0.000 abstract description 15

- 101000749294 Homo sapiens Dual specificity protein kinase CLK1 Proteins 0.000 abstract description 15

- 239000003990 capacitor Substances 0.000 description 25

- 238000005070 sampling Methods 0.000 description 24

- 238000010586 diagram Methods 0.000 description 16

- 230000010355 oscillation Effects 0.000 description 4

- 102100040844 Dual specificity protein kinase CLK2 Human genes 0.000 description 2

- 101000749291 Homo sapiens Dual specificity protein kinase CLK2 Proteins 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 238000004891 communication Methods 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229920006395 saturated elastomer Polymers 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/14—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit

- H03M1/16—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps

- H03M1/164—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps the steps being performed sequentially in series-connected stages

- H03M1/167—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps the steps being performed sequentially in series-connected stages all stages comprising simultaneous converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/14—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit

- H03M1/16—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps

- H03M1/162—Conversion in steps with each step involving the same or a different conversion means and delivering more than one bit with scale factor modification, i.e. by changing the amplification between the steps the steps being performed sequentially in a single stage, i.e. recirculation type

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Analogue/Digital Conversion (AREA)

Abstract

【解決手段】1段目の回路ST1内の演算増幅器1、サブA/Dコンバータ7、D/Aコンバータ8および演算増幅器2は、クロック信号CLK1に応答して動作する。2段目の回路ST2内の演算増幅器3、サブA/Dコンバータ9、D/Aコンバータ10および演算増幅器4は、クロック信号CLK1の3倍の周波数を有するクロック信号CLK3に応答して動作する。1段目の回路ST1内の演算増幅器2から出力されるアナログ信号はスイッチSW1を介して2段目の回路ST2内の入力ノードNIに与えられる。2段目の回路ST2内の演算増幅器4から出力されるアナログ信号はスイッチSW2を介して2段目の回路ST2内の入力ノードNIに与えられる。

【選択図】 図1

Description

【発明の属する技術分野】

本発明は、多段パイプライン(ステップフラッシュ)構成を有するアナログ−デジタル変換回路に関する。

【0002】

【従来の技術】

近年、ビデオ信号のデジタル処理技術の進歩に伴い、ビデオ信号処理用のアナログ−デジタル変換回路(A/Dコンバータ)の需要が大きくなっている。ビデオ信号処理用のアナログ−デジタル変換回路には高速変換動作が要求されるため、従来、2ステップフラッシュ(2ステップパラレル)方式が広く用いられていた。

【0003】

しかし、変換ビット数の増大に伴い、2ステップフラッシュ方式では十分な変換精度が得られなくなってきたため、多段パイプライン(ステップフラッシュ)構成を有するアナログ−デジタル変換回路が開発された(例えば、特許文献1参照)。

【0004】

図12は従来のアナログ−デジタル変換回路を示すブロック図である。図12のアナログ−デジタル変換回路101は、10ビット4段パイプライン構成を有する。

【0005】

図12において、アナログ−デジタル変換回路101は、サンプルホールド回路102、1段目〜4段目の回路103〜106、複数のラッチ回路107および出力回路108から構成されている。

【0006】

1段目(初段)の回路103は、サブA/Dコンバータ109、D/Aコンバータ110、演算増幅器111a、減算回路112および演算増幅器113を備える。減算回路112および演算増幅器113が差分増幅器114を構成する。2段目および3段目の回路104,105は、サブA/Dコンバータ109、D/Aコンバータ110、演算増幅器111、減算回路112および演算増幅器113を備える。1段目〜3段目の回路103〜105において、減算回路112および演算増幅器113が差分増幅器114を構成する。

【0007】

ただし、後述するように、1段目の回路103内の演算増幅器111aは、利得1を有し、サンプルホールド回路として働く。1段目の回路103内の演算増幅器113および2段目および3段目の回路104,105内の演算増幅器111,113の利得は2である。4段目(最終段)の回路106は、サブA/Dコンバータ109のみを備える。

【0008】

1段目の回路103は4ビット構成、2〜4段目の回路104〜106はそれぞれ2ビット構成である。1〜3段目の回路103〜105において、サブA/Dコンバータ109およびD/Aコンバータ110のビット数(ビット構成)は同じに設定されている。

【0009】

次に、図12のアナログ−デジタル変換回路101の動作を説明する。サンプルホールド回路102は、アナログ入力信号Vinをサンプリングして一定時間保持する。サンプルホールド回路102から出力されたアナログ入力信号Vinは、1段目の回路103へ転送される。

【0010】

1段目の回路103において、サブA/Dコンバータ109は、アナログ入力信号Vinに対してA/D変換を行う。サブA/Dコンバータ109のA/D変換結果である上位4ビットのデジタル出力(29 ,28 ,27 ,26 )は、D/Aコンバータ110へ転送されるとともに、4つのラッチ回路7を介して出力回路108へ転送される。D/Aコンバータ110は、サブA/Dコンバータ109のA/D変換結果である上位4ビットのデジタル出力をアナログ信号に変換する。

【0011】

一方、演算増幅器111aは、アナログ入力信号Vinをサンプリングして一定時間保持する。減算回路112は、演算増幅器111aから出力されたアナログ入力信号VinとD/Aコンバータ110のD/A変換結果とを減算する。演算増幅器113は、減算回路112の出力を増幅する。演算増幅器113の出力は、2段目の回路104へ転送される。

【0012】

2段目の回路104においては、サブA/Dコンバータ109が、1段目の回路103の演算増幅器113の出力に対してA/D変換を行う。サブA/Dコンバータ109のA/D変換結果は、D/Aコンバータ110へ転送されるとともに、3つのラッチ回路7を介して出力回路108へ転送される。これにより、2段目の回路104から中上位2ビットのデジタル出力(25 ,24 )が得られる。

【0013】

一方、演算増幅器111は、1段目の回路103の演算増幅器113の出力を増幅する。減算回路112は、演算増幅器111の出力とD/Aコンバータ110のD/A変換結果とを減算する。演算増幅器113は、減算回路112の出力を増幅する。演算増幅器113の出力は、3段目の回路105へ転送される。

【0014】

3段目の回路105においては、2段目の回路103の演算増幅器113の出力に対して2段目の回路104と同様の動作が行われる。それにより、3段目の回路105から中下位2ビットのデジタル出力(23 ,22 )が得られる。

【0015】

4段目の回路106においては、3段目の回路105の演算増幅器113の出力に対してサブA/Dコンバータ109がA/D変換を行い、下位2ビットのデジタル出力(21 ,20 )が得られる。

【0016】

1段目〜4段目の回路103〜106のデジタル出力は、各ラッチ回路107を経て同時に出力回路108に到達する。すなわち、各ラッチ回路107は各回路103〜106のデジタル出力の同期をとるために設けられている。

【0017】

出力回路108は、アナログ入力信号Vinに対応する10ビットのデジタル出力Dout を必要な場合はデジタル補正処理後パラレル出力する。

【0018】

【特許文献1】

特開平11−88172号公報

【0019】

【発明が解決しようとする課題】

このように多段パイプライン構成を有するアナログ−デジタル変換回路では、パイプライン処理および各段での増幅機能により、高速なスループット(変換周波数)および高精度(高分解能)を実現できる。そのため、数MHz〜100MHzの変換周波数で動作する高精度かつ高速の8〜12ビット構成のアナログ−デジタル変換回路が、デジタルビデオ信号処理、デジタル通信処理等の用途に広く採用されている。

【0020】

しかしながら、上記の多段パイプライン構成を有するアナログ−デジタル変換回路においては、同様の構成を有する回路が複数段に配列されるため、面積効率が高くない。また、システム構成上、回路の段数を増加または削減することによりビット分解能を容易に変更することができる。しかしながら、アナログ−デジタル変換回路を実際のLSI(大規模集積回路)に搭載した場合には、回路の段数を増加または削減することは不可能である。また、10ビットのアナログ−デジタル変換回路を8ビットのアナログ−デジタル変換回路として使用することは可能であるが、これは単にオーバースペック(過剰仕様)となるだけであり、面積効率の問題を解決することにはならない。

【0021】

本発明の目的は、省面積化が図られるとともにビット分解能の変更が可能なアナログ−デジタル変換回路を提供することである。

【0022】

【課題を解決するための手段および発明の効果】

(1)第1の発明

第1の発明に係るアナログ−デジタル変換回路は、第1および第2のノードを有する第1の回路と、入力されたアナログ信号および第2のノードのアナログ信号のいずれか一方をを選択的に第1のノードに与える切替手段と、切替手段を制御する制御手段とを備え、第1の回路は、第1のノードからのアナログ信号をデジタル信号に変換する第1のアナログ−デジタル変換器と、第1のアナログ−デジタル変換器から出力されたデジタル信号をアナログ信号に変換する第1のデジタル−アナログ変換器と、第1のノードからのアナログ信号と第1のデジタル−アナログ変換器から出力されたアナログ信号との差分を増幅して第2のノードに出力する第1の差分増幅器とを含み、制御手段は、入力されたアナログ信号が第1のノードに与えられた後、第1のアナログ−デジタル変換器による変換動作、第1のデジタル−アナログ変換器による変換動作および第1の差分増幅器による増幅動作が所定サイクル数行われるように切替手段を制御するものである。

【0023】

本発明に係るアナログ−デジタル変換回路においては、入力されたアナログ信号が第1のノードに与えられた後、第1の回路において、第1のアナログ−デジタル変換器による変換動作、第1のデジタル−アナログ変換器による変換動作および第1の差分増幅器による増幅動作が所定サイクル数行われる。それにより、各サイクルごとに第1の回路内の第1のアナログ−デジタル変換器からデジタル信号が順次出力される。

【0024】

このようにして、第1の回路により多段パイプライン構成が実現される。したがって、省面積化が図られる。

【0025】

また、切替手段の制御により第1の回路で行われるサイクル数を変更することにより、ビット分解能を容易に変更することができる。したがって、同一のハードウエア構成で異なるビット分解能を有するアナログ−デジタル変換回路が容易に実現される。

【0026】

(2)第2の発明

第2の発明に係るアナログ−デジタル変換回路は、第1の発明に係るアナログ−デジタル変換回路の構成において、第1の回路は、第1のノードのアナログ信号を増幅して第1の差分増幅器に与える第1の演算増幅器をさらに含むものである。

【0027】

この場合、第1の回路内に第1の演算増幅器および第1の差分増幅器が設けられているので、1段当たりの増幅器のループ定数を低減することができ、かつ1段当たりの増幅器の負荷容量が低減する。それにより、各増幅器の限界動作周波数が高くなる。その結果、各増幅器の性能を向上させることなく、高い変換動作を保ちつつ、変換速度を向上させることが可能となる。

【0028】

また、第1の回路の各サイクルにおいて、第1の演算増幅器による増幅動作および第1のアナログ−デジタル変換器による変換動作と、第1の差分増幅器による増幅動作および第1のデジタル−アナログ変換器による変換動作とを並行して行うことが可能となる。それにより、各サイクルにおける第1の演算増幅器による増幅動作、第1のアナログ−デジタル変換器による変換動作、第1のデジタル−アナログ変換器による変換動作および第1の差分増幅器による増幅動作のタイミングが緩和される。

【0029】

(3)第3の発明

第3の発明に係るアナログ−デジタル変換回路は、第1または第2の発明に係るアナログ−デジタル変換回路の構成において、切替手段を介して第1の回路の前段に少なくとも1段に設けられた第2の回路をさらに備え、第2の回路は、入力されたアナログ信号をデジタル信号に変換する第2のアナログ−デジタル変換器と、第2のアナログ−デジタル変換器から出力されたデジタル信号をアナログ信号に変換する第2のデジタル−アナログ変換器と、入力されたアナログ信号と第2のデジタル−アナログ変換器から出力されたアナログ信号との差分を増幅して切替手段を介して第1の回路に出力する第2の差分増幅器とを含んだものである。

【0030】

この場合、アナログ信号が第2の回路に入力され、第2のアナログ−デジタル変換器による変換動作、第2のデジタル−アナログ変換器による変換動作および第2の差分増幅器による増幅動作が行われる。第2の差分増幅器から出力されるアナログ信号が切替手段を介して第1の回路に入力され、第1の回路において、第1のアナログ−デジタル変換器による変換動作、第1のデジタル−アナログ変換器による変換動作および第1の差分増幅器による増幅動作が所定サイクル数行われる。それにより、第2の回路内の第2のアナログ−デジタル変換器からデジタル信号が出力され、各サイクルごとに第1の回路内の第1のアナログ−デジタル変換器からデジタル信号が順次出力される。

【0031】

このようにして、第2の回路および第1の回路により多段パイプライン構成が実現される。

【0032】

(4)第4の発明

第4の発明に係るアナログ−デジタル変換回路は、第3の発明に係るアナログ−デジタル変換回路の構成において、第2の回路は、入力されたアナログ信号を増幅して第2の差分増幅器に与える第2の演算増幅器をさらに含むものである。

【0033】

この場合、第2の回路内に第2の演算増幅器および第2の差分増幅器が設けられているので、1段当たりの増幅器のループ定数を低減することができ、かつ1段当たりの増幅器の負荷容量が低減する。それにより、各増幅器の限界動作周波数が高くなる。その結果、各増幅器の性能を向上させることなく、高い変換動作を保ちつつ、変換速度を向上させることが可能となる。

【0034】

また、第2の回路において、第2の演算増幅器による増幅動作および第2のアナログ−デジタル変換器による変換動作と、第2の差分増幅器による増幅動作および第2のデジタル−アナログ変換器による変換動作とを並行して行うことが可能となる。それにより、第2の回路において、第2の演算増幅器による増幅動作、第2のアナログ−デジタル変換器による変換動作、第2のデジタル−アナログ変換器による変換動作および第2の差分増幅器による増幅動作のタイミングが緩和される。

【0035】

(5)第5の発明

第5の発明に係るアナログ−デジタル変換回路は、第1〜第4のいずれかの発明に係るアナログ−デジタル変換回路の構成において、制御手段は、クロック信号および制御信号を発生する信号発生器を含み、第1の回路の第1のアナログ−デジタル変換器、第1のデジタル−アナログ変換器および第1の差分増幅器は、信号発生器により発生されたクロック信号に応答して動作し、切替手段は、信号発生器により発生された制御信号に応答して、入力されたアナログ信号を第1のノードに与える状態と、第2のノードのアナログ信号を第1のノードに与える状態とを切り替えるものである。

【0036】

この場合、クロック信号に応答して第1の回路の第1のアナログ−デジタル変換器、第1のデジタル−アナログ変換器および第1の差分増幅器の動作が行われ、制御信号に応答して、切替手段が入力されたアナログ信号を第1のノードに与える状態と第2のノードのアナログ信号を第1のノードに与える状態とに切り替えられる。それにより、第1の回路において、第1のアナログ−デジタル変換器による変換動作、第1のデジタル−アナログ変換器による変換動作および第1の差分増幅器による増幅動作が所定サイクル数行われ、多段パイプライン構成が実現される。

【0037】

(6)第6の発明

第6の発明に係るアナログ−デジタル変換回路は、第5の発明に係るアナログ−デジタル変換回路の構成において、制御手段は、信号発生器により発生されるクロック信号の周波数を変更する変更手段をさらに含むものである。

【0038】

この場合、変更手段によりクロック信号の周波数を変更することにより、第1の回路で行われるサイクル数を容易に変更することができる。それにより、ビット分解能を容易に変更することができる。

【0039】

(7)第7の発明

第7の発明に係るアナログ−デジタル変換回路は、第6の発明に係るアナログ−デジタル変換回路の構成において、信号発生器は、分周器を有する位相同期ループを含み、変更手段は、位相同期ループの分周器の分周比を設定する分周比設定手段を含むものである。

【0040】

この場合、分周比設定手段により位相同期ループの分周器の分周比を設定することにより、クロック信号の周波数を容易に変更し、ビット分解能を変更することができる。

【0041】

【発明の実施の形態】

図1は本発明の一実施の形態に係るアナログ−デジタル変換回路の構成を示すブロック図である。

【0042】

図1のアナログ−デジタル変換回路100は、1段目の回路ST1、2段目の回路ST2、スイッチSW1,SW2および信号発生器30を備える。

【0043】

1段目の回路ST1は、演算増幅器1、サブA/Dコンバータ7、D/Aコンバータ8、減算回路5および演算増幅器2を備える。減算回路5および演算増幅器2が差分増幅器2aを構成する。2段目の回路ST2は、演算増幅器3、サブA/Dコンバータ9、D/Aコンバータ10、減算回路6および演算増幅器4を備える。減算回路6および演算増幅器4が差分増幅器4aを構成する。

【0044】

1段目の回路ST1内の演算増幅器1,2および2段目の回路ST2内の演算増幅器3,4の利得はそれぞれ2である。1段目の回路ST1のサブA/Dコンバータ7は4ビット構成、2段目の回路ST2のサブA/Dコンバータ9は(2ビット+冗長1ビット)構成である。以下、冗長ビットを考慮せずに説明を行う。

【0045】

信号発生器30は、クロック信号CLK1,CLK2および制御信号SWを発生する。クロック信号CLK1の周波数はFsであり、クロック信号CLK3の周波数はクロック信号CLK1の周波数Fsの3倍すなわち3Fsである。制御信号SWの周波数はクロック信号CLK1の周波数Fsと等しい。

【0046】

1段目の回路ST1内の演算増幅器1、サブA/Dコンバータ7、D/Aコンバータ8および演算増幅器2は、クロック信号CLK1に応答して動作する。また、2段目の回路ST2内の演算増幅器3、サブA/Dコンバータ9、D/Aコンバータ10および演算増幅器4は、クロック信号CLK3に応答して動作する。さらに、スイッチSW1,SW2は、制御信号SWに応答して相補的にオンおよびオフする。

【0047】

入力端子Inには、アナログ信号Vinが与えられる。入力端子Inのアナログ信号Vinは、1段目の回路ST1内の演算増幅器1およびサブA/Dコンバータ7に入力される。サブA/Dコンバータ7は、アナログ信号Vinに対してA/D変換を行い、A/D変換結果である4ビットのデジタル信号を出力するとともにそのデジタル信号をD/Aコンバータ8に与える。D/Aコンバータ8は、サブA/Dコンバータ7から与えられる4ビットのデジタル信号に対してD/A変換を行い、アナログ信号VDAを出力する。

【0048】

一方、演算増幅器1は、入力端子Inのアナログ信号Vinをサンプリングおよび増幅して出力する。減算回路5は、演算増幅器1から出力されたアナログ信号VinとD/Aコンバータ8から出力されたアナログ信号VDAとを減算する。演算増幅器2は、減算回路5の出力信号を増幅してアナログ信号Voutを出力する。演算増幅器2から出力されるアナログ信号Voutは、スイッチSW1のオン時に2段目の回路ST2の入力ノードNIに与えられる。

【0049】

入力ノードNIのアナログ信号は、2段目の回路ST2内の演算増幅器3およびサブA/Dコンバータ9に入力される。サブA/Dコンバータ9は、アナログ信号に対してA/D変換を行い、A/D変換結果である2ビットのデジタル信号を出力するとともにそのデジタル信号をD/Aコンバータ10に与える。D/Aコンバータ10は、サブA/Dコンバータ9から与えられる2ビットのデジタル信号に対してD/A変換を行い、アナログ信号を出力する。

【0050】

一方、演算増幅器3は、入力ノードNIのアナログ信号をサンプリングおよび増幅して出力する。減算回路6は、演算増幅器3から出力されたアナログ信号とD/Aコンバータ10から出力されたアナログ信号とを減算する。演算増幅器4は、減算回路6の出力信号を増幅してアナログ信号を出力する。演算増幅器4から出力されるアナログ信号は、スイッチSW2のオン時に入力ノードNIに与えられる。

【0051】

本実施の形態では、2段目の回路ST2が第1の回路に相当し、1段目の回路ST1が第2の回路に相当する。また、スイッチSW1,SW2が切替手段に相当し、信号発生器30が制御手段に相当する。さらに、サブA/Dコンバータ9が第1のアナログ−デジタル変換器に相当し、D/Aコンバータ10が第1のデジタル−アナログ変換器に相当し、演算増幅器3が第1の演算増幅器に相当し、差分増幅器4aが第1の差分増幅器に相当する。また、サブA/Dコンバータ7が第2のアナログ−デジタル変換器に相当し、D/Aコンバータ8が第2のデジタル−アナログ変換器に相当し、演算増幅器1が第2の演算増幅器に相当し、差分増幅器2aが第2の差分増幅器に相当する。

【0052】

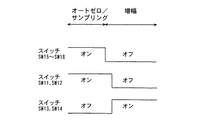

次に、図2を参照しながら図1のアナログ−デジタル変換回路100の全体の動作を説明する。図2は図1のアナログ−デジタル変換回路100の動作を説明するためのタイミングチャートである。

【0053】

図2において、AMPは増幅動作を示し、AZはオートゼロ動作を示し、SMPはサンプリング動作を示す。ここで、オートゼロ動作とは、演算増幅器の一対の入力端子間の電位差を0にする動作である。

【0054】

期間T1〜T5では、制御信号SWがローレベルになる。それにより、スイッチSW1がオフし、スイッチSW2がオンする。

【0055】

まず、期間T1〜T3では、クロック信号CLK1がハイレベルになる。それにより、1段目の回路ST1内の演算増幅器1が増幅動作を行い、サブA/Dコンバータ7がA/D変換動作を行う。この場合、サブA/Dコンバータ7から上位4ビットのデジタル信号D9〜D6が出力される。このとき、演算増幅器2はオートゼロ動作およびサンプリング動作を行う。また、D/Aコンバータ8の出力は不定となっている。

【0056】

次に、期間T4〜T6では、クロック信号CLK1がローレベルになる。それにより、1段目の回路ST1内の演算増幅器1がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ7がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器2は増幅動作を行い、D/Aコンバータ8はD/A変換動作を行う。D/Aコンバータ8から出力されるアナログ信号は確定する。

【0057】

期間T6〜T7では、制御信号SWがハイレベルになる。それにより、スイッチSW1がオンし、スイッチSW2がオフする。したがって、1段目の回路ST1内の演算増幅器2から出力されるアナログ信号がスイッチSW1を介して2段目の回路ST2の入力ノードNIに与えられる。

【0058】

まず、期間T6では、クロック信号CLK3がハイレベルになる。それにより、2段目の回路ST2内の演算増幅器3がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ9がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器4は増幅動作を行い、D/Aコンバータ10はD/A変換動作を行う。

【0059】

次に、期間T7では、クロック信号CLK3がローレベルになる。それにより、2段目の回路ST2内の演算増幅器3が増幅動作を行い、サブA/Dコンバータ9がA/D変換動作を行う。この場合、サブA/Dコンバータ9から中上位2ビットのデジタル信号D5,D4が出力される。このとき、演算増幅器4はオートゼロ動作およびサンプリング動作を行い、D/Aコンバータ10の出力は不定となっている。

【0060】

期間T8〜T11では、制御信号SWがローレベルになる。それにより、スイッチSW1がオフし、スイッチSW2がオンする。その結果、2段目の回路ST2内の演算増幅器4から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0061】

まず、期間T8では、クロック信号CLK3がハイレベルになる。それにより、2段目の回路ST2内の演算増幅器3がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ9がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器4は増幅動作を行い、D/Aコンバータ10はD/A変換動作を行う。それにより、演算増幅器4から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0062】

次に、期間T9では、クロック信号CLK3がローレベルになる。それにより、2段目の回路ST2内の演算増幅器3が増幅動作を行い、サブA/Dコンバータ9がA/D変換動作を行う。この場合、A/Dコンバータ9から中下位2ビットのデジタル信号D3,D2が出力される。このとき、演算増幅器4はオートゼロ動作およびサンプリング動作を行い、D/Aコンバータ10の出力は不定となっている。

【0063】

さらに、期間T10では、クロック信号CLK3がハイレベルになる。それにより、2段目の回路ST2内の演算増幅器3がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ9がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器4は増幅動作を行い、D/Aコンバータ10はD/A変換動作を行う。それにより、演算増幅器4から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0064】

次いで、期間T11では、クロック信号CLK3がローレベルになる。それにより、2段目の回路ST2内の演算増幅器3が増幅動作を行い、サブA/Dコンバータ9がA/D変換動作を行う。この場合、サブA/Dコンバータ9から下位2ビットのデジタル信号D1,D0が出力される。このとき、演算増幅器4はオートゼロ動作およびサンプリング動作を行い、D/Aコンバータ10の出力は不定となっている。

【0065】

上記のように、本実施の形態に係るアナログ−デジタル変換回路100においては、1段目の回路ST1から上位4ビットのデジタル信号D9〜D6が出力され、2段目の回路ST2から中上位2ビットのデジタル信号D5,D4、中下位2ビットのデジタル信号D3,D2および下位2ビットのデジタル信号D1,D0が順次出力される。このようにして、2段の回路ST1,ST2により10ビット4段パイプライン構成が実現される。したがって、省面積化が図られる。

【0066】

図3は本発明の他の実施の形態に係るアナログ−デジタル信号の構成を示すブロック図である。

【0067】

図3のアナログ−デジタル変換回路100aは、回路ST0、スイッチSW1,SW2および信号発生器30を備える。

【0068】

回路ST0は、演算増幅器11、サブA/Dコンバータ14、D/Aコンバータ15、減算回路13および演算増幅器12を備える。減算回路13および演算増幅器12が差分増幅器12aを構成する。

【0069】

回路ST0内の演算増幅器11,12の利得はそれぞれ4である。また、回路ST0のサブA/Dコンバータ14は4ビット構成である。

【0070】

信号発生器30は、クロック信号CLK1,CLK2および制御信号SWを発生する。クロック信号CLK1の周波数はFsであり、クロック信号CLK3の周波数はクロック信号CLK1の周波数Fsの3倍すなわち3Fsである。制御信号SWの周波数はクロック信号CLK1の周波数Fsと等しい。

【0071】

回路ST0内の演算増幅器11、サブA/Dコンバータ14、A/Dコンバータ15および演算増幅器12は、クロック信号CLK3に応答して動作する。また、スイッチSW1,SW2は、制御信号SWに応答して相補的にオンおよびオフする。

【0072】

入力端子Inには、アナログ信号Vinが与えられる。入力端子Inのアナログ信号Vinは、スイッチSW1のオン時に回路ST0内の演算増幅器11およびサブA/Dコンバータ14に入力される。サブA/Dコンバータ14は、アナログ信号Vinに対してA/D変換を行い、A/D変換結果である4ビットのデジタル信号を出力するとともにそのデジタル信号をD/Aコンバータ15に与える。D/Aコンバータ15は、サブA/Dコンバータ14から与えられる4ビットのデジタル信号に対してD/A変換を行い、アナログ信号を出力する。

【0073】

一方、演算増幅器11は、入力ノードNIのアナログ信号をサンプリングおよび増幅して出力する。減算回路13は、演算増幅器11から出力されたアナログ信号とD/Aコンバータ15から出力されたアナログ信号とを減算する。演算増幅器12は、減算回路13の出力信号を増幅してアナログ信号を出力する。演算増幅器12から出力されるアナログ信号は、スイッチSW2のオン時に入力ノードNIに与えられる。

【0074】

本実施の形態では、回路ST0が第1の回路に相当し、スイッチSW1,SW2が切替手段に相当し、信号発生器30が制御手段に相当する。さらに、サブA/Dコンバータ14が第1のアナログ−デジタル変換器に相当し、D/Aコンバータ15が第1のデジタル−アナログ変換器に相当し、演算増幅器11が第1の演算増幅器に相当し、差分増幅器12aが第1の差分増幅器に相当する。

【0075】

次に、図4を参照しながら図3のアナログ−デジタル変換回路100aの全体の動作を説明する。図4は図3のアナログ−デジタル変換回路100aの動作を説明するためのタイミングチャートである。

【0076】

図4において、AMPは増幅動作を示し、AZはオートゼロ動作を示し、SMPはサンプリング動作を示す。

【0077】

期間T1〜T2では、制御信号SWがハイレベルになる。それにより、スイッチSW1がオンし、スイッチSW2がオフする。したがって、入力端子Inに与えられるアナログ信号VinがスイッチSW1を介して入力ノードNIに与えられる。

【0078】

まず、期間T1では、クロック信号CLK3がハイレベルになる。それにより、回路ST0内の演算増幅器11がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ14がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器12は増幅動作を行い、D/Aコンバータ15の出力は不定となっている。

【0079】

次に、期間T2では、クロック信号CLK3がローレベルになる。それにより、回路ST0内の演算増幅器11が増幅動作を行い、サブA/Dコンバータ14がA/D変換動作を行う。この場合、サブA/Dコンバータ14から上位4ビットのデジタル信号D9〜D6が出力される。

【0080】

期間T3〜T6では、制御信号5Wがローレベルになる。それにより、スイッチSW1がオフし、スイッチSW2がオンする。したがって、演算増幅器12から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0081】

まず、期間T3では、クロック信号CLK3がハイレベルになる。それにより、回路ST0内の演算増幅器11がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ14がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器12は増幅動作を行い、D/Aコンバータ15はD/A変換動作を行う。その結果、演算増幅器12から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0082】

次に、期間T4では、クロック信号CLK3がローレベルになる。それにより、回路ST0内の演算増幅器11が増幅動作を行い、サブA/Dコンバータ14がA/D変換動作を行う。この場合、サブA/Dコンバータ14から中位3ビットのデジタル信号D5〜D3および冗長1ビットが出力される。このとき、演算増幅器12はオートゼロ動作およびサンプリング動作を行い、D/Aコンバータ15の出力は不定となっている。

【0083】

さらに、期間T5では、クロック信号CLK3がハイレベルになる。それにより、回路ST0内の演算増幅器11がオートゼロ動作およびサンプリング動作を行い、サブA/Dコンバータ14がオートゼロ動作およびサンプリング動作を行う。このとき、演算増幅器12は増幅動作を行い、D/Aコンバータ15はD/A変換動作を行う。その結果、演算増幅器12から出力ノードNOに出力されるアナログ信号がスイッチSW2を介して入力ノードNIに与えられる。

【0084】

続いて、期間T6では、クロック信号CLK3がローレベルになる。それにより、回路ST0内の演算増幅器11が増幅動作を行い、サブA/Dコンバータ14がA/D変換動作を行う。この場合、サブA/Dコンバータ14から下位3ビットのデジタル信号D2〜D0および冗長1ビットが出力される。このとき、演算増幅器12はオートゼロ動作およびサンプリング動作を行い、D/Aコンバータ15の出力は不定となっている。

【0085】

上記のように、本実施の形態に係るアナログ−デジタル変換回路100aにおいては、1段の回路ST0から上位4ビットのデジタル信号D9〜D6、中位3ビットのデジタル信号D5〜D3および下位3ビットのデジタル信号D2〜D0が順次出力される。このようにして、1段の回路ST0により10ビットの3段パイプライン構成が実現される。したがって、省面積化が実現される。

【0086】

また、上記実施の形態では、各段の回路ST1,ST2,ST0において、2段の演算増幅器1,2,3,4または11,12が設けられているが、各段の回路に1段の演算増幅器または3段以上の演算増幅器を設けてもよい。

【0087】

図5は図1および図3のアナログ−デジタル変換回路100,100aにおける信号発生器30の主要部の構成を示すブロック図である。

【0088】

図5の信号発生器30は、位相比較器31、VCO(電圧制御発振器)32、1/N分周器33、1/2分周器34およびレジスタ35を含む。レジスタ35には、予め値Nが格納されている。ここで、値Nは任意の正の整数である。レジスタ35から1/N分周器33に値Nを設定するための制御信号RCが与えられる。

【0089】

位相比較器31は、周波数Fsのクロック信号CLK1の位相と1/N分周器33の出力信号の位相とを比較し、位相差に応じた制御電圧をVCO32に与える。VCO32は、制御電圧に応じた周波数を有する発振信号を1/2分周器34および1/N分周器33に出力する。1/N分周器33は、VCO32から出力される発振信号を1/N分周し、1/N分周された出力信号を位相比較器31に与える。1/2分周器34は、VCO32から出力された発振信号を1/2分周し、1/2分周された発振信号をクロック信号CLKnとして出力する。クロック信号CLKnは、クロック信号CLK1のn倍の周波数nFsを有する。n=N/2である。

【0090】

例えば、1/N分周器33のレジスタにN=2が設定されている場合には、クロック信号CLKnの周波数はFsとなり、1/N分周器33のレジスタにN=4が設定されている場合には、クロック信号CLKnの周波数は2Fsとなり、N=6が設定されている場合には、クロック信号CLKnの周波数は3Fsとなり、N=8が設定されている場合には、クロック信号CLKnの周波数は4Fsる。なお、図1および図3の例はN=6の場合を示す。

【0091】

図1のアナログ−デジタル変換回路100においては、1/N分周器33の値Nを2に設定することによりクロック信号CLKnの周波数をFsに設定した場合、1段目の回路ST1が4ビット構成を有し、2段目の回路ST2が(2ビット+冗長1ビット)構成を有し、6ビットのパイプライン構成が実現される。また、1/N分周器33の値Nを4に設定することによりクロック信号CLKnの周波数を2Fsに設定した場合、1段目の回路ST1が4ビット構成を有し、2段目の回路ST2の第1および第2サイクルが(2ビット+冗長1ビット)構成を有し、8ビットのパイプライン構成が実現される。さらに、1/N分周器33の値Nを8に設定することによりクロック信号CLKnの周波数を4Fsに設定した場合、1段目の回路ST1が4ビット構成を有し、2段目の回路ST2の第1〜第4サイクルが(2ビット+冗長1ビット)構成を有し、12ビットのパイプライン構成が実現される。

【0092】

図3のアナログ−デジタル変換回路100aにおいては、1/N分周器33の値Nを2に設定することによりクロック信号CLKnの周波数をFsに設定した場合、回路ST0が4ビット構成を有し、4ビットのパイプライン構成が実現される。また、1/N分周器33の値Nを4に設定することによりクロック信号CLKnの周波数を2Fsに設定した場合、回路ST0の第1サイクルが4ビット構成を有し、回路ST0の第2サイクルが(3ビット+冗長1ビット)構成を有し、7ビットのパイプライン構成が実現される。さらに、1/N分周器33の値Nを8に設定することによりクロック信号CLKnの周波数を4Fsに設定した場合、回路ST0の第1サイクルが4ビット構成を有し、回路ST0の第2〜第4サイクルが(3ビット+冗長1ビット)構成を有し、13ビットのパイプライン構成が実現される。

【0093】

このように、図1および図3のアナログ−デジタル変換回路100,100aにおいては、1/N分周器33の分周比を任意に設定することにより、ビット分解能を容易に変更することができる。したがって、同一のハードウエア構成で異なるビット分解能を有するアナログ−デジタル変換回路が容易に実現される。

【0094】

なお、位相比較器31、VCO32および1/N分周器33が位相同期ループを構成し、1/N分周器33が分周器33に相当する。また、レジスタ35が分周比設定手段に相当する。

【0095】

図6は図1のアナログ−デジタル変換回路100における差分増幅器2aの回路図である。なお、図6の差分増幅器2aは完全差動方式の減算増幅回路である。

【0096】

図6の差分増幅器2aにおいて、演算増幅器20の非反転入力端子とノードN15との間にコンデンサ21が接続され、反転入力端子とノードN16との間にコンデンサ22が接続されている。

【0097】

ノードN15は、スイッチSW11を介してノードN11に接続され、かつスイッチSW13を介してノードN13に接続されている。ノードN16は、スイッチSW12を介してノードN12に接続され、かつスイッチSW14を介してノードN14に接続されている。

【0098】

演算増幅器20の反転出力端子は、ノードNO1に接続されるとともに、コンデンサ23を介して非反転入力端子に接続されている。演算増幅器20の非反転出力端子は、ノードNO2に接続されるとともに、コンデンサ24を介して反転入力端子に接続されている。

【0099】

演算増幅器20の非反転入力端子はスイッチSW15を介して基準電圧Vagを受ける基準端子に接続され、反転入力端子はスイッチSW17を介して基準端子に接続されている。演算増幅器20の反転出力端子はスイッチSW16を介して基準端子に接続され、非反転出力端子はスイッチSW18を介して基準端子に接続されている。ノードNO1,NO2は、それぞれコンデンサ25,26を介して接地されている。

【0100】

スイッチSW11〜SW18は、CMOSスイッチにより構成されている。これらのスイッチSW11〜SW18は、制御信号SWまたはその反転信号により制御される。

【0101】

この差分増幅器2aには、入力端子Inのアナログ信号VinおよびD/Aコンバータ8のD/A変換結果であるアナログ信号VDAが与えられる。すなわち、ノードN11,N12にそれぞれアナログ信号Vin(+),Vin(−)が与えられる。ここで、Vin=Vin(+)−Vin(−)である。また、ノードN13,N14にそれぞれアナログ信号VDA(+),VDA(−)が与えられる。ここで、VDA=VDA(+)−VDA(−)である。ノードNO1にはアナログ信号Vout(+)が現われ、ノードNO2にはアナログ信号Vout(−)が現われる。ここで、Vout=Vout(+)−Vout(−)である。

【0102】

次に、図7を参照しながら図6の差分増幅器2aの動作を説明する。図7は図6の差分増幅器2aの動作を説明するためのタイミングチャートである。ここでは、コンデンサ23,24の容量値をそれぞれCとし、コンデンサ21,22の容量値をそれぞれKCとする。Kは定数である。

【0103】

オートゼロ動作時およびサンプリング動作時には、スイッチSW11,SW12,SW15〜SW18がオンし、スイッチSW13,SW14がオフする。それにより、演算増幅器20の非反転入力端子および反転入力端子が等電位になり、反転出力端子および非反転出力端子が等電位になる。また、アナログ信号Vin(+)がスイッチSW11を介してノードN15に入力され、アナログ信号Vin(−)がスイッチSW12を介してノードN16に入力される。すなわち、アナログ信号Vin(+),Vin(−)がサンプリングされる。

【0104】

その後、スイッチSW15〜SW18がオフし、続いてスイッチSW11,SW12がオフする。この時点で、アナログ信号Vin(+),Vin(−)がコンデンサ21,22にそれぞれ保持される。

【0105】

増幅動作時に、スイッチSW13,SW14がオンする。それにより、アナログ信号VDA(+)がスイッチSW13を介してノードN15に入力され、アナログ信号VDA(−)がスイッチSW14を介してノードN16に入力される。その結果、アナログ信号Vin(+)とアナログ信号VDA(+)との差がK倍に増幅されるとともに、アナログ信号Vin(−)とアナログ信号VDA(−)との差がK倍に増幅される。それにより、ノードNO1にアナログ信号Vout(+)が現われ、ノードNO2にアナログ信号Vout(−)が現われる。ノードNO1,NO2間の電圧(アナログ信号Vout)は次式で表される。

【0106】

なお、図1の差分増幅器4aおよび図3の差分増幅器12aの構成および動作も図6および図7に示した差分増幅器2aの構成および動作と同様である。

【0107】

図8は図1のアナログ−デジタル変換回路100におけるサブA/Dコンバータ7の構成を示す回路図である。図8のサブA/Dコンバータ7は全並列比較(フラッシュ)方式サブA/Dコンバータである。

【0108】

図8のサブA/Dコンバータ7は、n個の抵抗R、n個の電圧比較器D1〜Dnおよびエンコーダ70により構成される。

【0109】

すべての抵抗Rは同じ抵抗値を有し、高電位側基準電圧VRTを受けるノードN31と低電位側基準電圧VRBを受けるノードN32との間に直列に接続されている。ここで、ノードN32とノードN31との間のn個の抵抗R間のノードN41〜N4nの電位をそれぞれVR(1)〜VR(n)とする。

【0110】

各電圧比較器D1〜Dnの非反転入力端子には、アナログ信号Vinが入力される。また、各電圧比較器D1〜Dnの反転入力端子には、それぞれノードN41〜N4nの電位VR(1)〜VR(n)が与えられる。

【0111】

それにより、各電圧比較器D1〜Dnの出力信号VD1〜VDnは、それぞれアナログ信号Vinが電位VR(1)〜VR(n)よりも高い場合にはハイレベルとなり、それぞれアナログ信号Vinが電位VR(1)〜VR(n)よりも低い場合にはローレベルとなる。

【0112】

エンコーダ70は、電圧比較器D1〜Dnの出力信号VD1〜VDnをエンコードし、4ビットのデジタル信号Doutを出力する。

【0113】

なお、図1のサブA/Dコンバータ9および図3のサブA/Dコンバータ14の構成および動作は、図8のサブA/Dコンバータ7の構成および動作と同様である。

【0114】

図9は図8のサブA/Dコンバータ7に用いられる差動型電圧比較器の回路図である。

【0115】

図9において、差動増幅回路50は、Pチャネル型MOS電界効果トランジスタ(以下、PMOSトランジスタと呼ぶ)51,52、Nチャネル型MOS電界効果トランジスタ(以下、NMOSトランジスタと呼ぶ)53,54および定電流源57により構成される。定電流源57には、飽和動作のNMOSトランジスタが使用される。

【0116】

ノードNDと出力ノードNO11との間にPMOSトランジスタ51が接続され、ノードNDと出力ノードNO12との間にPMOSトランジスタ52が接続されている。また、出力ノードNO11とノードNSとの間にNMOSトランジスタ53が接続され、出力ノードNO12とノードNSとの間にNMOSトランジスタ54が接続されている。

【0117】

ノードNDには電源電圧VDDが与えられ、ノードNSは定電流源57を介して接地されている。PMOSトランジスタ51,52のゲートにはバイアス電圧VB が与えられる。NMOSトランジスタ53,54のゲートはそれぞれ入力ノードNA,NBに接続されている。

【0118】

入力ノードNAはコンデンサ55を介してノードN1に接続され、入力ノードNBはコンデンサ56を介してノードN2に接続されている。入力ノードNAと出力ノードNO11との間にスイッチSW31が接続され、入力ノードNBと出力ノードNO12との間にスイッチSW41が接続されている。ノードN1にはスイッチSW32,SW33が並列に接続され、ノードN2にはスイッチSW42,SW43が並列に接続されている。

【0119】

スイッチSW31〜SW33,SW41〜SW43は、CMOSスイッチにより構成されている。これらのスイッチSW31〜SW33,SW41〜SW43は、制御信号SWまたはその反転信号により制御される。

【0120】

スイッチSW32,SW33の入力端にはそれぞれ入力電圧V1 (+),V2 (+)が与えられ、スイッチSW42,SW43の入力端にはそれぞれ入力電圧V1 (−),V2 (−)が与えられる。出力ノードNO11,NO12からは出力電圧Vo (+),Vo (−)が導出される。

【0121】

ここで、入力電圧V1 (+)と入力電圧V2 (+)との差を差分入力電圧ΔV(+)とし、入力電圧V1 (−)と入力電圧V2 (−)との差を差分入力電圧ΔV(−)とする。出力電圧Vo (+)と出力電圧Vo (−)との差を差分出力電圧ΔVo とする。この場合、図8のアナログ信号Vinが差分入力電圧ΔV(+)に相当し、電位VR(1)〜VR(n)のいずれかが差分入力電圧ΔV(−)に相当し、出力信号VD1〜VDnのいずれかが差分出力電圧ΔVo に相当する。

【0122】

図10は図9の電圧比較器の動作を説明するためのタイミングチャートである。

【0123】

オートゼロ動作時およびサンプリング動作時には、スイッチSW31,SW41,SW32,SW42がオンし、スイッチSW33,SW43がオフする。それにより、入力ノードNAと出力ノードNO11とが等電位になり、入力ノードNBと出力ノードNO12とが等電位になる。また、入力電圧V1 (+)がスイッチSW32を介して入力ノードNAに入力され、入力電圧V1 (−)がスイッチSW42を介して入力ノードNBに入力される。すなわち、入力電圧V1 (+)および入力電圧V1 (−)がサンプリングされる。

【0124】

その後、スイッチSW31,SW41がオフし、続いてスイッチSW32,SW42がオフする。この時点で、入力電圧V1 (+),V1 (−)がコンデンサ55,56にそれぞれ保持される。

【0125】

比較動作時には、スイッチSW33,SW43がオンする。これにより、入力電圧V2 (+)がスイッチSW33を介して入力ノードNAに入力され、入力電圧V2 (−)がスイッチSW43を介して入力ノードNBに入力される。その結果、入力ノードNAの電圧変化はV2 (+)−V1 (+)となり、入力ノードNBの電圧変化はV2 (−)−V1 (−)となる。

【0126】

入力ノードNAの差分入力電圧ΔV(+)=V2 (+)−V1 (+)と入力ノードNBの差分入力電圧ΔV(−)=V2 (−)−V1 (−)との比較結果に基づいて、出力ノードNO11の出力電圧Vo (+)および出力ノードNO12の出力電圧Vo (−)のうち一方が電源電圧VDDの側に変化し、他方が接地電位の側に変化する。それにより、出力ノードNO11,NO12間の差分出力電圧は0Vから比較結果に応じて正側または負側に変化する。

【0127】

なお、図8の電圧比較器D2〜Dnの構成および動作は、図9および図10の電圧比較器D1の構成および動作と同様である。

【0128】

図11は図1のアナログ−デジタル変換回路100におけるサブA/Dコンバータ7およびD/Aコンバータ8の回路図である。D/Aコンバータ8は容量アレイ方式D/Aコンバータである。なお、図11には図8のエンコーダ70は図示されていない。

【0129】

D/Aコンバータ8は、アレイ状に接続されたそれぞれn個のスイッチE1〜En,F1〜Fn,G1〜Gn,H1〜Hn、n個の正側コンデンサB1〜Bn、およびn個の負側コンデンサC1〜Cnから構成される。

【0130】

コンデンサB1〜Bn,C1〜Cnはすべて同じ容量値cを有する。コンデンサB1〜Bnの一方の端子(以下、出力端子と呼ぶ)からは差動正側出力電圧VDA(+)が生成され、コンデンサC1〜Cnの一方の端子(以下、出力端子という)からは差動負側出力電圧VDA(−)が生成される。なお、各コンデンサB1〜Bn,C1〜Cnの他方の端子を入力端子と呼ぶ。

【0131】

各スイッチE1〜Enの一方の端子はノードN31に接続され、他方の端子はコンデンサB1〜Bnの入力端子に接続されている。各スイッチF1〜Fnの一方の端子はノードN31に接続され、他方の端子はコンデンサC1〜Cnの入力端子に接続されている。各スイッチG1〜Gnの一方の端子はノードN32に接続され、他方の端子はコンデンサB1〜Bnの入力端子に接続されている。各スイッチH1〜Hnの一方の端子はノードN32に接続され、他方の端子はコンデンサC1〜Cnの入力端子に接続されている。

【0132】

各スイッチE1〜En,F1〜Fn,G1〜Gn,H1〜Hnはそれぞれ同一番号のスイッチで4連スイッチを構成する。例えば、スイッチE1,F1,G1,H1は1連であり、スイッチEn,Fn,Gn,Hnも1連である。そして、各スイッチE1〜En,F1〜Fn,G1〜Gn,H1〜Hnはそれぞれ各電圧比較器D1〜Dnの出力レベルに従ってオンオフ動作する。例えば、電圧比較器Dnの出力がハイレベルの場合、スイッチEn,Hnがオンし、スイッチGn,Fnはオフする。逆に、電圧比較器Dnの出力がローレベルの場合、スイッチEn,Hnがオフし、スイッチGn,Fnがオンする。

【0133】

次に、D/Aコンバータ8の動作を説明する。初期条件では、各コンデンサB1〜Bnの入力端子および出力端子の電位が共に0Vであり、各スイッチE1〜En,F1〜Fn,G1〜Gn,H1〜Hnはすべてオフしている。したがって、初期条件では、すべてのコンデンサB1〜Bn,C1〜Cnに蓄えられた電荷(電気量)Q1=0である。

【0134】

ここで、n個の電圧比較器D1〜Dnのうちm個の出力がハイレベルになった場合、各スイッチE1〜Enのうちm個がオンして(n−m)個がオフし、各スイッチG1〜Gnのうち(n−m)個がオンしてm個がオフする。この各スイッチE1〜En,G1〜Gnのオンオフ動作に従って、すべてのコンデンサB1〜Bnに蓄えられる電荷Q2は次式(A1)で表される。

【0135】

Q2=m(VRT−VDA(+))c+(n−m)(VRB−VDA(+))c…(A1)

電荷保存則より、Q1=Q2である。したがって、アナログ信号VDA(+)は次式(A2)で表される。

【0136】

VDA(+)=VRB+m(VRT−VRB)/n…(A2)

一方、n個の電圧比較器D1〜Dnのうちm個の出力がハイレベルになった場合、各スイッチH1〜Hnのうちm個がオンして(n−m)個がオフし、各スイッチF1〜Fnのうち(n−m)個がオンしてm個がオフする。この各スイッチH1〜Hn,F1〜Fnのオンオフ動作に従って、すべてのコンデンサC1〜Cnに蓄えられる電荷Q3は次式(A3)で表される。

【0137】

Q3=(n−m)(VRT−VDA(−))c+m(VRB−VDA(−))c…(A3)

電荷保存則より、Q1=Q3である。したがって、アナログ信号VDA(−)は次式(A4)で表される。

【0138】

VDA(−)=VRT−m(VRT−VRB)/n…(A4)

したがって、上式(A2),(A4)より、アナログ信号VDAは式(A5)で表される。

【0139】

VDA=VDA(+)−VDA(−)

=VRB−VRT+2m(VRT−VRB)/n…(A5)

以上のように、上記実施の形態に係るアナログ−デジタル変換回路100,100aにおいては、省面積化が図られるとともに、同一のハードウエア構成で異なるビット構成が実現されるので、エンベデッド型アナログ−デジタル変換回路に最適である。

【図面の簡単な説明】

【図1】本発明の一実施の形態に係るアナログ−デジタル変換回路の構成を示すブロック図である。

【図2】図1のアナログ−デジタル変換回路の動作を説明するためのタイミングチャートである。

【図3】本発明の他の実施の形態に係るアナログ−デジタル信号の構成を示すブロック図である。

【図4】図3のアナログ−デジタル変換回路の動作を説明するためのタイミングチャートである。

【図5】図1および図3のアナログ−デジタル変換回路における信号発生器の主要部の構成を示すブロック図である。

【図6】図1のアナログ−デジタル変換回路における差分増幅器の回路図である。

【図7】図6の差分増幅器の動作を説明するためのタイミングチャートである。

【図8】図1のアナログ−デジタル変換回路におけるサブA/Dコンバータの構成を示す回路図である。

【図9】図8のサブA/Dコンバータに用いられる差動型電圧比較器の回路図である。

【図10】図9の電圧比較器の動作を説明するためのタイミングチャートである。

【図11】図1のアナログ−デジタル変換回路におけるサブA/DコンバータおよびD/Aコンバータの回路図である。

【図12】従来のアナログ−デジタル変換回路を示すブロック図である。

【符号の説明】

100,100a アナログ−デジタル変換回路

ST1,ST2,ST0 回路

7,9,14 サブA/Dコンバータ

8,10,15 D/Aコンバータ

1,2,3,4,11,12 演算増幅器

5,6 減算回路

2a,4a,12a 差分増幅器

SW1,SW2 スイッチ

Claims (7)

- 第1および第2のノードを有する第1の回路と、

入力されたアナログ信号および前記第2のノードのアナログ信号のいずれか一方を選択的に前記第1のノードに与える切替手段と、

前記切替手段を制御する制御手段とを備え、

前記第1の回路は、

前記第1のノードからのアナログ信号をデジタル信号に変換する第1のアナログ−デジタル変換器と、

前記第1のアナログ−デジタル変換器から出力されたデジタル信号をアナログ信号に変換する第1のデジタル−アナログ変換器と、

前記第1のノードからのアナログ信号と前記第1のデジタル−アナログ変換器から出力されたアナログ信号との差分を増幅して前記第2のノードに出力する第1の差分増幅器とを含み、

前記制御手段は、入力されたアナログ信号が前記第1のノードに与えられた後、前記第1のアナログ−デジタル変換器による変換動作、前記第1のデジタル−アナログ変換器による変換動作および前記第1の差分増幅器による増幅動作が所定サイクル数行われるように前記切替手段を制御することを特徴とするアナログ−デジタル変換回路。 - 前記第1の回路は、前記第1のノードのアナログ信号を増幅して前記第1の差分増幅器に与える第1の演算増幅器をさらに含むことを特徴とする請求項1記載のアナログ−デジタル変換回路。

- 前記切替手段を介して前記第1の回路の前段に少なくとも1段に設けられた第2の回路をさらに備え、

前記第2の回路は、

入力されたアナログ信号をデジタル信号に変換する第2のアナログ−デジタル変換器と、

前記第2のアナログ−デジタル変換器から出力されたデジタル信号をアナログ信号に変換する第2のデジタル−アナログ変換器と、

前記入力されたアナログ信号と前記第2のデジタル−アナログ変換器から出力されたアナログ信号との差分を増幅して前記切替手段を介して前記第1の回路に出力する第2の差分増幅器とを含むことを特徴とする請求項1または2記載のアナログ−デジタル変換回路。 - 前記第2の回路は、前記入力されたアナログ信号を増幅して前記第2の差分増幅器に与える第2の演算増幅器をさらに含むことを特徴とする請求項3記載のアナログ−デジタル変換回路。

- 前記制御手段は、クロック信号および制御信号を発生する信号発生器を含み、

前記第1の回路の前記第1のアナログ−デジタル変換器、前記第1のデジタル−アナログ変換器および前記第1の差分増幅器は、前記信号発生器により発生されたクロック信号に応答して動作し、

前記切替手段は、前記信号発生器により発生された制御信号に応答して、入力されたアナログ信号を前記第1のノードに与える状態と、前記第2のノードのアナログ信号を前記第1のノードに与える状態とを切り替えることを特徴とする請求項1〜4のいずれかに記載のアナログ−デジタル変換回路。 - 前記制御手段は、前記信号発生器により発生されるクロック信号の周波数を変更する変更手段をさらに含むことを特徴とする請求項5記載のアナログ−デジタル変換回路。

- 前記信号発生器は、分周器を有する位相同期ループを含み、

前記変更手段は、前記位相同期ループの前記分周器の分周比を設定する分周比設定手段を含むことを特徴とする請求項6記載のアナログ−デジタル変換回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002258058A JP2004096636A (ja) | 2002-09-03 | 2002-09-03 | アナログ−デジタル変換回路 |

| EP03255510A EP1398880A3 (en) | 2002-09-03 | 2003-09-03 | Analog-digital conversion circuit |

| CNB031593186A CN100334809C (zh) | 2002-09-03 | 2003-09-03 | 模一数变换电路 |

| US10/653,251 US6859158B2 (en) | 2002-09-03 | 2003-09-03 | Analog-digital conversion circuit |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002258058A JP2004096636A (ja) | 2002-09-03 | 2002-09-03 | アナログ−デジタル変換回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007234156A Division JP2007325319A (ja) | 2007-09-10 | 2007-09-10 | アナログ−デジタル変換器 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2004096636A true JP2004096636A (ja) | 2004-03-25 |

| JP2004096636A5 JP2004096636A5 (ja) | 2005-07-07 |

Family

ID=31884709

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002258058A Pending JP2004096636A (ja) | 2002-09-03 | 2002-09-03 | アナログ−デジタル変換回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6859158B2 (ja) |

| EP (1) | EP1398880A3 (ja) |

| JP (1) | JP2004096636A (ja) |

| CN (1) | CN100334809C (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012111821A1 (ja) * | 2011-02-18 | 2012-08-23 | 国立大学法人静岡大学 | A/d変換器、イメージセンサデバイス及びアナログ信号からディジタル信号を生成する方法 |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4014553B2 (ja) * | 2003-09-29 | 2007-11-28 | 三洋電機株式会社 | アナログデジタル変換器 |

| US7095352B2 (en) * | 2004-03-02 | 2006-08-22 | Sanyo Electric Co., Ltd. | Analog-to-digital converter including a plurality of amplifier circuits |

| JP4093976B2 (ja) * | 2004-03-17 | 2008-06-04 | 三洋電機株式会社 | アナログデジタル変換器 |

| JP3785175B2 (ja) * | 2004-03-30 | 2006-06-14 | 株式会社東芝 | 多入力a/d変換装置及びこれを用いた無線受信機 |

| US7193553B1 (en) * | 2004-12-07 | 2007-03-20 | National Semiconductor Corporation | Analog to digital converter with power-saving adjustable resolution |

| JP2006173807A (ja) * | 2004-12-13 | 2006-06-29 | Sanyo Electric Co Ltd | アナログデジタル変換器 |

| JP2007208422A (ja) * | 2006-01-31 | 2007-08-16 | Sanyo Electric Co Ltd | アナログデジタル変換器 |

| US7397412B1 (en) * | 2006-02-03 | 2008-07-08 | Marvell International Ltd. | Low power analog to digital converter |

| US8553827B2 (en) * | 2009-10-20 | 2013-10-08 | Qualcomm Incorporated | ADC-based mixed-mode digital phase-locked loop |

| US9043062B2 (en) * | 2012-10-05 | 2015-05-26 | Ford Global Technologies, Llc | Hybrid electric vehicle powertrain and control system |

| US10230384B2 (en) | 2016-12-09 | 2019-03-12 | Rambus Inc. | Variable resolution digital equalization |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2689689B2 (ja) * | 1990-05-22 | 1997-12-10 | 日本電気株式会社 | 直並列型アナログ/ディジタル変換器 |

| JP3153271B2 (ja) * | 1991-07-05 | 2001-04-03 | 株式会社日立製作所 | Ad変換器 |

| JP3581485B2 (ja) * | 1996-04-05 | 2004-10-27 | 株式会社ルネサステクノロジ | パイプライン型a/dコンバータ |

| JP3384717B2 (ja) | 1997-09-04 | 2003-03-10 | 三洋電機株式会社 | アナログ−デジタル変換回路 |

| EP0901232A3 (en) * | 1997-09-04 | 2002-11-20 | Sanyo Electric Co., Ltd. | Voltage comparator, operational amplifier and analog-to-digital conversion circuit employing the same |

| US6097326A (en) * | 1998-05-26 | 2000-08-01 | National Semiconductor Corporation | Algorithmic analog-to-digital converter with reduced differential non-linearity and method |

| CN1285174C (zh) * | 2001-06-18 | 2006-11-15 | 三洋电机株式会社 | 模-数转换电路 |

-

2002

- 2002-09-03 JP JP2002258058A patent/JP2004096636A/ja active Pending

-

2003

- 2003-09-03 EP EP03255510A patent/EP1398880A3/en not_active Withdrawn

- 2003-09-03 US US10/653,251 patent/US6859158B2/en not_active Expired - Lifetime

- 2003-09-03 CN CNB031593186A patent/CN100334809C/zh not_active Expired - Fee Related

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2012111821A1 (ja) * | 2011-02-18 | 2012-08-23 | 国立大学法人静岡大学 | A/d変換器、イメージセンサデバイス及びアナログ信号からディジタル信号を生成する方法 |

| US9236879B2 (en) | 2011-02-18 | 2016-01-12 | National University Corporation Shizuoka University | A/D converter, image sensor device, and method of generating digital signal from analog signal |

| KR101743800B1 (ko) | 2011-02-18 | 2017-06-05 | 고쿠리츠 다이가꾸 호우진 시즈오까 다이가꾸 | A/d 변환기, 이미지 센서 디바이스 및 아날로그 신호로부터 디지털 신호를 생성하는 방법 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN1490936A (zh) | 2004-04-21 |

| EP1398880A3 (en) | 2006-04-26 |

| EP1398880A2 (en) | 2004-03-17 |

| US20040041722A1 (en) | 2004-03-04 |

| CN100334809C (zh) | 2007-08-29 |

| US6859158B2 (en) | 2005-02-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5710563A (en) | Pipeline analog to digital converter architecture with reduced mismatch error | |

| US6967611B2 (en) | Optimized reference voltage generation using switched capacitor scaling for data converters | |

| US8957794B2 (en) | A/D converter and method for calibrating the same | |

| US9059730B2 (en) | Pipelined successive approximation analog-to-digital converter | |

| CN101854174B (zh) | 一种流水线型模数转换器及其子转换级电路 | |

| US7030804B2 (en) | Switched-capacitor circuit and pipelined A/D converter | |

| KR20060052937A (ko) | 공간 효율적 저전력 주기적 a/d 변환기 | |

| CN111200437B (zh) | A/d转换器 | |

| Mulder et al. | An 800MS/s dual-residue pipeline ADC in 40nm CMOS | |

| JP2004096636A (ja) | アナログ−デジタル変換回路 | |

| JP2000036746A (ja) | A/d変換器 | |

| JP2006303671A (ja) | 積分器およびそれを使用する巡回型ad変換装置 | |

| US7224306B2 (en) | Analog-to-digital converter in which settling time of amplifier circuit is reduced | |

| JP2012227774A (ja) | アナログデジタル変換器および信号処理システム | |

| KR100294787B1 (ko) | 개방루프차동증폭기를갖는서브레인지아날로그/디지털컨버터 | |

| KR101711542B1 (ko) | 레인지-스케일링 기반의 복합 파이프라인 아날로그-디지털 컨버터 | |

| JP5609522B2 (ja) | アナログデジタル変換器および信号処理システム | |

| JP3942383B2 (ja) | アナログ−デジタル変換回路 | |

| Atchaya et al. | Design of High Speed Time–Interleaved SAR Analog to Digital Converter | |

| JP2004080581A (ja) | 電圧比較器、アナログ−デジタル変換器およびアナログ−デジタル変換回路 | |

| JP3851305B2 (ja) | アナログ−デジタル変換回路 | |

| JPH11112305A (ja) | 電圧比較器、演算増幅器、アナログ−デジタル変換器およびアナログ−デジタル変換回路 | |

| JP2007325319A (ja) | アナログ−デジタル変換器 | |

| JP3530349B2 (ja) | 減算増幅回路およびアナログ−デジタル変換回路 | |

| JP2004180333A (ja) | アナログ−デジタル変換回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041109 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20041109 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060719 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060808 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061005 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20070717 |