JP2010080900A - 絶縁ゲート型半導体装置 - Google Patents

絶縁ゲート型半導体装置 Download PDFInfo

- Publication number

- JP2010080900A JP2010080900A JP2008326093A JP2008326093A JP2010080900A JP 2010080900 A JP2010080900 A JP 2010080900A JP 2008326093 A JP2008326093 A JP 2008326093A JP 2008326093 A JP2008326093 A JP 2008326093A JP 2010080900 A JP2010080900 A JP 2010080900A

- Authority

- JP

- Japan

- Prior art keywords

- protection diode

- protection

- type semiconductor

- insulated gate

- junction

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/126—Top-view geometrical layouts of the regions or the junctions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/126—Top-view geometrical layouts of the regions or the junctions

- H10D62/127—Top-view geometrical layouts of the regions or the junctions of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/101—Integrated devices comprising main components and built-in components, e.g. IGBT having built-in freewheel diode

- H10D84/141—VDMOS having built-in components

- H10D84/148—VDMOS having built-in components the built-in components being breakdown diodes, e.g. Zener diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/60—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD]

- H10D89/601—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs

- H10D89/611—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs using diodes as protective elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/517—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers

- H10D64/519—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers characterised by their top-view geometrical layouts

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Abstract

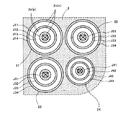

【解決手段】複数の保護ダイオードを並列接続した保護ダイオード群とし、保護ダイオード群の合計接合面積平均を所望の静電気放電耐量が確保できる値とする。合計接合面積平均を従来構造の接合面積平均と同等にすることで、従来と同等のESD耐量を維持してチップ上での保護ダイオード群の占有面積を低減できる。

【選択図】 図1

Description

2 保護ダイオード群

2n n型半導体領域

2p p型半導体領域

4 ゲート連結電極

5 動作領域

6 セル

7 ソース電極

10 MOSFET

11 第1ゲート電極層

12 第2ゲート電極層

17 第1ソース電極層

18 第2ソース電極層

21、22、23、24 保護ダイオード

21’、22’、23’、24’ 保護ダイオード

31 ゲートパッド電極

32 保護ダイオード

34 ゲート連結電極

35 動作領域

36 セル

J11、J12、J13、J14 pn接合部

J21、J22、J23、J24 pn接合部

J31、J32、J33、J34 pn接合部

J41、J42、J43、J44 pn接合部

J1、J2、J3、J4 合計接合面積

J、j 合計接合面積平均

j11、j12、j13、j14 pn接合部

Claims (12)

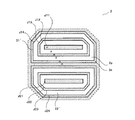

- 絶縁ゲート型半導体素子のトランジスタセルが配置される動作領域と、

前記トランジスタセルのゲート電極に接続する一つのゲートパッド電極と、

前記動作領域の外部に配置された保護ダイオード群とを備え、

該保護ダイオード群は一の保護ダイオードと他の保護ダイオードとを並列接続して構成され、前記一の保護ダイオードと前記他の保護ダイオードはそれぞれ、p型半導体領域とn型半導体領域からなる複数のpn接合を有することを特徴とする絶縁ゲート型半導体装置。 - 前記保護ダイオードは、前記ゲートパッド電極の下方に配置されることを特徴とする請求項1に記載の絶縁ゲート型半導体装置。

- 前記動作領域の周囲に導電層が設けられ、該導電層の一部に前記保護ダイオードが設けられることを特徴とする請求項1に記載の絶縁ゲート型半導体装置。

- 前記保護ダイオード群の前記一の保護ダイオードと前記他の保護ダイオードはそれぞれ、同心状に配置されたp型半導体領域とn型半導体領域からなる複数のpn接合を有することを特徴とする請求項2または請求項3に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードと前記他の保護ダイオードはそれぞれN個のpn接合を有し、対応する各pn接合毎に合計した接合面積の第1周目から第N周目までの平均値を、所望の静電気放電耐量が確保できる値とすることを特徴とする請求項4に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードと前記他の保護ダイオードは、同等の形状からなることを特徴とする請求項5に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードおよび他の保護ダイオードは矩形であることを特徴とする請求項6に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードおよび他の保護ダイオードは円形状であることを特徴とする請求項6に記載の絶縁ゲート型半導体装置。

- 前記保護ダイオード群は4つの保護ダイオードから構成されることを特徴とする請求項7または請求項8に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードと前記他の保護ダイオードは、それぞれの最外周のp型半導体領域またはn型半導体領域を共用することを特徴とする請求項9に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードと前記他の保護ダイオードは、それぞれの最外周のp型半導体領域またはn型半導体領域が互いに離間して配置され、金属層で接続されることを特徴とする請求項7または請求項8に記載の絶縁ゲート型半導体装置。

- 前記一の保護ダイオードと前記他の保護ダイオードは、それぞれの端面が露出しないことを特徴とする請求項10または請求項11に記載の絶縁ゲート型半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008326093A JP5337470B2 (ja) | 2008-04-21 | 2008-12-22 | 絶縁ゲート型半導体装置 |

| CN2009101327414A CN101577276B (zh) | 2008-04-21 | 2009-04-16 | 绝缘栅型半导体装置 |

| US12/425,893 US8106460B2 (en) | 2008-04-21 | 2009-04-17 | Insulated gate semiconductor device |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008110507 | 2008-04-21 | ||

| JP2008110507 | 2008-04-21 | ||

| JP2008217103 | 2008-08-26 | ||

| JP2008217103 | 2008-08-26 | ||

| JP2008326093A JP5337470B2 (ja) | 2008-04-21 | 2008-12-22 | 絶縁ゲート型半導体装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010080900A true JP2010080900A (ja) | 2010-04-08 |

| JP5337470B2 JP5337470B2 (ja) | 2013-11-06 |

Family

ID=41200402

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008326093A Active JP5337470B2 (ja) | 2008-04-21 | 2008-12-22 | 絶縁ゲート型半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8106460B2 (ja) |

| JP (1) | JP5337470B2 (ja) |

| CN (1) | CN101577276B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008085188A (ja) * | 2006-09-28 | 2008-04-10 | Sanyo Electric Co Ltd | 絶縁ゲート型半導体装置 |

| JP5511124B2 (ja) * | 2006-09-28 | 2014-06-04 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 絶縁ゲート型半導体装置 |

| JP2010177454A (ja) * | 2009-01-29 | 2010-08-12 | Sanyo Electric Co Ltd | 絶縁ゲート型半導体装置 |

| US8278728B2 (en) * | 2009-10-17 | 2012-10-02 | Florida Institute Of Technology | Array of concentric CMOS photodiodes for detection and de-multiplexing of spatially modulated optical channels |

| CN102122657A (zh) * | 2010-12-16 | 2011-07-13 | 苏州华芯微电子股份有限公司 | 集成电路的esd保护结构 |

| JP6037499B2 (ja) | 2011-06-08 | 2016-12-07 | ローム株式会社 | 半導体装置およびその製造方法 |

| JP6539035B2 (ja) * | 2014-01-08 | 2019-07-03 | ローム株式会社 | チップ部品 |

| JP2016058645A (ja) | 2014-09-11 | 2016-04-21 | 株式会社東芝 | 半導体装置 |

| US10692863B2 (en) * | 2016-09-30 | 2020-06-23 | Rohm Co., Ltd. | Semiconductor device and semiconductor package |

| JP7097742B2 (ja) * | 2018-05-01 | 2022-07-08 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| CN109585443A (zh) * | 2018-11-29 | 2019-04-05 | 中国电子科技集团公司第四十七研究所 | 硅衬底内部esd结构的制造方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07321307A (ja) * | 1994-05-20 | 1995-12-08 | Hitachi Ltd | 半導体装置 |

| JP2001326354A (ja) * | 2000-03-06 | 2001-11-22 | Rohm Co Ltd | 半導体装置 |

| JP2007035796A (ja) * | 2005-07-25 | 2007-02-08 | Matsushita Electric Ind Co Ltd | 半導体装置 |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3712995A (en) * | 1972-03-27 | 1973-01-23 | Rca Corp | Input transient protection for complementary insulated gate field effect transistor integrated circuit device |

| EP0322860B1 (en) * | 1987-12-28 | 1996-09-11 | Fuji Electric Co., Ltd. | Insulated gate semiconductor device |

| JPH07105495B2 (ja) | 1988-05-06 | 1995-11-13 | 富士電機株式会社 | 絶縁ゲート型半導体装置 |

| JP2919494B2 (ja) | 1989-08-10 | 1999-07-12 | 三洋電機株式会社 | 縦型mosfet |

| US5079608A (en) * | 1990-11-06 | 1992-01-07 | Harris Corporation | Power MOSFET transistor circuit with active clamp |

| JPH08274321A (ja) * | 1995-03-31 | 1996-10-18 | Rohm Co Ltd | 半導体装置 |

| JPH08330605A (ja) * | 1995-05-31 | 1996-12-13 | Nec Yamagata Ltd | 半導体装置 |

| DE19811297B4 (de) * | 1997-03-17 | 2009-03-19 | Fuji Electric Co., Ltd., Kawasaki | MOS-Halbleitervorrichtung mit hoher Durchbruchspannung |

| SG67518A1 (en) * | 1997-06-30 | 1999-09-21 | Matsushita Electric Works Ltd | Solid-state relay |

| JP3191747B2 (ja) * | 1997-11-13 | 2001-07-23 | 富士電機株式会社 | Mos型半導体素子 |

| GB9818182D0 (en) * | 1998-08-21 | 1998-10-14 | Zetex Plc | Gated semiconductor device |

| WO2000062345A1 (en) * | 1999-04-09 | 2000-10-19 | Shindengen Electric Manufacturing Co., Ltd. | High-voltage semiconductor device |

| US6413822B2 (en) * | 1999-04-22 | 2002-07-02 | Advanced Analogic Technologies, Inc. | Super-self-aligned fabrication process of trench-gate DMOS with overlying device layer |

| EP1231640A4 (en) * | 2000-06-27 | 2008-10-08 | Matsushita Electric Industrial Co Ltd | SEMICONDUCTOR COMPONENT |

| JP2002043574A (ja) | 2000-07-27 | 2002-02-08 | Sanyo Electric Co Ltd | Mosfetの保護装置およびその製造方法 |

| JP2002141507A (ja) * | 2000-10-31 | 2002-05-17 | Mitsubishi Electric Corp | 半導体装置とその製造方法 |

| JP2002208702A (ja) * | 2001-01-10 | 2002-07-26 | Mitsubishi Electric Corp | パワー半導体装置 |

| JP4124981B2 (ja) * | 2001-06-04 | 2008-07-23 | 株式会社ルネサステクノロジ | 電力用半導体装置および電源回路 |

| JP2002368218A (ja) | 2001-06-08 | 2002-12-20 | Sanyo Electric Co Ltd | 絶縁ゲート型半導体装置 |

| GB0202437D0 (en) * | 2002-02-02 | 2002-03-20 | Koninkl Philips Electronics Nv | Cellular mosfet devices and their manufacture |

| US6855970B2 (en) * | 2002-03-25 | 2005-02-15 | Kabushiki Kaisha Toshiba | High-breakdown-voltage semiconductor device |

| JP3721172B2 (ja) * | 2003-04-16 | 2005-11-30 | 株式会社東芝 | 半導体装置 |

| CN101567373B (zh) * | 2004-02-16 | 2011-04-13 | 富士电机系统株式会社 | 双方向元件及其制造方法 |

| JP2005332886A (ja) * | 2004-05-18 | 2005-12-02 | Toshiba Corp | 半導体装置 |

| US7439591B2 (en) * | 2004-10-05 | 2008-10-21 | Infineon Technologies Ag | Gate layer diode method and apparatus |

| JP2006140372A (ja) * | 2004-11-15 | 2006-06-01 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| JP2006310508A (ja) * | 2005-04-28 | 2006-11-09 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

| JP2007042817A (ja) * | 2005-08-02 | 2007-02-15 | Sanyo Electric Co Ltd | 絶縁ゲート型半導体装置およびその製造方法 |

| JP5048273B2 (ja) * | 2006-05-10 | 2012-10-17 | オンセミコンダクター・トレーディング・リミテッド | 絶縁ゲート型半導体装置 |

| JP5073992B2 (ja) * | 2006-08-28 | 2012-11-14 | オンセミコンダクター・トレーディング・リミテッド | 半導体装置 |

| JP2008085188A (ja) * | 2006-09-28 | 2008-04-10 | Sanyo Electric Co Ltd | 絶縁ゲート型半導体装置 |

| JP5511124B2 (ja) | 2006-09-28 | 2014-06-04 | セミコンダクター・コンポーネンツ・インダストリーズ・リミテッド・ライアビリティ・カンパニー | 絶縁ゲート型半導体装置 |

| JP2008130983A (ja) * | 2006-11-24 | 2008-06-05 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| JP4599379B2 (ja) * | 2007-08-31 | 2010-12-15 | 株式会社東芝 | トレンチゲート型半導体装置 |

| JP2009076761A (ja) * | 2007-09-21 | 2009-04-09 | Sanyo Electric Co Ltd | 半導体装置およびその製造方法 |

-

2008

- 2008-12-22 JP JP2008326093A patent/JP5337470B2/ja active Active

-

2009

- 2009-04-16 CN CN2009101327414A patent/CN101577276B/zh not_active Expired - Fee Related

- 2009-04-17 US US12/425,893 patent/US8106460B2/en active Active

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07321307A (ja) * | 1994-05-20 | 1995-12-08 | Hitachi Ltd | 半導体装置 |

| JP2001326354A (ja) * | 2000-03-06 | 2001-11-22 | Rohm Co Ltd | 半導体装置 |

| JP2007035796A (ja) * | 2005-07-25 | 2007-02-08 | Matsushita Electric Ind Co Ltd | 半導体装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP5337470B2 (ja) | 2013-11-06 |

| CN101577276A (zh) | 2009-11-11 |

| US8106460B2 (en) | 2012-01-31 |

| CN101577276B (zh) | 2012-05-23 |

| US20090261418A1 (en) | 2009-10-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5337470B2 (ja) | 絶縁ゲート型半導体装置 | |

| US12046641B2 (en) | SiC semiconductor device with insulating film and organic insulating layer | |

| JP6000513B2 (ja) | 絶縁ゲート型半導体装置 | |

| US7732869B2 (en) | Insulated-gate semiconductor device | |

| JP7139861B2 (ja) | 絶縁ゲート型バイポーラトランジスタ | |

| US11430781B2 (en) | Semiconductor die | |

| CN109524452B (zh) | 半导体器件 | |

| USRE47390E1 (en) | Semiconductor device with a protection diode | |

| JP4038389B2 (ja) | 半導体素子 | |

| JP2011009630A (ja) | 保護ダイオード | |

| JP2024096848A (ja) | 半導体装置 | |

| US7948032B2 (en) | Power MOS transistor device and layout | |

| JP4790340B2 (ja) | 半導体装置 | |

| JP3664129B2 (ja) | 半導体装置 | |

| US20250267954A1 (en) | Semiconductor device | |

| JP5431617B1 (ja) | 半導体装置 | |

| WO2025070298A1 (ja) | 半導体装置 | |

| WO2025070299A1 (ja) | 半導体装置 | |

| JP5697735B2 (ja) | 半導体装置 | |

| JP2010109167A (ja) | 半導体装置 | |

| JP2013008807A (ja) | 絶縁ゲート型半導体装置 | |

| JP2012019123A (ja) | 接合型電界効果トランジスタ | |

| JPH11265999A (ja) | Soi基板および半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20110609 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20111128 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20130215 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20130215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130405 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130522 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130709 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130805 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5337470 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: R3D04 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |