JP2010062247A - 記憶素子および記憶装置 - Google Patents

記憶素子および記憶装置 Download PDFInfo

- Publication number

- JP2010062247A JP2010062247A JP2008224711A JP2008224711A JP2010062247A JP 2010062247 A JP2010062247 A JP 2010062247A JP 2008224711 A JP2008224711 A JP 2008224711A JP 2008224711 A JP2008224711 A JP 2008224711A JP 2010062247 A JP2010062247 A JP 2010062247A

- Authority

- JP

- Japan

- Prior art keywords

- high resistance

- layer

- electrode

- resistance layer

- memory element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Granted

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/30—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices comprising selection components having three or more electrodes, e.g. transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B63/00—Resistance change memory devices, e.g. resistive RAM [ReRAM] devices

- H10B63/80—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays

- H10B63/82—Arrangements comprising multiple bistable or multi-stable switching components of the same type on a plane parallel to the substrate, e.g. cross-point arrays the switching components having a common active material layer

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/011—Manufacture or treatment of multistable switching devices

- H10N70/021—Formation of switching materials, e.g. deposition of layers

- H10N70/026—Formation of switching materials, e.g. deposition of layers by physical vapor deposition, e.g. sputtering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/20—Multistable switching devices, e.g. memristors

- H10N70/24—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies

- H10N70/245—Multistable switching devices, e.g. memristors based on migration or redistribution of ionic species, e.g. anions, vacancies the species being metal cations, e.g. programmable metallization cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/821—Device geometry

- H10N70/826—Device geometry adapted for essentially vertical current flow, e.g. sandwich or pillar type devices

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/841—Electrodes

- H10N70/8416—Electrodes adapted for supplying ionic species

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/882—Compounds of sulfur, selenium or tellurium, e.g. chalcogenides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N70/00—Solid-state devices having no potential barriers, and specially adapted for rectifying, amplifying, oscillating or switching

- H10N70/801—Constructional details of multistable switching devices

- H10N70/881—Switching materials

- H10N70/883—Oxides or nitrides

- H10N70/8833—Binary metal oxides, e.g. TaOx

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Memories (AREA)

Abstract

【解決手段】下部電極3と上部電極6の間に高抵抗層4とイオン源層5とを備える。高抵抗層4は、Teを含む酸化物から構成されている。Te以外の他の元素、例えばAlや、Zr,Ta,Hf,Si,Ge,Ni,Co,CuおよびAuのいずれかを添加してもよい。TeにAlを添加し、更にCuおよびZrを加えたものとする場合、高抵抗層4の組成比は、酸素を除いて、30≦Te≦100原子%、0≦Al≦70原子%、および0≦Cu+Zr≦36原子%の範囲で調整することが望ましい。イオン源層5は、少なくとも一種の金属元素と、Te,SおよびSeのうち少なくとも一種類のカルコゲン元素とから構成される。

【選択図】図1

Description

上部電極6に正電位(+電位)を印加すると共に、下部電極3に負電位(−電位)または零電位を印加すると、イオン源層5からCu,AgおよびZnのうち少なくとも一種類の金属元素がイオン化して高抵抗層4内を拡散していき、下部電極3側で電子と結合して析出したり、あるいは、高抵抗層4の内部に拡散した状態でとどまる。その結果、高抵抗層4の内部に、Cu,AgおよびZnのうち少なくとも一種類の金属元素を多量に含む電流パスが形成されたり、若しくは、高抵抗層4の内部に、Cu,AgおよびZnのうち少なくとも一種類の金属元素による欠陥が多数形成され、高抵抗層4の抵抗値が低くなる。このとき、イオン源層5の抵抗値は、高抵抗層4の記録前の抵抗値に比べて元々低いので、高抵抗層4の抵抗値が低くなることにより、記憶素子10全体の抵抗値も低くなる。このとき記憶素子10全体の抵抗が書き込み抵抗となる。

次に、上部電極6に負電位(−電位)を印加すると共に、下部電極3に正電位(+電位)または零電位を印加すると、高抵抗層2内に形成されていた電流パス、あるいは不純物準位を構成する、Cu,AgおよびZnのうち少なくとも一種類の金属元素がイオン化して、高抵抗層4内を移動してイオン源層5側に戻る。その結果、高抵抗層4内から、電流パス、若しくは、欠陥が消滅して、高抵抗層4の抵抗値が高くなる。このとき、イオン源層5の抵抗値は元々低いので、高抵抗層4の抵抗値が高くなることにより、記憶素子10全体の抵抗値も高くなる。このときの記憶素子10全体の抵抗が消去抵抗となる。

次に、上記高抵抗層4の効果を示す実施例について説明する。

上述の高抵抗層4の組成の異なる複数の記憶素子10について、室温での書き込み可能な電圧を調べた。その結果を図5に示す。なお、一般的に用いられているメモリの電源電圧は何種類もあるが、ここでは一例として1.8Vを基準とし、この電圧以下で書き込みできるかによって、低電圧動作可能かどうかを判断し、書き込みの可否は、書き込み動作後に抵抗値が20kΩ以下となった場合を、書き込み可能と判断した。図5は、書き込み方向極性に直流電圧を印加したときの、1.8V以下の電圧で書き込み可能な場合を黒ドット、記録が不可の場合を白ドットとし、高抵抗層4の構成材料を三次元(Te,AlおよびCu+Zr)にプロットしたものである。ここで、各元素の比率は酸素を除いたものである。

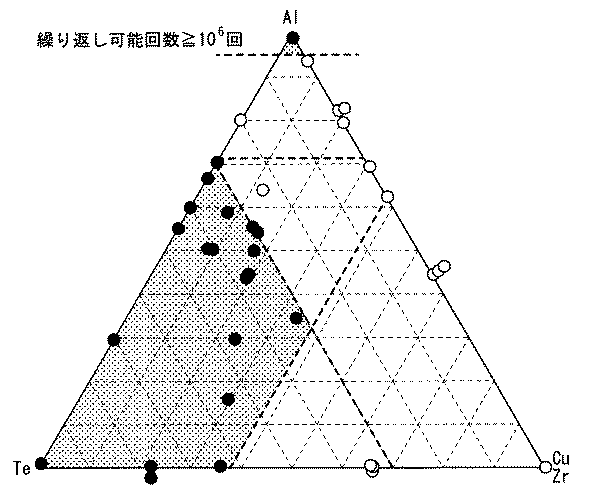

上述の高抵抗層4の組成の異なる複数の記憶素子10について、書き込み/消去の繰り返し動作実験を行った結果を図6に示した。動作条件は、書き込みパルス幅を25nsec,消去パルス幅を1nsec,書き込み電圧を2.2V,書き込み時電流を120μA,消去電圧を1.6V,消去時電流を70μAとした。ここで、書き込み/消去繰り返し動作回数として106 回を基準とし、106 回以上の繰り返し動作回数が可能な場合を黒ドット、不可の場合を白ドットとして三次元にプロットした。なお、各元素の比率は、実験1と同様に酸素を除いたものである。

T1(a,b,c)=(1,0,0)

T2(a,b,c)=(0.3,0.7,0)

T3(a,b,c)=(0.3,0.34,0.36)

T4(a,b,c)=(0.64,0,0.36)

Claims (8)

- 第1電極と第2電極の間に、

少なくともTeを含む酸化物により形成された高抵抗層と、

少なくとも一種類の金属元素と、Te,SおよびSeのうちの少なくとも一種類のカルコゲン元素とを含むイオン源層と

を備えた記憶素子。 - 前記第1電極および前記第2電極への電圧印加によって前記高抵抗層内に前記金属元素を含む電流パスが形成される,あるいは前記金属元素による多数の欠陥が形成されることにより、抵抗値が低下する請求項1に記載の記憶素子。

- 前記高抵抗層はAlを含む請求項1または2に記載の記憶素子。

- 前記高抵抗層において、Teが30〜100原子%に対しAlが0〜70原子%の範囲で含まれる請求項1または2に記載の記憶素子。

- 前記金属元素はCu,AgおよびZnのうちの少なくとも一種類である請求項1に記載の記憶素子。

- 前記高抵抗層において、Te,AlおよびCu+Zrがそれぞれ、30≦Te≦100原子%、0≦Al≦70原子%および0≦Cu+Zr≦36原子%の関係を満たす範囲で含まれる請求項4に記載の記憶素子。

- 前記高抵抗層において、TeとAlとCu+Zrとの組成比(原子%比,酸素は除く)は、それらを頂点とした三角図において、Teをa、Alをb、Cu+Zrをcとすると、数1に示したT1,T2,T3およびT4の各点を結んだ範囲内の値である請求項4に記載の記憶素子。

(数1)

T1(a,b,c)=(1,0,0)

T2(a,b,c)=(0.3,0.7,0)

T3(a,b,c)=(0.3,0.34,0.36)

T4(a,b,c)=(0.64,0,0.36) - 第1電極と第2電極との間にイオン源層および高抵抗層を有する記憶素子と、

前記第1電極に電気的に接続された第1配線と、

前記第2電極に電気的に接続された第2配線と、

前記第1配線に直列挿入され、かつ前記第1電極および前記第2電極の間に印加する電圧を制御するスイッチング素子とを備え、

前記記憶素子を構成する高抵抗層はTeを含む酸化物により形成され、

前記イオン源層は少なくとも一種類の金属元素と、Te,SおよびSeのうち少なくとも一種類のカルコゲン元素とを含む記憶装置。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008224711A JP5397668B2 (ja) | 2008-09-02 | 2008-09-02 | 記憶素子および記憶装置 |

| TW98128383A TWI472018B (zh) | 2008-09-02 | 2009-08-24 | Memory elements and memory devices |

| PCT/JP2009/065054 WO2010026923A1 (ja) | 2008-09-02 | 2009-08-28 | 記憶素子および記憶装置 |

| US13/060,342 US8547735B2 (en) | 2008-09-02 | 2009-08-28 | Memory element and memory device |

| CN200980132968.7A CN102132408B (zh) | 2008-09-02 | 2009-08-28 | 存储元件及存储装置 |

| KR1020117004024A KR101541573B1 (ko) | 2008-09-02 | 2009-08-28 | 기억 소자 및 기억 장치 |

| US14/021,713 US8873281B2 (en) | 2008-09-02 | 2013-09-09 | Memory element and memory device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008224711A JP5397668B2 (ja) | 2008-09-02 | 2008-09-02 | 記憶素子および記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2010062247A true JP2010062247A (ja) | 2010-03-18 |

| JP5397668B2 JP5397668B2 (ja) | 2014-01-22 |

Family

ID=41797091

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008224711A Expired - Fee Related JP5397668B2 (ja) | 2008-09-02 | 2008-09-02 | 記憶素子および記憶装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (2) | US8547735B2 (ja) |

| JP (1) | JP5397668B2 (ja) |

| KR (1) | KR101541573B1 (ja) |

| CN (1) | CN102132408B (ja) |

| TW (1) | TWI472018B (ja) |

| WO (1) | WO2010026923A1 (ja) |

Cited By (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151085A (ja) * | 2010-01-19 | 2011-08-04 | Sony Corp | 記憶素子および記憶装置 |

| JP2012019042A (ja) * | 2010-07-07 | 2012-01-26 | Sony Corp | 記憶素子および記憶装置 |

| EP2495729A2 (en) | 2011-03-04 | 2012-09-05 | Sony Corporation | Memory element and memory device |

| JP2012182172A (ja) * | 2011-02-28 | 2012-09-20 | Sony Corp | 記憶素子および記憶装置 |

| JP2012243820A (ja) * | 2011-05-16 | 2012-12-10 | Toshiba Corp | 不揮発性抵抗変化素子 |

| CN102820426A (zh) * | 2011-06-10 | 2012-12-12 | 索尼公司 | 存储元件和存储装置 |

| US8537594B2 (en) | 2010-09-21 | 2013-09-17 | Kabushiki Kaisha Toshiba | Resistance change element and resistance change memory |

| JP2014022619A (ja) * | 2012-07-20 | 2014-02-03 | Hitachi Ltd | 低電力で動作する半導体記憶装置 |

| JP2016506635A (ja) * | 2013-01-10 | 2016-03-03 | マイクロン テクノロジー, インク. | メモリセルおよびメモリセルの形成方法 |

| WO2020084703A1 (ja) * | 2018-10-24 | 2020-04-30 | 株式会社アルバック | Otsデバイスの製造方法およびotsデバイス |

Families Citing this family (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010101114A1 (ja) * | 2009-03-03 | 2010-09-10 | Tdk株式会社 | 誘電体磁器組成物、誘電体、セラミックス基板及び電子部品、並びに誘電体の製造方法 |

| JP2012064808A (ja) * | 2010-09-16 | 2012-03-29 | Sony Corp | 記憶素子および記憶装置 |

| JP2013016530A (ja) | 2011-06-30 | 2013-01-24 | Sony Corp | 記憶素子およびその製造方法ならびに記憶装置 |

| JP5708930B2 (ja) * | 2011-06-30 | 2015-04-30 | ソニー株式会社 | 記憶素子およびその製造方法ならびに記憶装置 |

| UA117901C2 (uk) | 2011-07-06 | 2018-10-25 | Ґенмаб Б.В. | Спосіб посилення ефекторної функції вихідного поліпептиду, його варіанти та їх застосування |

| AU2013285355A1 (en) | 2012-07-06 | 2015-01-29 | Genmab B.V. | Dimeric protein with triple mutations |

| EP3632462A1 (en) | 2012-07-06 | 2020-04-08 | Genmab B.V. | Dimeric protein with triple mutations |

| US8767448B2 (en) | 2012-11-05 | 2014-07-01 | International Business Machines Corporation | Magnetoresistive random access memory |

| WO2014087784A1 (ja) * | 2012-12-03 | 2014-06-12 | ソニー株式会社 | 記憶素子および記憶装置 |

| JP6308136B2 (ja) * | 2012-12-25 | 2018-04-11 | ソニー株式会社 | 記憶素子および記憶装置 |

| US8934284B2 (en) * | 2013-02-26 | 2015-01-13 | Seagate Technology Llc | Methods and apparatuses using a transfer function to predict resistance shifts and/or noise of resistance-based memory |

| JP6546162B2 (ja) | 2013-07-05 | 2019-07-17 | ゲンマブ エー/エス | ヒト化またはキメラcd3抗体 |

| US10490740B2 (en) * | 2013-08-09 | 2019-11-26 | Sony Semiconductor Solutions Corporation | Non-volatile memory system with reliability enhancement mechanism and method of manufacture thereof |

| DK3169706T3 (da) | 2014-07-11 | 2020-03-09 | Genmab As | Antistoffer, der binder axl |

| US9324937B1 (en) | 2015-03-24 | 2016-04-26 | International Business Machines Corporation | Thermally assisted MRAM including magnetic tunnel junction and vacuum cavity |

| JP6892431B2 (ja) | 2015-07-10 | 2021-06-23 | ゲンマブ エー/エス | 癌治療用のaxl特異的抗体−薬物コンジュゲート |

| CN108091870B (zh) | 2016-11-23 | 2021-02-26 | 清华大学 | 含氢过渡金属氧化物、制备方法及原电池 |

| CN108091913B (zh) | 2016-11-23 | 2020-01-21 | 清华大学 | 固态燃料电池及固态电解质的制备方法 |

| CN108091759B (zh) | 2016-11-23 | 2019-07-09 | 清华大学 | 相变电子器件 |

| CN108091760B (zh) | 2016-11-23 | 2019-11-22 | 清华大学 | 调控含氢过渡金属氧化物相变的方法 |

| JP7330942B2 (ja) | 2017-03-31 | 2023-08-22 | ジェンマブ ホールディング ビー.ブイ. | 二重特異性抗cd37抗体、モノクローナル抗cd37抗体、およびそれらの使用方法 |

| CR20250348A (es) | 2018-03-12 | 2025-09-23 | Genmab As | ANTICUERPOS QUE SE UNEN A 5T4 (Divisional 2020-463) |

| JP2022531894A (ja) | 2019-05-09 | 2022-07-12 | ゲンマブ ビー.ブイ. | がんの処置において使用するための抗dr5抗体の組み合わせの投与レジメン |

| US20220411529A1 (en) | 2019-11-06 | 2022-12-29 | Genmab B.V. | Antibody variant combinations and uses thereof |

| AU2021208532A1 (en) | 2020-01-16 | 2022-07-07 | Genmab A/S | Formulations of CD38 antibodies and uses thereof |

| WO2021155916A1 (en) | 2020-02-04 | 2021-08-12 | BioNTech SE | Treatment involving antigen vaccination and binding agents binding to pd-l1 and cd137 |

| KR20220154757A (ko) | 2020-03-18 | 2022-11-22 | 젠맵 에이/에스 | B7h4에 결합하는 항체 |

| MX2022013797A (es) | 2020-05-08 | 2022-11-30 | Genmab As | Anticuerpos biespecificos contra cd3 y cd20. |

| WO2022029011A1 (en) | 2020-08-06 | 2022-02-10 | BioNTech SE | Binding agents for coronavirus s protein |

| EP4210746A1 (en) | 2020-09-10 | 2023-07-19 | Genmab A/S | Bispecific antibodies against cd3 and cd20 for treating chronic lymphocytic leukemia |

| JP2023541860A (ja) | 2020-09-10 | 2023-10-04 | ジェンマブ エー/エス | びまん性大細胞型b細胞リンパ腫を治療するための併用療法におけるcd3及びcd20に対する二重特異性抗体 |

| MX2023003749A (es) | 2020-10-02 | 2023-04-24 | Genmab As | Anticuerpos capaces de unirse al receptor huerfano 2 similar a tirosina-cinasa receptora (ror2) y anticuerpos biespecificos que se unen a ror2 y al cumulo de diferenciacion 3 (cd3). |

| JP2024512386A (ja) | 2021-03-12 | 2024-03-19 | ジェンマブ エー/エス | 非活性化抗体バリアント |

| AU2022338208A1 (en) | 2021-09-06 | 2024-03-21 | Genmab A/S | Antibodies capable of binding to cd27, variants thereof and uses thereof |

| AU2022361691A1 (en) | 2021-10-08 | 2024-03-28 | Genmab A/S | Antibodies binding to cd30 and cd3 |

| CN114420838A (zh) * | 2021-12-30 | 2022-04-29 | 长江先进存储产业创新中心有限责任公司 | 相变存储器及其制造方法 |

| WO2023174521A1 (en) | 2022-03-15 | 2023-09-21 | Genmab A/S | Binding agents binding to epcam and cd137 |

| WO2023218046A1 (en) | 2022-05-12 | 2023-11-16 | Genmab A/S | Binding agents capable of binding to cd27 in combination therapy |

| CN119365215A (zh) | 2022-05-12 | 2025-01-24 | 健玛保 | 在组合疗法中能够结合cd27的结合剂 |

| AU2024271605A1 (en) | 2023-05-12 | 2025-11-13 | BioNTech SE | Antibodies capable of binding to ox40, variants thereof and uses thereof |

| AR133071A1 (es) | 2023-06-30 | 2025-08-20 | Genmab As | ANTICUERPOS QUE SE UNEN A LA PROTEÍNA DE ACTIVACIÓN DE FIBROBLASTOS a Y AL RECEPTOR DE MUERTE 4 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005197634A (ja) * | 2003-11-28 | 2005-07-21 | Sony Corp | 記憶素子及び記憶装置 |

| JP2006040946A (ja) * | 2004-07-22 | 2006-02-09 | Sony Corp | 記憶素子 |

| JP2009146480A (ja) * | 2007-12-12 | 2009-07-02 | Sony Corp | 記憶装置および情報再記録方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2002536840A (ja) | 1999-02-11 | 2002-10-29 | アリゾナ ボード オブ リージェンツ | プログラマブルマイクロエレクトロニックデバイスおよびその形成およびプログラミング方法 |

| JP4613478B2 (ja) | 2003-05-15 | 2011-01-19 | ソニー株式会社 | 半導体記憶素子及びこれを用いた半導体記憶装置 |

| JP4608875B2 (ja) * | 2003-12-03 | 2011-01-12 | ソニー株式会社 | 記憶装置 |

| JP4398945B2 (ja) * | 2006-02-23 | 2010-01-13 | シャープ株式会社 | 不揮発性半導体記憶装置及びデータ書き換え方法 |

| US7463512B2 (en) * | 2007-02-08 | 2008-12-09 | Macronix International Co., Ltd. | Memory element with reduced-current phase change element |

| JP5050813B2 (ja) * | 2007-11-29 | 2012-10-17 | ソニー株式会社 | メモリセル |

-

2008

- 2008-09-02 JP JP2008224711A patent/JP5397668B2/ja not_active Expired - Fee Related

-

2009

- 2009-08-24 TW TW98128383A patent/TWI472018B/zh not_active IP Right Cessation

- 2009-08-28 CN CN200980132968.7A patent/CN102132408B/zh not_active Expired - Fee Related

- 2009-08-28 WO PCT/JP2009/065054 patent/WO2010026923A1/ja not_active Ceased

- 2009-08-28 US US13/060,342 patent/US8547735B2/en not_active Expired - Fee Related

- 2009-08-28 KR KR1020117004024A patent/KR101541573B1/ko not_active Expired - Fee Related

-

2013

- 2013-09-09 US US14/021,713 patent/US8873281B2/en not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005197634A (ja) * | 2003-11-28 | 2005-07-21 | Sony Corp | 記憶素子及び記憶装置 |

| JP2006040946A (ja) * | 2004-07-22 | 2006-02-09 | Sony Corp | 記憶素子 |

| JP2009146480A (ja) * | 2007-12-12 | 2009-07-02 | Sony Corp | 記憶装置および情報再記録方法 |

Cited By (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2011151085A (ja) * | 2010-01-19 | 2011-08-04 | Sony Corp | 記憶素子および記憶装置 |

| US8847194B2 (en) | 2010-01-19 | 2014-09-30 | Sony Corporation | Memory component including an ion source layer and a resistance change layer, and a memory device using the same |

| JP2012019042A (ja) * | 2010-07-07 | 2012-01-26 | Sony Corp | 記憶素子および記憶装置 |

| US8537594B2 (en) | 2010-09-21 | 2013-09-17 | Kabushiki Kaisha Toshiba | Resistance change element and resistance change memory |

| JP2012182172A (ja) * | 2011-02-28 | 2012-09-20 | Sony Corp | 記憶素子および記憶装置 |

| EP2495729A2 (en) | 2011-03-04 | 2012-09-05 | Sony Corporation | Memory element and memory device |

| CN102683378A (zh) * | 2011-03-04 | 2012-09-19 | 索尼公司 | 存储元件和存储装置 |

| JP2012186316A (ja) * | 2011-03-04 | 2012-09-27 | Sony Corp | 記憶素子および記憶装置 |

| US20120294063A1 (en) * | 2011-03-04 | 2012-11-22 | Sony Corporation | Memory element and memory device |

| KR101913860B1 (ko) * | 2011-03-04 | 2018-10-31 | 소니 주식회사 | 기억 소자 및 기억 장치 |

| US9202560B2 (en) | 2011-03-04 | 2015-12-01 | Sony Corporation | Memory element and memory device with ion source layer and resistance change layer |

| JP2012243820A (ja) * | 2011-05-16 | 2012-12-10 | Toshiba Corp | 不揮発性抵抗変化素子 |

| US8885385B2 (en) | 2011-06-10 | 2014-11-11 | Sony Corporation | Memory element and memory device |

| US9231200B2 (en) | 2011-06-10 | 2016-01-05 | Sony Corporation | Memory element and memory device |

| CN102820426A (zh) * | 2011-06-10 | 2012-12-12 | 索尼公司 | 存储元件和存储装置 |

| JP2014022619A (ja) * | 2012-07-20 | 2014-02-03 | Hitachi Ltd | 低電力で動作する半導体記憶装置 |

| JP2016506635A (ja) * | 2013-01-10 | 2016-03-03 | マイクロン テクノロジー, インク. | メモリセルおよびメモリセルの形成方法 |

| US9508931B2 (en) | 2013-01-10 | 2016-11-29 | Micron Technology, Inc. | Memory cells and methods of forming memory cells |

| US10388871B2 (en) | 2013-01-10 | 2019-08-20 | Micron Technology, Inc. | Memory cells and methods of forming memory cells |

| US10923658B2 (en) | 2013-01-10 | 2021-02-16 | Micron Technology, Inc. | Memory cells and methods of forming memory cells |

| WO2020084703A1 (ja) * | 2018-10-24 | 2020-04-30 | 株式会社アルバック | Otsデバイスの製造方法およびotsデバイス |

| KR20200047443A (ko) * | 2018-10-24 | 2020-05-07 | 가부시키가이샤 아루박 | Ots 디바이스의 제조 방법 및 ots 디바이스 |

| KR102205768B1 (ko) * | 2018-10-24 | 2021-01-20 | 가부시키가이샤 아루박 | Ots 디바이스의 제조 방법 및 ots 디바이스 |

| US11335853B2 (en) | 2018-10-24 | 2022-05-17 | Ulvac, Inc. | Method of manufacturing OTS device, and OTS device |

Also Published As

| Publication number | Publication date |

|---|---|

| TW201011894A (en) | 2010-03-16 |

| TWI472018B (zh) | 2015-02-01 |

| KR101541573B1 (ko) | 2015-08-03 |

| WO2010026923A1 (ja) | 2010-03-11 |

| US20110155987A1 (en) | 2011-06-30 |

| CN102132408B (zh) | 2014-03-12 |

| US8873281B2 (en) | 2014-10-28 |

| US8547735B2 (en) | 2013-10-01 |

| US20140008600A1 (en) | 2014-01-09 |

| JP5397668B2 (ja) | 2014-01-22 |

| KR20110049814A (ko) | 2011-05-12 |

| CN102132408A (zh) | 2011-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5397668B2 (ja) | 記憶素子および記憶装置 | |

| JP4792714B2 (ja) | 記憶素子及び記憶装置 | |

| US7772029B2 (en) | Memory element and memory device comprising memory layer positioned between first and second electrodes | |

| JP4848633B2 (ja) | 記憶素子及び記憶装置 | |

| EP2178122B1 (en) | Memory element and memory device | |

| JP4815804B2 (ja) | 記憶素子及び記憶装置 | |

| KR101058856B1 (ko) | 기억소자 및 이를 이용한 기억장치 | |

| JP4396621B2 (ja) | 記憶素子及び記憶装置 | |

| JP5423941B2 (ja) | 記憶素子およびその製造方法、並びに記憶装置 | |

| JP4465969B2 (ja) | 半導体記憶素子及びこれを用いた半導体記憶装置 | |

| JP5434967B2 (ja) | 記憶素子及び記憶装置 | |

| JP2010278275A (ja) | 半導体記憶装置 | |

| JP4742971B2 (ja) | 記憶素子及び記憶装置 | |

| JP2007157941A (ja) | 記憶素子及び記憶装置 | |

| JP6162931B2 (ja) | 記憶素子および記憶装置 | |

| JP4760606B2 (ja) | 記憶素子及び記憶装置 | |

| JP5423940B2 (ja) | 記憶素子の製造方法および記憶装置の製造方法 | |

| JP4742887B2 (ja) | 記憶素子、記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110810 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130509 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130701 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130717 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130909 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130926 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131009 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5397668 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |