JP2008016732A - 発光ダイオード駆動回路 - Google Patents

発光ダイオード駆動回路 Download PDFInfo

- Publication number

- JP2008016732A JP2008016732A JP2006188443A JP2006188443A JP2008016732A JP 2008016732 A JP2008016732 A JP 2008016732A JP 2006188443 A JP2006188443 A JP 2006188443A JP 2006188443 A JP2006188443 A JP 2006188443A JP 2008016732 A JP2008016732 A JP 2008016732A

- Authority

- JP

- Japan

- Prior art keywords

- current

- emitting diode

- light emitting

- circuit

- current mirror

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H05—ELECTRIC TECHNIQUES NOT OTHERWISE PROVIDED FOR

- H05B—ELECTRIC HEATING; ELECTRIC LIGHT SOURCES NOT OTHERWISE PROVIDED FOR; CIRCUIT ARRANGEMENTS FOR ELECTRIC LIGHT SOURCES, IN GENERAL

- H05B45/00—Circuit arrangements for operating light-emitting diodes [LED]

- H05B45/40—Details of LED load circuits

- H05B45/44—Details of LED load circuits with an active control inside an LED matrix

- H05B45/46—Details of LED load circuits with an active control inside an LED matrix having LEDs disposed in parallel lines

Landscapes

- Led Devices (AREA)

Abstract

【課題】本発明は発光ダイオードの発光輝度の変動を抑えることができる発光ダイオード駆動回路を提供することを目的とする。

【解決手段】基準電流部33は、基準電流が抵抗を流れることで発生する電圧が一定の基準電圧と同一となるよう基準電流を制御する演算増幅器30と、基準電流に基づく第1の電流を生成する第1のカレントミラー回路を有し、各チャネルの電流出力部は、基準電流部の一部と共に構成され、第1の電流に基づく第2の電流を生成する第2のカレントミラー回路と、第2の電流を供給され、複数系統のスイッチのうちオンとなったスイッチに対応して第2の電流に比例する電流を生成する第3のカレントミラー回路を有し、第1、第2、第3のカレントミラー回路それぞれは、カスケード接続された2段のカレントミラー回路である。

【選択図】図2

【解決手段】基準電流部33は、基準電流が抵抗を流れることで発生する電圧が一定の基準電圧と同一となるよう基準電流を制御する演算増幅器30と、基準電流に基づく第1の電流を生成する第1のカレントミラー回路を有し、各チャネルの電流出力部は、基準電流部の一部と共に構成され、第1の電流に基づく第2の電流を生成する第2のカレントミラー回路と、第2の電流を供給され、複数系統のスイッチのうちオンとなったスイッチに対応して第2の電流に比例する電流を生成する第3のカレントミラー回路を有し、第1、第2、第3のカレントミラー回路それぞれは、カスケード接続された2段のカレントミラー回路である。

【選択図】図2

Description

本発明は発光ダイオード駆動回路に関し、配列された複数の発光ダイオードそれぞれを駆動する発光ダイオード駆動回路に関する。

プリンタ等において感光体を感光させる手段として、発光ダイオード(以下、「LED」という)をリニアに配列したLEDアレイを用いたものがある。このようなLEDアレイの各LEDを駆動する駆動回路としては、例えば特許文献1,2等に記載されているものがある。

図9は、従来の発光ダイオード駆動回路の一例の回路構成図を示す。この駆動回路は半導体集積回路化されている。

同図中、演算増幅器10の反転入力端子には基準電圧源11より基準電圧Vrefが印加されている。演算増幅器10の出力端子はpチャネルMOS電界効果トランジスタ(以下、単に「MOSトランジスタ」という)M1のゲートに接続されると共に、pチャネルMOSトランジスタM2のゲートに接続されている。MOSトランジスタM1,M2のソースは電源Vdd1に接続されている。MOSトランジスタM1,M2はカレントミラー回路を構成している。

MOSトランジスタM1のドレインは演算増幅器10の非反転入力端子に接続されると共に、抵抗R1を介して接地されている。MOSトランジスタM2のドレインはnチャネルMOSトランジスタM4のドレインに共通接続されている。

MOSトランジスタM4のドレインはnチャネルMOSトランジスタM4,M5のゲートに共通接続され、MOSトランジスタM4,M5のソースは接地されており、MOSトランジスタM4,M5はカレントミラー回路を構成している。

MOSトランジスタM5のドレインはpチャネルMOSトランジスタM6のゲートとドレインに接続されている。MOSトランジスタM6のゲートはアナログスイッチ等のスイッチ15,16それぞれを介してpチャネルMOSトランジスタM7,M8のゲートに接続されている。MOSトランジスタM6,M7,M8のソースは電源Vdd2に接続され、MOSトランジスタM7,M8のドレインはLED(発光ダイオード)18のアノードに接続され、LED18のカソードは接地されている。

スイッチ15,16は、端子17a,17bそれぞれから供給される階調制御用のスイッチ制御信号に応じてオン/オフを切り換える。MOSトランジスタM7,M8はスイッチ15,16がオンのときにMOSトランジスタM6とカレントミラー回路を構成する。スイッチ15はLED18を発光させるタイミングでオンとなり、スイッチ16はLED18の発光輝度を増大させて階調表現を行う場合にオンとなる。

特許第3296882号公報

特許第2516236号公報

従来の発光ダイオード駆動回路では、カレントミラー回路を構成しているMOSトランジスタM1のドレインであるA点の電位と、MOSトランジスタM2のドレインであるB点の電位が同電位ではないために両トランジスタのドレイン・ソース間電圧が異なり、また、両トランジスタの導通電圧Vtのばらつきは10%程度となるため、MOSトランジスタM1のドレイン電流とMOSトランジスタM2のドレイン電流が両トランジスタのゲート面積の比にならず、カレントミラーの精度が悪いという問題があった。

また、MOSトランジスタM4とM5やMOSトランジスタM6とM7,M8が構成する他のカレントミラー回路についても同様にカレントミラーの精度が悪いという問題があった。このため、基準電流Irefが一定であってもLED18に流れる電流が変動し、LED18の発光輝度が変動するという問題があった。

本発明は、上記の点に鑑みなされたものであり、発光ダイオードの発光輝度の変動を抑えることができる発光ダイオード駆動回路を提供することを目的とする。

本発明の発光ダイオード駆動回路は、基準電流を生成する基準電流部と、複数系統のスイッチをオン/オフ制御して前記基準電流に比例した複数系統の駆動電流を生成し発光ダイオードに供給する複数チャネル分の電流出力部からなる発光ダイオード駆動回路であって、

前記基準電流部は、前記基準電流が抵抗を流れることで発生する電圧が一定の基準電圧と同一となるよう前記基準電流を制御する演算増幅器と、

前記基準電流に基づく第1の電流を生成する第1のカレントミラー回路を有し、

各チャネルの前記電流出力部は、前記基準電流部の一部と共に構成され、前記第1の電流に基づく第2の電流を生成する第2のカレントミラー回路と、

前記第2の電流を供給され、前記複数系統のスイッチのうちオンとなったスイッチに対応して前記第2の電流に比例する電流を生成する第3のカレントミラー回路を有し、

前記第1、第2、第3のカレントミラー回路それぞれは、カスケード接続された2段のカレントミラー回路であることにより、発光ダイオードの発光輝度の変動を抑えることができる。

前記基準電流部は、前記基準電流が抵抗を流れることで発生する電圧が一定の基準電圧と同一となるよう前記基準電流を制御する演算増幅器と、

前記基準電流に基づく第1の電流を生成する第1のカレントミラー回路を有し、

各チャネルの前記電流出力部は、前記基準電流部の一部と共に構成され、前記第1の電流に基づく第2の電流を生成する第2のカレントミラー回路と、

前記第2の電流を供給され、前記複数系統のスイッチのうちオンとなったスイッチに対応して前記第2の電流に比例する電流を生成する第3のカレントミラー回路を有し、

前記第1、第2、第3のカレントミラー回路それぞれは、カスケード接続された2段のカレントミラー回路であることにより、発光ダイオードの発光輝度の変動を抑えることができる。

前記発光ダイオード駆動回路において、

前記第1及び第3のカレントミラー回路を構成し高電圧側の電源に接続される各トランジスタと前記高電圧側の電源との間に抵抗を設けることができる。

前記第1及び第3のカレントミラー回路を構成し高電圧側の電源に接続される各トランジスタと前記高電圧側の電源との間に抵抗を設けることができる。

前記発光ダイオード駆動回路において、

前記第2のカレントミラー回路を構成し低電圧側の電源に接続される各トランジスタと前記低電圧側の電源との間に抵抗を設けることができる。

前記第2のカレントミラー回路を構成し低電圧側の電源に接続される各トランジスタと前記低電圧側の電源との間に抵抗を設けることができる。

また、前記発光ダイオード駆動回路において、

前記複数チャネル分の電流出力部を一方向に並べて配置し、前記複数チャネル分の電流出力部の上に電源配線を前記一方向に延在させて配置し、

前記電源配線と各チャネルの前記電流出力部を接続する各チャネルのコンタクト領域の一部を開けて囲むよう前記電源配線を切り欠いたスリットを各チャネルに設けることができる。

前記複数チャネル分の電流出力部を一方向に並べて配置し、前記複数チャネル分の電流出力部の上に電源配線を前記一方向に延在させて配置し、

前記電源配線と各チャネルの前記電流出力部を接続する各チャネルのコンタクト領域の一部を開けて囲むよう前記電源配線を切り欠いたスリットを各チャネルに設けることができる。

本発明によれば、発光ダイオードの発光輝度の変動を抑えることができる。

以下、図面に基づいて本発明の実施形態について説明する。

<LEDアレイ駆動回路の構成>

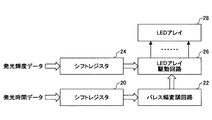

図1は、本発明の発光ダイオード駆動回路を用いたLEDアレイ装置の一実施形態のブロック構成図を示す。このLEDアレイ装置は例えば48チャネル構成である。

図1は、本発明の発光ダイオード駆動回路を用いたLEDアレイ装置の一実施形態のブロック構成図を示す。このLEDアレイ装置は例えば48チャネル構成である。

同図中、シフトレジスタ20には1チャネルについて例えば6ビットの発光時間データが48チャネル分時系列で供給され、シフトレジスタ20で順次シフトされてラッチされたのち、パルス幅変調回路22に供給される。パルス幅変調回路22は、チャネル毎に発光時間データで指示されるパルス幅の発光パルスを生成し、48チャネル分の発光パルスをLEDアレイ駆動回路26に供給する。

シフトレジスタ24には1チャネルについて例えば6ビットの発光輝度データが48チャネル分時系列で供給され、シフトレジスタ24で順次シフトされてラッチされたのち、LEDアレイ駆動回路26に供給される。LEDアレイ駆動回路26は、チャネル毎に発光輝度データをデコードしてn系統のスイッチ制御信号を生成し、チャネル毎に発光パルスでオンさせるMOSトランジスタを上記n系統のスイッチ制御信号によって決定する。LEDアレイ駆動回路26はLEDアレイ28を構成する48チャネルのLEDをチャネル単位に駆動する。

<発光ダイオード駆動回路の構成>

図2は、本発明の発光ダイオード駆動回路の一実施形態の回路構成図を示す。この駆動回路は半導体集積回路化されている。

図2は、本発明の発光ダイオード駆動回路の一実施形態の回路構成図を示す。この駆動回路は半導体集積回路化されている。

同図中、演算増幅器30の反転入力端子には基準電圧源回路31より基準電圧Vrefが印加されている。演算増幅器30の出力端子はpチャネルMOSトランジスタM11,M12それぞれのゲートに接続されている。MOSトランジスタM11,M12それぞれのソースは抵抗R11,R12それぞれを介して電源Vdd1に接続されてカレントミラー回路を構成している。MOSトランジスタM11,M12それぞれのドレインはpチャネルMOSトランジスタM13,M14それぞれのソースに接続されている。

MOSトランジスタM13,M14のゲートはMOSトランジスタM13のドレインに共通接続されてカレントミラー回路を構成しており、MOSトランジスタM13のドレインは演算増幅器30の非反転入力端子に接続されると共に、抵抗R13の一端に接続されている。抵抗R13の他端は接地されている。

ここで、MOSトランジスタM11,M12にカスケード接続されたMOSトランジスタM13,M14は能動領域で動作してゲート・ソース間電圧Vgsは略同一となるため、カレントミラー回路を構成しているMOSトランジスタM11のドレインであるA点の電位と、MOSトランジスタM12のドレインであるB点の電位は略同電位となる。このために、MOSトランジスタM11,M12のドレイン・ソース間電圧Vdsは略同一となる。

また、MOSトランジスタM11,M12のソースに接続された抵抗R11,R12の抵抗値は、MOSトランジスタM11,M12の導通抵抗に比して例えば100倍程度に選定されている。このため、MOSトランジスタM11,M12の導通電圧Vtのばらつきは、抵抗R11,R12がないときに対して1%未満に圧縮され、導通電圧Vtのばらつきは無視できる。

ここで、MOSトランジスタM11,M12のドレイン電流Idは(1)式で表される。なお、λ,μは比例定数、Wはゲート幅、Lはゲート長である。

Id=(1+λ・Vds)×(1/2)×μ×(W/L)×(Vgs−Vt)2 …(1)

(1)式において、MOSトランジスタM11,M12のVdsは略同一であり、Vtのばらつきは無視できるために、MOSトランジスタM11,M12のドレイン電流は両トランジスタのゲート面積の比となり、カレントミラーの精度が向上する。

(1)式において、MOSトランジスタM11,M12のVdsは略同一であり、Vtのばらつきは無視できるために、MOSトランジスタM11,M12のドレイン電流は両トランジスタのゲート面積の比となり、カレントミラーの精度が向上する。

MOSトランジスタM14のドレインはnチャネルMOSトランジスタM15のドレインに接続されている。MOSトランジスタM15のゲートはnチャネルMOSトランジスタM16のゲートと接続されてカレントミラー回路を構成している。

MOSトランジスタM15,M16それぞれのソースはnチャネルMOSトランジスタM17,M18それぞれのドレインに接続されている。MOSトランジスタM17,M18のゲートはMOSトランジスタM15のドレインに共通接続されてカレントミラー回路を構成し、MOSトランジスタM17,M18のソースは接地されている。

MOSトランジスタM15〜M18はカレントミラー回路がカスケード接続された構成となることにより、MOSトランジスタM11〜M14と同様にして、MOSトランジスタM15,M16のソース電位が略同一となり、ゲート面積が同一の場合MOSトランジスタM15,M16のドレイン電流は略同一となる。なお、MOSトランジスタM15,M16のゲートには電圧源33より定電圧Vaが印加されることでMOSトランジスタM17,M18のドレイン電位はVa−Vgs1(Vgs1はnチャネルMOSトランジスタのゲート・ドレイン間電圧)となる。

上記の演算増幅器30,基準電圧源回路31,MOSトランジスタM11〜M15及びM17は基準電流部32を構成しており、MOSトランジスタM13のドレインに基準電流Irefを流す。また、カレントミラー回路によってMOSトランジスタM16のドレインに基準電流Irefに比例した電流が流れる。

MOSトランジスタM16のドレインはpチャネルMOSトランジスタM22のドレインに接続されている。MOSトランジスタM22のソースはpチャネルMOSトランジスタM21のドレインに接続されている。MOSトランジスタM21のソースは抵抗R15を介して電源Vdd2に接続されている。

MOSトランジスタM21のゲートはMOSトランジスタM22のドレインに接続されると共に、アナログスイッチ等のスイッチ36,38,40それぞれを介してpチャネルMOSトランジスタM23,M25,M27のゲートに接続されている。スイッチ36,38,40がオンするとMOSトランジスタM23,M25,M27のゲート電位をMOSトランジスタM21のゲート電圧と同一にしてMOSトランジスタM23,M25,M27をオンし、スイッチ36,38,40がオフするとMOSトランジスタM23,M25,M27のゲート電位を電源電圧Vdd2としてMOSトランジスタM23,M25,M27をオフする。

MOSトランジスタM23,M25,M27それぞれのソースは抵抗R16,R17,R18それぞれを介して電源Vdd2に接続されており、MOSトランジスタM23,M25,M27はスイッチ36,38,40がオンのときにMOSトランジスタM21とカレントミラー回路を構成する。

MOSトランジスタM22のゲートはpチャネルMOSトランジスタM24,M26,M28のゲートに接続されている。MOSトランジスタM23,M25,M27それぞれのドレインはMOSトランジスタM24,M26,M28のソースに接続されており、MOSトランジスタM22,M24,M26,M28はカレントミラー回路を構成している。

MOSトランジスタM21〜M28はカレントミラー回路がカスケード接続された構成となることにより、MOSトランジスタM11〜M14と同様にして、MOSトランジスタM21,M23,M25,M27のドレイン電位が略同一となり、ゲート面積が同一の場合MOSトランジスタM22,M24,M26,M28のドレイン電流は略同一となる。ここでは、階調表現を行うために、例えばMOSトランジスタM21,M22のゲート面積に対して、MOSトランジスタM23,M24のゲート面積は6倍、MOSトランジスタM25,M26のゲート面積は3倍、MOSトランジスタM27,M28のゲート面積は2倍というように、ゲート面積をそれぞれ異ならせている。

なお、MOSトランジスタM22,M24,M26,M28のゲートには電圧源35より定電圧Vbが印加されて、MOSトランジスタM22,M24,M26,M28のソース電位はVb+Vgs2(Vgs2はpチャネルMOSトランジスタのゲート・ドレイン間電圧)とされている。

スイッチ36,38,40それぞれは端子37,39,41それぞれから供給されるn(ここではn=3)系統のスイッチ制御信号に応じてオン/オフを切り換える。なお、nは3に限らない。MOSトランジスタM24,M26,M28のドレインはLED451のアノードに接続され、LED451のカソードは接地されている。

ここで、スイッチ36,38,40がオフのときMOSトランジスタM23,M25,M27はオフしLED451に電流は流れない。スイッチ36がオンするとMOSトランジスタM23のドレイン電流がLED451に流れ、スイッチ36,38がオンするとMOSトランジスタM23,M25のドレイン電流の和がLED451に流れ、スイッチ36,38,40がオンするとMOSトランジスタM23,M25,M27のドレイン電流の和がLED451に流れ、LED451は流れる電流が大きくなるほど発光輝度が大となる。

上記のスイッチ36,38,40,MOSトランジスタM16,M18〜M28が1チャネル分の電流出力部441を構成している。LED451はLEDアレイ28の一部である。

m(=48)チャネル分の電流出力部441〜44mそれぞれは同一構成であり、mチャネル分のLED451〜45mそれぞれを駆動する。

このように、各カレントミラー回路のカレントミラーの精度を向上できるため、各チャネルのLED451〜45mの発光輝度の変動を抑えることができる。

<発光ダイオード駆動回路の変形例>

図3は、本発明の発光ダイオード駆動回路の一実施形態の変形例の回路構成図を示す。同図中、図2と異なる部分について説明する。図3では、MOSトランジスタM17,M18のソースは抵抗Ra,Rbを介して接地されている。なお、電源Vdd1,Vdd2を高電圧側の電源とすれば、接地は低電圧側の電源と言える。

図3は、本発明の発光ダイオード駆動回路の一実施形態の変形例の回路構成図を示す。同図中、図2と異なる部分について説明する。図3では、MOSトランジスタM17,M18のソースは抵抗Ra,Rbを介して接地されている。なお、電源Vdd1,Vdd2を高電圧側の電源とすれば、接地は低電圧側の電源と言える。

この場合、MOSトランジスタM17,M18にカスケード接続されたMOSトランジスタM15,M16は能動領域で動作してゲート・ソース間電圧Vgsは略同一となるため、カレントミラー回路を構成しているMOSトランジスタM17のドレインであるC点の電位と、MOSトランジスタM18のドレインであるD点の電位は略同電位となる。このために、MOSトランジスタM11,M12のドレイン・ソース間電圧Vdsは略同一となる。

また、MOSトランジスタM17,M18のソースに接続された抵抗Ra,Rbの抵抗値は、MOSトランジスタM17,M18の導通抵抗に比して例えば100倍程度に選定されているため、MOSトランジスタM17,M18の導通電圧Vtのばらつきは、抵抗Ra,Rbがないときに対して1%未満に圧縮され、導通電圧Vtのばらつきは無視できる。これによって、MOSトランジスタM17,M18のドレイン電流は両トランジスタのゲート面積の比となり、カレントミラーの精度が向上する。

更に、この変形例では、半導体集積回路の接地ラインを構成するアルミニューム配線の影響を抑えることができる。

図2の構成において、電流出力部44mが基準電流部32から最も離れて配置され、電流出力部44mの近傍に半導体集積回路の接地端子が設けられている場合を考えると、接地ラインのアルミニューム配線によって数Ωの抵抗値が生じる。このため、電流出力部44mのMOSトランジスタM18のソースが直接接地されるのに対し、基準電流部32のMOSトランジスタM17のソースは数Ωの抵抗値を介して接地された状態となり、MOSトランジスタM17,M18のゲート面積が同一であったとしても、電流出力部44mのMOSトランジスタM18のドレイン電流は基準電流部32のMOSトランジスタM17のドレイン電流と異なったものとなる。

これに対し、図3の構成において、抵抗Ra,Rbの抵抗値が共に数100Ωであるとすると、電流出力部44mと基準電流部32の間の接地ラインのアルミニューム配線によって数Ωの抵抗値が生じたとしても、数100Ωの抵抗Raが数Ω増加しただけであり、この程度の抵抗値の変化は無視することができ、電流出力部44mのMOSトランジスタM18のドレイン電流は基準電流部32のMOSトランジスタM17のドレイン電流と同一とみなすことができる。すなわち、上記接地ラインのアルミニューム配線の影響を十分に抑えることができる。

<電源配線>

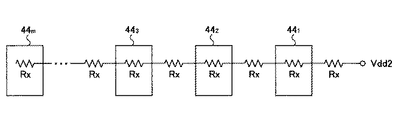

図4は、本発明の発光ダイオード駆動回路における電流出力部441〜44m部分の半導体集積回路の一例の平面図を示す。同図中、電流出力部441〜44mはX方向に一列に並べて配置されている。梨地で示す電源配線50は電流出力部441〜44mの上をX方向に延在しており、電源Vdd2を電流出力部441〜44mに供給する。

図4は、本発明の発光ダイオード駆動回路における電流出力部441〜44m部分の半導体集積回路の一例の平面図を示す。同図中、電流出力部441〜44mはX方向に一列に並べて配置されている。梨地で示す電源配線50は電流出力部441〜44mの上をX方向に延在しており、電源Vdd2を電流出力部441〜44mに供給する。

電流出力部441〜44mそれぞれには、ハッチングで示すコンタクト領域511〜51mが設けられている。コンタクト領域511〜51mには電流出力部441〜44mそれぞれの抵抗R15〜R18を電源Vdd2に接続するためのコンタクトが設けられる。図4の等価回路は図5に示すようになる。図5において、Rxは電源配線50の配線抵抗である。

この場合、電流出力部441〜44mのうちある電流出力部ではスイッチ36,38,40の全てがオンとなり、また、他の電流出力部ではスイッチ36,38,40のいずれかがオンとなり、各電流出力部441〜44mでスイッチ36,38,40のオンとなるパターンがそれぞれ異なる。このため、電流出力部441〜44mそれぞれで発生する電圧降下が異なり、電流出力部441〜44mそれぞれが駆動するLED451〜45mの駆動電流が安定しない、つまり、LED451〜45mの発光輝度が安定しない。

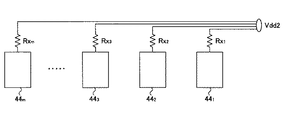

なお、図6に示すように、電流出力部441〜44mそれぞれに個別の電源配線521〜52mから電源Vdd2を供給することも考えられるが、個別の電源配線521〜52mを設ける領域が大幅に増加するため、実現性は極めて低い。図6において、Rx1〜Rxmは電源配線50の配線抵抗である。

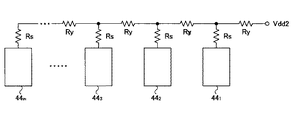

図7は、本発明の発光ダイオード駆動回路における電流出力部441〜44m部分の半導体集積回路の一実施形態の平面図を示す。同図中、電流出力部441〜44mはX方向に一列に並べて配置されている。梨地で示す電源配線50は電流出力部441〜44mの上にX方向に延在して配置されており、電源Vdd2を電流出力部441〜44mに供給する。

電流出力部441〜44mそれぞれには、ハッチングで示すコンタクト領域511〜51mが設けられている。コンタクト領域511〜51mには電流出力部441〜44mそれぞれの抵抗R15〜R18を電源Vdd2に接続するためのコンタクトが設けられる。なお、コンタクト領域511〜51mの上部は電源配線50が設けられている。

更に、コンタクト領域511〜51mそれぞれの周囲には、電源配線50を切り欠いたスリット部551〜55mが設けられ、コンタクト領域511〜51mはスリット部551〜55mによって一部(電流流入部)を開けて囲まれている。スリット部551〜55mはコンタクト領域511〜51mに流れ込む電流を制限するために設けられている。図7の等価回路は図8に示すようになる。図8において、Ryは電源配線50の配線抵抗、Rsはスリット部551〜55mによる等価的な制限抵抗である。なお、図7でスリット部551〜55mはコンタクト領域511〜51mの左側を開けて囲んでいるが、コンタクト領域511〜51mの右側または上側または下側を開けて囲む形状であっても良い。

このスリット部551〜55mを設けることにより、各電流出力部441〜44mでスイッチ36,38,40のオンとなるパターンがそれぞれ異なっても、電流出力部441〜44mに流れ込む電流が一定量以下に制限されるため、電流出力部441〜44mそれぞれで発生する電圧降下が制限される。

これにより、電流出力部441〜44mそれぞれにおける電源電圧Vdd2を安定化することができる。基準電流部32の電源電圧Vdd1に対する電流出力部441〜44mそれぞれの電源電圧Vdd2が安定すると、電流出力部441〜44mそれぞれが駆動するLED451〜45mそれぞれの駆動電流が安定し、LED451〜45mの発光輝度が安定する。

なお、スリット部551〜55mは、コンタクト領域511〜51mの一部(電流流入部)を開けて囲むものであるが、どの部分を開けるかは自由に選定できる。

なお、MOSトランジスタM11〜M14が請求項記載の第1のカレントミラー回路に相当し、MOSトランジスタM14のドレイン電流が第1の電流に相当し、MOSトランジスタM15〜M18が第2のカレントミラー回路に相当し、MOSトランジスタM16のドレイン電流が第2の電流に相当し、MOSトランジスタM21〜M28が第3のカレントミラー回路に相当する。

30 演算増幅器

31 基準電圧源回路

32 基準電流部

33,35 電圧源

36,38,40 スイッチ

441〜44m 電流出力部

451〜45m LED

50 電源配線

511〜51m コンタクト領域

551〜55m スリット部

M11〜M28 MOSトランジスタ

R11〜R18,Ra,Rb 抵抗

Vdd1,Vdd2 電源

31 基準電圧源回路

32 基準電流部

33,35 電圧源

36,38,40 スイッチ

441〜44m 電流出力部

451〜45m LED

50 電源配線

511〜51m コンタクト領域

551〜55m スリット部

M11〜M28 MOSトランジスタ

R11〜R18,Ra,Rb 抵抗

Vdd1,Vdd2 電源

Claims (4)

- 基準電流を生成する基準電流部と、複数系統のスイッチをオン/オフ制御して前記基準電流に比例した複数系統の駆動電流を生成し発光ダイオードに供給する複数チャネル分の電流出力部からなる発光ダイオード駆動回路であって、

前記基準電流部は、前記基準電流が抵抗を流れることで発生する電圧が一定の基準電圧と同一となるよう前記基準電流を制御する演算増幅器と、

前記基準電流に基づく第1の電流を生成する第1のカレントミラー回路を有し、

各チャネルの前記電流出力部は、前記基準電流部の一部と共に構成され、前記第1の電流に基づく第2の電流を生成する第2のカレントミラー回路と、

前記第2の電流を供給され、前記複数系統のスイッチのうちオンとなったスイッチに対応して前記第2の電流に比例する電流を生成する第3のカレントミラー回路を有し、

前記第1、第2、第3のカレントミラー回路それぞれは、カスケード接続された2段のカレントミラー回路であることを特徴とする発光ダイオード駆動回路。 - 請求項1記載の発光ダイオード駆動回路において、

前記第1及び第3のカレントミラー回路を構成し高電圧側の電源に接続される各トランジスタと前記高電圧側の電源との間に抵抗を設けたことを特徴とする発光ダイオード駆動回路。 - 請求項1または2記載の発光ダイオード駆動回路において、

前記第2のカレントミラー回路を構成し低電圧側の電源に接続される各トランジスタと前記低電圧側の電源との間に抵抗を設けたことを特徴とする発光ダイオード駆動回路。 - 請求項1乃至3のいずれか1項記載の発光ダイオード駆動回路において、

前記複数チャネル分の電流出力部を一方向に並べて配置し、前記複数チャネル分の電流出力部の上に電源配線を前記一方向に延在させて配置し、

前記電源配線と各チャネルの前記電流出力部を接続する各チャネルのコンタクト領域の一部を開けて囲むよう前記電源配線を切り欠いたスリットを各チャネルに設けたことを特徴とする発光ダイオード駆動回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006188443A JP2008016732A (ja) | 2006-07-07 | 2006-07-07 | 発光ダイオード駆動回路 |

| PCT/JP2007/062137 WO2008004426A1 (fr) | 2006-07-07 | 2007-06-15 | Circuit d'attaque de diode électroluminescente |

| CN2007800255352A CN101485003B (zh) | 2006-07-07 | 2007-06-15 | 发光二极管驱动电路 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006188443A JP2008016732A (ja) | 2006-07-07 | 2006-07-07 | 発光ダイオード駆動回路 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2008016732A true JP2008016732A (ja) | 2008-01-24 |

Family

ID=38894397

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006188443A Pending JP2008016732A (ja) | 2006-07-07 | 2006-07-07 | 発光ダイオード駆動回路 |

Country Status (3)

| Country | Link |

|---|---|

| JP (1) | JP2008016732A (ja) |

| CN (1) | CN101485003B (ja) |

| WO (1) | WO2008004426A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100986098B1 (ko) | 2008-04-18 | 2010-10-07 | 창원대학교 산학협력단 | 병렬 백라이트 led 드라이버 |

Families Citing this family (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101694963B (zh) * | 2009-09-22 | 2013-09-18 | 美芯晟科技(北京)有限公司 | 高精度低电压的电压电流转换电路 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06328782A (ja) * | 1993-05-26 | 1994-11-29 | Ricoh Co Ltd | 輝度制御回路装置 |

| JPH11251668A (ja) * | 1998-02-27 | 1999-09-17 | Sony Corp | 発光素子の駆動回路 |

| JP2001308272A (ja) * | 2000-04-19 | 2001-11-02 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| JP2005183657A (ja) * | 2003-12-19 | 2005-07-07 | Canon Inc | 光源駆動回路 |

| JP2006054362A (ja) * | 2004-08-13 | 2006-02-23 | Sanyo Electric Co Ltd | Led制御回路 |

-

2006

- 2006-07-07 JP JP2006188443A patent/JP2008016732A/ja active Pending

-

2007

- 2007-06-15 CN CN2007800255352A patent/CN101485003B/zh not_active Expired - Fee Related

- 2007-06-15 WO PCT/JP2007/062137 patent/WO2008004426A1/ja active Application Filing

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH06328782A (ja) * | 1993-05-26 | 1994-11-29 | Ricoh Co Ltd | 輝度制御回路装置 |

| JPH11251668A (ja) * | 1998-02-27 | 1999-09-17 | Sony Corp | 発光素子の駆動回路 |

| JP2001308272A (ja) * | 2000-04-19 | 2001-11-02 | Matsushita Electric Ind Co Ltd | 半導体集積回路装置 |

| JP2005183657A (ja) * | 2003-12-19 | 2005-07-07 | Canon Inc | 光源駆動回路 |

| JP2006054362A (ja) * | 2004-08-13 | 2006-02-23 | Sanyo Electric Co Ltd | Led制御回路 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100986098B1 (ko) | 2008-04-18 | 2010-10-07 | 창원대학교 산학협력단 | 병렬 백라이트 led 드라이버 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2008004426A1 (fr) | 2008-01-10 |

| CN101485003A (zh) | 2009-07-15 |

| CN101485003B (zh) | 2011-07-20 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6952083B2 (en) | Drive circuit for driving a current-driven display unit | |

| US7839097B2 (en) | System and method for wide-range high-accuracy-low-dropout current regulation | |

| JP3887229B2 (ja) | 電流駆動型表示装置の駆動回路 | |

| CN111065187B (zh) | 电流调节器 | |

| US7436248B2 (en) | Circuit for generating identical output currents | |

| JP2007317933A (ja) | 発光ダイオード駆動回路 | |

| WO2007148581A1 (ja) | 発光ダイオード駆動回路 | |

| JP6514946B2 (ja) | 電流ドライバ回路 | |

| JP2008016732A (ja) | 発光ダイオード駆動回路 | |

| JP4792933B2 (ja) | 電流制御回路およびled駆動用半導体集積回路 | |

| CN101473458B (zh) | 发光二极管驱动电路 | |

| US20130093339A1 (en) | Driving circuits for light emitting elements | |

| JP2010074379A (ja) | ドライバ回路、及び電子回路装置 | |

| JP5040185B2 (ja) | 発光ダイオード駆動回路 | |

| JP2008218910A (ja) | 発光ダイオード駆動回路 | |

| JP2005135366A (ja) | カレントミラー回路 | |

| JP2008218911A (ja) | 発光ダイオード駆動回路 | |

| CN115148162B (zh) | 驱动电路、背光电路及显示面板 | |

| JP2006216588A (ja) | 発光素子駆動装置 | |

| JP4983319B2 (ja) | 発光ダイオード駆動回路 | |

| JP2019121969A (ja) | レベルシフト装置、及びic装置 | |

| JPWO2023026919A5 (ja) | ||

| KR100657152B1 (ko) | 수동 매트릭스 유기 발광 다이오드용 출력 드라이버 | |

| JP2008310221A (ja) | 電流出力装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090327 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120327 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120918 |