JP2005183686A - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP2005183686A JP2005183686A JP2003422762A JP2003422762A JP2005183686A JP 2005183686 A JP2005183686 A JP 2005183686A JP 2003422762 A JP2003422762 A JP 2003422762A JP 2003422762 A JP2003422762 A JP 2003422762A JP 2005183686 A JP2005183686 A JP 2005183686A

- Authority

- JP

- Japan

- Prior art keywords

- region

- soi layer

- disposed

- isolation insulating

- soi

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

- 239000004065 semiconductor Substances 0.000 title claims description 65

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 238000002955 isolation Methods 0.000 claims abstract description 149

- 239000000758 substrate Substances 0.000 claims description 53

- 239000012535 impurity Substances 0.000 claims description 41

- 238000000034 method Methods 0.000 claims description 23

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 17

- 229920005591 polysilicon Polymers 0.000 claims description 17

- 238000005468 ion implantation Methods 0.000 claims description 7

- 238000000059 patterning Methods 0.000 claims description 6

- 230000003071 parasitic effect Effects 0.000 abstract description 18

- 238000000926 separation method Methods 0.000 abstract description 8

- 238000009413 insulation Methods 0.000 abstract description 3

- 239000010410 layer Substances 0.000 description 148

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 29

- 229910052814 silicon oxide Inorganic materials 0.000 description 29

- 229910021332 silicide Inorganic materials 0.000 description 25

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 25

- 230000015572 biosynthetic process Effects 0.000 description 22

- 238000002513 implantation Methods 0.000 description 21

- 230000004048 modification Effects 0.000 description 12

- 238000012986 modification Methods 0.000 description 12

- 229910052581 Si3N4 Inorganic materials 0.000 description 10

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 10

- 238000005530 etching Methods 0.000 description 10

- 229910052710 silicon Inorganic materials 0.000 description 10

- 239000010703 silicon Substances 0.000 description 10

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 10

- 101710183548 Pyridoxal 5'-phosphate synthase subunit PdxS Proteins 0.000 description 9

- 102100035459 Pyruvate dehydrogenase protein X component, mitochondrial Human genes 0.000 description 9

- 239000011229 interlayer Substances 0.000 description 9

- 239000000969 carrier Substances 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 229910052785 arsenic Inorganic materials 0.000 description 4

- 229910052698 phosphorus Inorganic materials 0.000 description 4

- 238000005498 polishing Methods 0.000 description 4

- 238000006243 chemical reaction Methods 0.000 description 3

- 239000012212 insulator Substances 0.000 description 3

- PXHVJJICTQNCMI-UHFFFAOYSA-N nickel Substances [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 3

- 230000003647 oxidation Effects 0.000 description 3

- 238000007254 oxidation reaction Methods 0.000 description 3

- 239000003870 refractory metal Substances 0.000 description 3

- 238000004544 sputter deposition Methods 0.000 description 3

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 2

- 230000005856 abnormality Effects 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 230000000295 complement effect Effects 0.000 description 2

- 238000000151 deposition Methods 0.000 description 2

- 230000008021 deposition Effects 0.000 description 2

- 238000001312 dry etching Methods 0.000 description 2

- 230000009977 dual effect Effects 0.000 description 2

- 238000009434 installation Methods 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 239000000203 mixture Substances 0.000 description 2

- 239000010936 titanium Substances 0.000 description 2

- 238000001039 wet etching Methods 0.000 description 2

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 230000015556 catabolic process Effects 0.000 description 1

- 239000010941 cobalt Substances 0.000 description 1

- 229910017052 cobalt Inorganic materials 0.000 description 1

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 description 1

- 239000013256 coordination polymer Substances 0.000 description 1

- 230000000779 depleting effect Effects 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 238000002347 injection Methods 0.000 description 1

- 239000007924 injection Substances 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 239000011733 molybdenum Substances 0.000 description 1

- 229910052759 nickel Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

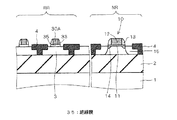

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/40—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00 with at least one component covered by groups H10D10/00 or H10D18/00, e.g. integration of IGFETs with BJTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/20—Inductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/40—Resistors

- H10D1/47—Resistors having no potential barriers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/80—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers characterised by the integration of at least one component covered by groups H10D12/00 or H10D30/00, e.g. integration of IGFETs

- H10D84/811—Combinations of field-effect devices and one or more diodes, capacitors or resistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/201—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates the substrates comprising an insulating layer on a semiconductor body, e.g. SOI

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/80—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple passive components, e.g. resistors, capacitors or inductors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0212—Manufacture or treatment of FETs having insulated gates [IGFET] using self-aligned silicidation

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/0223—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate

- H10D30/0227—Manufacture or treatment of FETs having insulated gates [IGFET] having source and drain regions or source and drain extensions self-aligned to sides of the gate having both lightly-doped source and drain extensions and source and drain regions self-aligned to the sides of the gate, e.g. lightly-doped drain [LDD] MOSFET or double-diffused drain [DDD] MOSFET

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/601—Insulated-gate field-effect transistors [IGFET] having lightly-doped drain or source extensions, e.g. LDD IGFETs or DDD IGFETs

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Element Separation (AREA)

- Thin Film Transistor (AREA)

Priority Applications (9)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003422762A JP2005183686A (ja) | 2003-12-19 | 2003-12-19 | 半導体装置およびその製造方法 |

| US11/002,142 US7173319B2 (en) | 2003-12-19 | 2004-12-03 | Semiconductor device and method of manufacturing the same |

| TW093138569A TW200525734A (en) | 2003-12-19 | 2004-12-13 | Semiconductor device and method of manufacturing the same |

| DE102004060170A DE102004060170A1 (de) | 2003-12-19 | 2004-12-14 | Halbleitervorrichtung und Verfahren zu ihrer Herstellung |

| KR1020040105991A KR20050062390A (ko) | 2003-12-19 | 2004-12-15 | 반도체장치 및 그 제조방법 |

| CNA2004100821457A CN1649160A (zh) | 2003-12-19 | 2004-12-17 | 半导体装置及其制造方法 |

| US11/500,340 US7352049B2 (en) | 2003-12-19 | 2006-08-08 | Semiconductor device and method of manufacturing the same |

| US11/617,936 US7453135B2 (en) | 2003-12-19 | 2006-12-29 | Semiconductor device and method of manufacturing the same |

| US11/873,907 US20080042237A1 (en) | 2003-12-19 | 2007-10-17 | Semiconductor device and method of manufacturing the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003422762A JP2005183686A (ja) | 2003-12-19 | 2003-12-19 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005183686A true JP2005183686A (ja) | 2005-07-07 |

| JP2005183686A5 JP2005183686A5 (enExample) | 2007-02-08 |

Family

ID=34675327

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003422762A Pending JP2005183686A (ja) | 2003-12-19 | 2003-12-19 | 半導体装置およびその製造方法 |

Country Status (6)

| Country | Link |

|---|---|

| US (4) | US7173319B2 (enExample) |

| JP (1) | JP2005183686A (enExample) |

| KR (1) | KR20050062390A (enExample) |

| CN (1) | CN1649160A (enExample) |

| DE (1) | DE102004060170A1 (enExample) |

| TW (1) | TW200525734A (enExample) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7524734B2 (en) | 2005-07-28 | 2009-04-28 | Seiko Epson Corporation | Wiring substrate, electro-optic device, electric apparatus, method of manufacturing wiring substrate, method of manufacturing electro-optic device, and method of manufacturing electric apparatus |

| JP2010239044A (ja) * | 2009-03-31 | 2010-10-21 | Sanken Electric Co Ltd | 集積化半導体装置及びその製造方法 |

| JP2012186491A (ja) * | 2012-05-07 | 2012-09-27 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2005183686A (ja) | 2003-12-19 | 2005-07-07 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| US7790527B2 (en) * | 2006-02-03 | 2010-09-07 | International Business Machines Corporation | High-voltage silicon-on-insulator transistors and methods of manufacturing the same |

| JP2007242660A (ja) * | 2006-03-06 | 2007-09-20 | Renesas Technology Corp | 半導体装置 |

| US20070232019A1 (en) * | 2006-03-30 | 2007-10-04 | Hynix Semiconductor Inc. | Method for forming isolation structure in nonvolatile memory device |

| CN100514585C (zh) * | 2006-04-12 | 2009-07-15 | 财团法人工业技术研究院 | 具有电感的晶片级构装结构及其构装方法 |

| US8089130B2 (en) | 2006-06-20 | 2012-01-03 | Agere Systems Inc. | Semiconductor device and process for reducing damaging breakdown in gate dielectrics |

| KR100819558B1 (ko) * | 2006-09-04 | 2008-04-07 | 삼성전자주식회사 | 반도체 저항소자들 및 그의 형성방법들 |

| JP5137378B2 (ja) * | 2006-10-20 | 2013-02-06 | ルネサスエレクトロニクス株式会社 | 半導体装置及びその製造方法 |

| JP4614981B2 (ja) * | 2007-03-22 | 2011-01-19 | Jsr株式会社 | 化学機械研磨用水系分散体および半導体装置の化学機械研磨方法 |

| JP4458129B2 (ja) * | 2007-08-09 | 2010-04-28 | ソニー株式会社 | 半導体装置およびその製造方法 |

| US7679139B2 (en) * | 2007-09-11 | 2010-03-16 | Honeywell International Inc. | Non-planar silicon-on-insulator device that includes an “area-efficient” body tie |

| CN101859783B (zh) * | 2010-04-30 | 2012-05-30 | 北京大学 | 一种抗总剂量辐照的soi器件及其制造方法 |

| CN101859782B (zh) * | 2010-04-30 | 2012-05-30 | 北京大学 | 抗总剂量辐照的soi器件及其制造方法 |

| US8492868B2 (en) * | 2010-08-02 | 2013-07-23 | International Business Machines Corporation | Method, apparatus, and design structure for silicon-on-insulator high-bandwidth circuitry with reduced charge layer |

| JP5616823B2 (ja) * | 2011-03-08 | 2014-10-29 | セイコーインスツル株式会社 | 半導体装置およびその製造方法 |

| US8765607B2 (en) * | 2011-06-01 | 2014-07-01 | Freescale Semiconductor, Inc. | Active tiling placement for improved latch-up immunity |

| KR101896412B1 (ko) * | 2011-08-01 | 2018-09-07 | 페어차일드코리아반도체 주식회사 | 폴리 실리콘 저항, 이를 포함하는 기준 전압 회로, 및 폴리 실리콘 저항 제조 방법 |

| FR3012666A1 (enExample) | 2013-10-31 | 2015-05-01 | St Microelectronics Crolles 2 | |

| FR3012665A1 (enExample) * | 2013-10-31 | 2015-05-01 | St Microelectronics Crolles 2 | |

| FR3012667A1 (enExample) | 2013-10-31 | 2015-05-01 | St Microelectronics Crolles 2 | |

| US9929135B2 (en) * | 2016-03-07 | 2018-03-27 | Micron Technology, Inc. | Apparatuses and methods for semiconductor circuit layout |

| DE102018112866B4 (de) * | 2018-05-29 | 2020-07-02 | Infineon Technologies Ag | Halbleitervorrichtung mit elektrischem Widerstand |

Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001308273A (ja) * | 2000-04-19 | 2001-11-02 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2002343873A (ja) * | 2001-05-17 | 2002-11-29 | Mitsubishi Electric Corp | 半導体装置 |

| JP2003051543A (ja) * | 2001-08-03 | 2003-02-21 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2003158198A (ja) * | 2001-09-07 | 2003-05-30 | Seiko Instruments Inc | 相補型mos半導体装置 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH09289324A (ja) | 1996-04-23 | 1997-11-04 | Matsushita Electric Works Ltd | 半導体装置の製造方法 |

| JP3161418B2 (ja) | 1998-07-06 | 2001-04-25 | 日本電気株式会社 | 電界効果トランジスタの製造方法 |

| JP4540146B2 (ja) | 1998-12-24 | 2010-09-08 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2001230315A (ja) | 2000-02-17 | 2001-08-24 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| KR100543393B1 (ko) | 2000-03-09 | 2006-01-20 | 후지쯔 가부시끼가이샤 | 반도체 장치 및 그 제조 방법 |

| US6358820B1 (en) * | 2000-04-17 | 2002-03-19 | Mitsubishi Denki Kabushiki Kaisha | Method of manufacturing semiconductor device |

| JP4969715B2 (ja) * | 2000-06-06 | 2012-07-04 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP4776755B2 (ja) | 2000-06-08 | 2011-09-21 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| JP2002110908A (ja) | 2000-09-28 | 2002-04-12 | Toshiba Corp | スパイラルインダクタおよびこれを備える半導体集積回路装置の製造方法 |

| US6635550B2 (en) * | 2000-12-20 | 2003-10-21 | Texas Instruments Incorporated | Semiconductor on insulator device architecture and method of construction |

| US6833602B1 (en) * | 2002-09-06 | 2004-12-21 | Lattice Semiconductor Corporation | Device having electrically isolated low voltage and high voltage regions and process for fabricating the device |

| JP2005183686A (ja) * | 2003-12-19 | 2005-07-07 | Renesas Technology Corp | 半導体装置およびその製造方法 |

-

2003

- 2003-12-19 JP JP2003422762A patent/JP2005183686A/ja active Pending

-

2004

- 2004-12-03 US US11/002,142 patent/US7173319B2/en not_active Expired - Fee Related

- 2004-12-13 TW TW093138569A patent/TW200525734A/zh unknown

- 2004-12-14 DE DE102004060170A patent/DE102004060170A1/de not_active Withdrawn

- 2004-12-15 KR KR1020040105991A patent/KR20050062390A/ko not_active Withdrawn

- 2004-12-17 CN CNA2004100821457A patent/CN1649160A/zh active Pending

-

2006

- 2006-08-08 US US11/500,340 patent/US7352049B2/en not_active Expired - Fee Related

- 2006-12-29 US US11/617,936 patent/US7453135B2/en not_active Expired - Fee Related

-

2007

- 2007-10-17 US US11/873,907 patent/US20080042237A1/en not_active Abandoned

Patent Citations (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2001308273A (ja) * | 2000-04-19 | 2001-11-02 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| JP2002343873A (ja) * | 2001-05-17 | 2002-11-29 | Mitsubishi Electric Corp | 半導体装置 |

| JP2003051543A (ja) * | 2001-08-03 | 2003-02-21 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2003158198A (ja) * | 2001-09-07 | 2003-05-30 | Seiko Instruments Inc | 相補型mos半導体装置 |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7524734B2 (en) | 2005-07-28 | 2009-04-28 | Seiko Epson Corporation | Wiring substrate, electro-optic device, electric apparatus, method of manufacturing wiring substrate, method of manufacturing electro-optic device, and method of manufacturing electric apparatus |

| JP2010239044A (ja) * | 2009-03-31 | 2010-10-21 | Sanken Electric Co Ltd | 集積化半導体装置及びその製造方法 |

| JP2012186491A (ja) * | 2012-05-07 | 2012-09-27 | Renesas Electronics Corp | 半導体装置及びその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| DE102004060170A1 (de) | 2005-07-28 |

| US20070105329A1 (en) | 2007-05-10 |

| TW200525734A (en) | 2005-08-01 |

| US20050133864A1 (en) | 2005-06-23 |

| US20080042237A1 (en) | 2008-02-21 |

| CN1649160A (zh) | 2005-08-03 |

| US7453135B2 (en) | 2008-11-18 |

| US20060270126A1 (en) | 2006-11-30 |

| US7173319B2 (en) | 2007-02-06 |

| KR20050062390A (ko) | 2005-06-23 |

| US7352049B2 (en) | 2008-04-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP2005183686A (ja) | 半導体装置およびその製造方法 | |

| US7804132B2 (en) | Semiconductor device | |

| KR100343288B1 (ko) | 에스오아이 모스 트랜지스터의 플로팅 바디 효과를제거하기 위한 에스오아이 반도체 집적회로 및 그 제조방법 | |

| EP2122669B1 (en) | Radio frequency isolation for soi transistors | |

| US9236372B2 (en) | Combined output buffer and ESD diode device | |

| US7332776B2 (en) | Semiconductor device | |

| JP2005251873A (ja) | 半導体集積回路およびその製造方法 | |

| US20060108644A1 (en) | Self-aligned double gate device and method for forming same | |

| US20100197091A1 (en) | Gate dielectric/isolation structure formation in high/low voltage regions of semiconductor device | |

| JP2007251146A (ja) | 半導体装置 | |

| JPH11233785A (ja) | Soimosfetおよびその製造方法 | |

| JP2009004800A (ja) | 半導体集積回路装置 | |

| JP2005197462A (ja) | 半導体装置及びその製造方法 | |

| WO2006116902A1 (en) | A metal oxide semiconductor field effect transistor having isolation structure and methods of manufacturing the same | |

| JP6673806B2 (ja) | 半導体装置 | |

| JP2006140539A (ja) | 半導体集積回路装置の製造方法 | |

| JP2008244098A (ja) | 半導体装置 | |

| JP2020126915A (ja) | 半導体装置 | |

| JP2005243692A (ja) | 半導体装置およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061218 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20061218 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091211 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100105 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100107 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20100427 |