JP2004158763A - 半導体受光素子 - Google Patents

半導体受光素子 Download PDFInfo

- Publication number

- JP2004158763A JP2004158763A JP2002325046A JP2002325046A JP2004158763A JP 2004158763 A JP2004158763 A JP 2004158763A JP 2002325046 A JP2002325046 A JP 2002325046A JP 2002325046 A JP2002325046 A JP 2002325046A JP 2004158763 A JP2004158763 A JP 2004158763A

- Authority

- JP

- Japan

- Prior art keywords

- light receiving

- light

- semiconductor

- substrate

- reflected

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Light Receiving Elements (AREA)

Abstract

【課題】素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することを目的とする。

【解決手段】基板(1)と、前記基板の上に設けられた半導体層(2)と、前記半導体層の主面上に設けられた受光部(3)と、を備え、前記基板及び前記半導体層の側面の少なくとも一部が前記主面に対して傾斜した反射面(15)とされ、前記反射面と対向する側面から入射し前記受光部よりも下を進行する光(L)を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする半導体受光素子を提供する。

【選択図】 図1

【解決手段】基板(1)と、前記基板の上に設けられた半導体層(2)と、前記半導体層の主面上に設けられた受光部(3)と、を備え、前記基板及び前記半導体層の側面の少なくとも一部が前記主面に対して傾斜した反射面(15)とされ、前記反射面と対向する側面から入射し前記受光部よりも下を進行する光(L)を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする半導体受光素子を提供する。

【選択図】 図1

Description

【0001】

【発明の属する技術分野】

本発明は、半導体受光素子に関し、特に、基板上に形成され、その基板の端面から入射される光を検出可能とした半導体受光素子に関する。

【従来の技術】

光通信や各種の計測の分野においては、簡易な光学配置で高い受光感度が得られるフォトダイオード(photodiode)やアバランシェ・フォトダイオード(avalanche photodiode)などの光半導体素子が必要とされる場合が多い。

【0002】

これらの半導体受光素子の構造としては、光吸収層に入射した光により発生したキャリアをドリフト電界により電極部に集める構造が一般的である。

【0003】

図13は、いわゆる「表面入射型」の半導体受光素子を表す断面図である。

【0004】

また、図14は、いわゆる「裏面入射型」の半導体受光素子を表す断面図である。

【0005】

またさらに、図15は、いわゆる「導波路型」の半導体受光素子を表す模式図である。

【0006】

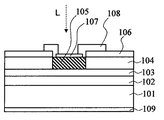

これらの図面に表した受光素子は、InP系の受光素子であり、いずれも、InP基板101の上に、n型InPバッファ層102、低キャリア濃度のn型InGaAs光吸収層103、n型InP窓層104をこの順に積層した構造を有する。そして、亜鉛(Zn)などのp型不純物を選択的に導入することにより、p型領域105が形成され、素子の表面は誘電体膜106や、反射防止(AR)膜107により適宜覆われている。さらに、p側電極108とn側電極109が形成されている。

【0007】

【発明が解決しようとする課題】

これらの受光素子においては、それぞれ図示したように、矢印Lの方向から光が入射され、光吸収層103において吸収され電気信号として検出される。しかし、現実の応用に際しては、検出すべき信号光は、受光素子の上下からではなく、左右方向から入射する場合が多い。

【0008】

例えば、光通信用の受信モジュールの場合、光ファイバから集光レンズ系を介して信号光をパッケージ内に導入する。一方、パッケージ内部では、実装基板の基板面に対して横方向へと各部品を展開する構造を有する。このため、通常は、信号光は、実装基板の基板面に対して上下方向からではなく左右方向から入射する場合が多い。

【0009】

従って、図13に例示した表面入射型や図14に例示した裏面入射型の受光素子を実装基板の上へ直接、実装する場合には、ミラーなどの光学部品が必要となる。

【0010】

図16は、マイクロミラーを用いた光学系を表す模式図である。すなわち、実装基板212の上には、表面入射型の受光素子211が実装されている。一方、信号光Lは、実装基板の基板面に対して横方向から入射する。この信号光は、マイクロミラー213により反射されて、受光素子212に入射する。マイクロミラー213は、例えば、シリコン(Si)の反射面に金属を蒸着した構造を有する。

【0011】

このように、表面入射型あるいは裏面入射型の受光素子を用いた場合、マイクロミラーなどの部品が必要とされ、部品点数が増加し、光軸調整も煩雑になるなどの問題がある。

【0012】

実装基板にマウントするもうひとつの方法として、チップキャリアを用いる方法がある。

【0013】

図17は、チップキャリアを用いた実装方式を表す模式図である。すなわち、受光素子211をセラミックのチップキャリア210にマウントし、信号光Lの方向に向けて実装基板212の上に実装する。しかし、この方法の場合も、やはりチップキャリアが必要とされる。さらに、チップキャリアが有する寄生容量や、ワイヤ214が有する寄生インダクタンスなどの影響で、伝送における群遅延特性が劣化するという問題も生ずる。

【0014】

一方、図15に例示した導波路型の受光素子の場合は、光の入射面が素子の側面であるため、受光素子を実装基板の上に直接実装して、左右から入射してくる信号光を受光できる。しかし、導波路型の受光素子の場合は導波路(ほぼ光吸収層3の部分に相当する)の断面の面積が小さいため、光結合ロスが生じやすく、感度が十分にとれないという問題がある。結合効率としては、2群系のレンズを用いても50%〜60%が限界であった。

【0015】

本発明は、かかる課題の認識に基づいてなされたものであり、その目的は、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することにある。

【0016】

【課題を解決するための手段】

上記目的を達成するため、本発明の第1の半導体受光素子は、上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備えたことを特徴とする。

【0017】

上記構成によれば、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0018】

また、本発明の第2の半導体受光素子は、上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備え、

前記第1の側面から入射し前記受光部と前記下面との間を前記上面に対して略平行な方向に進行する光を前記反射面において前記受光部に向けて反射させ検出可能としたことを特徴とする。

【0019】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0020】

また、本発明の第3の半導体受光素子は、基板と、前記基板の主面上に設けられた半導体層と、前記半導体層の上に設けられた受光部と、を備え、

前記基板及び前記半導体層の側面の少なくとも一部が前記主面に対して傾斜した反射面とされ、前記反射面と対向する側面から入射し前記基板または前記半導体層の少なくともいずれかの中を進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする。

【0021】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0022】

また、本発明の第4の半導体受光素子は、基板と、前記基板の主面上に設けられた受光部と、を備え、

前記基板の側面の一部が前記主面に対して傾斜した反射面とされ、前記反射面と対向する側面から入射し前記主面に対して略平行な方向に進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする。

【0023】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0024】

また、本発明の第5の半導体受光素子は、基板と、前記基板の主面上に設けられた受光部と、前記基板の側面から入射し前記基板内を前記主面に対して略平行な方向に進行する光を前記受光部の方向に反射させる反射面と、を備えたことを特徴とする。

【0025】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0026】

上記第1乃至第4の半導体受光素子において、前記受光部の上に設けられた電極をさらに備え、前記反射面により反射され前記受光部を透過した光の少なくとも一部が前記電極により反射されて前記受光部において検出可能とすれば、量子効率をさらに改善することができる。

【0027】

また、前記入射する光の光軸に対して平行な方向に沿って前記受光部が複数設けられ、前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能とすれば、いわゆるパラレル・リンク用の受光素子を実現できる。

【0028】

また、前記入射する光の光軸に対して垂直な方向に沿って前記受光部が複数設けられ、前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能としても、同様にパラレル・リンク用の受光素子を実現できる。

【0029】

また、本発明の第5の半導体受光素子は、基板と、前記基板の主面上に設けられた第1の半導体層と、前記第1導電型の半導体層の上に設けられた光吸収層と、前記光吸収層の上に設けられた第2の半導体層と、を備えた半導体受光素子であって、側面の一部が傾斜した反射面とされ、前記反射面に対向する側面から前記基板及び前記第2の半導体層の少なくともいずれかに入射し前記主面に対して略平行方向に進行する光を前記反射面により反射させ前記光吸収層において検出可能としたことを特徴とする。

【0030】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0031】

上記第5の半導体受光素子において、前記基板のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なることよりも大なるものとすれば、基板を伝搬する光の損失を低減できる。

【0032】

また、前記第1の半導体層及び前記第2の半導体層のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なるものとすれば、これらの半導体層における光の吸収を低減できる。

【0033】

また、前記第2の半導体層の上に設けられた電極をさらに備え、前記反射面により反射され前記光吸収層を透過した光の少なくとも一部が前記電極により反射されて前記光吸収層において検出可能とすれば、量子効率をさらに改善できる。

【0034】

また、前記反射面は、集光曲面を有するものとすれば、感度をさらに高くすることができる。

【0035】

また、前記反射面は、金属膜または誘電体多層膜を有するものとすれば、高い反射率を容易に得られる。

【0036】

なお、本願明細書において「絶縁性」とは、電気的に明瞭な絶縁状態のみならず、いわゆる「半絶縁」の状態も含むものとする。例えば、InPやGaAsに鉄(Fe)などをドーピングして比抵抗を高い状態とした、いわゆる「半絶縁基板」も、「絶縁性」であるものとする。

【0037】

【発明の実施の形態】

以下、図面を参照しつつ本発明の実施の形態について説明する。

【0038】

図1は、本発明の実施の形態にかかる半導体受光素子の要部構造を表す模式図である。すなわち、同図(a)はその平面図であり、同図(b)はその中心付近の断面図である。

【0039】

本実施形態の半導体受光素子は、側面から光Lを入射させ、その光を対向する反射面15により反射させて受光部に導く構造を有する。図1の構造について説明すると、n型半導体からなる基板1の上に、n型バッファ層2、光吸収層3、n型窓層4がこの順に積層された構造を有する。そして、窓層4の一部がp型化されたp型領域5が形成されている。なお、このp型領域5は、光吸収層3の一部も含むように形成してもよい。窓層4の表面は、誘電体などからなる保護膜6により覆われ、p型領域5の上にはp側電極8が接続されている。一方、基板1の裏面側には、n側電極9が接続されている。

【0040】

この受光素子は、いわゆる「pin型」の構造を有する。すなわち、p側電極8とn側電極9を介してpn接合に対して逆方向のバイアス電圧を印加すると、pn接合から光吸収層3に向けて空乏化領域が拡がる。この状態で光吸収層において光の吸収により電子・正孔対が生ずると、これらは、それぞれ空乏化領域の電界により反対方向に走行し、電流として検出される。

【0041】

さて、本実施形態の受光素子においては、受光素子の一方の側面には、反射防止膜(AR膜)7が設けられ、光Lは、この側面から図1に矢印で表したように入射される。一方、この光入射面と対向した素子の側面は斜面状とされ、反射面15が形成されている。反射面15は、例えば光Lに対する反射率の高い金属などの膜を被覆したり、または、屈折率が異なる複数の誘電体膜を積層させた、いわゆる「ブラッグ反射鏡」構造を用いることことにより形成できる。

【0042】

光Lは、この反射面15により反射され、受光部すなわち、p型領域5の下の光吸収層3の部分に導かれ、電流として検出される。すなわち、本実施形態によれば、受光素子の基板面に対して、略平行に入射する光を反射面15により反射させてプレーナ状の受光部において検出することができる。

【0043】

その結果として、図16あるいは図17に関して前述したような反射ミラー213やチップキャリア210などの部品が不要となり、光通信用の受信モジュールなどの各種の光半導体装置の部品点数を削減し、結合効率も高くすることが可能となる。

【0044】

また、本実施形態においては、反射面15により反射されて受光部に導かれた光Lのうちで、光吸収層3により吸収されずに透過した光は、窓層4を透過してp側電極8により反射され、再び光吸収層3に戻される。すなわち、受光素子の量子効率を上げて、高い感度を得ることができる。

【0045】

また、このように吸収層3を一度透過した光もp側電極8により反射させて検出可能とすれば、光吸収層3の厚みを薄くしても、高い量子効率を維持できる。光吸収層3を薄くすることにより、光励起キャリアの走行時間を短縮して応答時間を短くできる。つまり、本実施形態によれば、量子効率を高く維持しつつ、高速応答が可能な受光素子を得ることもできる。

【0046】

なお、本発明の受光素子においては、反射防止膜7を介して受光素子の中に入射される光Lは、基板1の内部を進行させてもよいが、バッファ層2など、基板以外の層の吸収率が低い場合には、これらの層も含めて光の伝搬路とすることもできる。またさらに、基板1以外の層の中を進行させてもよい。

【0047】

図2は、導波層10を設けた半導体受光素子を表す模式断面図である。すなわち、この受光素子の場合、基板1の上に導波層10を設け、入射光Lを、この導波層10に結合させて、その層内を反射面15まで伝搬させる。この際に、基板1と導波層10との間の屈折率を調節して、入射光Lが導波層10の層内に閉じこめられるようにすれば、損失を低減できる。

【0048】

以下、図1に例示した受光素子の構造及び製造方法について、その具体例を挙げつつさらに詳細に説明する。

【0049】

まず、基板1としては、例えば、n型のInP(キャリア濃度1〜7×1018/cm3)を用いることができる。そして、この上に気相成長法などの方法により、n型InPからなるバッフア層2(キャリア濃度1〜5×1018/cm3、膜厚2〜3μm)、アンドープInGaAsからなるn型の光吸収層3(キャリア濃度8×1014〜2×1015/cm3、膜厚1μm)、n型InPからなる窓層4(キャリア濃度1×1015〜5×1015 /cm3、膜厚1μm)を形成する。

【0050】

さらに窒化シリコン(SiNx)などの保護膜6を形成し、これをフォトリソグラフィ(以下PEP略)技術によりパターニングして、これをマスクとして亜鉛(Zn)などを拡散することによりp型領域5を形成する。そして、その上にp側電極8を形成した後、機械的、化学的研磨により基板1の裏面を研磨して、素子の厚みを120〜200μm程度に調整したのち、最終研磨面を鏡面状態にする。

【0051】

この後、PEPにより、反射面15を形成する部を除いてn側電極9を形成し、シンタ工程によりオーミック化する。その後、ウエーハの表側をワックス等で保護し、臭化水素(HBr)と硝酸(HNO3)の混合系のエッチャントによりエッチングして、反射面15となる斜面を形成する。InP基板1の裏面側からエッチングする場合、反射面15となる斜面は、軸方位<1−10>の順メサ面である。

【0052】

このように、エッチングによって斜面を形成した後、この斜面に金(Au)等の金属膜あるいは誘電体多層膜からなる反射膜を被覆することにより反射面15を形成できる。この後、素子分離する。

【0053】

なお、反射面15となる斜面を形成するエッチング方法としては、ウェットエッチング以外にも、厚膜レジスト(20〜100μm)を用いたイオンミリングなどのドライエッチングプロセスを用いることもできる。

【0054】

また、上述の具体例では、反射面15の斜面を形成するために、基板1の裏面側からエッチングを行うが、基板1の表面側からエッチングしてもよい。すなわち、反射面15を形成する部分以外のウエーハ表面を厚膜レジストなどで保護して、ウエットエッチングにより<110>軸方向の逆メサを形成する。この場合には、逆メサの側面を反射面15とすることができ、エッチングの進行状態に応じて、図3に表したような断面形状が得られることもある。

【0055】

以上、図1に表した本発明の実施形態の受光素子について具体例を挙げて説明したが、本発明はこれに限定されるものではない。例えば、基板1の上に設ける積層構造については、ヘテロ接合のバンドギャップ不連続を緩和するための中間層を設けたり、また、アバランシェ増倍を生じさせるための増倍層を設けて、APD(avalanche photodiode)としてもよい。

【0056】

また、p型領域5の平面形状についても、図1(a)に表したような略円形以外にも、各種の形状を与えることができる。

【0057】

また、図1(a)に例示したp側電極8には、ワイアなどを接続するためのボンディング・パッド部8Bが設けられているが、このようなパッド部を設けずに、p型領域5の上にワイアなどを接続してもよい

またさらに、反射面15とp型領域5(あるいは受光部)との配置関係やサイズの関係についても、各種の変形が可能である。

【0058】

図4は、本発明の変形例の半導体受光素子を表す模式断面図である。なお、以下に参照する同図については、図1及び図3に関して前述したものと同様の要素には、同一の符号を付して詳細な説明は省略する。

【0059】

本変形例においては、反射面15は、基板1の主面に対して略45度の傾斜を有し、p型領域5の下方に設けられている。このような配置関係の場合には、光Lは、受光素子に入射して基板1の主面に対して平行な方向に進行し、反射面15によりほぼ垂直上方に反射されて受光部に導かれる。

【0060】

図5は、反射面15がやや切り立った斜面とされた変形例を表す模式断面図である。すなわち、本変形例においては、p型領域5は、反射面15からやや離れた場所に設けられている。このような場合には、基板1の主面に対して略平行な方向に進行してくる光Lを受光部に導くために、反射面15は、やや切り立った斜面とされる。

【0061】

一方、図6は、反射面15が大きく傾斜した変形例を表す模式断面図である。

【0062】

すなわち、本変形例においては、p型領域5は、反射面15の上端に接近して設けられている。このような場合には、基板1の面内方向に進行してくる光Lを受光部に導くために、反射面15は、大きく傾斜した斜面とされる。

【0063】

一方、本発明においては、反射面15を曲面とすることもできる。

【0064】

図7は、反射面15を集光曲面とした変形例を表す模式断面図である。すなわち、反射面15は、基板1の面内方向に対して進行してくる光Lをp型領域5に集光するように、曲面状に形成されている。このようにすれば、厚みのある基板1の中を拡がって進行してくる光Lを小さな受光部に集光させて検出することができる。つまり、受光部に対する集光効率を上げて、さらに量子効率を改善できる。またさらに、p型領域5を小さくすることができるので、pn接合の寄生容量を下げることができる。その結果として、高速動作が可能となる。

【0065】

なお、図7においては、断面図のみを表したが、平面図(図1(a)に対応する)においても集光曲面を形成すれば、集光効率はさらに向上する。

【0066】

また、本発明においては、基板1を絶縁性の材料により形成してもよい。

【0067】

図8は、基板1を半絶縁体により形成した変形例を表す模式断面図である。すなわち、基板1は、例えば、鉄(Fe)をドープした半絶縁InPなどの材料により形成できる。この場合には、n側電極9は、素子の表面側に設ける。

【0068】

また、本発明においては、複数の受光部を集積させることもできる。

【0069】

図9は、2つの受光部をアレイ状に集積化させた変形例を表す模式断面図である。すなわち、2つの受光部を光軸に対して平行な方向に並べ、反射面15によって、それぞれの受光部に光Lが導かれる。この場合、2つの入射光A及びBの光軸を基板1の厚み方向に並べて入射させ、それぞれ別々の受光部により検出させることができ、いわゆる「光パラレルリンク」用の受光素子アレイを得ることができる。

【0070】

またさらに、このような集積型の受光素子において、図10に例示した如く、反射面15を、それぞれの入射光に対応させた集光曲面としてもよい。すなわち、入射光Aと入射光Bとにそれぞれ対応した2つの集光曲面が形成されている。このようにすれば、検出効率を上げることができると同時に、入射光A及びBのセパレーションも改善し、いわゆる「クロストーク」を低減できる。

【0071】

さらにまた、図7に関して前述したように、p型領域5のサイズを小さくできるので、pn接合の寄生容量を減らして、素子の遮断周波数を上げることもできる。すなわち、高い検出効率で高速動作が可能なパラレルリンク用の集積型受光素子を実現できる。

【0072】

一方、本発明においては、複数の受光部を入射光の光軸に対して垂直な方向に並べることもできる。

【0073】

図11は、2つの受光部を入射光の光軸に対して垂直な方向に並べた集積型の半導体受光素子を表す模式断面図である。この場合には、2つの入射光A及びBの光軸は基板面に対して平行な方向に並べて、それぞれ反射面15により反射させ、別々の受光部に導くことができる。

【0074】

本具体例の場合には、複数の入射光の光軸を基板1の面内方向に並べるので、その光軸の間隔も自由に設定でき、クロストークを解消するために光軸の間隔を広くすることも容易である。また、本具体例の場合も、図7及び図10に表したように、入射光のそれぞれに対応して反射面15に集光曲面を形成すれば、検出効率をさらに高くし、クロストークも低減し、受光部を小さくすることにより高速化も可能となる。

【0075】

なお、図9乃至図11においては、2つの受光部を集積した受光素子を表したが、本発明はこれには限定されず、3つ以上の受光部を入射光の光軸に対して平行な方向または垂直な方向に並べてもよい。またさらに、複数の受光部を、入射光の光軸に対して平行及び垂直な方向にマトリクス状に集積してもよい。

【0076】

図12は、複数の受光部をマトリクス状に集積した半導体受光素子の模式図である。すなわち、同図(a)はその平面図、同図(b)は断面図である。

【0077】

本具体例の場合、4つの受光部が、入射光A乃至Dのそれぞれに対応してマトリクス状に集積されている。このように、入射光の光軸に対して平行及び垂直な方向に受光部を並べると、多数の受光部をコンパクトに集積することが容易となる。その結果として、多チャンネルのパラレルリンク用の半導体受光素子を極めてコンパクトに実現できる。

【0078】

また、本具体例の場合も、図示したように、入射光のそれぞれに対応して反射面15に集光曲面を形成すれば、検出効率をさらに高くし、クロストークも低減し、受光部を小さくすることにより高速化も可能となる。

【0079】

なお、図12においては、4つの受光部をマトリクス状に集積した具体例を表したが、本発明はこれには限定されず、より多数の受光部を入射光の光軸に対して平行及び垂直な方向に並べてもよい。

【0080】

以上、具体例を参照しつつ本発明の実施の形態について説明した。しかし、本発明はこれらの具体例に限定されるものではない。

【0081】

すなわち、本発明の半導体受光素子の各部の構造、形状、材料、配置関係などについては、公知の半導体受光素子あるいはその他の素子を元に当業者が適宜適用したものも包含する。例えば、本発明においては、受光部として、図示したような「プレーナ型」のpn接合の他にも、例えば、「メサ型」のpn接合を採用することもできる。また、受光素子を構成する基板や各層の材料についても、具体例として挙げたInP系以外に、GaAs系やGaN系などの各種の化合物半導体や、Si、Geなどを用いることもできる。また、基板としては、半導体以外にも、例えば、サファイアをはじめとする各種の絶縁体などを用いることもできる。

【発明の効果】

以上詳述したように、本発明によれば、受光素子の基板面に対して略平行に入射する光を傾斜した反射面により反射させて受光部において検出することにより、反射ミラーやチップキャリアなどの部品が不要となり、光通信用の受信モジュールなどの各種の光半導体装置の部品点数を削減し、結合効率も高くすることが可能となる。

【0082】

すなわち、本発明によれば、優れた性能を有する半導体受光素子を提供することが可能となり、産業上のメリットは多大である。

【図面の簡単な説明】

【図1】本発明の実施の形態にかかる半導体受光素子の要部構造を表す模式図である。

【図2】導波層を設けた半導体受光素子を表す模式断面図である。

【図3】逆メサの側面を反射面15とした場合の半導体受光素子の要部構造を例示する模式図である。

【図4】本発明の変形例の半導体受光素子を表す模式断面図である。

【図5】反射面15がやや切り立った斜面とされた変形例を表す模式断面図である。

【図6】反射面15が大きく傾斜した変形例を表す模式断面図である。

【図7】反射面15を集光曲面とした変形例を表す模式断面図である。

【図8】基板1を半絶縁体により形成した変形例を表す模式断面図である。

【図9】2つの受光部をアレイ状に集積化させた変形例を表す模式断面図である。

【図10】反射面15を、それぞれの入射光に対応させた集光曲面とした具体例を表す模式断面図である。

【図11】2つの受光部を入射光の光軸に対して垂直な方向に並べた集積型の半導体受光素子を表す模式断面図である。

【図12】複数の受光部をマトリクス状に集積した半導体受光素子の模式図である。

【図13】いわゆる「表面入射型」の半導体受光素子を表す断面図である。

【図14】いわゆる「裏面入射型」の半導体受光素子を表す断面図である。

【図15】いわゆる「導波路型」の半導体受光素子を表す模式図である。

【図16】マイクロミラーを用いた光学系を表す模式図である。

【図17】チップキャリアを用いた実装方式を表す模式図である。

【符号の説明】

1 基板

2 バッフア層

3 光吸収層

4 窓層

5 p型領域

6 保護膜

7 反射防止膜

8 p側電極

8B パッド部

9 n側電極

15 反射面

101 基板

102 バッファ層

103 光吸収層

104 窓層

210 チップキャリア

211 受光素子

212 受光素子

212 実装基板

213 反射ミラー

214 ワイヤ

A〜D、L 入射光

【発明の属する技術分野】

本発明は、半導体受光素子に関し、特に、基板上に形成され、その基板の端面から入射される光を検出可能とした半導体受光素子に関する。

【従来の技術】

光通信や各種の計測の分野においては、簡易な光学配置で高い受光感度が得られるフォトダイオード(photodiode)やアバランシェ・フォトダイオード(avalanche photodiode)などの光半導体素子が必要とされる場合が多い。

【0002】

これらの半導体受光素子の構造としては、光吸収層に入射した光により発生したキャリアをドリフト電界により電極部に集める構造が一般的である。

【0003】

図13は、いわゆる「表面入射型」の半導体受光素子を表す断面図である。

【0004】

また、図14は、いわゆる「裏面入射型」の半導体受光素子を表す断面図である。

【0005】

またさらに、図15は、いわゆる「導波路型」の半導体受光素子を表す模式図である。

【0006】

これらの図面に表した受光素子は、InP系の受光素子であり、いずれも、InP基板101の上に、n型InPバッファ層102、低キャリア濃度のn型InGaAs光吸収層103、n型InP窓層104をこの順に積層した構造を有する。そして、亜鉛(Zn)などのp型不純物を選択的に導入することにより、p型領域105が形成され、素子の表面は誘電体膜106や、反射防止(AR)膜107により適宜覆われている。さらに、p側電極108とn側電極109が形成されている。

【0007】

【発明が解決しようとする課題】

これらの受光素子においては、それぞれ図示したように、矢印Lの方向から光が入射され、光吸収層103において吸収され電気信号として検出される。しかし、現実の応用に際しては、検出すべき信号光は、受光素子の上下からではなく、左右方向から入射する場合が多い。

【0008】

例えば、光通信用の受信モジュールの場合、光ファイバから集光レンズ系を介して信号光をパッケージ内に導入する。一方、パッケージ内部では、実装基板の基板面に対して横方向へと各部品を展開する構造を有する。このため、通常は、信号光は、実装基板の基板面に対して上下方向からではなく左右方向から入射する場合が多い。

【0009】

従って、図13に例示した表面入射型や図14に例示した裏面入射型の受光素子を実装基板の上へ直接、実装する場合には、ミラーなどの光学部品が必要となる。

【0010】

図16は、マイクロミラーを用いた光学系を表す模式図である。すなわち、実装基板212の上には、表面入射型の受光素子211が実装されている。一方、信号光Lは、実装基板の基板面に対して横方向から入射する。この信号光は、マイクロミラー213により反射されて、受光素子212に入射する。マイクロミラー213は、例えば、シリコン(Si)の反射面に金属を蒸着した構造を有する。

【0011】

このように、表面入射型あるいは裏面入射型の受光素子を用いた場合、マイクロミラーなどの部品が必要とされ、部品点数が増加し、光軸調整も煩雑になるなどの問題がある。

【0012】

実装基板にマウントするもうひとつの方法として、チップキャリアを用いる方法がある。

【0013】

図17は、チップキャリアを用いた実装方式を表す模式図である。すなわち、受光素子211をセラミックのチップキャリア210にマウントし、信号光Lの方向に向けて実装基板212の上に実装する。しかし、この方法の場合も、やはりチップキャリアが必要とされる。さらに、チップキャリアが有する寄生容量や、ワイヤ214が有する寄生インダクタンスなどの影響で、伝送における群遅延特性が劣化するという問題も生ずる。

【0014】

一方、図15に例示した導波路型の受光素子の場合は、光の入射面が素子の側面であるため、受光素子を実装基板の上に直接実装して、左右から入射してくる信号光を受光できる。しかし、導波路型の受光素子の場合は導波路(ほぼ光吸収層3の部分に相当する)の断面の面積が小さいため、光結合ロスが生じやすく、感度が十分にとれないという問題がある。結合効率としては、2群系のレンズを用いても50%〜60%が限界であった。

【0015】

本発明は、かかる課題の認識に基づいてなされたものであり、その目的は、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することにある。

【0016】

【課題を解決するための手段】

上記目的を達成するため、本発明の第1の半導体受光素子は、上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備えたことを特徴とする。

【0017】

上記構成によれば、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0018】

また、本発明の第2の半導体受光素子は、上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備え、

前記第1の側面から入射し前記受光部と前記下面との間を前記上面に対して略平行な方向に進行する光を前記反射面において前記受光部に向けて反射させ検出可能としたことを特徴とする。

【0019】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0020】

また、本発明の第3の半導体受光素子は、基板と、前記基板の主面上に設けられた半導体層と、前記半導体層の上に設けられた受光部と、を備え、

前記基板及び前記半導体層の側面の少なくとも一部が前記主面に対して傾斜した反射面とされ、前記反射面と対向する側面から入射し前記基板または前記半導体層の少なくともいずれかの中を進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする。

【0021】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0022】

また、本発明の第4の半導体受光素子は、基板と、前記基板の主面上に設けられた受光部と、を備え、

前記基板の側面の一部が前記主面に対して傾斜した反射面とされ、前記反射面と対向する側面から入射し前記主面に対して略平行な方向に進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする。

【0023】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0024】

また、本発明の第5の半導体受光素子は、基板と、前記基板の主面上に設けられた受光部と、前記基板の側面から入射し前記基板内を前記主面に対して略平行な方向に進行する光を前記受光部の方向に反射させる反射面と、を備えたことを特徴とする。

【0025】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0026】

上記第1乃至第4の半導体受光素子において、前記受光部の上に設けられた電極をさらに備え、前記反射面により反射され前記受光部を透過した光の少なくとも一部が前記電極により反射されて前記受光部において検出可能とすれば、量子効率をさらに改善することができる。

【0027】

また、前記入射する光の光軸に対して平行な方向に沿って前記受光部が複数設けられ、前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能とすれば、いわゆるパラレル・リンク用の受光素子を実現できる。

【0028】

また、前記入射する光の光軸に対して垂直な方向に沿って前記受光部が複数設けられ、前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能としても、同様にパラレル・リンク用の受光素子を実現できる。

【0029】

また、本発明の第5の半導体受光素子は、基板と、前記基板の主面上に設けられた第1の半導体層と、前記第1導電型の半導体層の上に設けられた光吸収層と、前記光吸収層の上に設けられた第2の半導体層と、を備えた半導体受光素子であって、側面の一部が傾斜した反射面とされ、前記反射面に対向する側面から前記基板及び前記第2の半導体層の少なくともいずれかに入射し前記主面に対して略平行方向に進行する光を前記反射面により反射させ前記光吸収層において検出可能としたことを特徴とする。

【0030】

上記構成によっても、素子の主面に対して平行な方向の入射光をそのまま導入でき、高速かつ高感度・高結合効率を実現できる半導体受光素子を提供することができる。

【0031】

上記第5の半導体受光素子において、前記基板のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なることよりも大なるものとすれば、基板を伝搬する光の損失を低減できる。

【0032】

また、前記第1の半導体層及び前記第2の半導体層のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なるものとすれば、これらの半導体層における光の吸収を低減できる。

【0033】

また、前記第2の半導体層の上に設けられた電極をさらに備え、前記反射面により反射され前記光吸収層を透過した光の少なくとも一部が前記電極により反射されて前記光吸収層において検出可能とすれば、量子効率をさらに改善できる。

【0034】

また、前記反射面は、集光曲面を有するものとすれば、感度をさらに高くすることができる。

【0035】

また、前記反射面は、金属膜または誘電体多層膜を有するものとすれば、高い反射率を容易に得られる。

【0036】

なお、本願明細書において「絶縁性」とは、電気的に明瞭な絶縁状態のみならず、いわゆる「半絶縁」の状態も含むものとする。例えば、InPやGaAsに鉄(Fe)などをドーピングして比抵抗を高い状態とした、いわゆる「半絶縁基板」も、「絶縁性」であるものとする。

【0037】

【発明の実施の形態】

以下、図面を参照しつつ本発明の実施の形態について説明する。

【0038】

図1は、本発明の実施の形態にかかる半導体受光素子の要部構造を表す模式図である。すなわち、同図(a)はその平面図であり、同図(b)はその中心付近の断面図である。

【0039】

本実施形態の半導体受光素子は、側面から光Lを入射させ、その光を対向する反射面15により反射させて受光部に導く構造を有する。図1の構造について説明すると、n型半導体からなる基板1の上に、n型バッファ層2、光吸収層3、n型窓層4がこの順に積層された構造を有する。そして、窓層4の一部がp型化されたp型領域5が形成されている。なお、このp型領域5は、光吸収層3の一部も含むように形成してもよい。窓層4の表面は、誘電体などからなる保護膜6により覆われ、p型領域5の上にはp側電極8が接続されている。一方、基板1の裏面側には、n側電極9が接続されている。

【0040】

この受光素子は、いわゆる「pin型」の構造を有する。すなわち、p側電極8とn側電極9を介してpn接合に対して逆方向のバイアス電圧を印加すると、pn接合から光吸収層3に向けて空乏化領域が拡がる。この状態で光吸収層において光の吸収により電子・正孔対が生ずると、これらは、それぞれ空乏化領域の電界により反対方向に走行し、電流として検出される。

【0041】

さて、本実施形態の受光素子においては、受光素子の一方の側面には、反射防止膜(AR膜)7が設けられ、光Lは、この側面から図1に矢印で表したように入射される。一方、この光入射面と対向した素子の側面は斜面状とされ、反射面15が形成されている。反射面15は、例えば光Lに対する反射率の高い金属などの膜を被覆したり、または、屈折率が異なる複数の誘電体膜を積層させた、いわゆる「ブラッグ反射鏡」構造を用いることことにより形成できる。

【0042】

光Lは、この反射面15により反射され、受光部すなわち、p型領域5の下の光吸収層3の部分に導かれ、電流として検出される。すなわち、本実施形態によれば、受光素子の基板面に対して、略平行に入射する光を反射面15により反射させてプレーナ状の受光部において検出することができる。

【0043】

その結果として、図16あるいは図17に関して前述したような反射ミラー213やチップキャリア210などの部品が不要となり、光通信用の受信モジュールなどの各種の光半導体装置の部品点数を削減し、結合効率も高くすることが可能となる。

【0044】

また、本実施形態においては、反射面15により反射されて受光部に導かれた光Lのうちで、光吸収層3により吸収されずに透過した光は、窓層4を透過してp側電極8により反射され、再び光吸収層3に戻される。すなわち、受光素子の量子効率を上げて、高い感度を得ることができる。

【0045】

また、このように吸収層3を一度透過した光もp側電極8により反射させて検出可能とすれば、光吸収層3の厚みを薄くしても、高い量子効率を維持できる。光吸収層3を薄くすることにより、光励起キャリアの走行時間を短縮して応答時間を短くできる。つまり、本実施形態によれば、量子効率を高く維持しつつ、高速応答が可能な受光素子を得ることもできる。

【0046】

なお、本発明の受光素子においては、反射防止膜7を介して受光素子の中に入射される光Lは、基板1の内部を進行させてもよいが、バッファ層2など、基板以外の層の吸収率が低い場合には、これらの層も含めて光の伝搬路とすることもできる。またさらに、基板1以外の層の中を進行させてもよい。

【0047】

図2は、導波層10を設けた半導体受光素子を表す模式断面図である。すなわち、この受光素子の場合、基板1の上に導波層10を設け、入射光Lを、この導波層10に結合させて、その層内を反射面15まで伝搬させる。この際に、基板1と導波層10との間の屈折率を調節して、入射光Lが導波層10の層内に閉じこめられるようにすれば、損失を低減できる。

【0048】

以下、図1に例示した受光素子の構造及び製造方法について、その具体例を挙げつつさらに詳細に説明する。

【0049】

まず、基板1としては、例えば、n型のInP(キャリア濃度1〜7×1018/cm3)を用いることができる。そして、この上に気相成長法などの方法により、n型InPからなるバッフア層2(キャリア濃度1〜5×1018/cm3、膜厚2〜3μm)、アンドープInGaAsからなるn型の光吸収層3(キャリア濃度8×1014〜2×1015/cm3、膜厚1μm)、n型InPからなる窓層4(キャリア濃度1×1015〜5×1015 /cm3、膜厚1μm)を形成する。

【0050】

さらに窒化シリコン(SiNx)などの保護膜6を形成し、これをフォトリソグラフィ(以下PEP略)技術によりパターニングして、これをマスクとして亜鉛(Zn)などを拡散することによりp型領域5を形成する。そして、その上にp側電極8を形成した後、機械的、化学的研磨により基板1の裏面を研磨して、素子の厚みを120〜200μm程度に調整したのち、最終研磨面を鏡面状態にする。

【0051】

この後、PEPにより、反射面15を形成する部を除いてn側電極9を形成し、シンタ工程によりオーミック化する。その後、ウエーハの表側をワックス等で保護し、臭化水素(HBr)と硝酸(HNO3)の混合系のエッチャントによりエッチングして、反射面15となる斜面を形成する。InP基板1の裏面側からエッチングする場合、反射面15となる斜面は、軸方位<1−10>の順メサ面である。

【0052】

このように、エッチングによって斜面を形成した後、この斜面に金(Au)等の金属膜あるいは誘電体多層膜からなる反射膜を被覆することにより反射面15を形成できる。この後、素子分離する。

【0053】

なお、反射面15となる斜面を形成するエッチング方法としては、ウェットエッチング以外にも、厚膜レジスト(20〜100μm)を用いたイオンミリングなどのドライエッチングプロセスを用いることもできる。

【0054】

また、上述の具体例では、反射面15の斜面を形成するために、基板1の裏面側からエッチングを行うが、基板1の表面側からエッチングしてもよい。すなわち、反射面15を形成する部分以外のウエーハ表面を厚膜レジストなどで保護して、ウエットエッチングにより<110>軸方向の逆メサを形成する。この場合には、逆メサの側面を反射面15とすることができ、エッチングの進行状態に応じて、図3に表したような断面形状が得られることもある。

【0055】

以上、図1に表した本発明の実施形態の受光素子について具体例を挙げて説明したが、本発明はこれに限定されるものではない。例えば、基板1の上に設ける積層構造については、ヘテロ接合のバンドギャップ不連続を緩和するための中間層を設けたり、また、アバランシェ増倍を生じさせるための増倍層を設けて、APD(avalanche photodiode)としてもよい。

【0056】

また、p型領域5の平面形状についても、図1(a)に表したような略円形以外にも、各種の形状を与えることができる。

【0057】

また、図1(a)に例示したp側電極8には、ワイアなどを接続するためのボンディング・パッド部8Bが設けられているが、このようなパッド部を設けずに、p型領域5の上にワイアなどを接続してもよい

またさらに、反射面15とp型領域5(あるいは受光部)との配置関係やサイズの関係についても、各種の変形が可能である。

【0058】

図4は、本発明の変形例の半導体受光素子を表す模式断面図である。なお、以下に参照する同図については、図1及び図3に関して前述したものと同様の要素には、同一の符号を付して詳細な説明は省略する。

【0059】

本変形例においては、反射面15は、基板1の主面に対して略45度の傾斜を有し、p型領域5の下方に設けられている。このような配置関係の場合には、光Lは、受光素子に入射して基板1の主面に対して平行な方向に進行し、反射面15によりほぼ垂直上方に反射されて受光部に導かれる。

【0060】

図5は、反射面15がやや切り立った斜面とされた変形例を表す模式断面図である。すなわち、本変形例においては、p型領域5は、反射面15からやや離れた場所に設けられている。このような場合には、基板1の主面に対して略平行な方向に進行してくる光Lを受光部に導くために、反射面15は、やや切り立った斜面とされる。

【0061】

一方、図6は、反射面15が大きく傾斜した変形例を表す模式断面図である。

【0062】

すなわち、本変形例においては、p型領域5は、反射面15の上端に接近して設けられている。このような場合には、基板1の面内方向に進行してくる光Lを受光部に導くために、反射面15は、大きく傾斜した斜面とされる。

【0063】

一方、本発明においては、反射面15を曲面とすることもできる。

【0064】

図7は、反射面15を集光曲面とした変形例を表す模式断面図である。すなわち、反射面15は、基板1の面内方向に対して進行してくる光Lをp型領域5に集光するように、曲面状に形成されている。このようにすれば、厚みのある基板1の中を拡がって進行してくる光Lを小さな受光部に集光させて検出することができる。つまり、受光部に対する集光効率を上げて、さらに量子効率を改善できる。またさらに、p型領域5を小さくすることができるので、pn接合の寄生容量を下げることができる。その結果として、高速動作が可能となる。

【0065】

なお、図7においては、断面図のみを表したが、平面図(図1(a)に対応する)においても集光曲面を形成すれば、集光効率はさらに向上する。

【0066】

また、本発明においては、基板1を絶縁性の材料により形成してもよい。

【0067】

図8は、基板1を半絶縁体により形成した変形例を表す模式断面図である。すなわち、基板1は、例えば、鉄(Fe)をドープした半絶縁InPなどの材料により形成できる。この場合には、n側電極9は、素子の表面側に設ける。

【0068】

また、本発明においては、複数の受光部を集積させることもできる。

【0069】

図9は、2つの受光部をアレイ状に集積化させた変形例を表す模式断面図である。すなわち、2つの受光部を光軸に対して平行な方向に並べ、反射面15によって、それぞれの受光部に光Lが導かれる。この場合、2つの入射光A及びBの光軸を基板1の厚み方向に並べて入射させ、それぞれ別々の受光部により検出させることができ、いわゆる「光パラレルリンク」用の受光素子アレイを得ることができる。

【0070】

またさらに、このような集積型の受光素子において、図10に例示した如く、反射面15を、それぞれの入射光に対応させた集光曲面としてもよい。すなわち、入射光Aと入射光Bとにそれぞれ対応した2つの集光曲面が形成されている。このようにすれば、検出効率を上げることができると同時に、入射光A及びBのセパレーションも改善し、いわゆる「クロストーク」を低減できる。

【0071】

さらにまた、図7に関して前述したように、p型領域5のサイズを小さくできるので、pn接合の寄生容量を減らして、素子の遮断周波数を上げることもできる。すなわち、高い検出効率で高速動作が可能なパラレルリンク用の集積型受光素子を実現できる。

【0072】

一方、本発明においては、複数の受光部を入射光の光軸に対して垂直な方向に並べることもできる。

【0073】

図11は、2つの受光部を入射光の光軸に対して垂直な方向に並べた集積型の半導体受光素子を表す模式断面図である。この場合には、2つの入射光A及びBの光軸は基板面に対して平行な方向に並べて、それぞれ反射面15により反射させ、別々の受光部に導くことができる。

【0074】

本具体例の場合には、複数の入射光の光軸を基板1の面内方向に並べるので、その光軸の間隔も自由に設定でき、クロストークを解消するために光軸の間隔を広くすることも容易である。また、本具体例の場合も、図7及び図10に表したように、入射光のそれぞれに対応して反射面15に集光曲面を形成すれば、検出効率をさらに高くし、クロストークも低減し、受光部を小さくすることにより高速化も可能となる。

【0075】

なお、図9乃至図11においては、2つの受光部を集積した受光素子を表したが、本発明はこれには限定されず、3つ以上の受光部を入射光の光軸に対して平行な方向または垂直な方向に並べてもよい。またさらに、複数の受光部を、入射光の光軸に対して平行及び垂直な方向にマトリクス状に集積してもよい。

【0076】

図12は、複数の受光部をマトリクス状に集積した半導体受光素子の模式図である。すなわち、同図(a)はその平面図、同図(b)は断面図である。

【0077】

本具体例の場合、4つの受光部が、入射光A乃至Dのそれぞれに対応してマトリクス状に集積されている。このように、入射光の光軸に対して平行及び垂直な方向に受光部を並べると、多数の受光部をコンパクトに集積することが容易となる。その結果として、多チャンネルのパラレルリンク用の半導体受光素子を極めてコンパクトに実現できる。

【0078】

また、本具体例の場合も、図示したように、入射光のそれぞれに対応して反射面15に集光曲面を形成すれば、検出効率をさらに高くし、クロストークも低減し、受光部を小さくすることにより高速化も可能となる。

【0079】

なお、図12においては、4つの受光部をマトリクス状に集積した具体例を表したが、本発明はこれには限定されず、より多数の受光部を入射光の光軸に対して平行及び垂直な方向に並べてもよい。

【0080】

以上、具体例を参照しつつ本発明の実施の形態について説明した。しかし、本発明はこれらの具体例に限定されるものではない。

【0081】

すなわち、本発明の半導体受光素子の各部の構造、形状、材料、配置関係などについては、公知の半導体受光素子あるいはその他の素子を元に当業者が適宜適用したものも包含する。例えば、本発明においては、受光部として、図示したような「プレーナ型」のpn接合の他にも、例えば、「メサ型」のpn接合を採用することもできる。また、受光素子を構成する基板や各層の材料についても、具体例として挙げたInP系以外に、GaAs系やGaN系などの各種の化合物半導体や、Si、Geなどを用いることもできる。また、基板としては、半導体以外にも、例えば、サファイアをはじめとする各種の絶縁体などを用いることもできる。

【発明の効果】

以上詳述したように、本発明によれば、受光素子の基板面に対して略平行に入射する光を傾斜した反射面により反射させて受光部において検出することにより、反射ミラーやチップキャリアなどの部品が不要となり、光通信用の受信モジュールなどの各種の光半導体装置の部品点数を削減し、結合効率も高くすることが可能となる。

【0082】

すなわち、本発明によれば、優れた性能を有する半導体受光素子を提供することが可能となり、産業上のメリットは多大である。

【図面の簡単な説明】

【図1】本発明の実施の形態にかかる半導体受光素子の要部構造を表す模式図である。

【図2】導波層を設けた半導体受光素子を表す模式断面図である。

【図3】逆メサの側面を反射面15とした場合の半導体受光素子の要部構造を例示する模式図である。

【図4】本発明の変形例の半導体受光素子を表す模式断面図である。

【図5】反射面15がやや切り立った斜面とされた変形例を表す模式断面図である。

【図6】反射面15が大きく傾斜した変形例を表す模式断面図である。

【図7】反射面15を集光曲面とした変形例を表す模式断面図である。

【図8】基板1を半絶縁体により形成した変形例を表す模式断面図である。

【図9】2つの受光部をアレイ状に集積化させた変形例を表す模式断面図である。

【図10】反射面15を、それぞれの入射光に対応させた集光曲面とした具体例を表す模式断面図である。

【図11】2つの受光部を入射光の光軸に対して垂直な方向に並べた集積型の半導体受光素子を表す模式断面図である。

【図12】複数の受光部をマトリクス状に集積した半導体受光素子の模式図である。

【図13】いわゆる「表面入射型」の半導体受光素子を表す断面図である。

【図14】いわゆる「裏面入射型」の半導体受光素子を表す断面図である。

【図15】いわゆる「導波路型」の半導体受光素子を表す模式図である。

【図16】マイクロミラーを用いた光学系を表す模式図である。

【図17】チップキャリアを用いた実装方式を表す模式図である。

【符号の説明】

1 基板

2 バッフア層

3 光吸収層

4 窓層

5 p型領域

6 保護膜

7 反射防止膜

8 p側電極

8B パッド部

9 n側電極

15 反射面

101 基板

102 バッファ層

103 光吸収層

104 窓層

210 チップキャリア

211 受光素子

212 受光素子

212 実装基板

213 反射ミラー

214 ワイヤ

A〜D、L 入射光

Claims (14)

- 上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備えたことを特徴とする半導体受光素子。

- 上面と、下面と、前記上面と前記下面との間に設けられた受光部と、第1の側面と、前記第1の側面と対向し前記上面に対して傾斜した反射面を有する第2の側面と、を備え、

前記第1の側面から入射し前記受光部と前記下面との間を前記上面に対して略平行な方向に進行する光を前記反射面において前記受光部に向けて反射させ検出可能としたことを特徴とする半導体受光素子。 - 基板と、

前記基板の主面上に設けられた半導体層と、

前記半導体層の上に設けられた受光部と、

を備え、

前記基板及び前記半導体層の側面の少なくとも一部が前記主面に対して傾斜した反射面とされ、

前記反射面と対向する側面から入射し前記基板または前記半導体層の少なくともいずれかの中を進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする半導体受光素子。 - 基板と、

前記基板の主面上に設けられた受光部と、

を備え、

前記基板の側面の一部が前記主面に対して傾斜した反射面とされ、

前記反射面と対向する側面から入射し前記主面に対して略平行な方向に進行する光を前記反射面により反射させ前記受光部に導いて検出可能としたことを特徴とする半導体受光素子。 - 基板と、

前記基板の主面上に設けられた受光部と、

前記基板の側面から入射し前記基板内を前記主面に対して略平行な方向に進行する光を前記受光部の方向に反射させる反射面と、

を備えたことを特徴とする半導体受光素子。 - 前記受光部の上に設けられた電極をさらに備え、

前記反射面により反射され前記受光部を透過した光の少なくとも一部が前記電極により反射されて前記受光部において検出可能とされたことを特徴とする請求項1〜4のいずれか1つに記載の半導体受光素子。 - 前記入射する光の光軸に対して平行な方向に沿って前記受光部が複数設けられ、

前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能とされたことを特徴とする請求項1〜6のいずれか1つに記載の半導体受光素子。 - 前記入射する光の光軸に対して垂直な方向に沿って前記受光部が複数設けられ、

前記反射面の第1の部分において反射される光と、前記第1の部分とは異なる第2の部分において反射される光とが、それぞれ前記複数の受光部のうちの異なるものにより検出可能とされたことを特徴とする請求項1〜6のいずれか1つに記載の半導体受光素子。 - 基板と、

前記基板の主面上に設けられた第1の半導体層と、

前記第1導電型の半導体層の上に設けられた光吸収層と、

前記光吸収層の上に設けられた第2の半導体層と、

を備えた半導体受光素子であって、

側面の一部が傾斜した反射面とされ、

前記反射面に対向する側面から前記基板及び前記第2の半導体層の少なくともいずれかに入射し前記主面に対して略平行方向に進行する光を前記反射面により反射させ前記光吸収層において検出可能としたことを特徴とする半導体受光素子。 - 前記基板のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なることよりも大なることを特徴とする請求項9記載の半導体受光素子。

- 前記第1の半導体層及び前記第2の半導体層のエネルギーバンドギャップは、前記光吸収層のエネルギーバンドギャップよりも大なることを特徴とする請求項9または10に記載の半導体受光素子。

- 前記第2の半導体層の上に設けられた電極をさらに備え、

前記反射面により反射され前記光吸収層を透過した光の少なくとも一部が前記電極により反射されて前記光吸収層において検出可能とされたことを特徴とする請求項9〜11のいずれか1つに記載の半導体受光素子。 - 前記反射面は、集光曲面を有することを特徴とする請求項1〜12のいずれか1つに記載の半導体受光素子。

- 前記反射面は、金属膜または誘電体多層膜を有することを特徴とする請求項1〜13のいずれか1つに記載の半導体受光素子。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002325046A JP2004158763A (ja) | 2002-11-08 | 2002-11-08 | 半導体受光素子 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002325046A JP2004158763A (ja) | 2002-11-08 | 2002-11-08 | 半導体受光素子 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2004158763A true JP2004158763A (ja) | 2004-06-03 |

Family

ID=32804400

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002325046A Pending JP2004158763A (ja) | 2002-11-08 | 2002-11-08 | 半導体受光素子 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2004158763A (ja) |

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013131637A (ja) * | 2011-12-21 | 2013-07-04 | Japan Oclaro Inc | 光モジュール |

| CN107516684A (zh) * | 2017-08-25 | 2017-12-26 | 深圳市芯思杰智慧传感技术有限公司 | 光电二极管芯片及其制作方法 |

| JP6685482B1 (ja) * | 2019-08-06 | 2020-04-22 | 三菱電機株式会社 | 半導体レーザ装置 |

| WO2022074780A1 (ja) * | 2020-10-08 | 2022-04-14 | 日本電信電話株式会社 | 半導体受光素子 |

-

2002

- 2002-11-08 JP JP2002325046A patent/JP2004158763A/ja active Pending

Cited By (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2013131637A (ja) * | 2011-12-21 | 2013-07-04 | Japan Oclaro Inc | 光モジュール |

| CN107516684A (zh) * | 2017-08-25 | 2017-12-26 | 深圳市芯思杰智慧传感技术有限公司 | 光电二极管芯片及其制作方法 |

| JP6685482B1 (ja) * | 2019-08-06 | 2020-04-22 | 三菱電機株式会社 | 半導体レーザ装置 |

| WO2022074780A1 (ja) * | 2020-10-08 | 2022-04-14 | 日本電信電話株式会社 | 半導体受光素子 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9276162B2 (en) | Semiconductor photodetector and method for manufacturing the same | |

| JP5410001B2 (ja) | シリコンベースショットキ障壁赤外線光検出器 | |

| TWI228320B (en) | An avalanche photo-detector(APD) with high saturation power, high gain-bandwidth product | |

| JP5250165B2 (ja) | 端面視光検出器 | |

| JPWO2007105593A1 (ja) | フォトダイオード、およびその製造方法、ならびに光通信デバイスおよび光インタコネクションモジュール | |

| US6737718B2 (en) | Semiconductor photodetector | |

| JP2002289904A (ja) | 半導体受光素子とその製造方法 | |

| KR102307789B1 (ko) | 후면 입사형 애벌런치 포토다이오드 및 그 제조 방법 | |

| US9406832B2 (en) | Waveguide-coupled MSM-type photodiode | |

| JP2011124450A (ja) | 半導体受光素子 | |

| JP5228922B2 (ja) | 半導体受光素子 | |

| JPH04246868A (ja) | P−i−nフォトダイオードおよびその効率を改善する方法 | |

| JP3589878B2 (ja) | 裏面入射型受光装置およびその作製方法 | |

| JP2004304187A (ja) | 受光素子及びその製造方法 | |

| JP6774792B2 (ja) | 赤外線デバイス | |

| JP2004158763A (ja) | 半導体受光素子 | |

| JP3589390B2 (ja) | 光電気集積回路およびヘテロ接合ホトトランジスタ | |

| JP7409489B2 (ja) | 受光装置 | |

| JP2004319684A (ja) | 半導体受光装置及びその製造方法 | |

| JPH04263475A (ja) | 半導体受光素子及びその製造方法 | |

| JPH0272679A (ja) | 光導波路付き半導体受光素子 | |

| JP2945438B2 (ja) | 光半導体装置及びそれを用いた受光器 | |

| JPH05102513A (ja) | 半導体受光素子 | |

| JPH0555619A (ja) | 半導体受光装置 | |

| JP4223774B2 (ja) | 半導体受光素子 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20040528 |