CN1163909C - 用于开关电流存储单元的时钟直通减少系统 - Google Patents

用于开关电流存储单元的时钟直通减少系统 Download PDFInfo

- Publication number

- CN1163909C CN1163909C CNB971991340A CN97199134A CN1163909C CN 1163909 C CN1163909 C CN 1163909C CN B971991340 A CNB971991340 A CN B971991340A CN 97199134 A CN97199134 A CN 97199134A CN 1163909 C CN1163909 C CN 1163909C

- Authority

- CN

- China

- Prior art keywords

- current

- voltage

- electrode

- coupled

- grid

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C27/00—Electric analogue stores, e.g. for storing instantaneous values

- G11C27/02—Sample-and-hold arrangements

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C27/00—Electric analogue stores, e.g. for storing instantaneous values

- G11C27/02—Sample-and-hold arrangements

- G11C27/024—Sample-and-hold arrangements using a capacitive memory element

- G11C27/028—Current mode circuits, e.g. switched current memories

Landscapes

- Control Of Electrical Variables (AREA)

- Dram (AREA)

- Analogue/Digital Conversion (AREA)

- Semiconductor Memories (AREA)

Abstract

电流单元包括串联在恒流源(51)和基准地之间的第一(M2)和第二(M1)MOS晶体管。这两个晶体管中的每一个都具有把其控制栅极耦合到其漏极的各自第一(59)和第二(63)开关。把采样和保持操作的采样阶段分割成第一和第二采样子阶段,在这两个采样子阶段期间把所保持的输入电流(Iin)加到电流单元。在第一采样子阶段期间,第二MOS晶体管(M1)记录相应于输入电流(Iin)、恒流源(51)和时钟直通误差的栅极电压。作为沟道效应的结果,在第二晶体管(M1)的漏极(62)处引起调制电压(Vmod),使用第一MOS晶体管(M2)在保持阶段期间把此调制电压(Vmod)存储和保持在第二MOS晶体管(M1)的漏极(62)。

Description

技术领域

本发明涉及时钟直通(feedthrough)误差减少的开关电流存储单元。

背景技术

在多年无人问津后,目前人们对诸如集成模拟信号处理器等集成的模拟电路越来越感兴趣。通常,这些电路是以电压域来设计的,且它们有时通过把电压从一个电容器转移到另一个电容器来实现其任务。然而,为了实现高的精度,这种方案需要大的线性集成电容器,继而还需要使用诸如双-多工艺等专门技术的高级CMOS工艺。这些专门的CMOS技术难以在VLSI甚至LSI工艺中实现。

开关电流“SI”电路是一种通过操纵电流来实现模拟功能的新电路原理。即,与电压大小相反,使用所采样的电流大小来表示信号。由于SI电路以电流域来操作,所以与基于模拟IC的更传统的电压相比,它们在更低的电源电压下操作且消耗更少的功率。更有利的是,由于SI电路通过控制电流而不是电容器的充电和放电来操纵信号,所以它们不需要高质量的线性电容器来实现高的性能,而且还可能实现较高的速度。因此,SI电路不需要专门的CMOS工艺技术并可用标准数字VLSI处理来实现。结果,SI使得可把数字和模拟功能组合在一公共的IC上。

然而,SI电路也有一些缺陷。首先,为了实现高性能的电路,每个所采样的电流幅值必须具有高的精度水平。如果使用标准电流反射镜,则电流反射镜两个支路中的晶体管必须严格匹配,以保证得到输入电流的准确输出拷贝。标准CMOS工艺不足以为高性能的SI电路实现晶体管的高度匹配。

通过使用电流存储单元来可避免晶体管匹配这种关系。如图1所示,电流存储单元(公知的电流复制器或动态电流反射镜)应能够在操作的采样阶段准确地拷贝输入电流Iin,然后在操作的保持阶段把所拷贝的电流再现为输出电流Iout。电流存储单元11可被有效地作为基于电流的采样-保持电路。在操作的第一阶段Φ1,开关13闭合,开关15断开,采样-保持控制输入端S/H被设定为采样“S”。在此期间,电流存储单元11测量输入电流Iin,并对输入电流Iin进行拷贝。在操作的第二阶段Φ2,开关13断开,开关15闭合,且S/H控制输入端被设定为保持“H”。然后,电流存储单元11将产生幅值等于测得的Iin的幅值的输出电流Iout。由于Iout根据Iin的测量值而不是直接根据Iin,所以电流存储单元11与静态元件匹配无关,因此可用于使用标准CMOS工艺的高精度应用中。

参考图2,示出基本的电流存储单元的内部图。输入电流Iin可以是双向的,但由于电流复制器10的实际上需要(即一些元件需要一直被正向偏置),所以必须使用偏置恒流源17。电流源17提供了基准电流Iref,该基准电流在被加到节点25处的Iin时保证电流复制器10总是能看见单向的电流。

在开关13闭合而开关15断开的采样阶段Φ1,电流复制器10接收节点25处的电流Iref+Iin。在保持阶段Φ2,开关13断开,开关15闭合,且电流复制器10在理想情况下保持恒定电流值Iref+Iin。恒流源17提供电流Iref,但由于开关15闭合,所以必须由Iout把输入电流的倒相拷贝-Iin提供给节点25。

在图3中示出已有技术的基本电流存储单元11的典型电路级示例。所示的电流复制器10包括一nMOS晶体管19,用于提供从节点25到地的电流通路并具有栅-漏本征电容21。开关23在采样阶段Φ1把节点25耦合到晶体管19的栅极,并在保持阶段Φ2把节点25与晶体管19的栅极隔离。

在采样阶段Φ1,开关13和23闭合,而开关15断开。输入电流Iin和基准电流Iref在节点25处求和并被加到晶体管19的漏极。由于开关23闭合,所以晶体管19起到正向偏置的连接二极管的晶体管的作用,且本征电容器21被充电到通过晶体管19产生电流Iref+Iin所需的栅极电压Vg。

在保持阶段Φ2期间,开关13和23断开,而开关15闭合。本征电容21将保持产生电流Iref+Iin所需的栅极电压Vg。实际上,晶体管19现在就象一存储nMOS晶体管。从而记录输入电流Iin。由于恒流源17提供Iref而存储晶体管19需要Iref+Iin,所以必须由输出端的负载来提供电流Iin,且输出电流Iout变为输入电流的倒相拷贝-Iin。

图3的基本电流存储单元11受到来自其实际电路结构的两个基本问题的影响。第一个问题是由沟道效应引起的晶体管19的沟道长度调制所引入的误差。沟道效应改变了晶体管19的跨导增益,从而改变了来源于给定栅极电压Vg的电流量。如果晶体管19的漏-源电压Vds在采样和保持阶段不保持恒定,则该晶体管19将受到沟道效应的影响。即,如果来自通过开关13的输入信号的晶体管19的Vds电压不同于来自通过开关15的负载信号的晶体管19的Vds电压,那么尽管晶体管19保持其栅极电压Vgs恒定,也将由于沟道效应而引入误差电流。

在

Electronics Letters,1990,Vol.26,No 19,pages 1593-1595以及

Electronics Letters,1990,Vol.26,No 5,pages 303-305中示出,使用加在节点25和存储晶体管19漏极之间简单的和调节的(regulated)级联电路(cascode),通过保持晶体管19的Vds相对恒定将减轻沟道效应,而不管节点25处的电压波动如何。Groeneveld等人的5,296,752号美国专利揭示了使用调节的级联电路的电流存储单元。

影响电流存储单元的第二个问题来自于开关23的实际情况。参考图4,在本领域中普遍的是,以nMOS晶体管27来实现开关23。晶体管27响应于控制输入端S/H,选择性地把节点25耦合到存储晶体管19的栅极。晶体管27的本征栅-源电容29把信号S/H有效地耦合到存储晶体管19的栅极。于是,当信号S/H从采样阶段变到保持阶段即从高变到低时,利用电容29把成比例的电压降传输到晶体管19的栅极。这样在晶体管19的栅极处引入第一栅极电压误差,叫做交叠电容误差。

开关晶体管27还引入了第二个误差。当控制输入端S/H把高电压加到开关晶体管27的栅极时,有一定数量的电荷q1+q2聚集在其沟道区。当使信号S/H为低时,电荷q2通过漏极离开沟道区,而电荷q1通过源极离开沟道区并重新分布于存储晶体管19的栅极。这样所引入的第二栅极误差叫做电荷注入,它与交叠电容误差一起把净栅极误差电压Vcft加在存储晶体管19的栅极。净栅极误差电压Vcft通常被叫做时钟直通误差,并可严重地限制电流存储单元的性能。

时钟直通误差的数值与开关晶体管27和存储晶体管19的相对电容有关。已发现,加上耦合在存储晶体管19的栅极和源极之间的大的实际电容器可减少但不能消除时钟直通误差。Groeneveld等人在5,296,752号美国专利中所述的电流存储单元还示出使用附加的实际电容器。然而,附加电容器的尺寸由实际情况和频率限制来限定。

在

Electronics Letters,1990,Vol.29,no.16,pages 1400-1401中,Hughes等人提出了类似于Hughes的4,958,123号美国专利中所述的电流存储单元,该存储单元通过把采样阶段Φ1分解成第一和第二采样子阶段Φ1a和Φ1b来减少时钟直通误差。

参考图5,在第一采样子阶段Φ1a期间,电流存储单元表现为以上所讨论的具有输入电流Iin和基准电流源Iref的典型电流存储单元。在此第一采样子阶段Φ1a期间,开关33、43和49闭合,而开关35和45断开。于是,pMOS晶体管31表现为由恒定电压Vref所控制的恒流源。Hughes的存储单元通过断开开关49来终止第一子阶段Φ1a,从而利用跨接在nMOS存储晶体管47的栅极和源极的电容器46以与典型电流存储单元类似的方式记录输入电流Iin、基准电流Iref和附加的第一时钟直通误差电流。

然而,与典型的电流存储单元不同的是,利用在开关49断开以及nMOS存储晶体管47已记录上述电流后的周期内保持闭合的开关43把输入电流Iin持续加到电流存储单元。

该周期构成了第二采样子阶段Φ1b。在第二采样子阶段Φ1b期间,通过断开开关33和闭合开关35把Hughes电流源Iref转换成二极管连接的pMOS晶体管。这样有效地形成了第二存储晶体管31,即使是pMOS型。二极管连接的pMOS晶体管31提供未被输入电流Iin提供的nMOS存储晶体管47所需的任何电流。即,pMOS存储晶体管提供先前由Vref所控制的基准电流以及开关49对nMOS存储晶体管47的动作所引入的附加第一时钟直通误差电流。于是,即使在nMOS存储晶体管47在第一Φ1a和第二Φ1b采样子阶段期间不发源流过相等的电流和,输入电流Iin也不受影响。

一旦确定pMOS存储晶体管,就通过断开开关43和35以及闭合开关45来开始保持阶段Φ2。这使pMOS存储晶体管31利用第二电容器37记录其电流。二极管连接的pMOS晶体管31的截止产生将被存储器37记录的附加第二传输误差。依据Hughes,连接pMOS 31漏极和nMOS存储晶体管47漏极的节点30表现为虚地,其电压保持不变,而不管增加还是除去Iin。因此,晶体管31和47的漏-源电压保持相对不变,从而减少沟道效应。Hughes还说明可使pMOS存储晶体管31所引入的第二时钟直通误差相对恒定,从而可在后面的电路级中消除该误差。

本发明的一个目的是提供一种时钟直通误差减少的电流存储单元。

本发明另一个目的是提供了一种不受存储晶体管的沟道效应的不利影响的电流存储单元。

本发明的再一个目的是提供一种电流存储单元,该单元同时补偿了时钟直通误差和沟道效应而无需附加复杂电路。

本发明的又一个目的是提供一种电路存储单元,该单元不仅仅依靠存储存储晶体管的栅-源电压来记录输入电流。

发明内容

在利用沟道效应并把它用作记录输入电流的两级采样阶段的一部分的电流存储单元中满足了以上目的。本发明的电流存储单元具有采样阶段和保持阶段,但采样阶段被分成采样收集(capture)阶段和采样修正阶段。

依据本发明的电流存储单元包括用于在采样收集和采样修正阶段把输入电流耦合到求和节点的输入开关、连续馈送到求和节点中的恒流源、用于在保持阶段期间把求和节点耦合到输出引线的输出开关、用于存储调制电压的装置以及电流复制器单元。用于存储调制电压的装置被耦合到求和节点,且在本说明书中称作调制电压存储器。调制电压存储器还与位于求和节点和基准地之间的电流复制器串联。电流复制器包括存储晶体管。

电流复制器响应于采样收集阶段,调制电压存储器响应于采样修正阶段。在采样收集阶段,把输入电流、恒流源和时钟直通误差的和记录在电流复制器中。由于输入电流仍旧被加到求和节点,所以采样修正阶段在电流复制器的存储晶体管中故意引起一定程度的沟道效应,从而足以消除记录时钟直通误差的影响。在把电流复制器耦合到调制电压存储器的节点处引起直接来自于沟道效应的漏极电压变化。此漏极电压变化被用作在电流复制器中引起的沟道效应数值的量度,以补偿时钟直通误差。

调制电压存储器通过记录漏极电压变化并在保持阶段保持漏极电压变化来响应于采样修正阶段。

在保持阶段,把沟道效应的测量值和输入电流、恒流源与时钟直通误差的和都加到电流复制器,以再现沟道效应误差消除的输入电流。

在本发明的本实施例中,以第一MOS存储晶体管来实现电流复制器,该晶体管具有把第一存储晶体管的栅极选择地耦合到其漏极的第一采样开关。以第二存储晶体管来实现电流复制器,此晶体管具有耦合到求和节点的漏极、耦合到第一存储晶体管的漏极的源极以及把第二存储晶体管的栅极选择性地耦合到其漏极的第二采样开关。

附图概述

图1是理想的电流存储单元的方框图。

图2是已有技术的基本电流存储单元。

图3是示出图2的电流复制器的已有技术的晶体管级(level)电流存储单元。

图4是示出图3的已有技术基本电流存储单元中误差源的晶体管级电路。

图5是已有技术的电流存储单元,该单元把采样-保持电流存储单元的采样阶段分成两个采样子阶段。

图6是依据本发明的电流存储单元的方框图。

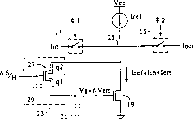

图7是依据本发明的电流存储单元的晶体管级插入示例。

图8是示出图7的存储晶体管性能的Vgs电流曲线族。

图9是依据本发明的时钟直通误差进一步衰减的电流存储单元的第二实施例。

图10是依据本发明的具有调节的级联电路输出级的电流存储单元的第三实施例。

图11是实际存储电容器进一步增大的图10的电流存储单元,

本发明的较佳实施方式

参考图6,恒流源51把恒定电流Iconst提供给电流求和节点50。输入电流Iin利用开关53进入电流求和节点50,输出电流Iout利用开关55进入电流求和节点50。用于存储调制电压57的装置和电流复制器单元61串联在电流求和节点50和基准地之间。

图6的电流存储单元的操作被分成采样阶段ΦS和保持阶段ΦH。采样阶段ΦS被进一步分成第一采样收集阶段ΦS1和第二采样修正阶段ΦS2。在采样阶段ΦS1和ΦS2期间,开关53闭合使Iin进入节点50,开关55断开把节点50与Iout隔离。

采样阶段ΦS以采样收集阶段ΦS1开始,在此期间Iin加上Iconst不受阻碍地从节点50通过调制电压存储器57和电流复制器61到达基准地。电流复制器61获得电流的测量值,ΦS1引线指令采样收集阶段结束而使电流复制器存储电流Iin+Iconst,并开始成为等效电流加上时钟直通误差的电流源。

通常,时钟直通误差将使电流复制器61把误差电流分量引入所存储的电流Iin+Iconst,但由于图6的电流存储单元仍旧处于简单采样模式且开关53保持闭合,所以进入节点50的总电流Iin+Iconst保持不变。因此,使电流复制器61在采样修正阶段ΦS2期间成为与它在采样收集阶段ΦS1期间采集的相同数量电流的源,而不管其时钟直通误差。如下所述,电流的这种强制关系使电流复制器61在节点56处感应出引起调制电压Vmod的沟道效应。调制电压Vmod是消除电流调制器61所引起的时钟直通误差的影响的有效修正电压。

一旦节点56稳定到补偿时钟直通误差所需的调制电压Vmod,则引线ΦS2指令采样修正阶段结束,从而使调制电压存储器57存储Vmod的值。采样修正阶段ΦS2的结束还指令整个采样阶段ΦS的结束,从而使开关53断开而使开关55闭合。

这样构成了保持阶段ΦS2。虽然将不再把Iin加到节点50,调制电压存储器57把节点56处电压Vmod处保持恒定。因此,使电流复制器61保持补偿和修正它在采样收集阶段ΦS1期间所引起的时钟直通误差所需的沟道效应的数量。结果,电流复制器61继续发源流过电流Iin+Iconst,而不管其时钟直通误差。由于恒流源51提供Iconst,所以Iout必须提供-Iin的值。

此外,与需要附加的电路来减少电流复制器61的沟道效应从而减轻此沟道效应所引起的任何附加误差的许多已有技术不同的是,电流存储单元实际上助长复制器单元61上的沟道效应。事实上,本发明的电流存储单元通过存储沟道效应的测量值Vmod,然后使电流复制器61在其内部感应出沟道效应的测量量,来存储和再现所拷贝的输入电流Iin。

参考图7,示出依据本发明的电流存储单元的晶体管级示例。对图7中具有与图6中所示元件类似功能的元件给出类似的标号并在以上进行了说明。

在图7中,示出的电流复制器61由存储晶体管M1构成,此晶体管利用响应于引线ΦS1的开关63把其栅极60选择性地耦合到其漏极62。存储晶体管M1的源极64被耦合到基准地,本征电容器65把其栅极60耦合到其源极64。

在此实施例中,调制电压存储器57具有类似于电流调制器61的结构,但本领域内的技术人员应理解,还可使用存储电压Vmod的其它方法。调制电压存储器57包括第二nMOS存储晶体管M2,该晶体管的漏极52耦合到电流求和节点50,其源极54耦合到节点56处M1的漏极62。利用响应于引线ΦS2的第二开关59把M2的栅极58选择性地耦合到其漏极52。

通过闭合开关53、59和63并断开开关55来开始采样收集阶段ΦS1。然后,求和节点50接收电流Iin和Iconst。电流Iin与Iconst的和通过调制电压存储器57的存储晶体管M2和电流复制器61的存储晶体管M1。

由于开关63闭合,所以M1是二极管连接的,其栅极60到源极64的电压与其漏极62到源极64的电压相同。然后,M1栅极60处的电压升高到促进漏极62到源极64的电流Iin+Iconst的值。本征电容65被充电到栅极60的电压的值。

由于开关59闭合,所以M2也是二极管连接的,其栅极58到源极54的电压也把它本身调节到促进电流Iin+Iconst的值。然而,由于M2的源极54连接到M1的漏极62,所以M2的栅极58处的电压跟踪M1的漏极62处的电压。

一旦M1的栅极60稳定到一稳定电压,则引线ΦS1通过断开开关63来指令采样收集阶段ΦS1的结束以及采样修正阶段ΦS2的开始。所有其它的开关保持不变。如上所述,开关63的断开把第一时钟直通误差电压Vcft1加到由开关63的交叠电容和电荷注入所引起的电容65。于是,存储晶体管M1想要驱动电流Iin+Iconst加上对应于其栅极处的附加时钟直通误差电压Vcft1的附加误差电流分量。但由于进入求和节点50的电流Iin和Iconst保持不变,所以使M1继续发源流过相同的电流Iin+Iconst,而不管第一时钟直通误差电压Vcft1。

这意味着,虽然M1起先对给定的栅极电压Vg发源流过电流Iin+Iconst,但它现在必须对另一个栅极电压Vg+Vcft1发源流过相同的电流Iin+Iconst。为了这样做,必须改变M1的跨导增益。这是由M1沟道效应的作用而带来的。即,把M1中反向沟道的尺寸调节到实现新的跨导增益gm。然后,新的gm使M1的漏极62处的电压发生变化。实际上,漏极62处的电压变为补偿及修正M1的时钟直通误差Vcft1所需的沟道效应量的量度,且保持了恒定电流Iin+Iconst。

图8中示出M1上沟道效应的效果。在图8中,对M1的两个栅-源电压VgsM1示出晶体管M1的漏-源电流IdsM1对漏-源电压VdsM1的特性曲线。

曲线VgsM1ΦS1示出采样收集阶段ΦS1结束时M1中的电流曲线。即,VgsM1ΦS1代表M1处的栅极电压升高到促进传导电流Iin+Iconst的值时采样收集ΦS1阶段结束时M1上的栅极电压。一旦M1的栅极电压稳定到栅极值VgsM1ΦS1,则其漏极电压将达到Vdsinitial的相应初始值。这示为图上的点“A”。

在开关63断开而开始采样修正阶段ΦS2时,把第一时钟直通误差电压Vcft1加到M1的栅极电压。曲线VgsM1ΦS2表示此新的栅极电压而且等于采样收集阶段VgsM1ΦS1结束时的栅极电压加上Vcft1。

在图8中,假设以nMOS晶体管来实现图7的开关63,因此进一步假设Vcft1具有负的值。结果,图8示出Vcft1使栅极电压M1下降。

这个假设基于两个因素。一个是,如果开关63是nMOS器件,则它将响应于引线ΦS1从高变到低而断开。这样会由于开关23和存储晶体管M1的交叠电容而使M1的栅极电压成比例地下降。第二,如果开关23是一nMOS器件,则因开关23断开所引起的M1栅极处的电荷注入将导致负电荷电子的增加,这些电子将进一步降低M1的栅极电压。然而,作这些假设纯粹是示意性的,且Vcft1对本发明来说不是决定性的。

在以图8中的点“B”表示的采样修正阶段ΦS2开始时,开关63已断开,且M1的栅极电压下降到新的值VgsM1ΦS2。对于给定的恒定漏-源电压Vdsinitial,M1栅极电压的下降同样将引起M1漏极电流的下降,即从操作点“A”处的初始值Iin+Iconst下降到操作点“B”处减少了误差电流Icft1的值。

然而,由于使本发明电流单元中的M1保持恒定电流Iin+Iconst而不管其栅极电压中的变化,所以在M1中引起沟道效应。因此,M1必须对给定的较低栅极电压流过更多的电流。结果,必须调节其跨导增益,在此情况下,此跨导增益是增加的,这将使其漏极电压被相应地调制即升高到操作点“C”处的新值Vdsfinal。在操作点“C”处M1的漏极电流恢复到其初始值Iin+Iconst,最终的漏极电压Vdsfinal是M1补偿开关63所引起的时钟直通误差Vcft1所需的新跨导增益的指示。实际上,Vdsfinal和Vdsinitial之差是修正M1的时钟直通误差Vcft1所需的跨导增益即沟道效应范围的变化的量度。

M1漏极62处的调制漏极电压Vdsfinal在图7中表示为Vmod。如上所述,M2的栅极58的电压跟踪M1的漏极62的电压。因此,M2的栅极58的电压随着M1的漏极62的电压被调节即调制类似的数量,M2的栅极58的电压变为Vmod。

在采样修正阶段ΦS1的结束时,开关59和53断开,开关55闭合。开关59的断开引起M2栅极58的电压被存储在本征电容67中,该电压保持修正电压Vmod的量值。通过保持M2栅极58的电压恒定,电容67把Vmod有效地保持恒定,从而使M1维持保持电流Iin+Iconst所需的沟道效应的数量。换句话说,本发明的电流存储单元通过存储存储晶体管M1的漏极电压来存储输入电流。

电容67还存储M2的栅极58处由开关59所引起的第二时钟直通误差Vcft2,该误差把误差电压引入节点56处的Vmod。虽然由开关59所引起的M2上的电荷注入可与由开关63引起的M1上的电荷注入相同,但第二时钟直通误差Vcft2对通过M2和M1的Ids电流的影响比Vcft1产生的影响低得多。

这是由于几个综合因素,但如果假定通过M1和M2的电流由Ids=K1(Vgs-Vth)2(1+K2Vds)确定,K1是尺寸与技术的函数,K2是沟道效应与阈值电压Vth的函数,则一般将不可能给出第二时钟直通误差Vcft2对通过M2和M1的Ids电流的影响减少的精确数量。精确的误差减少与各种电压值、电流、K1、K2和所使用的技术有关,但已发现,由Vcft2所引入的电流误差一般比只作用于M1而非M2上的Vcft1所引起的电流误差小10到100倍。通过观察第二时钟直通误差Vcft2分布在两个存储晶体管M1和M2上,且M2电极处的电压值比M1的电压值高得多从而时钟直通误差电压对M2的相对影响成比例的减少,可获得Vcft2对M2的影响减少的一般感觉。

于是,图7的电流存储单元通过存储电流复制器的存储晶体管M1的栅-源电压来再现输入电流甚至没有已有技术那样多,但宁可说是通过存储M1的漏-源电压来再现输入电流。

图9中示出依据本发明的电流单元的第二实施例。对具有与图7实施例中的元件相同功能的元件给出类似的标号,并在以上进行了说明。

在图9中,实际电容器66被耦合在M1的栅极60和基准地之间。如上所述,使用实际电容器减少了M1的时钟直通误差。如上所述,M2存储在M1的漏极62处取得的来自于M1上沟道效应的修正调制电压Vmod,但虽然由于M2的作用消除了M1的时钟直通误差,但使用电容器66减少了留在M1中的修正沟道效应的数量,从而减少M1的漏极62处的电压调制。电压调制的减少意味着,M2更能补偿M1的时钟直通误差。

还把第二实际电容器68耦合在M2的栅极58和相对地之间。第二实际电容器68不仅响应于开关59减少了M2所经历的第二时钟直通误差,而且还有助于存储和保持M2的栅极58处的修正调制电压Vmod。

参考图10,对具有与图7中的元件相同功能的所有的元件给出类似的标号,并在以上进行了说明。在图10中,调节的级联电路81被插在M2的漏极52和求和节点50之间。调节的级联电路81极大地增加了电流存储单元的输出阻抗。必须强调的是,如上所述,虽然一般在已有技术的电流存储单元中为了减少电流复制器存储晶体管M1的沟道效应而使用调节的级联电路,但把图10中的调节的级联电路81耦合到调制电压存储晶体管M2,而不是电流复制器存储晶体管M1,这样,由调节的级联电路81而使M1的漏极62的电压不保持固定,可响应于M1上的沟道效应自由地调节其电压值。

在本发明中,调节的级联电路81在增强输出阻抗和降低反馈电容特性的所有场效应晶体管的模拟电路中有更普遍的应用。通过在M2处使用级联电路级,图10的电流存储单元可实现更好的频率响应并以在求和节点50处摆动的更大的电压下进行操作。由于开关59把M2的栅极58选择性地耦合到求和节点50,所以调节的级联电路81包含在M2的二极管连接中。因此,当开关59闭合时,调节的级联电路81用作调节的级联电路电流反射镜的增强型输入级。当开关59断开时且电流存储单元进入保持阶段ΦH时,调节的级联电路81就象调节的级联电路电流源。

与使用简单的级联电路相比,使用调节的级联电路81提供了更好的性能,但本领域内的技术人员会认为无论使用任何简单或调节的级联电路都将增强M2的性能。在图10中,由于调节的级联电路在采样阶段ΦS1和ΦS2期间从节点50和M2的栅极58提供较低的输入电压降,同时在保持阶段ΦH提供了较大的输出阻抗,较大的电压摆动且较低的输出电容。这样,可把Iout加到不确定的负载,而不必太在意由负载在节点50上所引起的负载效应。换句话说,调节的级联电路81在M2处增强了电流存储单元的输出级,而无需防止电流复制器存储晶体管M1经历沟道效应。

参考图11,对具有与图10中的元件相同功能的所有的元件给出类似的标号,并在以上进行了说明。

在图11中,图9中所示的实际电容器66和68被分别耦合到M1的栅极60和M2的栅极58。此外,调节的级联电路81插在M2的漏极52和节点50之间,如上所述,电容器66和68减少了M1和M2的时钟直通误差,调节的级联电路增加了M2的输出阻抗。

Claims (20)

1.一种电流存储单元,其特征在于包括:

馈送电流到求和节点中的恒流源;

用于把输入电流选择性地耦合到所述求和节点的输入切换装置,所述输入切换装置把所述求和节点处的求和电流有效地达到等于所述恒流源电流和所述输入电流的和;

用于把所述求和节点选择性地耦合到输出引线的输出切换装置;

具有输入电极、输出电极和控制电极的电流复制器,所述电流复制器响应于所述控制电极在所述输入电极和所述输出电极之间有效地建立电流通路,所述控制电极还有用于调制所述电流通路,所述输入电极被耦合到接收所述和电流,所述输出电极被耦合到基准地;

用于把所述控制电极选择性地耦合到所述输入电极的控制开关,当所述控制开关闭合时所述开关在所述控制电极处有效地引起控制电压,所述控制电压与所述和电流有关,在所述控制开关断开时所述控制开关还有效地把误差电压引入所述控制电压;

耦合在所述控制电极和所述基准地之间的第一电压存储装置,当所述控制开关断开时所述第一电压存储装置有效地存储和保持所述控制电极处的所述控制电压;

响应于所述控制开关的断开在所述输入电极处产生调制电压的装置,所述调制电压有效地补偿所述误差电压并保持所述输入电极处的所述和电流不变;以及

耦合在所述输入电极和所述基准地之间的第二电压存储装置,所述第二电压存储装置有效地存储和保持所述第一输入电极处的所述调制电压,所述输入切换装置响应于各采样和保持阶段而把所述输入电流从所述求和节点中去耦合。

2.如权利要求1所述的电流存储单元,其特征在于所述第二电压存储装置包括电容器和具有漏极、源极和控制栅极的MOS晶体管,所述漏极被耦合到所述求和节点,所述源极被耦合到所述电流复制器的所述输入电极,所述电容器被耦合在所述控制栅极和所述基准地之间。

3.如权利要求2所述的电流存储单元,其特征在于所述第二电压存储装置还包括把所述控制栅极选择性地耦合到所述求和节点的第二控制开关,所述第二控制开关由另一个各自采样和保持阶段来控制。

4.如权利要求2所述的电流存储单元,其特征在于所述电容器是实际电容器和所述MOS晶体管的本征电容中的一种。

5.如权利要求1所述的电流存储单元,其特征在于所述第一电压存储装置包括耦合在所述控制电极和所述基准地之间的电容器。

6.如权利要求1所述的电流存储单元,其特征在于所述电流复制器包括具有漏极、源极和控制栅极的MOS晶体管,所述漏极被耦合到所述输入电极,所述源极被耦合到所述输出电极,所述控制栅极响应于所述控制电极。

7.如权利要求6所述电流存储单元,其特征在于用于产生调制电压的所述装置包括所述MOS晶体管中的沟道效应。

8.如权利要求7所述的电流存储单元,其特征在于用于产生调制电压的所述装置调制所述MOS晶体管的跨导增益。

9.如权利要求1所述的电流存储单元,其特征在于所述控制开关是一MOS晶体管。

10.一种具有第一采样阶段、第二采样阶段和保持阶段的电流存储单元,其特征在于包括:

馈送电流到求和节点中的恒流源;

被选择性地加到所述求和节点的输入电流;

具有第一漏极、第一源极和第一控制栅极的第一MOS晶体管,所述第一控制栅极有效地引起具有跨导增益的反向沟道并把所述第一漏极电气耦合到所述第一源极,所述第一漏极被耦合接收等于所述恒流源和所述输入电流的和的和电流;

用于在所述第一采样阶段把所述第一控制栅极选择性地耦合到所述第一漏极并在所述第二采样阶段把所述第一控制栅极与所述第一漏极分开的开关,所述开关还在所述第一采样阶段期间在所述第一控制栅极处有效地引起促进所述跨导增益和所述和电流的栅极电压,并在所述第二采样阶段期间把一误差电压有效地引入所述第一栅极电压;

用于调制所述反向沟道的跨导增益从而补偿所述误差电压并在所述第二采样阶段保持所述漏极电流不变的装置,用于调制所述跨导增益的所述装置还在所述第一漏极处产生补偿电压;以及

用于在所述保持阶段记录和保持所述第一漏极处的所述补偿电压的装置,响应于所述保持阶段而把所述输入电流与所述求和节点分开。

11.如权利要求10所述的电流存储单元,其特征在于用于调制所述反向沟道的所述跨导增益的所述装置包括在所述第一MOS晶体管中引起沟道效应。

12.如权利要求10所述的电流存储单元,其特征在于用于记录和保持所述补偿电压的所述装置串联在所述求和节点和所述第一漏极之间。

13.如权利要求12所述的电流存储单元,其特征在于用于记录和保持所述补偿电压的所述装置包括具有第二漏极、第二源极和第二控制栅极的第二MOS晶体管,所述第二漏极被耦合到所述求和节点,所述第二源极被耦合到所述第一漏极。

14.如权利要求13所述的电流存储单元,其特征在于用于记录和保持所述补偿电压的所述装置还包括用于把所述第二控制栅极选择性地耦合到所述求和节点的第二开关。

15.如权利要求14所述的电流存储单元,其特征在于用于记录和保持所述补偿电压的所述装置还包括耦合在所述第二控制栅极和基准地之间的电容。

16.如权利要求15所述的电流存储单元,其特征在于所述电容是所述第二MOS晶体管的本征电容和实际电容器中的一种。

17.如权利要求14所述的电流存储单元,其特征在于用于记录和保持所述补偿电压的所述装置还包括耦合在所述求和节点和所述第二漏极之间的级联电路。

18.如权利要求17所述的电路单元,其特征在于所述级联电路是简单级联电路和调节的级联电路中的一种。

19.如权利要求10所述的电流存储单元,其特征在于所述第一MOS晶体管包括耦合在所述第一控制栅极和所述第一源极之间的电容,所述电容有效地存储所述栅极电压。

20.如权利要求19所述的电流存储单元,其特征在于所述电容是所述第一MOS晶体管的本征电容和实际电容器中的一种。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/714,376 | 1996-09-16 | ||

| US08/714,376 US5783952A (en) | 1996-09-16 | 1996-09-16 | Clock feedthrough reduction system for switched current memory cells |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1234902A CN1234902A (zh) | 1999-11-10 |

| CN1163909C true CN1163909C (zh) | 2004-08-25 |

Family

ID=24869791

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB971991340A Expired - Fee Related CN1163909C (zh) | 1996-09-16 | 1997-09-04 | 用于开关电流存储单元的时钟直通减少系统 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US5783952A (zh) |

| EP (1) | EP0925588B1 (zh) |

| JP (1) | JP2001523371A (zh) |

| KR (1) | KR100466082B1 (zh) |

| CN (1) | CN1163909C (zh) |

| DE (1) | DE69717469T2 (zh) |

| HK (1) | HK1021064A1 (zh) |

| TW (1) | TW337019B (zh) |

| WO (1) | WO1998011554A1 (zh) |

Families Citing this family (57)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB9720740D0 (en) * | 1997-10-01 | 1997-12-03 | Philips Electronics Nv | Switched-current memory |

| US6028466A (en) * | 1998-02-05 | 2000-02-22 | Lucent Technologies Inc. | Integrated circuit including high transconductance voltage clamp |

| US6307406B1 (en) * | 1998-09-25 | 2001-10-23 | Lucent Technologies, Inc. | Current comparator for current mode circuits |

| JP4193452B2 (ja) * | 2001-08-29 | 2008-12-10 | 日本電気株式会社 | 電流負荷デバイス駆動用半導体装置及びそれを備えた電流負荷デバイス |

| CN100382130C (zh) * | 2001-08-29 | 2008-04-16 | 日本电气株式会社 | 用于驱动电流负载器件的半导体器件及提供的电流负载器件 |

| US7365713B2 (en) | 2001-10-24 | 2008-04-29 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device and driving method thereof |

| US7456810B2 (en) | 2001-10-26 | 2008-11-25 | Semiconductor Energy Laboratory Co., Ltd. | Light-emitting device and driving method thereof |

| US7576734B2 (en) * | 2001-10-30 | 2009-08-18 | Semiconductor Energy Laboratory Co., Ltd. | Signal line driving circuit, light emitting device, and method for driving the same |

| US7742064B2 (en) | 2001-10-30 | 2010-06-22 | Semiconductor Energy Laboratory Co., Ltd | Signal line driver circuit, light emitting device and driving method thereof |

| TWI261217B (en) * | 2001-10-31 | 2006-09-01 | Semiconductor Energy Lab | Driving circuit of signal line and light emitting apparatus |

| TWI256607B (en) | 2001-10-31 | 2006-06-11 | Semiconductor Energy Lab | Signal line drive circuit and light emitting device |

| US6927618B2 (en) | 2001-11-28 | 2005-08-09 | Semiconductor Energy Laboratory Co., Ltd. | Electric circuit |

| JP2003283271A (ja) * | 2002-01-17 | 2003-10-03 | Semiconductor Energy Lab Co Ltd | 電気回路 |

| JP4271479B2 (ja) * | 2003-04-09 | 2009-06-03 | 株式会社半導体エネルギー研究所 | ソースフォロワ及び半導体装置 |

| TW591586B (en) * | 2003-04-10 | 2004-06-11 | Toppoly Optoelectronics Corp | Data-line driver circuits for current-programmed electro-luminescence display device |

| JP4543625B2 (ja) * | 2003-05-27 | 2010-09-15 | ソニー株式会社 | 表示装置 |

| US6844759B2 (en) * | 2003-06-10 | 2005-01-18 | Concordia University | Method and circuit for eliminating charge injection from transistor switches |

| KR100515300B1 (ko) | 2003-10-07 | 2005-09-15 | 삼성에스디아이 주식회사 | 전류 샘플/홀드 회로와 전류 샘플/홀드 방법 및 이를이용한 역다중화 장치와 디스플레이 장치 |

| CA2490858A1 (en) | 2004-12-07 | 2006-06-07 | Ignis Innovation Inc. | Driving method for compensated voltage-programming of amoled displays |

| US7068024B1 (en) * | 2004-12-30 | 2006-06-27 | Taiwan Semiconductor Manufacturing Company, Ltd. | Voltage regulator having positive temperature coefficient for self-compensation and related method of regulating voltage |

| JP4779113B2 (ja) * | 2005-02-09 | 2011-09-28 | 国立大学法人 名古屋工業大学 | サンプルホールド回路 |

| CN102663977B (zh) | 2005-06-08 | 2015-11-18 | 伊格尼斯创新有限公司 | 用于驱动发光器件显示器的方法和系统 |

| US9269322B2 (en) | 2006-01-09 | 2016-02-23 | Ignis Innovation Inc. | Method and system for driving an active matrix display circuit |

| US9489891B2 (en) | 2006-01-09 | 2016-11-08 | Ignis Innovation Inc. | Method and system for driving an active matrix display circuit |

| EP1971975B1 (en) | 2006-01-09 | 2015-10-21 | Ignis Innovation Inc. | Method and system for driving an active matrix display circuit |

| FR2899841B1 (fr) * | 2006-04-12 | 2008-07-04 | Bic Soc | Pointe d'ecriture pour effectuer des traces de differentes largeurs et instrument d'ecriture comprenant une telle pointe |

| WO2009127065A1 (en) | 2008-04-18 | 2009-10-22 | Ignis Innovation Inc. | System and driving method for light emitting device display |

| CA2637343A1 (en) | 2008-07-29 | 2010-01-29 | Ignis Innovation Inc. | Improving the display source driver |

| US9370075B2 (en) | 2008-12-09 | 2016-06-14 | Ignis Innovation Inc. | System and method for fast compensation programming of pixels in a display |

| US8633873B2 (en) * | 2009-11-12 | 2014-01-21 | Ignis Innovation Inc. | Stable fast programming scheme for displays |

| CA2687631A1 (en) | 2009-12-06 | 2011-06-06 | Ignis Innovation Inc | Low power driving scheme for display applications |

| CA2696778A1 (en) | 2010-03-17 | 2011-09-17 | Ignis Innovation Inc. | Lifetime, uniformity, parameter extraction methods |

| KR101132216B1 (ko) * | 2010-12-02 | 2012-04-02 | 금오공과대학교 산학협력단 | 라우팅 더미 커패시터를 구비한 디지털 아날로그 변환기 |

| US9351368B2 (en) | 2013-03-08 | 2016-05-24 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US20140368491A1 (en) | 2013-03-08 | 2014-12-18 | Ignis Innovation Inc. | Pixel circuits for amoled displays |

| US9886899B2 (en) | 2011-05-17 | 2018-02-06 | Ignis Innovation Inc. | Pixel Circuits for AMOLED displays |

| CN106898307B (zh) | 2011-05-28 | 2021-04-27 | 伊格尼斯创新公司 | 在以交错模式实施的显示器上显示图像的方法 |

| US9747834B2 (en) | 2012-05-11 | 2017-08-29 | Ignis Innovation Inc. | Pixel circuits including feedback capacitors and reset capacitors, and display systems therefore |

| CN102915071A (zh) * | 2012-10-23 | 2013-02-06 | 南京航空航天大学 | 面向混合信号处理的低电压低功耗开关电流采样保持电路 |

| US8975948B2 (en) * | 2012-11-15 | 2015-03-10 | Texas Instruments Incorporated | Wide common mode range transmission gate |

| US9336717B2 (en) | 2012-12-11 | 2016-05-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9786223B2 (en) | 2012-12-11 | 2017-10-10 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| US9721505B2 (en) | 2013-03-08 | 2017-08-01 | Ignis Innovation Inc. | Pixel circuits for AMOLED displays |

| CA2894717A1 (en) | 2015-06-19 | 2016-12-19 | Ignis Innovation Inc. | Optoelectronic device characterization in array with shared sense line |

| KR102158382B1 (ko) | 2013-08-22 | 2020-09-22 | 삼성디스플레이 주식회사 | 전류 메모리 셀 및 이를 포함하는 전류 모드 디지털 아날로그 컨버터 |

| CA2873476A1 (en) | 2014-12-08 | 2016-06-08 | Ignis Innovation Inc. | Smart-pixel display architecture |

| CA2886862A1 (en) | 2015-04-01 | 2016-10-01 | Ignis Innovation Inc. | Adjusting display brightness for avoiding overheating and/or accelerated aging |

| CA2898282A1 (en) | 2015-07-24 | 2017-01-24 | Ignis Innovation Inc. | Hybrid calibration of current sources for current biased voltage progra mmed (cbvp) displays |

| US10373554B2 (en) | 2015-07-24 | 2019-08-06 | Ignis Innovation Inc. | Pixels and reference circuits and timing techniques |

| US10657895B2 (en) | 2015-07-24 | 2020-05-19 | Ignis Innovation Inc. | Pixels and reference circuits and timing techniques |

| CA2908285A1 (en) | 2015-10-14 | 2017-04-14 | Ignis Innovation Inc. | Driver with multiple color pixel structure |

| US9715941B2 (en) * | 2015-10-30 | 2017-07-25 | Sony Semiconductor Solutions Corporation | State machine controlled MOS linear resistor |

| US9728271B2 (en) * | 2015-10-30 | 2017-08-08 | Sony Semiconductor Solutions Corporation | Charge injection noise reduction in sample-and-hold circuit |

| CN106415282B (zh) | 2016-08-16 | 2019-06-21 | 深圳市汇顶科技股份有限公司 | 一种电流采样保持电路及信号采集系统 |

| KR101767172B1 (ko) | 2016-09-12 | 2017-08-10 | 서울과학기술대학교 산학협력단 | 클락-피드스루(clock-feedthrough) 최소화하기 위한 전류메모리 회로 |

| US11469223B2 (en) * | 2019-05-31 | 2022-10-11 | Analog Devices International Unlimited Company | High precision switched capacitor MOSFET current measurement technique |

| CN115622549B (zh) * | 2022-12-19 | 2023-02-28 | 晟矽微电子(南京)有限公司 | 开关电路、数模转换器、芯片及电子设备 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4958123A (en) * | 1987-12-23 | 1990-09-18 | U.S. Philips Corporation | Circuit arrangement for processing sampled analogue electrical signals |

| US4937469A (en) * | 1988-08-30 | 1990-06-26 | International Business Machines Corporation | Switched current mode driver in CMOS with short circuit protection |

| GB2231423A (en) * | 1989-05-10 | 1990-11-14 | Philips Electronic Associated | Integrator circuit |

| GB2231424A (en) * | 1989-05-10 | 1990-11-14 | Philips Electronic Associated | Integrator circuit |

| GB2234835A (en) * | 1989-08-07 | 1991-02-13 | Philips Electronic Associated | Intergrator circuit |

| GB2235799A (en) * | 1989-09-06 | 1991-03-13 | Philips Electronic Associated | Differentiator circuit |

| US5296752A (en) * | 1991-05-08 | 1994-03-22 | U.S. Philips Corporation | Current memory cell |

| GB9204763D0 (en) * | 1992-03-05 | 1992-04-15 | Philips Electronics Uk Ltd | Signal processing arrangements |

| GB9301463D0 (en) * | 1993-01-26 | 1993-03-17 | Philips Electronics Uk Ltd | Current memory |

| GB9424810D0 (en) * | 1994-12-08 | 1995-02-08 | Philips Electronics Uk Ltd | Current comparator arrangement |

| GB9517787D0 (en) * | 1995-08-31 | 1995-11-01 | Philips Electronics Uk Ltd | Current memory |

-

1996

- 1996-09-16 US US08/714,376 patent/US5783952A/en not_active Expired - Lifetime

-

1997

- 1997-09-04 JP JP51370398A patent/JP2001523371A/ja not_active Ceased

- 1997-09-04 DE DE69717469T patent/DE69717469T2/de not_active Expired - Lifetime

- 1997-09-04 WO PCT/US1997/015590 patent/WO1998011554A1/en active IP Right Grant

- 1997-09-04 CN CNB971991340A patent/CN1163909C/zh not_active Expired - Fee Related

- 1997-09-04 EP EP97940818A patent/EP0925588B1/en not_active Expired - Lifetime

- 1997-09-04 KR KR10-1999-7002163A patent/KR100466082B1/ko not_active IP Right Cessation

- 1997-09-05 TW TW086112807A patent/TW337019B/zh not_active IP Right Cessation

-

2000

- 2000-01-05 HK HK00100055A patent/HK1021064A1/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| CN1234902A (zh) | 1999-11-10 |

| TW337019B (en) | 1998-07-21 |

| EP0925588B1 (en) | 2002-11-27 |

| DE69717469T2 (de) | 2003-06-26 |

| WO1998011554A1 (en) | 1998-03-19 |

| HK1021064A1 (en) | 2000-05-26 |

| JP2001523371A (ja) | 2001-11-20 |

| EP0925588A1 (en) | 1999-06-30 |

| DE69717469D1 (de) | 2003-01-09 |

| EP0925588A4 (zh) | 1999-07-21 |

| KR20000036128A (ko) | 2000-06-26 |

| US5783952A (en) | 1998-07-21 |

| KR100466082B1 (ko) | 2005-01-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1163909C (zh) | 用于开关电流存储单元的时钟直通减少系统 | |

| KR960005360B1 (ko) | 샘플된 아날로그 전기 신호를 처리하기 위한 회로 장치 | |

| US4622480A (en) | Switched capacitor circuit with high power supply projection ratio | |

| CN1755833A (zh) | 用于在低电源电压操作中产生电压参考的浮动栅极模拟电压电平移位电路和方法 | |

| US4843265A (en) | Temperature compensated monolithic delay circuit | |

| US20060049857A1 (en) | Switch linearized track and hold circuit for switch linearization | |

| US5463394A (en) | Current switch for a high speed DAC | |

| CN1745354A (zh) | 浮动栅参考电压生成器的输出电压补偿电路和方法 | |

| US20050127889A1 (en) | Reference power supply circuit for semiconductor device | |

| US5684738A (en) | Analog semiconductor memory device having multiple-valued comparators and floating-gate transistor | |

| CN1266838C (zh) | 低电源电压下亦可产生稳定恒流的半导体集成电路器件 | |

| CN200983116Y (zh) | 金属氧化物半导体电压基准电路 | |

| US5623306A (en) | Dark current suppression for solid state image sensing device | |

| JP3313125B2 (ja) | Ccd型固体撮像素子 | |

| CN1010446B (zh) | 读出放大器 | |

| US4455493A (en) | Substrate bias pump | |

| JPS6118210A (ja) | 電荷転送アナログ比較器及び該比較器を使用するデバイス | |

| US5206553A (en) | Clamping circuit | |

| US20090039924A1 (en) | Systems and methods for reducing distortion in semiconductor based sampling systems | |

| CN1214393C (zh) | 数据确定电路及数据确定方法 | |

| JPH11163647A (ja) | スイッチトキャパシタ回路 | |

| JP2004129276A (ja) | トラックアンドホールド回路 | |

| US5065056A (en) | Clamping circuit | |

| KUNTMAN | Accurate active-feedback CMOS cascode current mirror with improved output swing | |

| JP2512723B2 (ja) | 光電変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| REG | Reference to a national code |

Ref country code: HK Ref legal event code: GR Ref document number: 1021064 Country of ref document: HK |

|

| C56 | Change in the name or address of the patentee | ||

| CP03 | Change of name, title or address |

Address after: American California Patentee after: Atmel Corp. Address before: American California Patentee before: Atmel Corporation |

|

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20040825 Termination date: 20130904 |