CN101819931B - 制造半导体装置的方法 - Google Patents

制造半导体装置的方法 Download PDFInfo

- Publication number

- CN101819931B CN101819931B CN201010119463.1A CN201010119463A CN101819931B CN 101819931 B CN101819931 B CN 101819931B CN 201010119463 A CN201010119463 A CN 201010119463A CN 101819931 B CN101819931 B CN 101819931B

- Authority

- CN

- China

- Prior art keywords

- make

- semiconductor device

- silicide layer

- water

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 34

- 238000004519 manufacturing process Methods 0.000 title claims abstract description 16

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims abstract description 78

- 229910021332 silicide Inorganic materials 0.000 claims abstract description 67

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 claims abstract description 67

- 230000002829 reductive effect Effects 0.000 claims abstract description 52

- 238000000034 method Methods 0.000 claims abstract description 45

- 238000004140 cleaning Methods 0.000 claims abstract description 32

- 238000001312 dry etching Methods 0.000 claims abstract description 19

- 238000005530 etching Methods 0.000 claims description 28

- 239000002184 metal Substances 0.000 claims description 20

- 229910052751 metal Inorganic materials 0.000 claims description 20

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 claims description 18

- 230000004888 barrier function Effects 0.000 claims description 16

- 239000007789 gas Substances 0.000 claims description 13

- 229910005883 NiSi Inorganic materials 0.000 claims description 10

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 9

- 229910021529 ammonia Inorganic materials 0.000 claims description 9

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 claims description 7

- 230000015572 biosynthetic process Effects 0.000 claims description 7

- 238000001035 drying Methods 0.000 claims description 7

- 239000001257 hydrogen Substances 0.000 claims description 7

- 229910052739 hydrogen Inorganic materials 0.000 claims description 7

- 239000007788 liquid Substances 0.000 claims description 7

- 230000009467 reduction Effects 0.000 claims description 7

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 7

- 230000001590 oxidative effect Effects 0.000 claims description 5

- 239000007864 aqueous solution Substances 0.000 claims description 4

- 229910052581 Si3N4 Inorganic materials 0.000 claims 1

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical group N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims 1

- 230000008569 process Effects 0.000 abstract description 10

- 239000010410 layer Substances 0.000 description 65

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 16

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 14

- 238000004380 ashing Methods 0.000 description 9

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 description 8

- 230000003647 oxidation Effects 0.000 description 8

- 238000007254 oxidation reaction Methods 0.000 description 8

- 229960002163 hydrogen peroxide Drugs 0.000 description 7

- 238000011010 flushing procedure Methods 0.000 description 6

- 239000000758 substrate Substances 0.000 description 5

- 235000011114 ammonium hydroxide Nutrition 0.000 description 4

- 238000005868 electrolysis reaction Methods 0.000 description 4

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 3

- QGZKDVFQNNGYKY-UHFFFAOYSA-O Ammonium Chemical compound [NH4+] QGZKDVFQNNGYKY-UHFFFAOYSA-O 0.000 description 2

- 229910004298 SiO 2 Inorganic materials 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000000137 annealing Methods 0.000 description 2

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 239000003792 electrolyte Substances 0.000 description 2

- 238000000635 electron micrograph Methods 0.000 description 2

- 239000012535 impurity Substances 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 239000001301 oxygen Substances 0.000 description 2

- 229910052760 oxygen Inorganic materials 0.000 description 2

- 230000001105 regulatory effect Effects 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 238000005245 sintering Methods 0.000 description 2

- 206010010144 Completed suicide Diseases 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- 238000010306 acid treatment Methods 0.000 description 1

- 239000011260 aqueous acid Substances 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000004090 dissolution Methods 0.000 description 1

- 239000011229 interlayer Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 238000005554 pickling Methods 0.000 description 1

- 238000009832 plasma treatment Methods 0.000 description 1

- 230000000717 retained effect Effects 0.000 description 1

- 238000001878 scanning electron micrograph Methods 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

- H01L21/0206—Cleaning during device manufacture during, before or after processing of insulating layers

- H01L21/02063—Cleaning during device manufacture during, before or after processing of insulating layers the processing being the formation of vias or contact holes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76814—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics post-treatment or after-treatment, e.g. cleaning or removal of oxides on underlying conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/285—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation

- H01L21/28506—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers

- H01L21/28512—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table

- H01L21/28518—Deposition of conductive or insulating materials for electrodes conducting electric current from a gas or vapour, e.g. condensation of conductive layers on semiconductor bodies comprising elements of Group IV of the Periodic Table the conductive layers comprising silicides

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Abstract

一种制造半导体装置的方法,包括:通过干法蚀刻去除在含Ni硅化物层上表面形成的绝缘层,由此使含Ni硅化物层至少部分地露出;以及使用具有还原作用的还原水清洗含Ni硅化物层的露出部。

Description

本申请基于日本专利申请No.2009-046801,其内容通过引用结合于此。

技术领域

本发明涉及一种制造半导体装置的方法。

背景技术

涉及到半导体装置的尺寸缩小、集成度的提高以及操作速度的提高,一直以来不断地要求在栅电极上和源/漏(杂质扩散层)区上形成的硅化物具有更低的电阻率。因此,这种情况促使采用包含NiSi、NiPtSi等的含Ni硅化物膜。

另一方面,为了防止薄硅化物膜的穿透,并且为了保持侧壁的必要厚度,也要求硅化物膜在用于形成接触插塞的干法蚀刻工艺中确保大的选择性。然而,这种情况使得更难以同时满足去除工艺中产生的沉积物以及硅化物的氧化溶解的要求。

作为在硅化物层上形成的绝缘膜中形成接触孔的示例性方法,日本专利特许公布No.2007-234760描述了如下所述技术。

根据日本专利特许公布No.2007-234760,在硅化物层上形成作为蚀刻阻止膜的SiN膜,并在其上形成作为层间绝缘膜的氧化硅膜。然后形成具有预定图案的抗蚀剂膜,所述预定图案包含开口,通过这些开口形成接触孔,然后通过使用抗蚀剂膜作为掩模的干法蚀刻,选择性地去除氧化硅膜,通常是通过O2等离子体灰化来去除抗蚀剂膜。此后,使用氧化硅膜作为掩模来选择性地去除作为蚀刻阻止膜的SiN膜。以这种方式形成接触孔。根据在该公布中所描述的形成接触孔的方法,由于发生灰化,所以留下作为蚀刻阻止膜的SiN膜未被去除,使得可以防止硅化物层直接暴露于O2等离子体。

在上述低电阻化的趋势中,采用诸如NiSi的含Ni硅化物层作为硅化物提出了另外的要求,即,要求在用作较高蚀刻阻止膜的SiN膜蚀刻工艺中对Ni硅化物层保持大的选择性。因此,为确保这种大的选择性,有必要在更有可能产生沉积物的条件下蚀刻SiN膜,使得更有可能在接触孔的底部产生沉积物。在形成接触孔后,进行清洗以去除沉积物是重要的。

一般通过灰化或者通过使用氨水与过氧化氢水溶液的混合溶液(下文中有时称氨/过氧化氢溶液)、氢氟酸溶液或硫酸与过氧化氢水溶液(下文中有时称硫酸/过氧化氢溶液)的混合溶液来进行清洗,以去除这类沉积物。

日本专利特许公布No.2007-234760中公开了一种工艺,在该工艺中形成接触孔,接下来使用氢氟酸等进行酸洗,并使用碱性化学品进行处理。该专利公布中还公开了硅化物层表面的RF蚀刻。

日本专利特许公布No.2002-146574中公开了,活性阴极水和活性阳极水也可应用于在通过蚀刻形成开口之后进行的清洗,所述开口使硅化物层露出。

根据该公布,组成活性阴极水和活性阳极水的电解质水溶液包含1至30质量%的氢氧化氨和1至30质量%的氟化物。

本发明人已经有如下的认识。上述公布中公开的现有技术仍然存在着以下方面的问题。

在日本专利特许公布No.2007-234760所述的现有技术中,硅化物层上沉积物的去除与通常使用含酸水溶液进行的氧化或氧等离子体处理一起发生。在日本专利特许公布No.2002-146574中所描述的现有技术中,使用含1至30质量%氢氧化氨的电解质水溶液的清洗基本上需要用水进行冲洗的后续处理。

然而,硅化物层,特别是Ni硅化物层,即使通过这种使用水进行的冲洗也容易氧化。

如上所述,通过现有技术去除硅化物层上的沉积物与不期望的硅化物层氧化相关联。

发明内容

根据本发明提供一种制造半导体装置的方法,包括:

通过干法蚀刻来去除在含Ni硅化物层上形成的绝缘层,从而使含Ni硅化物层至少部分地露出;以及

使用还原水清洗含Ni硅化物层的露出部。

此时可以使用还原水清洗在干法蚀刻中产生的沉积在含Ni硅化物层上的沉积物。

根据本发明可提供一种制造半导体装置的方法,该方法能够在不使硅化物层氧化的情况下去除沉积物。

附图说明

根据下面结合附图对某些优选实施方式进行的描述,使本发明的上述以及其他的目的、优点和特征更明显,其中:

图1是示出本发明的一个实施方式中的半导体装置的制造工序的流程图;

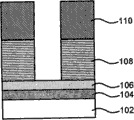

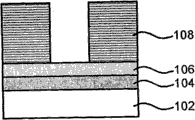

图2A至2C和图3A至3C是示出本发明的一个实施方式的半导体装置制造工艺的截面图;

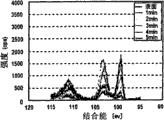

图4A至4E是在绝缘膜中形成的接触孔的截面SEM图像;以及

图5A至5D是接触孔底部的X射线光电子能谱(XPS)图。

具体实施方式

现在将参照示例性实施方式来描述本发明。本领域技术人员将会意识到,使用本发明的教导内容可以实现许多可替选的实施方式,并且本发明不局限于为了例示的目的而示出的实施方式。

参考附图说明了本发明的一个实施方式。需指出的是,在所有附图中,以相同的数字或符号表示任何相同的构成要素,不再重复对其的说明。

将参考图1至图3C来说明本实施方式的半导体装置的制造方法。

图1是示出本实施方式中的半导体装置制造工序的流程图,图2A至2C和图3A至3C是示出本实施方式中的半导体装置制造工艺的截面图。

在本实施方式中,首先,在半导体衬底102上形成含Ni硅化物层104(S100)。然后在含Ni硅化物层104上形成蚀刻阻止膜106(S102)。然后在蚀刻阻止膜106上形成绝缘膜108(S104)。此后,在绝缘膜108上形成具有预定图案的抗蚀剂层110(S106),然后使用抗蚀剂层110作为掩模来蚀刻绝缘膜108,以由此形成接触孔(开口)(S108)。然后通过灰化来去除抗蚀剂层110(S110)。

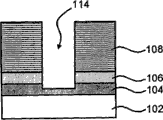

接下来使用绝缘膜108作为掩模,通过干法蚀刻来去除蚀刻阻止膜106(S112)。由此,在接触孔的底部处使含Ni硅化物层104露出。然后使用还原水114来清洗产品(S114)。通过清洗,可以去除接触孔中的沉积物112,并由此可以清洗含Ni硅化物层104的表面。在本实施方式中,还原水114可以是碱性还原性水溶液。

在本实施方式中,然后将半导体衬底102转移至膜生长腔室,同时保持对含Ni硅化物层104的保护。接下来在膜生长腔室中,在接触孔中生长作为金属膜116的导电膜(S116)。

下面将进一步详细说明上述的过程。需指出的是,图中所示的只是源/漏区上的硅化物部分,而简化了对本发明来说是非必要的栅极绝缘膜、栅电极等的描述。

含Ni硅化物层104可以优选地选自NiSi层、NiPtSi层以及这些层的堆叠,并且可以按下述的方式来制造。本文中的一个示例涉及采用NiSi层的情况。首先,通过溅射在由硅衬底构成的半导体衬底102的上表面形成厚度大约5nm以上且20nm以下的作为金属膜的Ni膜。然后使产物在250℃以上且350℃以下经受第一退火(烧结)。结果,形成Ni2Si层。此后,通过通常使用SPM(硫酸/过氧化氢(/水)混合物)进行的蚀刻,去除金属膜的未反应部分。然后使产物在350℃以上且400℃以下经受第二退火(烧结),以由此形成NiSi层。

在本实施方式的半导体装置100的制造方法中,绝缘层优选地包含至少第一绝缘膜(蚀刻阻止膜106)和在其上形成的第二绝缘膜(绝缘膜108)。

形成接触孔的工艺优选地包括使用抗蚀剂层作为掩模来选择性蚀刻绝缘膜108的工艺、去除抗蚀剂层的工艺以及使用绝缘膜108作为掩模对蚀刻阻止膜106进行选择性蚀刻的工艺。

通常可以通过使用SiN膜来构造蚀刻阻止膜106。通常通过原子层沉积(ALD)来形成蚀刻阻止膜106。通常可以通过使用氧化硅(SiO2)膜来构造绝缘膜108。

接下来,在绝缘膜108上形成具有预定图案的抗蚀剂层110(图2A),所述预定图案包含用于形成接触孔的开口。接下来,通过使用抗蚀剂层110作为掩模进行干法蚀刻,来选择性地去除绝缘膜108(图2B)。接下来,通过灰化或者通过使用SPM或APM的湿法蚀刻来去除抗蚀剂层110(图2C)。然后,通过使用绝缘膜108作为掩模进行干法蚀刻,来选择性地去除蚀刻阻止膜106(图3A)。以这种方式,形成到达含Ni硅化物层104的凹部(接触孔)。

在对蚀刻阻止膜106的干法蚀刻中(S112),考虑到要确保满意的选择性水平,优选地使用诸如CH3F的H比例大的气体。又可替选地,可以使用诸如CH2F2和CHF3的氟碳化合物气体。该气体可以包含氧等。

然而,作为干法蚀刻的结果,在该工艺中的接触孔具有在其中聚积的沉积物112。在本实施方式中,通过使用还原水114的清洗来去除保留在接触孔中的这种沉积物112(图3B以及图1中的步骤S114)。通过清洗,沉积物112被去除,由此清洗含Ni硅化物层104。应该理解的是,本文中的清洗还包括简单的冲洗。

本实施方式的半导体装置100的制造方法优选地包括:通过干法蚀刻去除在含Ni硅化物层104上表面形成的绝缘层,由此使含Ni硅化物层104至少部分地露出的工艺;以及使用还原水114清洗含Ni硅化物层104的露出部。

所述方法进一步优选地包括在绝缘层中形成凹部(接触孔)的工艺和用还原水114清洗接触孔的工艺。

还原水旨在通过用OH基团保护含Ni硅化物层104的表面防止其被氧化,还原水优选地为在提供用于清洗之前才进行测量时包含0.01ppm以上氨的富氢水或电解还原水。还优选还原水为包含1000ppm以下氨的富氢水或电解还原水,使得在用还原水处理之后,不再需要用水冲洗。

氨浓度更优选在0.1ppm以上至100ppm以下的范围内。具有的氨浓度调节至该范围内的还原水呈碱性。由在以还原水处理之前才用pH计测量的pH值来计算氨浓度。本文中可以采用任何市售的pH计。

还原水的pH值优选大于7,并且具有负的ORP(氧化-还原电位)。还原水的pH值更优选地大于8。考虑到借助于碱性去除沉积物,还原水的ORP值更优选地小于-100mV。具体地,ORP值更优选地为-800mV以上且-500mV以下。具有的ORP值调节至该范围内的还原水呈碱性。

在以还原水处理之前才使用pH计测量pH值。在以还原水处理之前才使用ORP计测量氧化-还原电位。本文中可以采用任何市售的ORP计。

可以在室温或适当高于室温的条件下使用还原水。

电解还原水是作为电解含少量氨离子(1质量%以下)的水的结果而在阴极侧上产生的液体。用于产生电解还原水的装置可以是两部件电解装置,或者可以可替选地是三部件电解装置。富氢水优选地为通过把氢气溶入到稀释的氨水溶液中得到的水,所述氢气作为电解的结果在阴极处产生或者由储气瓶供给。

可以通过调节氨离子量获得所需的pH值和氧化-还原电位,并且也可以通过调节溶解的氢气量获得所需的氧化-还原电位值。

以还原水进行清洗可以采用单晶片处理模式和批处理模式这两种。处理的持续时间可优选地为30秒以上,并且特别地为60秒以上且180秒以下。

以还原水清洗后不一定接下来要使用纯水或其他种类的水进行冲洗以去除还原水。

因此,在本实施方式的半导体装置100的制造方法中,从以还原水进行清洗之后含Ni硅化物层104被还原水覆盖的时间点开始,直到在接触孔中形成阻挡金属和金属膜时的时间点,在该时段期间可以保持含Ni硅化物层104不接触水。

图4A至4E是接触孔的截面SEM图像。本文中所示的是干法蚀刻后的结果(图4A)、干法蚀刻之后进行常规清洗处理(图4B中通过灰化,图4C中通过用硫酸/过氧化氢溶液清洗,以及图4E中通过用稀氢氟酸清洗)后的结果以及干法蚀刻之后根据本实施方式用还原水清洗后的结果(图4D)。图5A至5D是以一分钟为间隔在各个工艺之后一至五分钟时测量的接触孔底部的XPS图。本文中所示的是干法蚀刻后得到的XPS图(图5A)、干法蚀刻之后进行常规清洗处理(图5B中通过灰化,以及图5C中通过用硫酸/过氧化氢溶液清洗)后得到的XPS图以及干法蚀刻之后根据本实施方式用还原水清洗后得到的XPS图(图5D)。

本文中所用还原水具有的氨浓度为10ppm,pH值为9.5,以及氧化-还原电位为-600mV。

根据SEM图像判断来看,灰化(图4B)以及用硫酸/过氧化氢溶液清洗(图4C)似乎可成功地去除了沉积物。然而,与本实施方式中用还原水处理后得到的结果(图4D)相比可知,在接触孔的底部处,使用SPM进行去除不充分。还发现DHF处理(图4E)对绝缘膜以及接触孔底部造成不期望有的蚀刻。

此外,蚀刻后得到的XPS图(图5A)和干法蚀刻之后进行常规清洗处理(图5B中通过灰化,图5C中通过用硫酸/过氧化氢溶液清洗)后得到的XPS图在大约103eV处示出峰,可能表明存在SiO2。

与之相比之下,在本实施方式中用还原水清洗之后得到的XPS图(图5D)没有显示出由SiO2所引起的峰,表明NiSi膜暴露于接触孔的底部。

这大概是因为NiSi膜上的导电抑制物(SiO2)通过以负ORP为特征的还原水的还原功能被还原。

用还原水清洗之后还发现,在清洗之后一至五分钟内的任何时间点上没有在接触孔的底部通过XPS观察到由SiO2所引起的峰。因此在用还原水处理后的延长持续时间段内,在接触孔的底部处可以防止含Ni硅化物层104的表面被氧化。

现在返回到日本专利特许公布No.2002-146574中公开的现有技术,因为氢氧化氨的浓度高达1至30质量%,所以以活性阴极水清洗之后接下来一定要用水进行冲洗。虽然在该公布中没有公开Ni硅化物作为所述硅化物,但如果硅化物是Ni硅化物,用水冲洗会对含Ni硅化物层产生不期望有的氧化。

相反,根据本实施方式的半导体装置100的制造方法,在用还原水处理之后,不再需要用水冲洗。因此,在使含Ni硅化物层104露出之后,可以在不使露出的表面经受用含氧化性气体的气体进行的任何处理、并且不使露出的表面接触pH≤(不大于)7的任何液体的情形下,使用还原水清洗露出的表面。

此外,在用还原水进行清洗处理后,可以在不使清洗的表面接触诸如SPM的pH≤7的任何液体的情形下,对清洗的表面进行干燥处理。

然后把半导体衬底102转移至膜生长腔室。接下来,在接触孔中形成导电金属膜116(图3C)。

在本实施方式的半导体装置100的制造方法中,在对清洗的表面进行干燥处理后,可以在接触孔中形成阻挡金属和金属膜116。更具体而言,在对清洗的表面进行干燥处理后,在不使干燥的表面经受用含氧化性气体的气体进行的任何处理、并且不使干燥的表面接触pH≤7的任何液体的情形下,在接触孔(凹部)中形成阻挡金属和金属膜116。

金属膜116和阻挡金属可以构造成堆叠结构。

例如,金属膜116可以优选地采用Ti。阻挡金属可以优选地采用由W、Ti、Ta、这些元素的氮化物或这些元素的堆叠组成的层。

已经对本发明的实施方式进行了说明,但其并不是对本发明的限制。

例如,通常在栅电极上的硅化物层也可以采用本发明的实施方式,而不是局限于杂质扩散层上的硅化物层。

可以以自对准方式(如自对准硅化物工艺)形成含Ni硅化物层。Ni硅化物层可以是诸如NiPtSi层的任何包含Ni的硅化物层,而不是局限于NiSi层,或者可以是这些层的堆叠。

这些元素的化学计量比可以是任意的,使得并不总是需要NiSi的Ni与Si的组成比为1∶1。

蚀刻阻止膜106不局限于SiN膜,可以是能够确保相对于其上形成的绝缘膜108具有一定程度的蚀刻选择性的任何蚀刻阻止膜。

进一步可以在SiN膜下方以及在硅化物层与SiN膜之间形成氧化硅膜。该构造使得蚀刻氧化硅膜成为必要,使得同样由氧化硅膜组成的绝缘膜108也从上面被轻微地蚀刻,但只进行到不会造成问题的程度。

绝缘膜108可以是低k膜,而不是局限于氧化硅膜。低k膜可以以MSQ、SiOCH、HSQ和有机膜为例子。

根据其特征在于用还原水清洗其中含Ni硅化物层露出的接触孔的本发明实施方式,可以彻底去除沉积物,并且可以保持期望的接触电阻水平,因为硅化物层的表面不大可能被氧化。

根据本发明实施方式所述那样,用还原水进行清洗,既不需要用氧化性气体进行处理,也不需要氧化处理,并且甚至在用还原水处理之后不必用水冲洗。因此可以防止硅化物层在其表面上被氧化,并且因此可以将接触电阻保持在期望水平处。

由于无需通过例如氢氟酸处理、RF蚀刻等方式蚀刻含Ni硅化物层的表面,因此,即使硅化物层变薄,也可以将接触电阻保持在期望的水平处,并且还可以抑制泄漏电流。

此外,以还原水进行清洗可以成功地用H终止Ni硅化物表面上的悬键,并且这有助于进一步防止表面被氧化。

当然可以将所述实施方式与上述的多种修改相结合,只要在其中不发生冲突即可。可以按各种方式对所述实施方式及修改的实施方式中具体描述的各个组件的构造进行修改,只要能实现本发明的目的即可。

显而易见的是,本发明并不局限于上述的实施方式,在不偏离本发明范围和实质的情况下,可以对上述的实施方式进行修改和改变。

Claims (13)

1.一种制造半导体装置的方法,其包含:

通过干法蚀刻去除在含Ni硅化物层上形成的绝缘层,从而使所述含Ni硅化物层至少部分地露出;以及

使用还原水清洗所述含Ni硅化物层的露出部,

其中所述还原水是碱性还原性水溶液,且

其中所述还原水是包含0.01ppm以上且1000ppm以下氨的富氢水或电解还原水。

2.如权利要求1中所述的制造半导体装置的方法,其中

所述还原水具有的pH值大于7,并且具有负ORP(氧化-还原电位)。

3.如权利要求1中所述的制造半导体装置的方法,其中

在所述使所述含Ni硅化物层露出之后,在不使所述露出的表面经受使用含氧化性气体的气体进行的任何处理、并且不使所述露出的表面接触pH≤7的任何液体的情形下,使用所述还原水清洗露出的表面。

4.如权利要求1中所述的制造半导体装置的方法,其中

在所述通过干法蚀刻去除绝缘层时,在所述绝缘层中形成凹部;以及

在所述清洗中,使用所述还原水清洗所述凹部。

5.如权利要求1中所述的制造半导体装置的方法,进一步包含:

在使用所述还原水进行所述清洗之后,在不使所述清洗的表面接触pH≤7的任何液体的情形下,对清洗的表面进行干燥的工序。

6.如权利要求5中所述的制造半导体装置的方法,进一步包含:

在所述干燥所述清洗的表面之后,在凹部形成阻挡金属和金属膜的工序。

7.如权利要求6中所述的制造半导体装置的方法,其中

在所述干燥所述清洗的表面之后,在不使所述干燥的表面经受使用含氧化性气体的气体进行的任何处理、并且不使所述干燥的表面接触pH≤7的任何液体的情形下,在所述凹部形成所述阻挡金属和所述金属膜。

8.如权利要求4中所述的制造半导体装置的方法,其中

所述绝缘层至少具有第一绝缘膜以及在其上表面形成的第二绝缘膜。

9.如权利要求8中所述的制造半导体装置的方法,其中

所述形成所述凹部进一步包含:

使用抗蚀剂层作为掩模,来选择性地蚀刻所述第二绝缘膜;

去除所述抗蚀剂层;以及

使用所述第二绝缘膜作为掩模,来选择性地蚀刻所述第一绝缘膜。

10.如权利要求8中所述的制造半导体装置的方法,其中

所述第一绝缘膜是氮化硅膜。

11.如权利要求8中所述的制造半导体装置的方法,其中

所述第二绝缘膜是氧化硅膜。

12.如权利要求1中所述的制造半导体装置的方法,其中

所述含Ni硅化物层选自NiSi层、NiPtSi层以及这些层的堆叠。

13.如权利要求6中所述的制造半导体装置的方法,其中

在使用所述还原水的所述清洗之后,从所述含Ni硅化物层被所述还原水覆盖的时间点开始,直到在所述凹部形成所述阻挡金属和所述金属膜的时间点为止,在这一期间不使所述含Ni硅化物层接触水。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009-046801 | 2009-02-27 | ||

| JP2009046801A JP2010205782A (ja) | 2009-02-27 | 2009-02-27 | 半導体装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101819931A CN101819931A (zh) | 2010-09-01 |

| CN101819931B true CN101819931B (zh) | 2013-02-13 |

Family

ID=42654964

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN201010119463.1A Expired - Fee Related CN101819931B (zh) | 2009-02-27 | 2010-02-23 | 制造半导体装置的方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8293653B2 (zh) |

| JP (1) | JP2010205782A (zh) |

| CN (1) | CN101819931B (zh) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5326113B2 (ja) * | 2009-06-25 | 2013-10-30 | ルネサスエレクトロニクス株式会社 | 半導体装置の洗浄方法 |

| US8784572B2 (en) | 2011-10-19 | 2014-07-22 | Intermolecular, Inc. | Method for cleaning platinum residues on a semiconductor substrate |

| US8697573B2 (en) | 2011-11-09 | 2014-04-15 | Intermolecular, Inc. | Process to remove Ni and Pt residues for NiPtSi applications using aqua regia with microwave assisted heating |

| FR3013502A1 (fr) * | 2013-11-20 | 2015-05-22 | Commissariat Energie Atomique | Procede de protection d’une couche de siliciure |

| US9865466B2 (en) * | 2015-09-25 | 2018-01-09 | Applied Materials, Inc. | Silicide phase control by confinement |

| CN114005831B (zh) * | 2021-10-28 | 2024-03-22 | 上海华力微电子有限公司 | 一种改善NAND flash字线间漏电的工艺集成方法 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1113034A (zh) * | 1994-03-25 | 1995-12-06 | 日本电气株式会社 | 具有用于阳极和阴极分别再生的反馈通道的湿法处理设备 |

| CN1228197A (zh) * | 1996-08-20 | 1999-09-08 | 奥加诺株式会社 | 清洗电子元件构件或类似零件的方法和装置 |

| CN1501448A (zh) * | 2002-11-19 | 2004-06-02 | 台湾积体电路制造股份有限公司 | 制作接触孔于硅化镍层上方的方法 |

Family Cites Families (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3111979B2 (ja) * | 1998-05-20 | 2000-11-27 | 日本電気株式会社 | ウエハの洗浄方法 |

| KR100389917B1 (ko) * | 2000-09-06 | 2003-07-04 | 삼성전자주식회사 | 산화성 물질을 포함하는 아노드 수 및/또는 환원성 물질을포함하는 캐소드 수를 사용하는 반도체 제조를 위한 습식공정 및 이 공정에 사용되는 아노드수 및/또는 캐소드수 |

| JP2002305177A (ja) * | 2001-02-01 | 2002-10-18 | Dainippon Screen Mfg Co Ltd | 基板処理装置 |

| JP4046486B2 (ja) * | 2001-06-13 | 2008-02-13 | Necエレクトロニクス株式会社 | 洗浄水及びウエハの洗浄方法 |

| JP3667273B2 (ja) * | 2001-11-02 | 2005-07-06 | Necエレクトロニクス株式会社 | 洗浄方法および洗浄液 |

| JP3680063B2 (ja) * | 2002-03-12 | 2005-08-10 | 株式会社東芝 | 半導体装置の製造方法 |

| JP3828511B2 (ja) * | 2003-06-26 | 2006-10-04 | 株式会社東芝 | 半導体装置の製造方法 |

| JP2005085981A (ja) * | 2003-09-09 | 2005-03-31 | Matsushita Electric Ind Co Ltd | 電子デバイスの製造方法及び洗浄方法 |

| JP2005183937A (ja) * | 2003-11-25 | 2005-07-07 | Nec Electronics Corp | 半導体装置の製造方法およびレジスト除去用洗浄装置 |

| JP2006024823A (ja) * | 2004-07-09 | 2006-01-26 | Casio Comput Co Ltd | レジスト除去方法 |

| JP4917328B2 (ja) | 2006-02-28 | 2012-04-18 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| JP2008198935A (ja) * | 2007-02-15 | 2008-08-28 | Sony Corp | 絶縁ゲート電界効果トランジスタの製造方法。 |

-

2009

- 2009-02-27 JP JP2009046801A patent/JP2010205782A/ja active Pending

-

2010

- 2010-02-22 US US12/656,981 patent/US8293653B2/en not_active Expired - Fee Related

- 2010-02-23 CN CN201010119463.1A patent/CN101819931B/zh not_active Expired - Fee Related

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1113034A (zh) * | 1994-03-25 | 1995-12-06 | 日本电气株式会社 | 具有用于阳极和阴极分别再生的反馈通道的湿法处理设备 |

| CN1228197A (zh) * | 1996-08-20 | 1999-09-08 | 奥加诺株式会社 | 清洗电子元件构件或类似零件的方法和装置 |

| CN1501448A (zh) * | 2002-11-19 | 2004-06-02 | 台湾积体电路制造股份有限公司 | 制作接触孔于硅化镍层上方的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN101819931A (zh) | 2010-09-01 |

| US20100221912A1 (en) | 2010-09-02 |

| JP2010205782A (ja) | 2010-09-16 |

| US8293653B2 (en) | 2012-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7256137B2 (en) | Method of forming contact plug on silicide structure | |

| CN101819931B (zh) | 制造半导体装置的方法 | |

| CN100414684C (zh) | 除去了连接孔内的损伤层、自然氧化膜的半导体装置的制造方法 | |

| KR100786923B1 (ko) | 반도체장치의 제조방법 | |

| US20070170588A1 (en) | Connection structure and fabrication method for the same | |

| JP5153131B2 (ja) | 半導体素子のデュアルゲート形成方法 | |

| KR100801074B1 (ko) | 반도체 소자 제조 방법 및 이에 따라 제조된 반도체 소자 | |

| US7867901B2 (en) | Method for forming silicide in semiconductor device | |

| US20110139750A1 (en) | Method of removing post-etch residues | |

| JP2010056574A (ja) | 半導体装置の製造方法 | |

| KR100714311B1 (ko) | 실리콘 표면의 세정용액 및 이를 사용하는 반도체 소자의제조방법들 | |

| JP4917328B2 (ja) | 半導体装置の製造方法 | |

| JP4108445B2 (ja) | 半導体装置の製造方法 | |

| JP2009259996A (ja) | 半導体装置およびその製造方法 | |

| JP5601026B2 (ja) | 半導体装置の製造方法 | |

| JP2006294842A (ja) | 半導体装置の製造方法 | |

| JP2005136097A (ja) | 半導体装置の製造方法 | |

| KR100869844B1 (ko) | 반도체소자의 듀얼게이트 형성방법 | |

| KR20030018779A (ko) | 반도체 장치의 실리사이드막 제조 방법 | |

| JP2006066621A (ja) | 半導体装置とその製造方法 | |

| KR100756772B1 (ko) | 트랜지스터의 제조 방법 | |

| CN118712124A (zh) | 半导体结构的形成方法 | |

| JP3945345B2 (ja) | 半導体装置の製造方法 | |

| KR101035585B1 (ko) | 반도체 소자의 실리사이드층 형성 방법 | |

| CN118335687A (zh) | 半导体结构的制作方法及半导体结构 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20130213 Termination date: 20170223 |