CN101257300A - 可调式晶体管体偏置电路 - Google Patents

可调式晶体管体偏置电路 Download PDFInfo

- Publication number

- CN101257300A CN101257300A CNA2007100847338A CN200710084733A CN101257300A CN 101257300 A CN101257300 A CN 101257300A CN A2007100847338 A CNA2007100847338 A CN A2007100847338A CN 200710084733 A CN200710084733 A CN 200710084733A CN 101257300 A CN101257300 A CN 101257300A

- Authority

- CN

- China

- Prior art keywords

- charge pump

- voltage

- transistor

- adjustable

- voltage regulator

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17784—Structural details for adapting physical parameters for supply voltage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0013—Arrangements for reducing power consumption in field effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

- H02M3/078—Charge pumps of the Schenkel-type with means for reducing the back bias effect, i.e. the effect which causes the threshold voltage of transistors to increase as more stages are added to the converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0018—Special modifications or use of the back gate voltage of a FET

Landscapes

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Dc-Dc Converters (AREA)

- Logic Circuits (AREA)

Abstract

本发明提供一种集成电路,其包括带有体端的n沟道和p沟道金属氧化物半导体晶体管。提供了位于该集成电路上的可调式晶体管体偏置电路,该集成电路向所述体端提供体偏置电压,以使功耗最小化。通过使用集成电路上的载有配置数据的可编程单元,可调式体偏置电路可以被控制。集成电路可以是包含有可编程逻辑的可编程逻辑器件集成电路。可调式体偏置电路可以产生可调式的负体偏置电压,用于偏置n沟道金属氧化物半导体晶体管。可调式体偏置电路包括带隙基准电路、电荷泵电路和可调式电压调节器。

Description

技术领域

[0001]本发明一般涉及晶体管体偏置电路,尤其涉及用于集成电路,如可编程逻辑器件的可调式晶体管体偏置电路。

背景技术

[0002]现代集成电路的性能常受到功耗考虑的限制。具有不良功率效率的电路给系统设计人员提出了不受欢迎的要求。电源容量需要增加,热管理问题需要被处理,为了适应效率低的电路,电路设计需要被修改。

[0003]集成电路常使用互补金属氧化物半导体(CMOS)晶体管技术。CMOS集成电路具有n沟道金属氧化物半导体(NMOS)和p沟道金属氧化物半导体(PMOS)晶体管。

[0004]NMOS和PMOS集成电路都有四个端——漏极、源极、栅极和体端。体端或衬底端(body terminal)有时也称为阱端(wellterminal)或块端(bulk terminal),体端能够被偏置来提高晶体管的性能。例如,正偏置电压可以加在PMOS晶体管的体端,而负偏置电压可以加在NMOS晶体管的体端。这些偏置电压提高了晶体管的有效阈值电压,并因此而降低了晶体管的泄漏电流。泄漏电流的降低减小了功耗。

[0005]合适的偏置电压趋于是小电压。例如,一个NMOS体偏置电压可能会小于几百个毫伏。更大的体偏置电压可以被用于进一步减小泄漏电流,但是这可能会对器件性能有显著的不良影响。在减小泄漏电流和牺牲性能二者之间的最佳平衡一般是通过使用小的体偏置电压来获得的。

[0006]体偏置电压可以在芯片外产生,但是这类方法耗费了稀少的输入-输出管脚。另外,不可调的体偏置电压源会在可编程逻辑器件中产生一些问题,在可编程器件中常希望改变所使用的偏置量。

[0007]因此希望提供一种可调的片上晶体管体偏置电压电路,用于减小集成电路,如可编程逻辑器件集成电路上的功耗。

发明内容

[0008]根据本发明,提供一种集成电路如可编程逻辑器件电路,该集成电路包括可调式体偏置电路。可调式体偏置电路由控制信号控制。控制信号可以由可编程单元提供,这些可编程单元已经载入配置数据,控制信号可以由集成电路上的可编程逻辑来提供,或者从外部源来获得。解码器用来解码未解码的控制信号。

[0009]可调式体偏置电路可以包含产生负电压的一个电荷泵电路,通过使用该负电压产生可调的负体偏置电压的一个可调式电压调节器,以及为该可调式电压调节器和电荷泵提供基准信号的一个带隙基准电路。

[0010]可调式电压调节器可以包含一个可调式分压器,连接在电荷泵电路和可调式分压器之间的一个晶体管,和一个运算放大器。可调式分压器可以包含一串联的电阻链和很多个连接在各对串联电阻之间的晶体管。可调式体偏置电路的控制信号可以加在晶体管的栅极,以限定期望的分压器电压分接位置。运算放大器在一个输入处接收来自带隙基准电路的一个基准电压,并且在另一个输入处接收从分压器分接点反馈的多个信号。运算放大器带有一个输出,其被施加到和电荷泵电路连接的晶体管的栅极。由可调式电压调节器产生的负体偏置电压的幅值通过调节分压器来控制。

[0011]通过附图和以下的详细说明,本发明的进一步特征、特性和各种优势将会更明显。

附图说明

[0012]图1为一个根据本发明的说明性可编程逻辑器件集成电路的框图。

[0013]图2为一个根据本发明的体偏置的n沟道金属氧化物半导体晶体管的原理图。

[0014]图3为一个根据本发明的体偏置的n沟道金属氧化物半导体晶体管的横截面视图。

[0015]图4为一个根据本发明的说明性电荷泵的原理图。

[0016]图5为图4电荷泵的简化示意图。

[0017]图6为根据本发明的时序图,展示了图4和图5所示类型的电荷泵如何产生负输出电压用于晶体管体偏置。

[0018]图7为展示金属氧化物半导体晶体管电容器的电容值作为所加电压的函数而变化的曲线图。

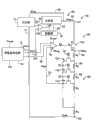

[0019]图8为一个根据本发明的说明性可调式体偏置电路布置的电路图,该电路布置可用于偏置集成电路如可编程逻辑器件集成电路中的晶体管。

[0020]图9为一个根据本发明的说明性可调式体偏置电路的电路图,该电路具有一个电荷泵、带隙基准电路和可调式调节器。

[0021]图10为一个根据本发明的说明性可调式体偏置电路的电路图,该电路具有一个基于可编程分压器的调节器。

[0022]图11为一个根据本发明的说明性运算放大器的电路图,该运算放大器用于图10所示类型的调节器。

[0023]图12为展示了根据本发明的图10可编程分压器中的每一个晶体管怎样被各自的可编程单元控制的图。

[0024]图13展示了根据本发明的图10可编程分压器中的晶体管怎样被可编程单元提供的并且被解码器解码的控制信号控制。

[0025]图14展示了根据本发明的图10可编程分压器中的每一个晶体管怎样被一个外部控制信号控制,该外部控制信号通过各自的输入-输出管脚提供。

[0026]图15展示了根据本发明的图10可编程分压器中的晶体管怎样被多个控制信号控制,这些控制信号由一个外部源通过输入-输出管脚来提供,并且被一个解码器解码。

具体实施方式

[0027]本发明涉及可调式体偏置电压源。体偏置电压源可以使用在任何合适的集成电路中。根据本发明的带有一个特定的合适布置的可调式体偏置电路可以用在可编程逻辑器件集成电路中。体偏置电路还可以用在带有可编程电路的集成电路上,这种可编程电路不是指传统的可编程逻辑器件,如包含有可编程电路的微处理器、包含有可编程电路的数字信号处理器、带有可编程电路的定制集成电路等等。作为例子,在可编程逻辑器件集成电路的背景下一般性地描述本发明。

[0028]可编程逻辑器件集成电路可使用配置数据来定制。在一个典型的方案中,逻辑设计者在设计期望的逻辑电路时使用计算机辅助设计(CAD)系统。计算机辅助设计系统使用可编程逻辑器件的硬件性能上的信息来产生配置数据。

[0029]可编程逻辑器件包含可编程单元。可编程单元可以是基于任何合适的可编程技术,如熔丝、反熔丝、激光编程单元、电编程单元、非易失性存储单元、易失性存储单元、掩模编程单元等等。在此作为一个实例描述的典型方案中,可编程单元是基于随机存取存储器(RAM)单元。

[0030]为了定制可编程逻辑器件以实施期望的逻辑电路,配置数据由计算机辅助设计系统产生并被载入可编程存储单元。在可编程逻辑器件的运行期间,基于其载入的配置数据,每一个存储单元提供一个静态输出信号。存储单元的输出信号被施加到可编程逻辑器件上的可编程逻辑区域中的n沟道金属氧化物半导体晶体管和p沟道金属氧化物半导体晶体管上。这就配置了器件的可编程逻辑,使得可编程逻辑器件实施期望的逻辑电路。

[0031]根据本发明,可编程逻辑器件被配备可调式体偏置电路。p沟道体偏置电路为这个可编程逻辑器件上的p沟道金属氧化物半导体晶体管产生一个体偏置电压。n沟道体偏置电路为这个可编程逻辑器件上的n沟道金属氧化物半导体晶体管产生一个体偏置电压。体偏置电压降低晶体管泄漏电流,并由此提高了器件性能。

[0032]根据本发明的一个说明性可编程逻辑器件10示于图1中。可编程逻辑器件10具有输入-输出电路12,用于使信号离开器件10,并且用于经由输入-输出管脚14从其它器件接收信号。互连资源16如全局和局部垂直和水平传导线路和总线用来路由器件10上的信号。互连资源16包括固定互连(传导线路)和可编程互连(即,各自固定互连间的可编程连接)。可编程逻辑18可以包括组合和时序逻辑电路。可编程逻辑18可以被配置来执行定制的逻辑功能。和互连资源16关联的可编程互连可以被认为是可编程逻辑18的一部分。

[0033]可编程逻辑器件10包含可编程单元20,如随机存取存储器单元,其能够通过使用管脚14和输入-输出电路12来载入配置数据(也称为编程数据)。一旦载入,可编程单元都能提供一个相应的静态控制输出信号,该控制信号控制可编程逻辑18中的一个相关联逻辑部件的状态。可编程单元输出信号被用来控制金属氧化物半导体(MOS)晶体管的栅极。在可编程组件中,如多路复用器、查找表、逻辑阵列、与、或、与非、以及或非逻辑门等等,这些晶体管中多数一般是n沟道金属氧化物半导体(NMOS)传输晶体管。当可编程单元输出为高时,由该可编程单元控制的传输晶体管被导通,并且逻辑信号从它的输入传递至输出。当可编程单元输出为低时,这个传输晶体管被关闭并且不再传递逻辑信号。

[0034]可编程单元可以从任何合适的源载入。在一个典型的装置中,可编程单元从一个外部的可擦除可编程只读存储器载入,并且经由管脚14和输入-输出电路12控制一个称为配置器件的芯片。

[0035]器件10的电路可以使用任何合适的架构来组织。作为例子,可编程逻辑器件10的逻辑可以在较大可编程逻辑区域的一系列行和列中来组织,每一个较大可编程逻辑区域包含多个较小逻辑区域。器件10的逻辑资源可以通过互连资源16,如相关的垂直和水平导线,相互连接。这些导线可以包括基本跨越整个器件10的全局传导线路,跨越器件10的一部分的分数线路如半线路或四分之一线路,特定长度的交叉线路(如,足够互连几个逻辑区域),较小的局部线路或任何其它合适的互连资源布置。如果希望,器件10的逻辑可以被布置成更多级或更多层,其中多个大区域互连组成逻辑的较大部分。此外,其它器件布置可以使用没有布置在行和列中的逻辑。

[0036]器件10上的晶体管有四个端——一个源极、一个漏极、一个栅极和一个体端。体端有时也被称为阱端(well terminal)或块端(bulkterminal),体端能够被偏置来降低功耗。在p沟道金属氧化物半导体晶体管中,体端电压能够相对于正电源电压(有时称为Vcc)而轻微地升高。在n沟道金属氧化物半导体晶体管中,体端电压可以相对于地(有时称为Vss)而降低。例如,如果Vss是0V,则n沟道金属氧化物半导体晶体管的体端可以偏置到一个幅值范围为0到500mV或0到1000mV(如,100mV,200mV,300mV等等)的负电压。

[0037]图2中示出了一个说明性n沟道金属氧化物半导体晶体管22的原理图。晶体管22的源极标记为S,漏极标记为D,栅极标记为G,体端标记为B。如图2所示,一个体偏置电压Vbias加在体端B,图3示出了图2的n沟道晶体管22的横截面图。源极S和漏极D通过使用植入区域24而形成。栅结构26由一个绝缘体如硅氧化物的薄层和一个栅导体如硅化多晶硅而形成。体端B使用植入区域28以形成一个带有p型体区域30的欧姆接触。

[0038]本发明的可调式体偏置电路可以产生稳定精确的负偏置电压,其幅值为几十或几百毫伏(或者更大)。这些负偏置电压可以用来偏置n沟道晶体管如图2和图3中的晶体管22,以降低功耗。一般而言,任何合适数量的晶体管都可以被配备体偏置。例如,器件10上的一些或全部的n沟道晶体管可以被配备体偏置,一些或全部的p沟道晶体管可以被配备体偏置。提供大规模体偏置的一个优势在于器件10的功耗将会被最小化。选择性地使用体偏置的一个优势在于性能能够被最优化。例如,在希望最大性能的关键信号路径上,体偏置可以被避免(或减少)。

[0039]关于器件10上的哪一个电路被提供体偏置,和使用的偏置量可以由逻辑设计者或CAD工具在设计的过程中来决定。基于这些决定,CAD工具能够产生用于调节可调式体偏置电路的配置数据。一旦载入到可编程逻辑器件中,配置数据可以被用来有选择地为器件10的各个部分打开或关闭偏置,并且调节用于器件10各部分(如,在器件10的一些部分处最大化性能,在器件10的另一些部分处最大化功耗节省)的偏置量。一般地,在一个给定的可编程逻辑器件上,可以产生任何合适数量的不同的体偏置电压。用于偏置n沟道金属氧化物半导体晶体管的一个单体偏置电压的产生被描述为一个实例。

[0040]负的体偏置电压Vbias被用来偏置n沟道金属氧化物半导体晶体管。在一个典型的方案中,器件10的地电压Vss为0V。图4中所示类型的一个电荷泵32可以被用来产生一个电压Vout,Vout相对于Vss是负的(即,一个小于0V的电压)。图4实例中所示的电荷泵32是一个两级泵。这仅是说明性的。电荷泵32可以有任意合适数量的级(如,三级或更多级)。

[0041]如图4所示,时钟信号CLK和它的逆NCLK被分别施加到端34和36。电容38和40为金属氧化物半导体晶体管电容(有时称为MOS电容),它们由MOS晶体管的结构组成。电容38和40中的电容电介质由MOS晶体管结构中的栅极绝缘体构成。每个电容的一个电极由一个晶体管栅极端组成。每个电容的另一个电极由电连接的漏极端、源极端和体端组成,如图4所示。电荷泵32中MOS电容的使用是有利的,这是因为在器件10上很容易得到MOS电容,并且在半导体制造工艺过程中不需要特殊的处理步骤。

[0042]电荷泵32具有三个带有端的晶体管,这些端连接组成二极管42、44、46。如果期望,其它二极管结构可以用来组成二极管42、44、46。图5中展示了图4电荷泵32的一个电路图,其中二极管42、44、46采用二极管符号来表示,并且其中MOS晶体管电容38和40采用电容符号来表示。

[0043]电荷泵32的运行在图6的时序图中示出。时钟信号CLK和NCLK在图6的第一和第二条迹线中示出。节点N1和N2上的电压在图6的第三和第四条迹线中示出。图6的第五条迹线展示了在电荷泵输出处的电压Vout。

[0044]初始,在时间t1,电荷泵32的节点N1的电压为0V,如图6中的第三条迹线所示。在时间t2,时钟信号CLK变为高,并且它的逆NCLK变为低。在时间t2处信号CLK中上升的过程中,电容38的跨接电压不改变。结果,在时间t2处节点N1的电压上升。节点N1的电压的上升导通了二极管42。节点N1的电压最大上升在二极管42的导通电压处(约为0.6V或一个晶体管阈值电压Vt)被封顶,其值小于CLK的幅值。

[0045]在时间t3处,信号CLK变低,信号NCLK变高。电容38的跨接电压在时间t3处信号转换的过程中不变,所以信号CLK的下降引起节点N1的电压下降,这示于图6的第三条迹线中。在节点N2处的电压为一个二极管导通电压(约为0.6V或一个晶体管阈值电压Vt),由于二极管44被导通,N2处的电压高于节点N1处的电压。

[0046]在时间t4,信号CLK变高,信号NCLK变低。电容40的跨接电压在时间t4处转换的过程中不发生变化,所以随着端36上的NCLK信号中的下降,节点N2处的电压在时间t4下降。这就迫使电荷泵32输出端上的电压Vout为低,这示于图6的第五条迹线中。由于二极管46被导通,所以电压Vout为一个二极管导通电压,高于N2处的电压。

[0047]如这个讨论所说明的,图4和图5的电荷泵32在其输出产生一个负电压Vout。

[0048]电荷泵中的级数和时钟信号的大小影响着负输出电压Vout的大小。另外,时钟信号CLK和NCLK可以被选择为启用和禁止来调节输出电压Vout。但是,单独使用电荷泵来产生体偏置电压Vbias(即,使用Vout作为Vbias)一般是不可取的,这是因为电压依赖于电荷泵MOS电容38和40的特性。

[0049]MOS电容如MOS电容38和40典型地展示了具有这种类型的电压依赖特性的电容值C,C的曲线展示于图7中。在大于Vst或小于-Vst的电压处,电容值C是一个相对常量。在这种状态下,电荷泵的行为是可预测的,并且通过恰当的调节,电荷泵能够产生一个稳定精确的输出电压Vout。在电容电压位于-Vst和Vst之间时,电容值C作为所加电压的函数而显著变化。在这种状态下,电荷泵32的运行趋向于不稳定。因此,建议避免在电容38和40的跨接电压处于-Vst和Vst之间的情况下使电荷泵32运行。

[0050]在一个给定的可编程逻辑器件上,Vst的值依赖于形成的MOS结构类型。一般地,Vst的值近似地等于一个或两个晶体管阈值电压Vt(即,具有Vt值为约0.6V的集成电路上的Vst近似为1V)。Vbias需要的电压电平趋于在0V和-1V之间,但是图4和图5的电荷泵在这个电压范围内不适合产生稳定的电压。结果是,一般不希望使用图4和图5的电荷泵直接地产生电压Vbias。

[0051]根据本发明,图4和图5中所示类型的电荷泵被提供分压器和反馈电路,这就使得可能产生一个稳定精确的电压Vbias,用于偏置器件10上的n沟道金属氧化物半导体晶体管。电荷泵产生一个稳定的电压Vout(称为Vneg),Vout约为-1V(作为例子)。分压器减小Vneg的大小来产生几十或几百mV的Vbias值。这些Vbias值落入偏置n沟道晶体管所需的典型需要范围内,以减小功耗,同时不会负面影响晶体管的性能。

[0052]根据本发明的一个可调式体偏置电路布置示于图8中。如图8所示,可编程逻辑器件集成电路10包括片上可调式体偏置电路48。体偏置电路48在它的输出产生一个可调式体偏置输出电压Vbias。传导路径如路径52被用来把Vbias分配给合适的n沟道晶体管(在图8中的示意性示为电路50)的体端。在可编程逻辑器件10上可能会有任意合适数量的可调式体偏置发生器,其中的每一个可以产生Vbias的不同的相应值。

[0053]可调式体偏置电路48可以使用图9中所示类型的一个基于电荷泵的电路来实施。在图9中的实例中,可调式体偏置电路48有一个电荷泵电路56,一个带隙基准电路54和一个可调式电压调节器60。电路48在其输出66处产生一个可调式负输出电压Vbias。在输出66处产生的电压Vbias通过路径如路径52(图8)被施加在n沟道金属氧化物半导体晶体管的体端。

[0054]带隙基准电路54产生基准信号,基准信号通过路径62提供给可调式调节器60,并且通过路径63提供给电荷泵电路56。可调式调节器60和电荷泵电路56在产生稳定的输出信号时使用基准信号。

[0055]电荷泵电路56产生一个负的电荷泵输出电压Vneg,它通过路径58提供给可调式调节器60。Vneg的幅值优选大于Vbias的最大希望幅值。例如,如果需要的Vbias最大值为-0.9V,那么Vneg优选为约-0.9V或更小(如,-1.0V,-1.2V等等)。

[0056]可调式电压调节器60被控制信号(在图9中示意性示为在控制输入64处接收的控制信号CONTROL)控制。控制信号用来决定输出66处产生的偏置电压Vbias的幅值。控制信号可以被用来例如设置偏置电压Vbias到-100mV、到-200mV或任何其它合适的偏置量级。

[0057]可调式电压调节器60和电荷泵电路56可以通过使用任何合适的电路来实施。一个合适的布置示于图10中。在图10图示说明的布置中,带隙基准电路54通过一个正电源电压Vccpd和一个地电压Vss来供电。电源电压Vccpd例如可以是2.5V左右。电源电压Vccpd优选从一个预先存在的电源线获得,以避免不必要地增加可编程逻辑器件10的复杂性。作为例子,电源电压Vccpd可以为与图1输入-输出电路12中用来给驱动电路供电的电源电压相同的电压。

[0058]带隙基准电路54在相应的输出线路70和72上提供基准电压Vref1和Vref2。为Vref1和Vref2选择的特定值并不是关键的。一个Vref1的合适值实例为0.5V。一个Vref2的合适值实例为1V(Vref1的两倍)。带隙基准电路54还提供一个基准电流Iref。Iref例如可以为10μA。

[0059]电荷泵电路56包括一个电荷泵32,一个分压器74,一个比较器76和一个振荡器78。振荡器78通过路径80提供时钟信号CLK和NCLK到电荷泵32。线路82上的比较器76产生的输出控制振荡器78。电荷泵32的输出为电压Vneg并通过路径90提供给电压调节器60。电压Vneg还通过反馈路径88反馈到分压器74。分压器74使用Vneg和Vref2(在输入73处接收到)来在线路84上产生一个输出信号,该输出信号和经由线路88反馈的电压Vneg成比例。基准电压Vref1通过路径86加在比较器76上。

[0060]比较器76比较线路84和86上的信号,并在路径82上产生相应的输出。当线路84上的信号大于线路86上的信号时,线路82上的比较器76的输出为高。这会导通振荡器78并引起电荷泵32驱动Vneg更低。当线路84上的信号小于线路86上的信号时,线路82上的比较器76的输出为低。这将关断振荡器78,发出Vneg已经达到其希望值的信号。使用这个反馈布置,Vneg的值在它的希望值(例如,-1V)处被保持不变。

[0061]电压Vneg通过路径90提供给可调式调节器60,并且形成它的负电源。电压Vref2作为正电源用于可调式电压调节器60。可调式电压调节器60有一个可调式分压器68,该分压器由大量的串联电阻98组成。典型的电阻值为约10KΩ至50KΩ。电压调节器60中电阻链的一个端维持为电压Vbias。电阻链的另外一端连接到正电源Vref2。

[0062]电压Vtap为分压器中电阻链的分接电压。调节器60有一个反馈路径92,用来向运算放大器94的一个输入提供电压Vtap。电压Vtap的幅值由可调式分压器的状态来决定。通过调节电压Vtap从串联电阻98分接的点,能够调节分压器的电压设定点。

[0063]在图10的说明性布置中,通过设定可编程单元20的状态,分压器的串联电阻中的电压分接点位置可以被确定。每一个可编程单元20控制一个相应的晶体管102。每一个可编程单元的状态由它的内容来确定。在器件编程过程中,配置数据被载入到可编程单元20。载入逻辑0的可编程单元产生低输出信号,并且关断其相关联的晶体管102。可编程单元中的一个载入一个逻辑1。可编程逻辑单元中的逻辑1使得该可编程单元的输出变为高。这个高输出信号导通一个相应的晶体管102。晶体管102被导通的位置决定了分压器68的设定点。

[0064]来自分压器68的电压Vtap通过反馈路径92被反馈到运算放大器94。运算放大器94通过使用合适的电源电压来供电(如,图10实例中的电压Vccpd和Vneg)。运算放大器94优选从带隙基准电路54接收基准信号,如电流基准Iref和电压基准Vref1。电流基准Iref通过输入线路96提供给运算放大器94。电压基准信号Vref1加在运算放大器94的输入端。

[0065]运算放大器94比较来自分压器68的分接电压Vtap和基准电压Vref1,并且产生一个相应的输出控制信号Vx。信号Vx加在晶体管104的栅极G。晶体管104通常是导通的且运行在饱和状态。电流经过分压器68的电阻,晶体管104的源极和漏极,从Vref2节点69(处于1V)流到Vneg节点91(处于-1V)。当Vx上升时,晶体管104在其源极和漏极传导的电流量也上升。这导致在输出端66的电压Vbias的下降。当Vx下降时,流经晶体管1 04的电流量也下降,提高了Vbias。

[0066]来自分压器68、通过运算放大器94的反馈环精确地将电压Vbias维持在它的希望值。如果Vbias开始轻微地升高超过它的设定点(如,从-100mV升高为-99mV),Vtap就会轻微地升高(如,从500mV升高为501mV)。通过路径92提供的反馈引起运算放大器94的输出增加,所以运算放大器94输出处的电压Vx将会升高。响应于Vx的增加值,流经晶体管104的电流将会增大高。增大流经晶体管104的电流将会引起Vbias向着它的希望设定点值(如,在本实例中的-100mV)的方向下降(如,从-99mV到-100mV)。如果Vbias开始轻微地下降低于它的设定点,通过路径92的反馈将引起Vbias上升(如,从-101mV到-100mV)。

[0067]在分压器68中使用的电阻98的个数是由用于可调式电压调节器60的期望电压步幅数来决定的。如果使用大量的电阻98,将会存在相对大的电压步幅数,并且电压调节器60能够产生一个高精度水平的期望Vbias电平。如果使用较少的电阻98,那么每个电压步幅将会更大,并且得到较低的精度,但是电路复杂性将会降低。一般地,任何合适数量的电阻98和相关联的分接电阻102可以使用在分压器68中。

[0068]图10的运算放大器94可以使用的说明性电路示于图1 1中。如图11所示,运算放大器94使用正电源电压Vccpd和负电源电压Vneg被供电。运算放大器94的输出126产生电压Vx,Vx加在晶体管104的栅极(图10)。

[0069]基准电流Iref通过线路96加在输入106。晶体管108和109组成一个电流镜,所以幅值为Iref的电流流经路径110。晶体管112和114也组成了一个电流镜,所以电流Iref流经路径116。由于它们的晶体管具有相等的强度,所以图11中的电流镜有一个值为1的镜反射率。如果希望,也可以使用带有其它镜反射率的电流镜。

[0070]负输入128和正输入130分别地接收电压Vref1和电压Vtap。基准Vref1由带隙基准电路54(图10)产生,并且为常量。Vtap值轻微地波动高于和低于Vref1,因为Vbias围绕其期望的设定点值轻微地波动。相对于基准电压值Vref1的Vtap值决定电流是否被导引通过路径118或路径132。

[0071]当Vtap大于Vref1时,p沟道金属氧化物半导体晶体管134的导通比p沟道金属氧化物半导体晶体管136的导通要更强一些。这就导致路径116中待导引的电流Iref流入118中的电流相对多于流入路径132中的电流。晶体管120和122组成一个电流镜,所以导引进入路径118的额外电流导致额外的电流被导引流入路径124。

[0072]当Vtap低于Vref1时,电流被导引进入路径132。晶体管138和140组成了一个电流镜,所以导引进入路径132的额外电流引起更多的电流被导引进入路径142。在稳定状态中,Vtap的值稳|定|到Vref1,并且相等的电流量流经运算放大器94的左手侧和右手侧分支。

[0073]晶体管146和144为负载晶体管,其分别将流经路径124和142的电流转换为节点150和148处的电压。当由于在端130处Vtap下降引起通过路径142的电流增加时,电压Vx下降。当由于在端130处Vtap升高引起通过路径142的电流下降时,电压Vx升高。

[0074]在图10的实例中,分压器68的设定可以使用载入到可编程单元20中的配置数据来调节。在这类情况中,可编程单元20的输出作为可调式调节器60的控制信号(如图9中路径64上的CONTROL信号所示)。这类布置只是说明性的。如果希望,任何合适的用于控制分压器68和电压调节器60的技术可以被使用。例如,其它技术可以用来提供控制信号到电压分接晶体管102。

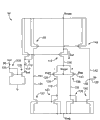

[0075]用于控制晶体管102的说明性布置示于图12、13、14和15中。

[0076]在图12的布置中,单个可编程单元20和每一个晶体管102相联系。通过使用各自的控制线路152,可编程单元20的输出被提供到晶体管102的栅极。

[0077]图13示出了一个使用解码器156的控制布置。可编程单元20被使用来提供控制信号到输入线路158上的解码器156。解码器156包括将在输入线路158上的未解码控制信号转换为线路160上相应的解码控制信号的逻辑。线路160被用来将这些控制信号路由到各自晶体管102的栅极。

[0078]解码器(如图13中的解码器156)的使用增加了器件10的复杂性。另外,解码器156和路由线路158和160的逻辑需要占电路的地方或电路面积。但是,解码器如解码器156的使用减少了对可编程单元20的需要。例如,通过使用N个可编程单元控制2N个线路160是可能的。在有相对多数量的晶体管102的情况下,对于控制每一个晶体管102来说,使用解码器156比使用单独的可编程单元20更有效。

[0079]如果希望,外部控制信号可以被用来控制晶体管102的栅极。如图14所示,每一个晶体管102可以接收经过相关联的路径162来自一个相应的输入-输出管脚14的控制信号。在图15的布置中,一个解码器166被插入输入-输出管脚14和晶体管102之间。路径164将来自输入-输出管脚14的未解码控制信号传送到解码器166。路径168传送解码的控制信号到晶体管102。

[0080]图14中线路162和图15中线路164的控制信号可以从内部源(例如,图1中可编程逻辑18中的逻辑,或在器件10中的硬布线逻辑)来提供。这些控制信号可以在器件10的运行过程中动态产生。

[0081]还可以使用这些方法的组合。例如,晶体管102中的一些可以被来自图12中所示专用可编程单元20的信号控制,和/或被内部提供的信号控制,和/或被图14中线路162上的外部提供的信号控制,而其它晶体管102可以使用解码器来控制。来自可编程单元20,可编程逻辑18或外部源的未解码的控制信号可以被提供给解码器。

[0082]前面只是说明本发明的原理,本领域的技术人员可以做各种修改而不脱离本发明的范围和精神。

Claims (30)

1. 一种集成电路,其包括:

带有体端的n沟道金属氧化物半导体晶体管;和

可调式基于电荷泵的体偏置电路,其将负的体偏置电压施加到所述体端。

2. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括:

载有配置数据的可编程单元。

3. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括可调式电压调节器。

4. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路并且其中所述可调式基于电荷泵的体偏置电路包括一个可调式电压调节器,所述集成电路进一步包括:

载有配置数据的可编程单元。

5. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路并且其中所述可调式基于电荷泵的体偏置电路包括一个可调式电压调节器,所述集成电路进一步包括:

载有配置数据的可编程单元,其中的一些所述可编程单元产生控制所述可调式电压调节器的输出信号。

6. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路并且其中所述可调式基于电荷泵的体偏置电路包括一个可调式电压调节器,所述集成电路进一步包括:

载有配置数据的可编程单元,其中的一些所述可编程单元产生未解码的控制信号;和

一个解码器,其接收所述未解码的控制信号并将相应的解码控制信号施加到所述可调式电压调节器。

7. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;和

可调式电压调节器,其使用所述负的电荷泵输出电压产生所述负的体偏置电压。

8. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;

可调式电压调节器,其使用所述负的电荷泵输出电压产生所述负的体偏置电压;和

带隙基准电路,其将至少一个基准信号施加到所述可调式电压调节器。

9. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压,其中所述电荷泵电路包括分压器、比较器、振荡器和电荷泵;

可调式电压调节器,其使用所述负的电荷泵输出电压产生所述负的体偏置电压;和

带隙基准电路,其将至少一个基准信号施加到所述可调式电压调节器,其中所述电荷泵电路中的所述分压器通过一个反馈线路从所述电荷泵接收所述负的电荷泵输出电压,并提供一个相应的信号到所述比较器的第一输入,其中所述比较器在第二输入从所述带隙基准电路接收一个电压基准信号,其中所述比较器比较所述第一输入和第二输入,并产生控制所述振荡器的一个相应输出,并且其中所述振荡器产生给所述电荷泵的时钟信号。

10. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;和

可调式电压调节器,其包括一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出电压产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置。

11. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括载有配置数据的可编程单元,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵,其产生负的电荷泵输出电压;和

可调式电压调节器,其包括一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出产生所述负的体偏置电压,其中可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置,所述控制信号来自至少一些所述可编程单元。

12. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括载有配置数据的可编程单元,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;

带有输出的解码器;和

可调式电压调节器,其包括一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出电压来产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置,所述控制信号来自所述解码器的输出。

13. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括载有配置数据的可编程单元,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;

带有输出和输入的解码器,其中所述输入从至少一些所述可编程单元接收控制信号;以及

可调式电压调节器,其包含一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出电压来产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置,所述控制信号来自所述解码器的输出。

14. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括载有配置数据的可编程单元,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生一个负的电荷泵输出电压;

带有输出和输入的解码器,其中所述输入通过所述输入-输出管脚接收控制信号;

可调式电压调节器,其包含一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出电压来产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置,所述控制信号来自所述解码器的输出。

15. 根据权利要求1所述的集成电路,其中所述集成电路包括一个可编程逻辑器件集成电路,所述集成电路进一步包括载有配置数据的可编程单元和产生信号的可编程逻辑,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其产生负的电荷泵输出电压;

带有输出和输入的解码器,其中所述输入从所述可编程逻辑接收至少一些所述信号;

可调式电压调节器,其包含一个可调式分压器,其中所述可调式电压调节器使用所述负的电荷泵输出电压来产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管带有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加到其栅极的控制信号控制,以在所述串联电阻中限定一个电压分接点位置,所述控制信号来自所述解码器的输出。

16. 根据权利要求1所述的集成电路,其中所述可调式基于电荷泵的体偏置电路包括:

电荷泵电路,其包含多个金属氧化物半导体电容,所述电荷泵电路产生负的电荷泵输出电压;

带隙基准电路,其提供至少一个基准信号;和

可调式电压调节器,其包括一串联电阻链,多个晶体管,所述晶体管连接在各自的串联电阻对之间以建立限定相关联的分接电压的可选择的分压器分接点,一个运算放大器,所述运算放大器带有从所述带隙基准电路接收所述基准信号的第一输入、第二输入和一个输出,提供所述分接电压到所述第二输入的反馈路径,以及连接在所述电荷泵和所述串联电阻链之间的一个晶体管,其中所述晶体管有一个栅极,其连接到所述运算放大器的所述输出。

17. 在集成电路上的一种晶体管体偏置电路,其包括:

电荷泵,其产生负的电压;和

可调式电压调节器,其使用来自所述电荷泵的所述负的电压产生负的晶体管体偏置电压。

18. 根据权利要求17所述的晶体管体偏置电路,进一步包括载有配置数据的多个可编程单元,其产生相应的输出信号,其中所述可调式电压调节器包括一个分压器,所述分压器具有多个晶体管,其中每个晶体管有一个栅极,所述栅极从所述多个可编程单元的各自一个接收一个所述输出信号。

19. 根据权利要求17所述的晶体管体偏置电路,进一步包括:

多个可编程单元,其载有配置数据,产生相应的输出信号;和

一个带隙基准电路,其提供至少一个基准信号到所述可调式电压调节器,其中所述可调式电压调节器包括一个可调式分压器,其中所述可调式电压调节器使用由所述电荷泵产生的所述负的电压产生所述负的体偏置电压,其中所述可调式电压调节器包括多个电阻和多个晶体管,其中所述晶体管连接在各自的电阻对之间,其中所述晶体管带有栅极,其中每个栅极从所述可编程单元中的相应一个接收各自的输出信号。

20. 根据权利要求17所述的晶体管体偏置电路,其中所述电荷泵包括金属氧化物半导体晶体管结构,其被配置为金属氧化物半导体电容,所述体偏置电路进一步包括:

载有配置数据的多个可编程单元,其产生相应的输出信号;和

一个带隙基准电路,其提供至少一个基准信号到所述可调式电压调节器,其中所述可调式电压调节器包括一个可调式分压器,其中所述可调式电压调节器包括一个运算放大器,并使用由所述电荷泵产生的所述负的电压产生所述负的体偏置电压,其中所述可调式电压调节器包括多个电阻和多个晶体管,其中所述晶体管连接在各自的电阻对之间,其中所述晶体管带有栅极,其中每个栅极从所述可编程单元中的相应一个接收各自的输出信号,并且其中所述配置数据导通所述晶体管中的一个给定晶体管,以限定一个从所述分压器至决定所述负的体偏置电压的所述运算放大器的反馈路径。

21. 一种可编程逻辑器件集成电路,其包括:

可编程逻辑,其包括n沟道金属氧化物半导体晶体管,所述晶体管带有体端,负的体偏置电压加在所述体端;

带隙基准电路,其提供一个基准电压;和

可调式电压调节器,其带有一个用来接收负的电荷泵输出电压的端,其从所述带隙基准电路接收所述基准电压,并且提供所述负的体偏置电压给所述可编程逻辑中的所述n沟道金属氧化物半导体晶体管的所述体端。

22. 根据权利要求21所述的可编程逻辑器件集成电路,进一步包括:

可编程单元,其载有配置数据,其中一些所述可编程单元产生控制所述可调式电压调节器的输出信号。

23. 根据权利要求21所述的可编程逻辑器件集成电路,进一步包括:

电荷泵电路,其产生所述负的电荷泵输出电压,所述可调式电压调节器接收这个输出电压,其中所述可调式电压调节器使用所述负的电荷泵输出电压产生所述负的体偏置电压。

24. 根据权利要求21所述的可编程逻辑器件集成电路,其中所述可调式电压调节器包括一个可调式分压器,所述可编程逻辑器件进一步包括:

电荷泵电路,其产生所述负的电荷泵输出电压,所述可调式分压器接收这个输出电压。

25. 根据权利要求21所述的可编程逻辑器件集成电路,进一步包括:

振荡器;

比较器;

电荷泵,其产生所述负的电荷泵输出电压;

分压器,其通过反馈线路从所述电荷泵接收所述负的电荷泵输出电压,并且提供一个相应的信号给所述比较器的第一输入,其中所述比较器在第二输入处从所述带隙基准电路接收所述基准电压,其中所述比较器比较所述第一输入和第二输入并产生一个控制所述振荡器的相应的输出,其中所述振荡器为所述电荷泵产生时钟信号。

26. 根据权利要求21所述的可编程逻辑器件集成电路,其中所述可编程逻辑包括载有配置数据的可编程单元,其中所述可调式电压调节器包括:

可调式分压器,其包括多个串联电阻和多个晶体管,其中所述可调式电压调节器使用所述负的电荷泵输出电压产生所述负的体偏置电压,其中所述晶体管有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加在其栅极上的控制信号控制,以限定所述串联电阻中的一个电压分接点位置,所述控制信号来自至少一些所述可编程单元的所述输出。

27. 根据权利要求21所述的可编程逻辑器件进一步包括:

电荷泵电路,其产生所述负的电荷泵输出电压;和

解码器,其具有输入和输出,其中所述输入接收控制信号,其中所述可调式电压调节器使用所述负的电荷泵输出电压产生所述负的体偏置电压,其中所述可调式电压调节器包括多个串联电阻和多个晶体管,其中所述晶体管有栅极,并且连接在各自的串联电阻对之间,其中所述晶体管由施加在其栅极上的控制信号控制,以限定所述串联电阻中的一个电压分接点位置,所述控制信号来自所述解码器的所述输出。

28. 根据权利要求21所述的可编程逻辑器件集成电路,其中所述可调式电压调节器进一步包括:

运算放大器,其接收所述基准电压,并提供一个输出信号;

晶体管,其具有从所述运算放大器接收所述输出信号的一个栅极;和

一个电阻链,其连接到所述晶体管。

29. 根据权利要求21所述的可编程逻辑器件集成电路,其中所述可调式电压调节器进一步包括:

一串联电阻链,其位于所述可调式分压器中;和

多个晶体管,其连接在各自的串联电阻对之间,以建立一个可选择的分压器分接点,该点限定了一个相关联的分接电压。

30. 根据权利要求21所述的可编程逻辑器件集成电路,进一步包括一个电荷泵,其提供所述负的电荷泵输出电压,其中所述可调式电压调节器进一步包括:

电阻;

多个晶体管,其连接在各自的电阻对之间,以建立一个可选择的分压器分接点,该点限定了一个相关联的分接电压;

运算放大器,其具有第一输入、第二输入和一个输出,所述第一输入从所述带隙基准电路接收所述基准信号;和

反馈路径,其向所述第二输入提供所述分接电压;和

晶体管,其连接在所述电荷泵与所述电阻之间,其中所述晶体管带有连接到所述运算放大器的输出的一个栅极。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/369,664 | 2006-03-06 | ||

| US11/369,664 US7495471B2 (en) | 2006-03-06 | 2006-03-06 | Adjustable transistor body bias circuitry |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN101257300A true CN101257300A (zh) | 2008-09-03 |

Family

ID=38110608

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNA2007100847338A Pending CN101257300A (zh) | 2006-03-06 | 2007-02-28 | 可调式晶体管体偏置电路 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7495471B2 (zh) |

| EP (1) | EP1833152A1 (zh) |

| JP (1) | JP4648346B2 (zh) |

| CN (1) | CN101257300A (zh) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101814829A (zh) * | 2010-04-22 | 2010-08-25 | 上海宏力半导体制造有限公司 | 电荷泵电路的参考电压产生电路及电荷泵电路 |

| CN102903384A (zh) * | 2011-07-25 | 2013-01-30 | 旺宏电子股份有限公司 | 待机电荷升压器装置及其操作方法 |

| CN103534950A (zh) * | 2011-05-16 | 2014-01-22 | 株式会社半导体能源研究所 | 可编程逻辑装置 |

| CN104601163A (zh) * | 2013-10-30 | 2015-05-06 | 飞思卡尔半导体公司 | 体偏置控制电路 |

| CN105308530A (zh) * | 2013-05-17 | 2016-02-03 | 英特尔公司 | 使用动态电路基准的片上电源发生器 |

| CN106253665A (zh) * | 2016-08-29 | 2016-12-21 | 深圳市华星光电技术有限公司 | 增加升降压幅度的电荷泵 |

| CN107357351A (zh) * | 2017-08-15 | 2017-11-17 | 电子科技大学 | 一种基于自供电电荷泵架构的nmos ldo |

Families Citing this family (37)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007251351A (ja) | 2006-03-14 | 2007-09-27 | Renesas Technology Corp | 半導体装置 |

| US7642754B2 (en) * | 2006-06-08 | 2010-01-05 | Semiconductor Components Industries, L.L.C. | Method of forming a voltage regulator and structure therefor |

| KR100817058B1 (ko) * | 2006-09-05 | 2008-03-27 | 삼성전자주식회사 | 룩업 테이블을 이용한 바디 바이어싱 제어회로 및 이의바디 바이어싱 제어방법 |

| JP2008136047A (ja) * | 2006-11-29 | 2008-06-12 | Sony Corp | 固体撮像装置及び撮像装置 |

| US8183843B2 (en) * | 2007-01-26 | 2012-05-22 | Infineon Technologies Ag | Voltage regulator and associated methods |

| US8115462B2 (en) * | 2007-06-20 | 2012-02-14 | Atmel Corporation | Voltage regulator for an integrated circuit |

| US7800402B1 (en) * | 2007-11-05 | 2010-09-21 | Altera Corporation | Look-up table overdrive circuits |

| DE102008007029B4 (de) * | 2008-01-31 | 2014-07-03 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Betrieb einer elektronischen Schaltung mit körpergesteuertem Doppelkanaltransistor und SRAM-Zelle mit körpergesteuertem Doppelkanaltransistor |

| KR100961210B1 (ko) | 2008-11-04 | 2010-06-09 | 주식회사 하이닉스반도체 | 제어신호생성회로 및 이를 이용하는 센스앰프회로 |

| US8081502B1 (en) | 2008-12-29 | 2011-12-20 | Altera Corporation | Memory elements with body bias control |

| US8742831B2 (en) * | 2009-02-23 | 2014-06-03 | Honeywell International Inc. | Method for digital programmable optimization of mixed-signal circuits |

| CN101867015A (zh) * | 2009-04-16 | 2010-10-20 | 台湾积体电路制造股份有限公司 | 通过施加p-衬底偏压和调节阈值电压提高磁性隧道结的编程电流 |

| KR101143470B1 (ko) | 2010-07-02 | 2012-05-08 | 에스케이하이닉스 주식회사 | 전압 정류 회로 |

| US8416011B2 (en) | 2010-11-08 | 2013-04-09 | Lsi Corporation | Circuit and method for generating body bias voltage for an integrated circuit |

| US8416009B2 (en) | 2011-07-13 | 2013-04-09 | International Business Machines Corporation | Solutions for controlling bulk bias voltage in an extremely thin silicon-on-insulator (ETSOI) integrated circuit chip |

| DE102013207324A1 (de) * | 2012-05-11 | 2013-11-14 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung und elektronisches Gerät |

| US9348959B1 (en) * | 2012-06-29 | 2016-05-24 | Xilinx, Inc. | Optimizing supply voltage and threshold voltage |

| US8847565B2 (en) * | 2012-09-14 | 2014-09-30 | Nxp B.V. | Shunt regulator for adverse voltage/circuit conditions |

| US9112495B1 (en) * | 2013-03-15 | 2015-08-18 | Mie Fujitsu Semiconductor Limited | Integrated circuit device body bias circuits and methods |

| JP6406926B2 (ja) | 2013-09-04 | 2018-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9577626B2 (en) | 2014-08-07 | 2017-02-21 | Skyworks Solutions, Inc. | Apparatus and methods for controlling radio frequency switches |

| KR102211167B1 (ko) | 2014-08-14 | 2021-02-02 | 삼성전자주식회사 | 바디 바이어스 전압 생성기 및 이를 포함하는 시스템-온-칩 |

| US9467124B2 (en) * | 2014-09-30 | 2016-10-11 | Skyworks Solutions, Inc. | Voltage generator with charge pump and related methods and apparatus |

| US9917507B2 (en) | 2015-05-28 | 2018-03-13 | Sandisk Technologies Llc | Dynamic clock period modulation scheme for variable charge pump load currents |

| US9647536B2 (en) | 2015-07-28 | 2017-05-09 | Sandisk Technologies Llc | High voltage generation using low voltage devices |

| WO2017037568A1 (en) * | 2015-08-31 | 2017-03-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device or electronic device including the semiconductor device |

| US9520776B1 (en) | 2015-09-18 | 2016-12-13 | Sandisk Technologies Llc | Selective body bias for charge pump transfer switches |

| CN108205349A (zh) * | 2016-12-19 | 2018-06-26 | 北京兆易创新科技股份有限公司 | 一种带隙基准电路 |

| US10483985B2 (en) * | 2017-01-23 | 2019-11-19 | Samsung Electronics Co., Ltd. | Oscillator using supply regulation loop and operating method thereof |

| KR102426729B1 (ko) | 2017-08-11 | 2022-07-29 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의 동작 방법 |

| US10552563B2 (en) * | 2018-01-10 | 2020-02-04 | Qualcomm Incorporated | Digital design with bundled data asynchronous logic and body-biasing tuning |

| US10469097B1 (en) | 2018-12-06 | 2019-11-05 | Nxp Usa, Inc. | Body bias circuit for current steering DAC switches |

| US11271566B2 (en) * | 2018-12-14 | 2022-03-08 | Integrated Device Technology, Inc. | Digital logic compatible inputs in compound semiconductor circuits |

| KR102071354B1 (ko) * | 2019-11-13 | 2020-01-30 | 주식회사 스카이칩스 | 벅-부스트 직류-직류 변환 장치 |

| KR102696754B1 (ko) * | 2019-12-30 | 2024-08-21 | 에스케이하이닉스 주식회사 | 데이터 입출력 회로를 포함하는 메모리 장치 |

| US11894768B2 (en) * | 2020-04-27 | 2024-02-06 | Sony Semiconductor Solutions Corporation | DC/DC converter |

| KR20230140036A (ko) | 2022-03-29 | 2023-10-06 | 삼성전자주식회사 | 바디 바이어스 전압 생성기 및 이를 포함하는 반도체 장치 |

Family Cites Families (87)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5103160A (en) * | 1991-04-25 | 1992-04-07 | Hughes Aircraft Company | Shunt regulator with tunnel oxide reference |

| DE4221575C2 (de) * | 1992-07-01 | 1995-02-09 | Ibm | Integrierter CMOS-Halbleiterschaltkreis und Datenverarbeitungssystem mit integriertem CMOS-Halbleiterschaltkreis |

| US5341034A (en) * | 1993-02-11 | 1994-08-23 | Benchmarq Microelectronics, Inc. | Backup battery power controller having channel regions of transistors being biased by power supply or battery |

| KR0169157B1 (ko) * | 1993-11-29 | 1999-02-01 | 기다오까 다까시 | 반도체 회로 및 mos-dram |

| US5422591A (en) * | 1994-01-03 | 1995-06-06 | Sgs-Thomson Microelectronics, Inc. | Output driver circuit with body bias control for multiple power supply operation |

| US5689209A (en) * | 1994-12-30 | 1997-11-18 | Siliconix Incorporated | Low-side bidirectional battery disconnect switch |

| US5670907A (en) | 1995-03-14 | 1997-09-23 | Lattice Semiconductor Corporation | VBB reference for pumped substrates |

| JP2931776B2 (ja) | 1995-08-21 | 1999-08-09 | 三菱電機株式会社 | 半導体集積回路 |

| US5661685A (en) | 1995-09-25 | 1997-08-26 | Xilinx, Inc. | Programmable logic device with configurable power supply |

| US5600264A (en) * | 1995-10-16 | 1997-02-04 | Xilinx, Inc. | Programmable single buffered six pass transistor configuration |

| US5689144A (en) * | 1996-05-15 | 1997-11-18 | Siliconix Incorporated | Four-terminal power MOSFET switch having reduced threshold voltage and on-resistance |

| KR100189752B1 (ko) * | 1996-06-01 | 1999-06-01 | 구본준 | 독립적인 웰 바이어스 전압을 가진 전압 펌프회로 |

| KR100203136B1 (ko) * | 1996-06-27 | 1999-06-15 | 김영환 | 래치-업을 방지하는 상승전압발생기 |

| JP3264622B2 (ja) * | 1996-07-16 | 2002-03-11 | 株式会社東芝 | 半導体装置 |

| US6593799B2 (en) * | 1997-06-20 | 2003-07-15 | Intel Corporation | Circuit including forward body bias from supply voltage and ground nodes |

| US6411156B1 (en) * | 1997-06-20 | 2002-06-25 | Intel Corporation | Employing transistor body bias in controlling chip parameters |

| US6535034B1 (en) * | 1997-07-30 | 2003-03-18 | Programmable Silicon Solutions | High performance integrated circuit devices adaptable to use lower supply voltages with smaller device geometries |

| US5841694A (en) * | 1997-07-30 | 1998-11-24 | Programmable Silicon Solutions | High performance programmable interconnect |

| US6346415B1 (en) * | 1997-10-21 | 2002-02-12 | Targeted Genetics Corporation | Transcriptionally-activated AAV inverted terminal repeats (ITRS) for use with recombinant AAV vectors |

| US6097242A (en) * | 1998-02-26 | 2000-08-01 | Micron Technology, Inc. | Threshold voltage compensation circuits for low voltage and low power CMOS integrated circuits |

| US6157691A (en) * | 1998-04-14 | 2000-12-05 | Lsi Logic Corporation | Fully integrated phase-locked loop with resistor-less loop filer |

| JP3136593B2 (ja) * | 1998-08-17 | 2001-02-19 | 日本電気株式会社 | レギュレータ内蔵半導体装置 |

| US6242728B1 (en) * | 1998-08-20 | 2001-06-05 | Foveon, Inc. | CMOS active pixel sensor using native transistors |

| JP4384759B2 (ja) * | 1998-09-14 | 2009-12-16 | テキサス インスツルメンツ インコーポレイテツド | Mos集積回路の特性を改良するためのボディ電圧のパルス動作 |

| US6484265B2 (en) * | 1998-12-30 | 2002-11-19 | Intel Corporation | Software control of transistor body bias in controlling chip parameters |

| JP4390305B2 (ja) * | 1999-01-04 | 2009-12-24 | 株式会社ルネサステクノロジ | 半導体装置 |

| US6271713B1 (en) * | 1999-05-14 | 2001-08-07 | Intel Corporation | Dynamic threshold source follower voltage driver circuit |

| JP2001034040A (ja) * | 1999-07-21 | 2001-02-09 | Sharp Corp | 接触帯電装置ならびにそれを備えたプロセスカートリッジおよび画像形成装置 |

| US6448840B2 (en) * | 1999-11-30 | 2002-09-10 | Intel Corporation | Adaptive body biasing circuit and method |

| EP1236209B2 (en) * | 1999-11-30 | 2014-04-09 | PRYSMIAN Kabel und Systeme GmbH | Electrical cable having a hardgrade-epr insulation |

| KR100347140B1 (ko) * | 1999-12-31 | 2002-08-03 | 주식회사 하이닉스반도체 | 전압 변환 회로 |

| KR20010077099A (ko) * | 2000-01-31 | 2001-08-17 | 윤종용 | 자기 정렬된 웰 바이어스 영역을 갖는 모스 트랜지스터 및그 제조방법 |

| JP2001230664A (ja) * | 2000-02-15 | 2001-08-24 | Mitsubishi Electric Corp | 半導体集積回路 |

| US20020140496A1 (en) * | 2000-02-16 | 2002-10-03 | Ali Keshavarzi | Forward body biased transistors with reduced temperature |

| JP2001339045A (ja) * | 2000-05-25 | 2001-12-07 | Hitachi Ltd | 半導体集積回路装置 |

| US6549032B1 (en) * | 2000-08-22 | 2003-04-15 | Altera Corporation | Integrated circuit devices with power supply detection circuitry |

| TW463466B (en) * | 2000-08-30 | 2001-11-11 | Silicon Integrated Sys Corp | Current A/D converter and the unit cell thereof |

| TW448617B (en) * | 2000-09-15 | 2001-08-01 | Silicon Integrated Sys Corp | N-well bias preset circuit for CMOS and the method thereof |

| US6343044B1 (en) * | 2000-10-04 | 2002-01-29 | International Business Machines Corporation | Super low-power generator system for embedded applications |

| US6744301B1 (en) * | 2000-11-07 | 2004-06-01 | Intel Corporation | System using body-biased sleep transistors to reduce leakage power while minimizing performance penalties and noise |

| JP2002191169A (ja) * | 2000-12-20 | 2002-07-05 | Mitsubishi Electric Corp | 半導体集積回路 |

| KR100385230B1 (ko) * | 2000-12-28 | 2003-05-27 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치의 프로그램 방법 |

| US6373281B1 (en) * | 2001-01-22 | 2002-04-16 | International Business Machines Corporation | Tri-state dynamic body charge modulation for sensing devices in SOI RAM applications |

| US6597203B2 (en) * | 2001-03-14 | 2003-07-22 | Micron Technology, Inc. | CMOS gate array with vertical transistors |

| US6757196B1 (en) * | 2001-03-22 | 2004-06-29 | Aplus Flash Technology, Inc. | Two transistor flash memory cell for use in EEPROM arrays with a programmable logic device |

| US6429726B1 (en) * | 2001-03-27 | 2002-08-06 | Intel Corporation | Robust forward body bias generation circuit with digital trimming for DC power supply variation |

| US6469572B1 (en) * | 2001-03-28 | 2002-10-22 | Intel Corporation | Forward body bias generation circuits based on diode clamps |

| US6670655B2 (en) * | 2001-04-18 | 2003-12-30 | International Business Machines Corporation | SOI CMOS device with body to gate connection |

| US6605981B2 (en) * | 2001-04-26 | 2003-08-12 | International Business Machines Corporation | Apparatus for biasing ultra-low voltage logic circuits |

| GB0111300D0 (en) * | 2001-05-09 | 2001-06-27 | Mitel Knowledge Corp | Method and apparatus for synchronizing slave network node to master network node |

| JP2002343083A (ja) * | 2001-05-18 | 2002-11-29 | Mitsubishi Electric Corp | 半導体装置 |

| US6554249B2 (en) * | 2001-05-30 | 2003-04-29 | Fmc Technologies, Inc. | Plug valve having seal segments with booster springs |

| US6483375B1 (en) * | 2001-06-28 | 2002-11-19 | Intel Corporation | Low power operation mechanism and method |

| US6518826B2 (en) * | 2001-06-28 | 2003-02-11 | Intel Corporation | Method and apparatus for dynamic leakage control |

| US6763484B2 (en) * | 2001-06-28 | 2004-07-13 | Intel Corporation | Body bias using scan chains |

| US6559702B2 (en) * | 2001-07-19 | 2003-05-06 | Texas Instruments Incorporated | Bias generator and method for improving output skew voltage |

| US6529421B1 (en) * | 2001-08-28 | 2003-03-04 | Micron Technology, Inc. | SRAM array with temperature-compensated threshold voltage |

| US6621325B2 (en) * | 2001-09-18 | 2003-09-16 | Xilinx, Inc. | Structures and methods for selectively applying a well bias to portions of a programmable device |

| US6630700B2 (en) * | 2001-10-05 | 2003-10-07 | Motorola, Inc. | NMOS circuit in isolated wells that are connected by a bias stack having pluralirty of diode elements |

| JP4090231B2 (ja) * | 2001-11-01 | 2008-05-28 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US6650141B2 (en) * | 2001-12-14 | 2003-11-18 | Lattice Semiconductor Corporation | High speed interface for a programmable interconnect circuit |

| US6614301B2 (en) * | 2002-01-31 | 2003-09-02 | Intel Corporation | Differential amplifier offset adjustment |

| US20030151428A1 (en) * | 2002-02-12 | 2003-08-14 | Ouyang Paul H. | 5 Volt tolerant input/output buffer |

| US6525559B1 (en) * | 2002-04-22 | 2003-02-25 | Pericom Semiconductor Corp. | Fail-safe circuit with low input impedance using active-transistor differential-line terminators |

| US7254603B2 (en) * | 2002-05-03 | 2007-08-07 | Sonics, Inc. | On-chip inter-network performance optimization using configurable performance parameters |

| JP4401621B2 (ja) * | 2002-05-07 | 2010-01-20 | 株式会社日立製作所 | 半導体集積回路装置 |

| JP3821047B2 (ja) * | 2002-05-09 | 2006-09-13 | 富士電機デバイステクノロジー株式会社 | 電圧可変レギュレータ |

| US6870213B2 (en) * | 2002-05-10 | 2005-03-22 | International Business Machines Corporation | EEPROM device with substrate hot-electron injector for low-power |

| US20030218478A1 (en) * | 2002-05-24 | 2003-11-27 | Sani Mehdi Hamidi | Regulation of crowbar current in circuits employing footswitches/headswitches |

| US6731158B1 (en) * | 2002-06-13 | 2004-05-04 | University Of New Mexico | Self regulating body bias generator |

| KR20050065518A (ko) | 2002-08-08 | 2005-06-29 | 코닌클리즈케 필립스 일렉트로닉스 엔.브이. | 제어 유닛, 집적 회로 장치, 및 트랜지스터의 적어도하나의 임계 전압을 제어하는 방법 |

| US6972599B2 (en) * | 2002-08-27 | 2005-12-06 | Micron Technology Inc. | Pseudo CMOS dynamic logic with delayed clocks |

| US7120804B2 (en) * | 2002-12-23 | 2006-10-10 | Intel Corporation | Method and apparatus for reducing power consumption through dynamic control of supply voltage and body bias including maintaining a substantially constant operating frequency |

| KR100553681B1 (ko) * | 2003-03-06 | 2006-02-24 | 삼성전자주식회사 | 전압 레귤레이터 회로 및 그것을 이용한 불 휘발성 반도체메모리 장치 |

| US6972593B1 (en) * | 2003-08-05 | 2005-12-06 | Altera Corp. | Method and apparatus for protecting a circuit during a hot socket condition |

| US6975535B2 (en) * | 2003-08-14 | 2005-12-13 | Mosel Vitelic, Inc. | Electronic memory, such as flash EPROM, with bitwise-adjusted writing current or/and voltage |

| US7098689B1 (en) * | 2003-09-19 | 2006-08-29 | Xilinx, Inc. | Disabling unused/inactive resources in programmable logic devices for static power reduction |

| JP4221274B2 (ja) * | 2003-10-31 | 2009-02-12 | 株式会社東芝 | 半導体集積回路および電源電圧・基板バイアス制御回路 |

| JP2005157620A (ja) * | 2003-11-25 | 2005-06-16 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| US6972616B2 (en) * | 2004-04-14 | 2005-12-06 | Broadcom Corporation | Low-noise, fast-settling bias circuit and method |

| JP2004241122A (ja) * | 2004-05-06 | 2004-08-26 | Matsushita Electric Ind Co Ltd | レギュレータ |

| US7112997B1 (en) * | 2004-05-19 | 2006-09-26 | Altera Corporation | Apparatus and methods for multi-gate silicon-on-insulator transistors |

| US7348827B2 (en) * | 2004-05-19 | 2008-03-25 | Altera Corporation | Apparatus and methods for adjusting performance of programmable logic devices |

| US7129745B2 (en) * | 2004-05-19 | 2006-10-31 | Altera Corporation | Apparatus and methods for adjusting performance of integrated circuits |

| US7119604B2 (en) * | 2004-06-17 | 2006-10-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Back-bias voltage regulator having temperature and process variation compensation and related method of regulating a back-bias voltage |

| US20060119382A1 (en) * | 2004-12-07 | 2006-06-08 | Shumarayev Sergey Y | Apparatus and methods for adjusting performance characteristics of programmable logic devices |

| US7330049B2 (en) * | 2006-03-06 | 2008-02-12 | Altera Corporation | Adjustable transistor body bias generation circuitry with latch-up prevention |

-

2006

- 2006-03-06 US US11/369,664 patent/US7495471B2/en not_active Expired - Fee Related

-

2007

- 2007-02-13 EP EP07003010A patent/EP1833152A1/en not_active Withdrawn

- 2007-02-22 JP JP2007042839A patent/JP4648346B2/ja not_active Expired - Fee Related

- 2007-02-28 CN CNA2007100847338A patent/CN101257300A/zh active Pending

-

2008

- 2008-06-27 US US12/163,695 patent/US7592832B2/en not_active Expired - Fee Related

Cited By (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101814829B (zh) * | 2010-04-22 | 2015-09-16 | 上海华虹宏力半导体制造有限公司 | 电荷泵电路的参考电压产生电路及电荷泵电路 |

| CN101814829A (zh) * | 2010-04-22 | 2010-08-25 | 上海宏力半导体制造有限公司 | 电荷泵电路的参考电压产生电路及电荷泵电路 |

| US9344090B2 (en) | 2011-05-16 | 2016-05-17 | Semiconductor Energy Laboratory Co., Ltd. | Programmable logic device |

| CN103534950A (zh) * | 2011-05-16 | 2014-01-22 | 株式会社半导体能源研究所 | 可编程逻辑装置 |

| CN103534950B (zh) * | 2011-05-16 | 2017-07-04 | 株式会社半导体能源研究所 | 可编程逻辑装置 |

| CN102903384A (zh) * | 2011-07-25 | 2013-01-30 | 旺宏电子股份有限公司 | 待机电荷升压器装置及其操作方法 |

| CN102903384B (zh) * | 2011-07-25 | 2015-09-30 | 旺宏电子股份有限公司 | 待机电荷升压器装置及其操作方法 |

| CN105308530A (zh) * | 2013-05-17 | 2016-02-03 | 英特尔公司 | 使用动态电路基准的片上电源发生器 |

| US9857814B2 (en) | 2013-05-17 | 2018-01-02 | Intel Corporation | On-chip supply generator using dynamic circuit reference |

| CN104601163A (zh) * | 2013-10-30 | 2015-05-06 | 飞思卡尔半导体公司 | 体偏置控制电路 |

| CN104601163B (zh) * | 2013-10-30 | 2019-05-28 | 恩智浦美国有限公司 | 体偏置控制电路 |

| CN106253665A (zh) * | 2016-08-29 | 2016-12-21 | 深圳市华星光电技术有限公司 | 增加升降压幅度的电荷泵 |

| CN106253665B (zh) * | 2016-08-29 | 2019-06-25 | 深圳市华星光电技术有限公司 | 增加升降压幅度的电荷泵 |

| CN107357351A (zh) * | 2017-08-15 | 2017-11-17 | 电子科技大学 | 一种基于自供电电荷泵架构的nmos ldo |

| CN107357351B (zh) * | 2017-08-15 | 2018-10-26 | 电子科技大学 | 一种基于自供电电荷泵架构的nmos ldo |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007243178A (ja) | 2007-09-20 |

| EP1833152A1 (en) | 2007-09-12 |

| JP4648346B2 (ja) | 2011-03-09 |

| US20070205824A1 (en) | 2007-09-06 |

| US20080258802A1 (en) | 2008-10-23 |

| US7495471B2 (en) | 2009-02-24 |

| US7592832B2 (en) | 2009-09-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101257300A (zh) | 可调式晶体管体偏置电路 | |

| US7639067B1 (en) | Integrated circuit voltage regulator | |

| US7184348B2 (en) | Sensing circuit for a semiconductor memory | |

| US5039882A (en) | Address decoder circuit for non-volatile memory | |

| US7777466B2 (en) | Voltage regulator or non-volatile memories implemented with low-voltage transistors | |

| US7656225B2 (en) | Voltage generation circuit and semiconductor memory device including the same | |

| JP2008117215A (ja) | 基準電位発生回路 | |

| US9536575B2 (en) | Power source for memory circuitry | |

| US5905677A (en) | Voltage regulator for non-volatile semiconductor electrically programmable memory devices | |

| US9971372B2 (en) | Voltage regulators | |

| US6424134B2 (en) | Semiconductor integrated circuit device capable of stably generating internal voltage independent of an external power supply voltage | |

| US9881654B2 (en) | Power source for memory circuitry | |

| TWI235294B (en) | Reference voltage generating circuit and internal voltage generating circuit for controlling internal voltage level | |

| US6559710B2 (en) | Raised voltage generation circuit | |

| US6366505B1 (en) | Device for controlling a translator-type high voltage selector switch | |

| CN111638743B (zh) | 电流电压转换电路、基准电压产生电路及半导体存储装置 | |

| CN110211623B (zh) | 一种nor flash存储单元阵列的电源系统 | |

| US9928921B2 (en) | Non-volatile memory, semiconductor device and reading method | |

| US5691944A (en) | Non-volatile semiconductor memory device | |

| US7317334B2 (en) | Voltage translator circuit and semiconductor memory device | |

| US20050052214A1 (en) | Level shifter circuit | |

| KR20080060322A (ko) | 반도체 소자의 내부전압 발생기 | |

| US8619489B2 (en) | Driving circuit for memory device | |

| JP2002150786A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Open date: 20080903 |