JP4648346B2 - 調整可能なトランジスタボディバイアス回路網 - Google Patents

調整可能なトランジスタボディバイアス回路網 Download PDFInfo

- Publication number

- JP4648346B2 JP4648346B2 JP2007042839A JP2007042839A JP4648346B2 JP 4648346 B2 JP4648346 B2 JP 4648346B2 JP 2007042839 A JP2007042839 A JP 2007042839A JP 2007042839 A JP2007042839 A JP 2007042839A JP 4648346 B2 JP4648346 B2 JP 4648346B2

- Authority

- JP

- Japan

- Prior art keywords

- voltage

- adjustable

- charge pump

- body bias

- integrated circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 claims description 38

- 229910044991 metal oxide Inorganic materials 0.000 claims description 37

- 150000004706 metal oxides Chemical class 0.000 claims description 37

- 239000003990 capacitor Substances 0.000 description 23

- 238000010586 diagram Methods 0.000 description 15

- 239000004020 conductor Substances 0.000 description 7

- 238000011960 computer-aided design Methods 0.000 description 6

- 230000006870 function Effects 0.000 description 4

- 238000000034 method Methods 0.000 description 4

- 230000002829 reductive effect Effects 0.000 description 4

- 230000008901 benefit Effects 0.000 description 3

- 230000008859 change Effects 0.000 description 3

- 230000007423 decrease Effects 0.000 description 3

- 239000007943 implant Substances 0.000 description 3

- 230000002411 adverse Effects 0.000 description 2

- 238000013459 approach Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 230000003068 static effect Effects 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 210000000746 body region Anatomy 0.000 description 1

- 230000000295 complement effect Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000013461 design Methods 0.000 description 1

- 238000012938 design process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 229910052814 silicon oxide Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

- H03K19/1778—Structural details for adapting physical parameters

- H03K19/17784—Structural details for adapting physical parameters for supply voltage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0013—Arrangements for reducing power consumption in field effect transistor circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/06—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider

- H02M3/07—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using resistors or capacitors, e.g. potential divider using capacitors charged and discharged alternately by semiconductor devices with control electrode, e.g. charge pumps

- H02M3/073—Charge pumps of the Schenkel-type

- H02M3/078—Charge pumps of the Schenkel-type with means for reducing the back bias effect, i.e. the effect which causes the threshold voltage of transistors to increase as more stages are added to the converters

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K2217/00—Indexing scheme related to electronic switching or gating, i.e. not by contact-making or -breaking covered by H03K17/00

- H03K2217/0018—Special modifications or use of the back gate voltage of a FET

Landscapes

- Physics & Mathematics (AREA)

- Mathematical Physics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Computing Systems (AREA)

- General Engineering & Computer Science (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Dc-Dc Converters (AREA)

- Logic Circuits (AREA)

Description

本発明は、トランジスタボディバイアス回路に関するもので、より特定的には、プログラマブルロジックデバイスなどの集積回路のための調整可能なトランジスタボディバイアス回路に関する。

本発明に従って、調整可能なボディバイアス回路網を含むプログラマブルロジックデバイス集積回路などの集積回路が提供される。調整可能なボディバイアス回路網は制御信号によって制御される。制御信号は、構成データがロードされたプログラマブルエレメントから供給され得、集積回路上のプログラマブルロジックによって供給され得、または、外部ソースから得られ得る。デコーダは、デコードされない制御信号をデコードするために使用され得る。

(項目1)

集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

マイナスボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網と

を備える、集積回路。

(項目2)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、

構成データがロードされるプログラマブルエレメント

をさらに備える、請求項1に記載の集積回路。

(項目3)

上記調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備える、請求項1に記載の集積回路。

(項目4)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備え、該集積回路は、

構成データがロードされるプログラマブルエレメント

をさらに備える、請求項1に記載の集積回路。

(項目5)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備え、該集積回路は、

構成データがロードされるプログラマブルエレメント

をさらに備え、該プログラマブルエレメントのいくつかは、該調整可能な電圧レギュレータを制御する出力信号を生成する、請求項1に記載の集積回路。

(上記6)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備え、該集積回路は、

構成データがロードされるプログラマブルエレメントであって、該プログラマブルエレメントのいくつかは、デコードされない制御信号を生成する、プログラマブルエレメントと、

デコーダであって、該デコードされない制御信号を受信し、対応するデコードされた制御信号を該調整可能な電圧レギュレータに印加する、デコーダと

をさらに備える、請求項1に記載の集積回路。

(項目7)

上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成する調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目8)

上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成する調整可能な電圧レギュレータと、

少なくとも一つの基準信号を該調整可能な電圧レギュレータに印加するバンドギャップ基準回路と

を備える、請求項1に記載の集積回路。

(項目9)

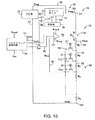

上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路であって、該チャージポンプ回路は、分圧器、比較器、発振器、およびチャージポンプを含む、チャージポンプ回路と、

該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成する調整可能な電圧レギュレータと、

少なくとも一つの基準信号を該調整可能な電圧レギュレータに印加するバンドギャップ基準回路であって、該チャージポンプ回路における該分圧器は、フィードバック線を介して該チャージポンプから該マイナスチャージポンプ出力電圧を受信し、対応する信号を該比較器の第1入力に供給し、該比較器は、第2入力において該バンドギャップ基準回路から電圧基準信号を受信し、該比較器は、該第1入力と該第2入力を比較し、該発振器を制御する対応する出力を生成し、該発振器は、該チャージポンプのためにクロック信号を生成する、バンドギャップ基準回路と

を備える、請求項1に記載の集積回路。

(項目10)

上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目11)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントをさらに備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために、該プログラマブルエレメントの少なくともいくつかの出力から該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目12)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントをさらに備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

出力を有するデコーダと、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために、該デコーダの出力から該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目13)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントをさらに備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

出力および入力を有するデコーダであって、該入力は該プログラマブルエレメントの少なくともいくつかから制御信号を受信する、デコーダと、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために、該デコーダの出力から該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目14)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントおよび入出力ピンをさらに備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

出力および入力を有するデコーダであって、該入力は該入出力ピンを介して制御信号を受信する、デコーダと、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために、該デコーダの出力から該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目15)

上記集積回路は、プログラマブルロジックデバイス集積回路を備え、該集積回路は、構成データがロードされるプログラマブルエレメントおよび信号を生成するプログラマブルロジックをさらに備え、上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

出力および入力を有するデコーダであって、該入力は該プログラマブルロジックからの信号の少なくともいくつかを受信する、デコーダと、

調整可能な分圧器を含む調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、該マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、該直列接続された抵抗器における電圧タップポイント位置を規定するために、該デコーダの出力から該トランジスタのゲートに印加された制御信号によって制御される、調整可能な電圧レギュレータと

を備える、請求項1に記載の集積回路。

(項目16)

上記調整可能なチャージポンプベースのボディバイアス回路網は、

マイナスチャージポンプ出力電圧を生成する複数の金属酸化物半導体コンデンサを含むチャージポンプ回路と、

少なくとも一つの基準信号を供給するバンドギャップ基準回路と、

調整可能な電圧レギュレータと、

を備え、

該調整可能な電圧レギュレータは、上記直列接続の抵抗器の連鎖と、関係したタップ電圧を規定する選択可能な分圧器タップポイントを確立するために直列接続の抵抗器のそれぞれのペア間に接続された複数のトランジスタと、演算増幅器であって、該バンドギャップ基準回路から該基準信号を受信する第1入力を有し、第2入力を有し、および出力を有する演算増幅器と、該タップ電圧を該第2入力に供給するフィードバックパスと、該チャージポンプと該直列接続の抵抗器の連鎖との間に接続されたトランジスタであって、該トランジスタは、該演算増幅器の出力に接続されたゲートを有する、トランジスタと

を備える、請求項1に記載の集積回路。

(項目17)

集積回路上にあるトランジスタボディバイアス回路であって、

マイナス電圧を生成するチャージポンプと、

該チャージポンプからの該マイナス電圧を使用してマイナストランジスタボディバイアス電圧を生成する調整可能な電圧レギュレータと

を備える、トランジスタボディバイアス回路。

(項目18)

対応する出力信号を生成する構成データがロードされる複数のプログラマブルエレメント

をさらに備え、上記調整可能電圧レギュレータは、複数のトランジスタを有する分圧器を有し、該分圧器の各々は、該複数のプログラマブルエレメントのそれぞれの一つから該出力信号の一つを受信するゲートを有する、請求項17に記載のトランジスタボディバイアス回路。

(項目19)

対応する出力信号を生成する構成データがロードされる複数のプログラマブルエレメントと、

少なくとも一つの基準信号を上記調整可能な電圧レギュレータに供給するバンドギャップ基準回路と

をさらに備え、該調整可能な電圧レギュレータは、調整可能な分圧器を含み、該調整可能な電圧レギュレータは、上記チャージポンプによって生成される上記マイナス電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の抵抗器および複数のトランジスタを含み、該トランジスタは、該抵抗器のそれぞれのペア間に接続され、該トランジスタはゲートを有し、そのゲートの各々は、該プログラマブルエレメントの対応する一つからそれぞれの出力信号を受信する、請求項17に記載のトランジスタボディバイアス回路。

(項目20)

上記チャージポンプは、金属酸化物半導体コンデンサとして構成される金属酸化物半導体トランジスタ構造を備え、該ボディバイアス回路は、

対応する出力信号を生成する構成データがロードされる複数のプログラマブルエレメントと、

少なくとも一つの基準信号を上記調整可能な電圧レギュレータに供給するバンドギャップ基準回路と

をさらに備え、該調整可能な電圧レギュレータは、調整可能な分圧器を含み、該調整可能な電圧レギュレータは、演算増幅器を備え、上記チャージポンプによって生成される上記マイナス電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の抵抗器および複数のトランジスタを含み、該トランジスタは、該抵抗器のそれぞれのペア間に接続され、該トランジスタは、ゲートを有し、そのゲートの各々は該プログラマブルエレメントの対応する一つからそれぞれの出力信号を受信し、該構成データは、該マイナスボディバイス電圧を決定する該演算増幅器への該分圧器からのフィードバックパスを規定するために、該トランジスタの所定の一つをオンにする、請求項17に記載のトランジスタボディバイアス回路。

(項目21)

プログラマブルロジックデバイス集積回路であって、

マイナスボディバイアス電圧が印加されるボディ端子を有するnチャネル金属酸化物半導体トランジスタを含むプログラマブルロジックと、

基準電圧を供給するバンドギャップ基準回路と、

端子を有する調整可能な電圧レギュレータであって、該端子は、マイナスチャージポンプ出力電圧を受信し、該バンドギャップ基準回路からの該基準電圧を受信し、該マイナスボディバイアス電圧を該プログラマブルロジックにおける該nチャネル金属酸化物半導体の該ボディ端子に供給する、調整可能な電圧レギュレータと

を備える、プログラマブルロジックデバイス集積回路。

(項目22)

構成データがロードされるプログラマブルエレメント

をさらに備え、

該プログラマブルエレメントのいくつかは、上記調整可能な電圧レギュレータを制御する出力信号を生成する、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目23)

上記調整可能な電圧レギュレータによって受信される上記マイナスチャージポンプ出力電圧を生成するチャージポンプ回路

をさらに備え、該調整可能電圧レギュレータは該マイナスポンプ出力電圧を使用して該マイナスボディバイス電圧を生成する、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目24)

上記調整可能な電圧レギュレータは、調整可能な分圧器を備え、上記プログラマブルロジックデバイスは、

該調整可能な分圧器によって受信される上記マイナスチャージポンプ出力電圧を生成するチャージポンプ回路

をさらに備える、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目25)

発振器と、

比較器と、

上記マイナスチャージポンプ出力電圧を生成するチャージポンプと、

フィードバック線を介して、該チャージポンプから該マイナスチャージポンプ出力電圧を受信し、対応する信号を該比較器の第1入力に供給する分圧器と

をさらに備え、該比較器は、該基準電圧を第2入力における上記バンドギャップ基準回路から受信し、該比較器は、該第1入力および第2入力と比較し、該発振器を制御する対応する出力を生成し、該発振器は該チャージポンプのためにクロック信号を生成する、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目26)

上記プログラマブルロジックは、構成データがロードされるプログラマブルエレメントを備え、上記調整可能な電圧レギュレータは、

複数の直列接続された抵抗器および複数のトランジスタを含む調整可能な分圧器

を備え、該調整可能な電圧レギュレータは、上記マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、直列接続された抵抗器における電圧タップポイント位置を規定するために、該プログラマブルエレメントの少なくともいくつかの出力から該トランジスタのゲートに印加される制御信号によって制御される、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目27)

上記プログラマブルロジックデバイス集積回路は、

上記マイナスチャージポンプ出力電圧を生成するチャージポンプ回路と、

出力および入力を有するデコーダと

を備え、該入力は制御信号を受信し、上記調整可能な電圧レギュレータは、上記マイナスチャージポンプ出力電圧を使用して上記マイナスボディバイアス電圧を生成し、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器および複数のトランジスタを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペア間に接続され、該トランジスタは、直列接続された抵抗器における電圧タップポイント位置を規定するために、該デコーダの出力から該トランジスタのゲートに印加される制御信号によって制御される、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目28)

上記調整可能な電圧レギュレータは、

上記基準電圧を受信し、出力信号を供給する演算増幅器と、

該演算増幅器からの出力信号を受信するゲートを有するトランジスタと、

該トランジスタに接続された抵抗器の連鎖と

をさらに備える、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目29)

上記調整可能な電圧レギュレータは、

上記調整可能な分圧器における直列接続された抵抗器の連鎖と、

関係したタップ電圧を規定する選択可能な分圧器タップポイントを確立するために、該直列接続された抵抗器のそれぞれのペア間に接続される複数のトランジスタと

をさらに備える、請求項21に記載のプログラマブルロジックデバイス集積回路。

(項目30)

上記プログラマブルロジックデバイス集積回路は、

上記マイナスチャージポンプ出力電圧を供給するチャージポンプ

をさらに備え、上記調整可能電圧レギュレータは、

抵抗器と、

関係したタップ電圧を規定する選択可能な分圧器タップポイントを確立するために、該抵抗器のそれぞれのペア間に接続される複数のトランジスタと、

演算増幅器であって、上記バンドギャップ基準回路からの上記基準信号を受信する第1入力を有し、第2入力を有し、出力を有する、演算増幅器と、

該タップ電圧を該第2入力に供給するフィードバックパスと、

上記チャ-ジポンプと該抵抗器との間に接続されたトランジスタであって、該演算増幅器の出力に接続されたゲートを有する、トランジスタと

をさらに備える、請求項21に記載のプログラマブルロジックデバイス集積回路。

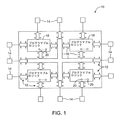

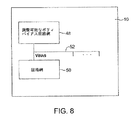

ボディ端子を有するnチャネルおよびpチャネル金属酸化物半導体トランジスタを含む集積回路が提供される。調整可能なトランジスタボディバイス回路網は、電力消費を最小にするために、ボディバイス電圧をボディ端子に供給する集積回路上に提供される。調整可能なボディバイアス回路網は、構成データがロードされる集積回路上のプログラマブルエレメントを使用して制御され得る。集積回路は、プログラマブルロジックを含むプログラマブルロジクデバイス集積回路であり得る。調整可能なボディバイス回路網は、nチャネル金属酸化物半導体トランジスタをバイアスするための調整可能なマイナスボディバイアス電圧を生成し得る。調整可能なボディバイアス回路網は、バンドギャップ基準回路、チャージポンプ回路、および調整可能な電圧レギュレータを含む。

本発明は、調整可能なボディバイアス電圧ソースに関する。ボディバイアス電圧ソースは、任意の適切な集積回路において使用され得る。一つの特に適切な配置と共に、本発明に従う調整可能なボディバイアス回路網は、プログラマブルロジックデバイス集積回路において使用される。ボディバイアス回路網はまた、プログラマブルロジックデバイスとは従来呼ばれないプログラマブル回路網を有する集積回路上でも使用される。そのプログラマブル回路網は、プログラマブル回路網を含むマイクロプロセッサ、プログラマブル回路網を含むディジタル信号プロセッサ、プログラマブル回路を有するカスタム集積回路などである。本発明は、例としてプログラマブルロジックデバイス集積回路に関連して一般的に記述される。

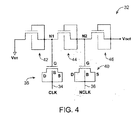

フィードバック回路網が提供され、これにより、デバイス10のnチャネル金属酸化物半導体トランジスタをバイアスするための安定した正確な電圧Vbiasを生成することが可能となる。チャージポンプは、約−1V(例として)の安定した電圧Vout(Vnegと呼ばれる)を生成する。分圧器は、数10または数100mVのVbias値を生成するために、Vnegのサイズを減少させる。これらのVbias値は、トランジスタ性能を不利益に影響することなく消費電力を減らすために、nチャネルトランジスタをバイアスするに典型的に必要とされる範囲内に入る。

のマイナス電源を形成する。電圧Vref2は、調整可能な電圧レギュレータ60のためのプラスの電源として働く。調整可能な電圧レギュレータ60は、多数の直列接続の抵抗器98から形成される調整可能な分圧器を有する。典型的な抵抗値は、約10kO〜50kOである。電圧レギュレータ60における抵抗器連鎖の一端は、電圧Vbiasに維持される。抵抗器チェーンのもう一方の端は、プラス電源Vref2に接続される。

12 入出力回路網

14 入出力ピン

16 相互接続リソース

18 プログラマブルロジック

20 プログラマブルエレメント

22 トランジスタ

24、28 インプラント領域

26 ゲート構造

30 p型ボディ領域

32 チャージポンプ

34、36 端子

38、40 コンデンサ

42、44、46 ダイオード

48 ボディバイアス回路網

50 回路網

52、58 パス

54 バンドギャプ基準回路

56 チャージポンプ回路

60 電圧レギュレータ

Claims (16)

- 集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

負のボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網であって、該集積回路は、プログラマブルロジックデバイス集積回路を備え、該調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備えている、調整可能なチャージポンプベースのボディバイアス回路網と

を備え、該集積回路は、構成データがロードされる複数のプログラマブルエレメントをさらに備え、該複数のプログラマブルエレメントのうちのいくつかは、該調整可能な電圧レギュレータを制御する出力信号を生成する、集積回路。 - 集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

負のボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網であって、該集積回路は、プログラマブルロジックデバイス集積回路を備え、該調整可能なチャージポンプベースのボディバイアス回路網は、調整可能な電圧レギュレータを備えている、調整可能なチャージポンプベースのボディバイアス回路網と

を備え、該集積回路は、構成データがロードされる複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちのいくつかは、デコードされない制御信号を生成する、複数のプログラマブルエレメントと、

該デコードされない制御信号を受信し、対応するデコードされる制御信号を該調整可能な電圧レギュレータに印加するデコーダと

をさらに備える、集積回路。 - 集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

負のボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網と

を備え、

該調整可能なチャージポンプベースのボディバイアス回路網は、

負のチャージポンプ出力電圧を生成するチャージポンプ回路と、

複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちの少なくともいくつかが、構成データがロードされ、出力信号を生成するプログラマブルエレメントである、複数のプログラマブルエレメントと、

該出力信号に基づいて、該負のチャージポンプ出力電圧を用いて、該負のボディバイアス電圧を生成する調整可能な電圧レギュレータと

を備える、集積回路。 - 前記調整可能なチャージポンプベースのボディバイアス回路網は、少なくとも1つの基準信号を前記調整可能な電圧レギュレータに印加するバンドギャップ基準回路をさらに備える、請求項3に記載の集積回路。

- 集積回路上のトランジスタボディバイアス回路であって、

負の電圧を生成するチャージポンプと、

複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちの少なくともいくつかが、構成データがロードされ、出力信号を生成するプログラマブルエレメントである、複数のプログラマブルエレメントと、

該出力信号に基づいて、該チャージポンプからの該負の電圧を用いて、負のトランジスタボディバイアス電圧を生成する調整可能な電圧レギュレータと

を備える、トランジスタボディバイアス回路。 - 前記少なくとも1つのプログラマブルエレメントは、対応する出力信号を生成する複数のプログラマブルエレメントを備え、前記調整可能な電圧レギュレータは、複数のトランジスタを有する分圧器を有し、該複数の分圧器のそれぞれは、該複数のプログラマブルエレメントのそれぞれの1つから該出力信号のうちの1つを受信するゲートを有する、請求項5に記載のトランジスタボディバイアス回路。

- プログラマブルロジックデバイス集積回路であって、

負のボディバイアス電圧が印加されるボディ端子を有するnチャネル金属酸化物半導体トランジスタを含むプログラマブルロジックと、

基準電圧を供給するバンドギャップ基準回路と、

端子を有する調整可能な電圧レギュレータであって、該端子は、負のチャージポンプ出力電圧を受信し、該バンドギャップ基準回路から該基準電圧を受信し、該負のボディバイアス電圧を該プログラマブルロジックにおける該nチャネル金属酸化物半導体トランジスタの該ボディ端子に供給する、調整可能な電圧レギュレータと、

構成データがロードされる複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちのいくつかが、該調整可能な電圧レギュレータを制御する出力信号を生成する、複数のプログラマブルエレメントと

を備える、プログラマブルロジックデバイス集積回路。 - 前記調整可能な電圧レギュレータによって受信される前記負のチャージポンプ出力電圧を生成するチャージポンプ回路をさらに備え、該調整可能な電圧レギュレータは、該負のチャージポンプ出力電圧を用いて、前記負のボディバイアス電圧を生成する、請求項7に記載のプログラマブルロジックデバイス集積回路。

- 前記調整可能な電圧レギュレータは、調整可能な分圧器を備え、前記プログラマブルロジックデバイスは、

該調整可能な分圧器によって受信される前記負のチャージポンプ出力電圧を生成するチャージポンプ回路をさらに備える、請求項7に記載のプログラマブルロジックデバイス集積回路。 - 前記調整可能な電圧レギュレータは、

前記基準電圧を受信し、出力信号を供給する演算増幅器と、

該演算増幅器から該出力信号を受信するゲートを有するトランジスタと、

該トランジスタに接続された抵抗器のチェーンと

をさらに備える、請求項7に記載のプログラマブルロジックデバイス集積回路。 - 前記調整可能な電圧レギュレータは、

前記調整可能な分圧器において直列接続された抵抗器のチェーンと、

関係したタップ電圧を規定する選択可能な分圧器タップポイントを確立するために、該直列接続された抵抗器のそれぞれのペア間に接続される複数のトランジスタと

をさらに備える、請求項7に記載のプログラマブルロジックデバイス集積回路。 - 集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

負のボディバイアス電圧を該ボディ端子へ印加する調整可能なチャージポンプベースのボディバイアス回路網と

を備え、該調整可能なチャージポンプベースのボディバイアス回路網は、

負のチャージポンプ出力電圧を生成するチャージポンプ回路と、

該負のチャージポンプ出力電圧を用いて、該負のボディバイアス電圧を生成する調整可能な電圧レギュレータであって、該調整可能な電圧レギュレータは、調整可能な分圧器を含み、該調整可能な電圧レギュレータは、複数の直列接続された抵抗器と複数のトランジスタとを含み、該トランジスタは、ゲートを有し、該直列接続された抵抗器のそれぞれのペアの間で接続され、該トランジスタは、該直列接続された抵抗器の電圧タップポイントの位置を規定するために、該トランジスタのゲートに印加される制御信号によって制御される、調整可能な電圧レギュレータと、

構成データがロードされる複数のプログラマブルエレメントであって、該トランジスタを制御する該制御信号は、該複数のプログラマブルエレメントの少なくともいくつかの出力から印加される、複数のプログラマブルエレメントと

を備えている、集積回路。 - 集積回路上のトランジスタボディバイアス回路であって、

負の電圧を生成するチャージポンプと、

該チャージポンプからの該負の電圧を用いて、負のトランジスタボディバイアス電圧を生成する調整可能な電圧レギュレータと、

複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちの少なくともいくつかが、構成データがロードされ、対応する出力信号を生成するプログラマブルエレメントであり、該対応する出力信号は、該調整可能な電圧レギュレータを制御するために該調整可能な電圧レギュレータに印加され、これにより、該負のトランジスタボディバイアス電圧が調整される、複数のプログラマブルエレメントと

を備える、トランジスタボディバイアス回路。 - 前記調整可能な電圧レギュレータは、複数のトランジスタを有する分圧器を備え、該複数のトランジスタの各々は、前記複数のプログラマブルエレメントのそれぞれ1つから該出力信号のうちの1つを受信するゲートを有する、請求項13に記載のトランジスタボディバイアス回路。

- 集積回路であって、

ボディ端子を有するnチャネル金属酸化物半導体トランジスタと、

調整可能なボディバイアス回路網であって、該調整可能なボディバイアス回路網は、少なくとも1つの制御信号を受信する制御入力経路を有し、該制御信号に基づいて負のボディバイアス電圧を該ボディ端子に印加する出力経路を有する、調整可能なボディバイアス回路網と、

複数のプログラマブルエレメントであって、該複数のプログラマブルエレメントのうちの少なくともいくつかが、構成データがロードされ、対応する出力信号を生成するプログラマブルエレメントであり、該対応する出力信号は、該調整可能なボディバイアス回路網を制御するために該調整可能なボディバイアス回路網に印加され、これにより、該負のボディバイアス電圧が調整される、複数のプログラマブルエレメントと

を備える、集積回路。 - 前記調整可能なボディバイアス回路網は、調整可能なチャージポンプベースのボディバイアス回路網を備える、請求項15に記載の集積回路。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/369,664 US7495471B2 (en) | 2006-03-06 | 2006-03-06 | Adjustable transistor body bias circuitry |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007243178A JP2007243178A (ja) | 2007-09-20 |

| JP2007243178A5 JP2007243178A5 (ja) | 2010-03-11 |

| JP4648346B2 true JP4648346B2 (ja) | 2011-03-09 |

Family

ID=38110608

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007042839A Expired - Fee Related JP4648346B2 (ja) | 2006-03-06 | 2007-02-22 | 調整可能なトランジスタボディバイアス回路網 |

Country Status (4)

| Country | Link |

|---|---|

| US (2) | US7495471B2 (ja) |

| EP (1) | EP1833152A1 (ja) |

| JP (1) | JP4648346B2 (ja) |

| CN (1) | CN101257300A (ja) |

Families Citing this family (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2007251351A (ja) | 2006-03-14 | 2007-09-27 | Renesas Technology Corp | 半導体装置 |

| US7642754B2 (en) * | 2006-06-08 | 2010-01-05 | Semiconductor Components Industries, L.L.C. | Method of forming a voltage regulator and structure therefor |

| KR100817058B1 (ko) * | 2006-09-05 | 2008-03-27 | 삼성전자주식회사 | 룩업 테이블을 이용한 바디 바이어싱 제어회로 및 이의바디 바이어싱 제어방법 |

| JP2008136047A (ja) * | 2006-11-29 | 2008-06-12 | Sony Corp | 固体撮像装置及び撮像装置 |

| US8183843B2 (en) * | 2007-01-26 | 2012-05-22 | Infineon Technologies Ag | Voltage regulator and associated methods |

| US8115462B2 (en) * | 2007-06-20 | 2012-02-14 | Atmel Corporation | Voltage regulator for an integrated circuit |

| US7800402B1 (en) * | 2007-11-05 | 2010-09-21 | Altera Corporation | Look-up table overdrive circuits |

| DE102008007029B4 (de) * | 2008-01-31 | 2014-07-03 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Betrieb einer elektronischen Schaltung mit körpergesteuertem Doppelkanaltransistor und SRAM-Zelle mit körpergesteuertem Doppelkanaltransistor |

| KR100961210B1 (ko) * | 2008-11-04 | 2010-06-09 | 주식회사 하이닉스반도체 | 제어신호생성회로 및 이를 이용하는 센스앰프회로 |

| US8081502B1 (en) | 2008-12-29 | 2011-12-20 | Altera Corporation | Memory elements with body bias control |

| US8742831B2 (en) * | 2009-02-23 | 2014-06-03 | Honeywell International Inc. | Method for digital programmable optimization of mixed-signal circuits |

| CN101867015A (zh) * | 2009-04-16 | 2010-10-20 | 台湾积体电路制造股份有限公司 | 通过施加p-衬底偏压和调节阈值电压提高磁性隧道结的编程电流 |

| CN101814829B (zh) * | 2010-04-22 | 2015-09-16 | 上海华虹宏力半导体制造有限公司 | 电荷泵电路的参考电压产生电路及电荷泵电路 |

| KR101143470B1 (ko) | 2010-07-02 | 2012-05-08 | 에스케이하이닉스 주식회사 | 전압 정류 회로 |

| US8416011B2 (en) | 2010-11-08 | 2013-04-09 | Lsi Corporation | Circuit and method for generating body bias voltage for an integrated circuit |

| KR101889383B1 (ko) * | 2011-05-16 | 2018-08-17 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 프로그래머블 로직 디바이스 |

| US8416009B2 (en) | 2011-07-13 | 2013-04-09 | International Business Machines Corporation | Solutions for controlling bulk bias voltage in an extremely thin silicon-on-insulator (ETSOI) integrated circuit chip |

| US9024679B2 (en) * | 2011-07-25 | 2015-05-05 | Macronix International Co., Ltd. | Standby charge pump system |

| DE102013022449B3 (de) | 2012-05-11 | 2019-11-07 | Semiconductor Energy Laboratory Co., Ltd. | Halbleitervorrichtung und elektronisches Gerät |

| US9348959B1 (en) * | 2012-06-29 | 2016-05-24 | Xilinx, Inc. | Optimizing supply voltage and threshold voltage |

| US8847565B2 (en) * | 2012-09-14 | 2014-09-30 | Nxp B.V. | Shunt regulator for adverse voltage/circuit conditions |

| US9112495B1 (en) * | 2013-03-15 | 2015-08-18 | Mie Fujitsu Semiconductor Limited | Integrated circuit device body bias circuits and methods |

| KR101903843B1 (ko) * | 2013-05-17 | 2018-10-02 | 인텔 코포레이션 | 동적 회로 기준을 이용하는 온-칩 공급 발생기 |

| JP6406926B2 (ja) | 2013-09-04 | 2018-10-17 | 株式会社半導体エネルギー研究所 | 半導体装置 |

| US9088280B2 (en) * | 2013-10-30 | 2015-07-21 | Freescale Semiconductor, Inc. | Body bias control circuit |

| US9577626B2 (en) | 2014-08-07 | 2017-02-21 | Skyworks Solutions, Inc. | Apparatus and methods for controlling radio frequency switches |

| KR102211167B1 (ko) | 2014-08-14 | 2021-02-02 | 삼성전자주식회사 | 바디 바이어스 전압 생성기 및 이를 포함하는 시스템-온-칩 |

| US9467124B2 (en) * | 2014-09-30 | 2016-10-11 | Skyworks Solutions, Inc. | Voltage generator with charge pump and related methods and apparatus |

| US9917507B2 (en) | 2015-05-28 | 2018-03-13 | Sandisk Technologies Llc | Dynamic clock period modulation scheme for variable charge pump load currents |

| US9647536B2 (en) | 2015-07-28 | 2017-05-09 | Sandisk Technologies Llc | High voltage generation using low voltage devices |

| WO2017037568A1 (en) * | 2015-08-31 | 2017-03-09 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device or electronic device including the semiconductor device |

| US9520776B1 (en) | 2015-09-18 | 2016-12-13 | Sandisk Technologies Llc | Selective body bias for charge pump transfer switches |

| CN106253665B (zh) * | 2016-08-29 | 2019-06-25 | 深圳市华星光电技术有限公司 | 增加升降压幅度的电荷泵 |

| CN108205349A (zh) * | 2016-12-19 | 2018-06-26 | 北京兆易创新科技股份有限公司 | 一种带隙基准电路 |

| US10483985B2 (en) * | 2017-01-23 | 2019-11-19 | Samsung Electronics Co., Ltd. | Oscillator using supply regulation loop and operating method thereof |

| KR102426729B1 (ko) | 2017-08-11 | 2022-07-29 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 불휘발성 메모리 장치의 동작 방법 |

| CN107357351B (zh) * | 2017-08-15 | 2018-10-26 | 电子科技大学 | 一种基于自供电电荷泵架构的nmos ldo |

| US10552563B2 (en) * | 2018-01-10 | 2020-02-04 | Qualcomm Incorporated | Digital design with bundled data asynchronous logic and body-biasing tuning |

| US10469097B1 (en) | 2018-12-06 | 2019-11-05 | Nxp Usa, Inc. | Body bias circuit for current steering DAC switches |

| US11271566B2 (en) * | 2018-12-14 | 2022-03-08 | Integrated Device Technology, Inc. | Digital logic compatible inputs in compound semiconductor circuits |

| KR102071354B1 (ko) * | 2019-11-13 | 2020-01-30 | 주식회사 스카이칩스 | 벅-부스트 직류-직류 변환 장치 |

| KR102696754B1 (ko) * | 2019-12-30 | 2024-08-21 | 에스케이하이닉스 주식회사 | 데이터 입출력 회로를 포함하는 메모리 장치 |

| US11894768B2 (en) * | 2020-04-27 | 2024-02-06 | Sony Semiconductor Solutions Corporation | DC/DC converter |

| KR20230140036A (ko) | 2022-03-29 | 2023-10-06 | 삼성전자주식회사 | 바디 바이어스 전압 생성기 및 이를 포함하는 반도체 장치 |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000066744A (ja) * | 1998-08-17 | 2000-03-03 | Nec Corp | レギュレータ内蔵半導体装置 |

| JP2003330551A (ja) * | 2002-05-09 | 2003-11-21 | Fuji Electric Co Ltd | 電圧可変レギュレータ |

| JP2004241122A (ja) * | 2004-05-06 | 2004-08-26 | Matsushita Electric Ind Co Ltd | レギュレータ |

| JP2004273103A (ja) * | 2003-03-06 | 2004-09-30 | Samsung Electronics Co Ltd | 電圧レギュレータ回路及び半導体メモリ装置 |

| JP2005503668A (ja) * | 2001-09-18 | 2005-02-03 | ザイリンクス インコーポレイテッド | プログラマブルデバイスの一部にウェルバイアスを選択的にかけるための構造および方法 |

| JP2005136322A (ja) * | 2003-10-31 | 2005-05-26 | Toshiba Corp | 半導体集積回路および電源電圧・基板バイアス制御回路 |

| JP2005157620A (ja) * | 2003-11-25 | 2005-06-16 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2006510121A (ja) * | 2002-12-23 | 2006-03-23 | インテル・コーポレーション | 供給電圧及びボディバイアスのダイナミック制御を通して電力消費を削減するための一つの方法及び装置 |

| JP2007538474A (ja) * | 2004-05-19 | 2007-12-27 | アルテラ コーポレイション | 集積回路の性能を調整するための装置および方法 |

Family Cites Families (78)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5103160A (en) * | 1991-04-25 | 1992-04-07 | Hughes Aircraft Company | Shunt regulator with tunnel oxide reference |

| DE4221575C2 (de) | 1992-07-01 | 1995-02-09 | Ibm | Integrierter CMOS-Halbleiterschaltkreis und Datenverarbeitungssystem mit integriertem CMOS-Halbleiterschaltkreis |

| US5341034A (en) | 1993-02-11 | 1994-08-23 | Benchmarq Microelectronics, Inc. | Backup battery power controller having channel regions of transistors being biased by power supply or battery |

| KR0169157B1 (ko) | 1993-11-29 | 1999-02-01 | 기다오까 다까시 | 반도체 회로 및 mos-dram |

| US5422591A (en) | 1994-01-03 | 1995-06-06 | Sgs-Thomson Microelectronics, Inc. | Output driver circuit with body bias control for multiple power supply operation |

| US5689209A (en) | 1994-12-30 | 1997-11-18 | Siliconix Incorporated | Low-side bidirectional battery disconnect switch |

| US5670907A (en) | 1995-03-14 | 1997-09-23 | Lattice Semiconductor Corporation | VBB reference for pumped substrates |

| JP2931776B2 (ja) | 1995-08-21 | 1999-08-09 | 三菱電機株式会社 | 半導体集積回路 |

| US5661685A (en) | 1995-09-25 | 1997-08-26 | Xilinx, Inc. | Programmable logic device with configurable power supply |

| US5600264A (en) | 1995-10-16 | 1997-02-04 | Xilinx, Inc. | Programmable single buffered six pass transistor configuration |

| US5689144A (en) | 1996-05-15 | 1997-11-18 | Siliconix Incorporated | Four-terminal power MOSFET switch having reduced threshold voltage and on-resistance |

| KR100189752B1 (ko) | 1996-06-01 | 1999-06-01 | 구본준 | 독립적인 웰 바이어스 전압을 가진 전압 펌프회로 |

| KR100203136B1 (ko) | 1996-06-27 | 1999-06-15 | 김영환 | 래치-업을 방지하는 상승전압발생기 |

| JP3264622B2 (ja) | 1996-07-16 | 2002-03-11 | 株式会社東芝 | 半導体装置 |

| US6593799B2 (en) | 1997-06-20 | 2003-07-15 | Intel Corporation | Circuit including forward body bias from supply voltage and ground nodes |

| US6411156B1 (en) | 1997-06-20 | 2002-06-25 | Intel Corporation | Employing transistor body bias in controlling chip parameters |

| US5841694A (en) | 1997-07-30 | 1998-11-24 | Programmable Silicon Solutions | High performance programmable interconnect |

| US6535034B1 (en) | 1997-07-30 | 2003-03-18 | Programmable Silicon Solutions | High performance integrated circuit devices adaptable to use lower supply voltages with smaller device geometries |

| US6346415B1 (en) * | 1997-10-21 | 2002-02-12 | Targeted Genetics Corporation | Transcriptionally-activated AAV inverted terminal repeats (ITRS) for use with recombinant AAV vectors |

| US6097242A (en) | 1998-02-26 | 2000-08-01 | Micron Technology, Inc. | Threshold voltage compensation circuits for low voltage and low power CMOS integrated circuits |

| US6157691A (en) | 1998-04-14 | 2000-12-05 | Lsi Logic Corporation | Fully integrated phase-locked loop with resistor-less loop filer |

| US6242728B1 (en) | 1998-08-20 | 2001-06-05 | Foveon, Inc. | CMOS active pixel sensor using native transistors |

| JP4384759B2 (ja) | 1998-09-14 | 2009-12-16 | テキサス インスツルメンツ インコーポレイテツド | Mos集積回路の特性を改良するためのボディ電圧のパルス動作 |

| US6484265B2 (en) | 1998-12-30 | 2002-11-19 | Intel Corporation | Software control of transistor body bias in controlling chip parameters |

| JP4390305B2 (ja) | 1999-01-04 | 2009-12-24 | 株式会社ルネサステクノロジ | 半導体装置 |

| US6271713B1 (en) | 1999-05-14 | 2001-08-07 | Intel Corporation | Dynamic threshold source follower voltage driver circuit |

| JP2001034040A (ja) | 1999-07-21 | 2001-02-09 | Sharp Corp | 接触帯電装置ならびにそれを備えたプロセスカートリッジおよび画像形成装置 |

| US6448840B2 (en) | 1999-11-30 | 2002-09-10 | Intel Corporation | Adaptive body biasing circuit and method |

| ES2310528T5 (es) * | 1999-11-30 | 2014-07-02 | Prysmian Kabel Und Systeme Gmbh | Cable eléctrico que incluye un aislamiento con un grado de dureza EPR |

| KR100347140B1 (ko) | 1999-12-31 | 2002-08-03 | 주식회사 하이닉스반도체 | 전압 변환 회로 |

| KR20010077099A (ko) | 2000-01-31 | 2001-08-17 | 윤종용 | 자기 정렬된 웰 바이어스 영역을 갖는 모스 트랜지스터 및그 제조방법 |

| JP2001230664A (ja) | 2000-02-15 | 2001-08-24 | Mitsubishi Electric Corp | 半導体集積回路 |

| US20020140496A1 (en) | 2000-02-16 | 2002-10-03 | Ali Keshavarzi | Forward body biased transistors with reduced temperature |

| JP2001339045A (ja) * | 2000-05-25 | 2001-12-07 | Hitachi Ltd | 半導体集積回路装置 |

| US6549032B1 (en) | 2000-08-22 | 2003-04-15 | Altera Corporation | Integrated circuit devices with power supply detection circuitry |

| TW463466B (en) | 2000-08-30 | 2001-11-11 | Silicon Integrated Sys Corp | Current A/D converter and the unit cell thereof |

| TW448617B (en) | 2000-09-15 | 2001-08-01 | Silicon Integrated Sys Corp | N-well bias preset circuit for CMOS and the method thereof |

| US6343044B1 (en) | 2000-10-04 | 2002-01-29 | International Business Machines Corporation | Super low-power generator system for embedded applications |

| US6744301B1 (en) | 2000-11-07 | 2004-06-01 | Intel Corporation | System using body-biased sleep transistors to reduce leakage power while minimizing performance penalties and noise |

| JP2002191169A (ja) * | 2000-12-20 | 2002-07-05 | Mitsubishi Electric Corp | 半導体集積回路 |

| KR100385230B1 (ko) | 2000-12-28 | 2003-05-27 | 삼성전자주식회사 | 불휘발성 반도체 메모리 장치의 프로그램 방법 |

| US6373281B1 (en) | 2001-01-22 | 2002-04-16 | International Business Machines Corporation | Tri-state dynamic body charge modulation for sensing devices in SOI RAM applications |

| US6597203B2 (en) | 2001-03-14 | 2003-07-22 | Micron Technology, Inc. | CMOS gate array with vertical transistors |

| US6757196B1 (en) | 2001-03-22 | 2004-06-29 | Aplus Flash Technology, Inc. | Two transistor flash memory cell for use in EEPROM arrays with a programmable logic device |

| US6429726B1 (en) | 2001-03-27 | 2002-08-06 | Intel Corporation | Robust forward body bias generation circuit with digital trimming for DC power supply variation |

| US6469572B1 (en) | 2001-03-28 | 2002-10-22 | Intel Corporation | Forward body bias generation circuits based on diode clamps |

| US6670655B2 (en) | 2001-04-18 | 2003-12-30 | International Business Machines Corporation | SOI CMOS device with body to gate connection |

| US6605981B2 (en) | 2001-04-26 | 2003-08-12 | International Business Machines Corporation | Apparatus for biasing ultra-low voltage logic circuits |

| GB0111300D0 (en) | 2001-05-09 | 2001-06-27 | Mitel Knowledge Corp | Method and apparatus for synchronizing slave network node to master network node |

| JP2002343083A (ja) | 2001-05-18 | 2002-11-29 | Mitsubishi Electric Corp | 半導体装置 |

| US6554249B2 (en) | 2001-05-30 | 2003-04-29 | Fmc Technologies, Inc. | Plug valve having seal segments with booster springs |

| US6518826B2 (en) | 2001-06-28 | 2003-02-11 | Intel Corporation | Method and apparatus for dynamic leakage control |

| US6483375B1 (en) | 2001-06-28 | 2002-11-19 | Intel Corporation | Low power operation mechanism and method |

| US6763484B2 (en) | 2001-06-28 | 2004-07-13 | Intel Corporation | Body bias using scan chains |

| US6559702B2 (en) | 2001-07-19 | 2003-05-06 | Texas Instruments Incorporated | Bias generator and method for improving output skew voltage |

| US6529421B1 (en) * | 2001-08-28 | 2003-03-04 | Micron Technology, Inc. | SRAM array with temperature-compensated threshold voltage |

| US6630700B2 (en) | 2001-10-05 | 2003-10-07 | Motorola, Inc. | NMOS circuit in isolated wells that are connected by a bias stack having pluralirty of diode elements |

| JP4090231B2 (ja) | 2001-11-01 | 2008-05-28 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US6650141B2 (en) | 2001-12-14 | 2003-11-18 | Lattice Semiconductor Corporation | High speed interface for a programmable interconnect circuit |

| US6614301B2 (en) | 2002-01-31 | 2003-09-02 | Intel Corporation | Differential amplifier offset adjustment |

| US20030151428A1 (en) | 2002-02-12 | 2003-08-14 | Ouyang Paul H. | 5 Volt tolerant input/output buffer |

| US6525559B1 (en) | 2002-04-22 | 2003-02-25 | Pericom Semiconductor Corp. | Fail-safe circuit with low input impedance using active-transistor differential-line terminators |

| US7254603B2 (en) | 2002-05-03 | 2007-08-07 | Sonics, Inc. | On-chip inter-network performance optimization using configurable performance parameters |

| JP4401621B2 (ja) | 2002-05-07 | 2010-01-20 | 株式会社日立製作所 | 半導体集積回路装置 |

| US6870213B2 (en) | 2002-05-10 | 2005-03-22 | International Business Machines Corporation | EEPROM device with substrate hot-electron injector for low-power |

| US20030218478A1 (en) | 2002-05-24 | 2003-11-27 | Sani Mehdi Hamidi | Regulation of crowbar current in circuits employing footswitches/headswitches |

| US6731158B1 (en) | 2002-06-13 | 2004-05-04 | University Of New Mexico | Self regulating body bias generator |

| AU2003250452A1 (en) | 2002-08-08 | 2004-02-25 | Koninklijke Philips Electronics N.V. | Circuit and method for controlling the threshold voltage of transistors |

| US6972599B2 (en) | 2002-08-27 | 2005-12-06 | Micron Technology Inc. | Pseudo CMOS dynamic logic with delayed clocks |

| US6972593B1 (en) | 2003-08-05 | 2005-12-06 | Altera Corp. | Method and apparatus for protecting a circuit during a hot socket condition |

| US6975535B2 (en) | 2003-08-14 | 2005-12-13 | Mosel Vitelic, Inc. | Electronic memory, such as flash EPROM, with bitwise-adjusted writing current or/and voltage |

| US7098689B1 (en) | 2003-09-19 | 2006-08-29 | Xilinx, Inc. | Disabling unused/inactive resources in programmable logic devices for static power reduction |

| US6972616B2 (en) | 2004-04-14 | 2005-12-06 | Broadcom Corporation | Low-noise, fast-settling bias circuit and method |

| US7348827B2 (en) | 2004-05-19 | 2008-03-25 | Altera Corporation | Apparatus and methods for adjusting performance of programmable logic devices |

| US7112997B1 (en) | 2004-05-19 | 2006-09-26 | Altera Corporation | Apparatus and methods for multi-gate silicon-on-insulator transistors |

| US7119604B2 (en) * | 2004-06-17 | 2006-10-10 | Taiwan Semiconductor Manufacturing Company, Ltd. | Back-bias voltage regulator having temperature and process variation compensation and related method of regulating a back-bias voltage |

| US20060119382A1 (en) | 2004-12-07 | 2006-06-08 | Shumarayev Sergey Y | Apparatus and methods for adjusting performance characteristics of programmable logic devices |

| US7330049B2 (en) | 2006-03-06 | 2008-02-12 | Altera Corporation | Adjustable transistor body bias generation circuitry with latch-up prevention |

-

2006

- 2006-03-06 US US11/369,664 patent/US7495471B2/en not_active Expired - Fee Related

-

2007

- 2007-02-13 EP EP07003010A patent/EP1833152A1/en not_active Withdrawn

- 2007-02-22 JP JP2007042839A patent/JP4648346B2/ja not_active Expired - Fee Related

- 2007-02-28 CN CNA2007100847338A patent/CN101257300A/zh active Pending

-

2008

- 2008-06-27 US US12/163,695 patent/US7592832B2/en not_active Expired - Fee Related

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2000066744A (ja) * | 1998-08-17 | 2000-03-03 | Nec Corp | レギュレータ内蔵半導体装置 |

| JP2005503668A (ja) * | 2001-09-18 | 2005-02-03 | ザイリンクス インコーポレイテッド | プログラマブルデバイスの一部にウェルバイアスを選択的にかけるための構造および方法 |

| JP2003330551A (ja) * | 2002-05-09 | 2003-11-21 | Fuji Electric Co Ltd | 電圧可変レギュレータ |

| JP2006510121A (ja) * | 2002-12-23 | 2006-03-23 | インテル・コーポレーション | 供給電圧及びボディバイアスのダイナミック制御を通して電力消費を削減するための一つの方法及び装置 |

| JP2004273103A (ja) * | 2003-03-06 | 2004-09-30 | Samsung Electronics Co Ltd | 電圧レギュレータ回路及び半導体メモリ装置 |

| JP2005136322A (ja) * | 2003-10-31 | 2005-05-26 | Toshiba Corp | 半導体集積回路および電源電圧・基板バイアス制御回路 |

| JP2005157620A (ja) * | 2003-11-25 | 2005-06-16 | Matsushita Electric Ind Co Ltd | 半導体集積回路 |

| JP2004241122A (ja) * | 2004-05-06 | 2004-08-26 | Matsushita Electric Ind Co Ltd | レギュレータ |

| JP2007538474A (ja) * | 2004-05-19 | 2007-12-27 | アルテラ コーポレイション | 集積回路の性能を調整するための装置および方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| US20070205824A1 (en) | 2007-09-06 |

| US7592832B2 (en) | 2009-09-22 |

| US7495471B2 (en) | 2009-02-24 |

| CN101257300A (zh) | 2008-09-03 |

| EP1833152A1 (en) | 2007-09-12 |

| JP2007243178A (ja) | 2007-09-20 |

| US20080258802A1 (en) | 2008-10-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4648346B2 (ja) | 調整可能なトランジスタボディバイアス回路網 | |

| US7639067B1 (en) | Integrated circuit voltage regulator | |

| US6498469B2 (en) | Internal supply voltage generating circuit and method of generating internal supply voltage using an internal reference voltage generating circuit and voltage-drop regulator | |

| US8085085B1 (en) | Substrate bias feedback scheme to reduce chip leakage power | |

| US7514953B2 (en) | Adjustable transistor body bias generation circuitry with latch-up prevention | |

| US7400123B1 (en) | Voltage regulator with variable drive strength for improved phase margin in integrated circuits | |

| US20100264899A1 (en) | Semiconductor device generating voltage for temperature compensation | |

| US7859301B2 (en) | Power regulator circuitry for programmable logic device memory elements | |

| JPH0926829A (ja) | 内部電源回路 | |

| US6429705B1 (en) | Resetting circuit independent of a transistor's threshold | |

| US20100039082A1 (en) | Low dropout voltage regulator with clamping | |

| US9081402B2 (en) | Semiconductor device having a complementary field effect transistor | |

| US6424134B2 (en) | Semiconductor integrated circuit device capable of stably generating internal voltage independent of an external power supply voltage | |

| US7816976B2 (en) | Power supply circuit using insulated-gate field-effect transistors | |

| US7626448B2 (en) | Internal voltage generator | |

| US6297688B1 (en) | Current generating circuit | |

| US20050093581A1 (en) | Apparatus for generating internal voltage capable of compensating temperature variation | |

| US8970257B2 (en) | Semiconductor device for offset compensation of reference current | |

| US8222952B2 (en) | Semiconductor device having a complementary field effect transistor | |

| US7576575B2 (en) | Reset signal generator in semiconductor device | |

| US20020175663A1 (en) | Reference voltage generator tolerant to temperature variations | |

| KR100607164B1 (ko) | 기준 전압 발생 회로 | |

| US20050104571A1 (en) | Power-up signal generating circuit | |

| KR20090047700A (ko) | 기준전압 발생회로 | |

| KR20040024789A (ko) | 안정된 내부 전압을 발생하는 내부전압 발생기 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100121 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20100121 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20100121 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20100212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100308 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20100608 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100713 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101012 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20101111 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20101209 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20131217 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4648346 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |