CN100512370C - 三值脉冲发生电路 - Google Patents

三值脉冲发生电路 Download PDFInfo

- Publication number

- CN100512370C CN100512370C CNB2006101420617A CN200610142061A CN100512370C CN 100512370 C CN100512370 C CN 100512370C CN B2006101420617 A CNB2006101420617 A CN B2006101420617A CN 200610142061 A CN200610142061 A CN 200610142061A CN 100512370 C CN100512370 C CN 100512370C

- Authority

- CN

- China

- Prior art keywords

- output

- voltage

- input

- switch

- pulse generation

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0002—Multistate logic

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/08—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices

- H03K19/094—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using semiconductor devices using field-effect transistors

- H03K19/09425—Multistate logic

Abstract

本发明提供一种三值脉冲发生电路,其可实现抑制开关元件的贯通电流来降低消耗电力。具备:包括三个逻辑元件(14a、14b、14c)的逻辑电路部(10)和包括由三个逻辑元件(14a、14b、14c)的各自输出而控制的三个开关元件(22、24、26)的开关控制部(20)。由三值脉冲发生电路(100)可以解决上述课题,该三值脉冲发生电路(100)通过按照使三个开关元件(22、24、26)不同时处于导通状态的方式进行控制,切换并输出互相不同的三个电压值(Vhigh、Vmid、Vlow)。

Description

技术领域

本发明涉及一种抑制开关元件的贯通电流,减少消耗电力的三值脉冲发生电路。

背景技术

固体摄像装置具备光电变换部和电荷传输部的功能,是一种用于通过电荷传输部传输由光电变换部对应入射光而生成的信息电荷,从而得到图像数据的装置。作为固体摄像装置例示了CCD(Charge Coupled Device)固体摄像装置。

例如,帧传输型CCD固体摄像装置具备:兼具光电变换元件和垂直移位寄存器的摄像部、具备对从摄像部传输而来的信息电荷的暂时进行缓存的垂直移位寄存器的蓄积部、具备从蓄积部将按每一行输出的信息电荷进行输送的水平移位寄存器的水平传输部、和输出与从水平传输部按每一位输出的信息电荷对应的电压的输出部。在帧传输型CCD固体摄像装置中,当进行摄像时,对摄像部中配置为矩阵状的光电变换元件的每一位生成与入射光强度对应的信息电荷。此外,在帧传输时,摄像部的各位所生成的信息电荷通过垂直移位寄存器被以一帧量垂直传输,缓存在蓄积部中,并且被缓存在蓄积部中的信息电荷按每一行量向水平传输部传输。

在固体摄像装置中,为了提高摄像时的信息电荷的蓄积能力和垂直传输时的信息电荷的传输效率,需要以摄像时和垂直传输时不同电压值的时钟脉冲施加给摄像部以及蓄积部的三值时钟脉冲进行控制。

发明内容

因此,本发明的目的在于,提供一种抑制开关元件的贯通电流,降低消耗电力的三值脉冲发生电路。

本发明涉及一种输出互相不同的三个电压值的三值脉冲发生电路,其特征在于,具备:包括三个逻辑元件的逻辑电路部;和包括由所述三个逻辑元件的各个输出而控制的三个开关元件的开关控制部,在所述三个开关元件的各自一端,分别输入互相不同的三个电压值,从另一端输出电压值,所述开关控制部通过按照使所述三个开关元件不同时处于导通状态的方式进行控制,切换所述三个电压值并输出,将所述三个逻辑元件中的一个输出反馈到其他两个逻辑元件中至少一个的输入,可进行控制以使所述三个开关元件不同时处于导通状态。

具体而言,优选所述逻辑电路部构成为包括OR元件和第一AND元件以及第二AND元件,所述OR元件的输出被反馈到所述第一AND元件以及所述第二AND元件的输入,所述第一AND元件的输出以及所述第二AND元件的输出被反馈到所述OR元件的输入。

此外,优选所述逻辑电路部构成为包括OR元件、第一AND元件和第二AND元件及多谐振荡器电路,所述OR元件的输出被反馈到所述第一AND元件以及所述第二AND元件的输入,所述第一AND元件的输出以及所述第二AND元件的输出被反馈到所述OR元件的输入,并且经由所述多谐振荡器电路被反馈到所述第一AND元件以及所述第二AND元件的输入。

这些逻辑电路,能够适用于采用两个N沟道MOSFET和一个P沟道MOSFET作为所述三个开关元件而构成的所述开关控制部。

此外,优选所述逻辑电路部构成为包括第一OR元件、第二OR元件和AND元件以及多谐振荡器电路,所述AND元件的输出被反馈到所述第一OR元件以及所述第二OR元件的输入,所述第一OR元件的输出以及所述第二OR元件的输出被反馈到所述AND元件的输入,并且经由所述多谐振荡器电路被反馈到所述第一OR元件以及所述第二OR元件的输入。

这些逻辑电路,能够适用于采用一个N沟道MOSFET和两个P沟道MOSFET作为所述三个开关元件而构成的所述开关控制部。

通过本发明,能够抑制三值脉冲发生电路中的开关元件的贯通电流,降低消耗电力。

附图说明

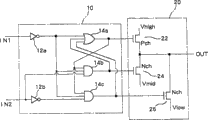

图1是表示本发明第一实施方式所涉及的三值脉冲发生电路的结构的电路图。

图2是表示本发明第一实施方式所涉及的三值脉冲发生电路的作用的时序图。

图3是表示本发明第二实施方式所涉及的三值脉冲发生电路的结构的电路图。

图4是表示本发明第二实施方式所涉及的三值脉冲发生电路的作用的时序图。

图5是表示本发明第三实施方式所涉及的三值脉冲发生电路的结构的电路图。

图6是表示本发明第三实施方式所涉及的三值脉冲发生电路的作用的时序图。

图中:10、30、50—逻辑电路部;12a、12b、32a、32b、52a、52b—NOT元件;14a、36a、56a、56b—OR元件;14b、14c、36b、36c、56c—AND元件;20、40、60—开关控制部;22、42、62、64—P沟道MOSFET;24、26、44、46、66—N沟道MOSFET;34a、34b—NOR元件;54a、54b—NAND元件;100、200、300—三值脉冲发生电路。

具体实施方式

(第一实施方式)

本发明的第一实施方式的三值脉冲发生电路100如图1所示,包括逻辑电路部10以及开关控制部20。逻辑电路部10包括逻辑元件,生成控制开关元件的开关的控制信号并输出。开关控制部20包括多个开关元件,按照由逻辑电路部10生成的控制信号选择规定三个电压值Vhigh、Vmid、Vlow中的一个,作为输出信号OUT输出。三值脉冲发生电路100,例如用作帧传输方式的CCD固体摄像装置中的摄像部的驱动用驱动器,但并不限定于此,也可用作其他装置的驱动用驱动器。

逻辑电路部10能够包括:兼作缓冲器的NOT元件12a和12b、OR元件14a、AND元件14b和14c而构成。本实施方式的OR元件14a、AND元件14b和14c分别具有三个输入端子。此外,开关控制部20包括P沟道MOSFET22、N沟道MOSFET24、26。

对NOT元件12a输入第一输入信号IN1,对NOT元件12b输入第二输入信号IN2。第二输入信号IN2还被输入到AND元件14b中。NOT元件12a的输出被输入到OR元件14a及AND元件14b、14c。此外,NOT元件12b的输出被输入到AND元件14c。

OR元件14a的输出被输入到开关控制部20的MOSFET22的栅极,并且被输入到AND元件14b、14c。AND元件14b的输出被输入到开关控制部20的MOSFET24的栅极,并且被输入到OR元件14a。AND元件14c的输出被输入到开关控制部20的MOSFET26的栅极,并且被输入到OR元件14a。

向开关控制部20的MOSFET22的源极施加第一电压Vhigh,对MOSFET24的源极施加比第一电压Vhigh低的第二电压Vmid,对MOSFET26的源极施加比第二电压Vmid低的第三电压Vlow。例如第一电压Vhigh为3V,第二电压Vmid为—5V,第三电压Vlow为—7V。MOSFET22、24、26的漏极与输出端子公共连接。

接下来,参照图2,对三值脉冲发生电路100的作用进行说明。图2是表示输出信号OUT相对第一输入信号IN1以及第二输入信号IN2的状态的变化的时序图。

当第一输入信号IN1为低电平,第二输入信号IN2也为低电平时,只有MOSFET26为导通状态,MOSFET22、24为截止状态。因此,输出信号OUT成为第三电压值Vlow。当第一输入信号IN1为高电平,第二输入信号IN2为低电平的情况下,只有MOSFET22为导通状态,MOSFET24、26为截止状态。此外,在第一输入信号IN1以及第二输入信号IN2均为高电平的情况下,只有MOSFET22为导通状态,MOSFET24、26为截止状态。因此,输入信号OUT成为第一电压值Vhigh。在第一输入信号IN1为低电平,第二输入信号IN2为高电平的情况下,只有MOSFET24为导通状态,MOSFET22、26为截止状态。因此,输出信号OUT成为第二电压值Vmid。

此时,如图2所示,在第一输入信号IN1为高电平的期间中使第二输入信号IN2从低电平变化为高电平。由此,在第一电压值Vhigh和第二电压值Vmid之间或者第一电压值Vhigh和第三电压值Vlow之间切换输出信号Vout,能够产生三值脉冲。

在逻辑电路电路部10中,OR元件14a的输出被反馈到AND元件14b、14c的输入中,并且AND元件14b、14c的输出被反馈到OR元件14a的输入。这样,通过对作为开关元件的三个MOSFET22、24、26输出控制信号的三个逻辑元件、即OR元件14a、AND元件14b、14c的输出互相进行反馈,能够按照只使开关控制部20中所包括的开关元件、即MOSFET22、24、26的任意一个处于导通状态的方式进行控制。能够防止因MOSFET22、24同时处于导通状态而导致MOSFET22的源极和MOSFET24的源极处于被连接的状态,因MOSFET22、26同时处于导通状态而导致MOSFET22的源极和MOSFET26的源极处于被连接的状态,因MOSFET24、26同时处于导通状态而导致MOSFET24的源极和MOSFET26的源极处于被连接的状态。即,能够防止多个开关元件同时处于导通状态而产生的贯通电流的发生,由此可以降低三值脉冲发生电路100的消耗电力。

(第二实施方式)

本发明第二实施方式的三值脉冲发生电路200,如图3所示,包括逻辑电路部30以及开关控制部40。逻辑电路部30与第一实施方式同样包括逻辑元件,生成控制开关元件的开关的控制信号并输出。开关控制部40,与第一实施方式相同包括多个开关元件,按照由逻辑电路部30所生成的控制信号选择规定的三个电压值Vhigh、Vmid、Vlow中的一个,作为输出信号OUT输出。三值脉冲发生电路200,例如用作帧传输方式的CCD固体摄像装置的摄像部的驱动用驱动器,但并不限于此,也可用作其他装置的驱动用驱动器。

逻辑电路部30,可以包括兼作缓冲器的NOT元件32a和32b、构成多谐振荡器的NOR元件34a和34b、OR元件36a以及AND元件36b和36c而构成。本实施方式的OR元件36a、AND元件36b、36c分别具有三个输入端子。此外,开关控制部40构成为包括P沟道MOSFET42、N沟道MOSFET44、46。

对NOT元件32a输入第一输入信号IN1,对NOT元件32b输入第二输入信号IN2。第二输入信号IN2还被输入到NOR元件34b中。NOT元件32a的输出被输入到OR元件36a及AND元件36b、36c。NOT元件32b的输出被输入到NOR元件34a。此外,NOR元件34a的输出被输入到AND元件36b,NOR元件34b的输出被输入到AND元件36c。

OR元件36a的输出A被输入到开关控制部40的MOSFET42的栅极,并且被输入到AND元件36b、36c。AND元件36b的输出B被输入到开关控制部40的MOSFET44的栅极,并且被输入到OR元件36a以及构成多谐振荡器电路的NOR元件34b。AND元件36c的输出C被输入到开关控制部40的MOSFET46的栅极,并且被输入到OR元件36a以及构成多谐振荡器电路的NOR元件34a。

开关控制部40与第一实施方式的开关控制部20相同,由一个P沟道MOSFET42以及两个N沟道MOSFET44构成。开关控制部40的MOSFET42的源极被施加第一电压Vhigh,在MOSFET44的源极施加比第一电压Vhigh低的第二电压Vmid,在MOSFET46的源极施加比第二电压Vmid低的第三电压Vlow。例如第一电压Vhigh为3V,第二电压Vmid为—5V,第三电压Vlow为—7V。MOSFET42、44、46的漏极与输出端子公共连接。

接下来,参照图4,对三值脉冲发生电路200的作用进行说明。图4是表示输出A、B、C以及输出信号OUT相对第一输入信号IN1以及第二输入信号IN2的状态的变化的时序图。

当第一输入信号IN1为低电平,第二输入信号IN2也为低电平时,输出A以及输出C为高电平,输出B为低电平。由此,只有MOSFET46为导通状态,MOSFET42、44为截止状态。因此,输出信号OUT成为第三电压值Vlow。

接着,如果第二输入信号IN2仍保持低电平,第一输入信号IN1变为高电平,则首先AND元件36c的输出C变化为低电平(步骤S1)。接着,受到AND元件36c的变化,构成多谐振荡器电路的NOR元件34a的输出变为高电平,NOR元件34b的输出变为低电平(步骤S2)。由此,AND元件36c的输出C的变换延迟,OR元件36a的输出A变为低电平。即,在MOSFET46变为截止状态后,只有MOSFET42变为导通状态。因此,输出信号OUT从第三电压值Vlow切换为第一电压值Vhigh。

如果第二输入信号IN2仍保持低电平,第一输入信号IN1变为低电平,则稍微延迟后OR元件36a的输出A再次返回到高电平(步骤S3),延迟一段时间后AND元件36c的输出C变为高电平(步骤S4)。由此,输出信号OUT再次变为第三电压值Vlow。

在第一输入信号IN1仍保持高电平,第二输入信号IN2变为高电平的情况下,只有MOSFET22为导通状态,MOSFET24、26为截止状态。因此,输出信号OUT成为第一电压值Vhigh。

接下来,当第二输入信号IN2仍保持高电平,第一输入信号IN1变为低电平时,首先OR元件36a的输出A变化为高电平(步骤S5)。接着,受到OR元件36a的输出A的变化,AND元件36b的输出B变为高电平。即,在MOSFET42变为截止状态后,只有MOSFET44变为导通状态。因此,输出信号OUT从第一电压值Vhigh切换为第二电压值Vmid。

如果第二输入信号IN2仍保持高电平,第一输入信号IN1返回到高电平,则稍微延迟后AND元件36b的输出B再次返回到低电平(步骤S7),延迟一段时间后OR元件36a的输出A变为低电平(步骤S8)。由此,输出信号OUT再次变为第一电压值Vhigh。

如上所述,可以一边进行控制以使开关控制部40的开关元件同时只有一个处于导通状态,一边在第一电压值Vhigh和第二电压值Vmid之间或者第一电压值Vhigh和第三电压值Vlow之间切换输出信号OUT。此外,在本实施方式的三值脉冲发生电路200中,也可以一边进行控制以使开关控制部40的开关元件同时只有一个处于导通状态,一边在第二电压值Vmid和第三电压值Vlow之间进行切换。

在逻辑电路部30中,OR元件36a的输出被反馈到AND元件36b、36c的输入,并且AND元件36b、36c的输出经由多谐振荡器电路分别反馈到AND元件36c、36b的输入。这样,通过互相反馈OR元件36a、AND元件36b、36c的输出,能够进行控制以使只有开关控制部40中包括的开关元件、即MOSFET42、44、46的任意一个变为导通状态,该OR元件36a、AND元件36b、36c是对作为开关元件的三个MOSFET42、44、46输出控制信号的三个逻辑元件。能够防止因MOSFET42、44同时处于导通状态而使得MOSFET42的源极和MOSFET44的源极处于被连接的状态,因MOSFET42、46同时处于导通状态而使得MOSFET42的源极和MOSFET46的源极处于被连接的状态,因MOSFET44、46同时处于导通状态而使得MOSFET44的源极和MOSFET46的源极处于被连接的状态。即,能够防止多个开关元件同时处于导通状态而发生的贯通电流的产生,由此可以降低三值脉冲发生电路200的消耗电力。

(第三实施方式)

本发明第三实施方式的三值脉冲发生电路300如图5所示,包括逻辑电路部50以及开关控制部60。逻辑电路部50与第一实施方式同样包括逻辑元件,生成控制开关元件的开关的控制信号并输出。开关控制部60与第一实施方式同样包括多个开关元件,按照由逻辑电路部50所生成的控制信号选择规定的三个电压值Vhigh、Vmid、Vlow中的一个,作为输出信号OUT输出。三值脉冲发生电路300,例如用作帧传输方式的CCD固体摄像装置中的摄像部的驱动用驱动器,但并不限定于此,也可用作其他装置的驱动用驱动器。

逻辑电路部50,可以包括兼作缓冲器的NOT元件52a和52b、构成多谐振荡器的NAND元件54a和54b、OR元件56a和56b以及AND元件56c而构成。本实施方式的OR元件56a和56b、AND元件56c分别具有三个输入端子。此外,开关控制部60构成为包括P沟道MOSFET62、64、N沟道MOSFET66。

对NOT元件52a输入第一输入信号IN1,对NOT元件52b输入第二输入信号IN2。第二输入信号IN2还被输入到NAND元件54a中。NOT元件52a的输出被输入到OR元件56a、56b及AND元件56c。NOT元件52b的输出被输入到NAND元件54b。此外,NAND元件54a的输出被输入到OR元件56a,NAND元件54b的输出被输入到OR元件56b。

OR元件56a的输出A被输入到开关控制部60的MOSFET62的栅极,并且被输入到AND元件56c以及构成多谐振荡器电路的NAND元件54b。OR元件56b的输出B被输入到开关控制部60的MOSFET64的栅极,并且被输入到AND元件56c以及构成多谐振荡器电路的NAND元件54a。AND元件56c的输出C被输入到开关控制部60的MOSFET66的栅极,并且被输入到OR元件56a、56b。

开关控制部60的MOSFET62的源极被施加第一电压Vhigh,对MOSFET64的源极施加比第一电压Vhigh低的第二电压Vmid,对MOSFET66的源极施加比第二电压Vmid低的第三电压Vlow。例如第一电压Vhigh为1V,第二电压Vmid为—3V,第三电压Vlow为—7V。MOSFET62、64、66的漏极与输出端子公共连接。

接下来,参照图6,对三值脉冲发生电路300的作用进行说明。图6是表示输出A、B、C以及输出信号OUT相对第一输入信号IN1以及第二输入信号IN2的状态的变化的时序图。

当第一输入信号IN1为低电平,第二输入信号IN2也为低电平时,输出A、输出B以及输出C全部为高电平。由此,只有MOSFET66为导通状态,MOSFET62、64为截止状态。因此,输出信号OUT成为第三电压值Vlow。

接下来,如果第二输入信号IN2仍保持低电平,第一输入信号IN1变为高电平,则首先AND元件56c的输出C变化为低电平(步骤S10)。接着,受到AND元件56c的变化,OR元件56b的输出变为低电平(步骤S11)。即,在MOSFET66变为截止状态后,只有MOSFET64变为导通状态。因此,输出信号OUT从第三电压值Vlow切换为第二电压值Vmid。

如果第二输入信号IN2仍保持低电平,第一输入信号IN1返回到低电平,则稍微延迟后OR元件56b的输出B再次返回到高电平(步骤S12),延迟一段时间后AND元件56c的输出C变为高电平(步骤S13)。由此,输出信号OUT再次变为第三电压值Vlow。

在第一输入信号IN1仍保持低电平,第二输入信号IN2变为高电平的情况下,输出A、输出B以及输出C全部维持高电平的状态。因此,只有MOSFET66处于导通状态,输出信号OUT维持第三电压值Vlow。

接着,如果第二输入信号IN2仍保持高电平,第一输入信号IN1变为高电平,则首先AND元件56c的输出C变化为低电平(步骤S14)。接着,受到AND元件56c的输出C的变化,AND元件56a的输出A变为低电平(步骤S15)。即,在MOSFET66变为截止状态后,只有MOSFET62变为导通状态。因此,输出信号OUT从第三电压值Vlow切换为第一电压值Vhigh。

如果第二输入信号IN2仍保持高电平,第一输入信号IN1返回到低电平,则稍微延迟后OR元件56a的输出A再次返回到高电平(步骤S16),延迟一段时间后AND元件56c的输出C变为高电平(步骤S17)。由此,输出信号OUT再次变为第三电压值Vlow。

接下来,如果第一输入信号IN1仍保持高电平,第二输入信号IN2从低电平变为高电平,则首先OR元件56b的输出B变化为高电平(步骤S18)。接下来,受到OR元件56b的输出B的变化,OR元件56a的输出A变为低电平(步骤S19)。即,在MOSFET64处于截止状态后,只有MOSFET62处于导通状态。因此,输出信号OUT从第二电压值Vmid切换为第一电压值Vhigh。

如果第一输入信号IN1仍保持高电平,第二输入信号IN2返回到低电平,则稍微延迟后OR元件56a的输出A再次返回到高电平(步骤S20),延迟一段时间后OR元件56b的输出B成为低电平(步骤S21)。由此,输出信号OUT再次变为第二电压值Vmid。

如上所述,可以一边进行控制以使开关控制部60的开关元件同时只有一个处于导通状态,一边在第一电压值Vhigh和第二电压值Vmid之间或者第一电压值Vhigh和第三电压值Vlow之间、或者第二电压值Vmid与第三电压值Vlow之间切换输出信号OUT。

在逻辑电路部50中,AND元件56c的输出被反馈到OR元件56a、56b的输入,并且OR元件56a、56b的输出经由多谐振荡器电路分别反馈到OR元件56b、56c的输入。这样,通过互相反馈OR元件56a和56b、AND元件56c的输出,能够进行控制以使只有开关控制部60中包括的开关元件、即MOSFET62、64、66的任意一个变为导通状态,该OR元件56a和56b、AND元件56c是对作为开关元件的三个MOSFET元件62、64、66输出控制信号的三个逻辑元件。能够防止因MOSFET62、64同时处于导通状态而使得MOSFET62的源极和MOSFET64的源极处于被连接的状态,因MOSFET62、66同时处于导通状态而使得MOSFET62的源极和MOSFET66的源极处于被连接的状态,因MOSFET64、66同时处于导通状态而使得MOSFET64的源极和MOSFET66的源极处于被连接的状态。即,能够防止多个开关元件同时处于导通状态所发生的贯通电流的产生,由此可以降低三值脉冲发生电路300的消耗电力。

此外,三值脉冲发生电路300在(Vhigh—Vmid)<(Vmid—Vlow)的情况下,通过采用P沟道MOSFET64,能够避免反向栅偏置效应所引起的驱动能力的降低。因此,在(Vhigh—Vmid)<(Vmid—Vlow)的情况下,优选采用三值脉冲发生电路300。另一方面,在(Vhigh—Vmid)>(Vmid—Vlow)的情况下,优选采用三值脉冲发生电路200。

此外,在第一到第三实施方式的三值脉冲发生电路100、200、300中,通过提高逻辑电路部10、30、50的驱动电压,也能够提高后级的开关控制部20、40、60的驱动能力。

另外,本发明的技术思想并不限于上述实施方式,也可采用与逻辑电路10、30、50不同的逻辑电路来控制开关控制部。其中,通过采用上述实施方式的逻辑电路10、30、50,能够使电路比其他逻辑电路简易且小型,能够抑制制造成本。

Claims (4)

1、一种三值脉冲发生电路,输出互相不同的三个电压值,其特征在于,

具备:包括三个逻辑元件的逻辑电路部;和包括由所述三个逻辑元件的各个输出而控制的三个开关元件的开关控制部,

在所述三个开关元件的各自一端分别输入互相不同的三个电压值,从另一端输出电压值,

所述逻辑电路部以如下方式进行控制:按照使所述三个开关元件不同时处于导通状态的方式切换所述三个电压值并输出,

将所述三个逻辑元件中的一个输出反馈到其他两个逻辑元件中至少一个的输入。

2、根据权利要求1所述的三值脉冲发生电路,其特征在于,

所述逻辑电路部构成为包括OR元件和第一AND元件以及第二AND元件,

所述OR元件的输出被反馈到所述第一AND元件以及所述第二AND元件的输入,

所述第一AND元件的输出以及所述第二AND元件的输出被反馈到所述OR元件的输入。

3、根据权利要求1所述的三值脉冲发生电路,其特征在于,

所述逻辑电路部构成为包括OR元件、第一AND元件和第二AND元件及多谐振荡器电路,

所述OR元件的输出被反馈到所述第一AND元件以及所述第二AND元件的输入,

所述第一AND元件的输出以及所述第二AND元件的输出被反馈到所述OR元件的输入,并且经由所述多谐振荡器电路被反馈到所述第一AND元件以及所述第二AND元件的输入。

4、根据权利要求1所述的三值脉冲发生电路,其特征在于,

所述逻辑电路部构成为包括第一OR元件、第二OR元件和AND元件以及多谐振荡器电路,

所述AND元件的输出被反馈到所述第一OR元件以及所述第二OR元件的输入,

所述第一OR元件的输出以及所述第二OR元件的输出被反馈到所述AND元件的输入,并且经由所述多谐振荡器电路被反馈到所述第一OR元件以及所述第二OR元件的输入。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005310899A JP2007124084A (ja) | 2005-10-26 | 2005-10-26 | 3値パルス発生回路 |

| JP2005310899 | 2005-10-26 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1956489A CN1956489A (zh) | 2007-05-02 |

| CN100512370C true CN100512370C (zh) | 2009-07-08 |

Family

ID=37985386

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2006101420617A Expired - Fee Related CN100512370C (zh) | 2005-10-26 | 2006-10-08 | 三值脉冲发生电路 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US7521979B2 (zh) |

| JP (1) | JP2007124084A (zh) |

| KR (1) | KR100787326B1 (zh) |

| CN (1) | CN100512370C (zh) |

| TW (1) | TW200721676A (zh) |

Families Citing this family (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7672393B2 (en) * | 2006-08-02 | 2010-03-02 | Richtek Technology Corporation | Single-wire asynchronous serial interface |

| CN101834595B (zh) * | 2010-05-04 | 2012-10-24 | 宁波大学 | 一种单功率时钟钟控传输门三值绝热电路及t运算电路 |

| JP6545213B2 (ja) * | 2017-03-17 | 2019-07-17 | アンリツ株式会社 | 3値信号発生装置及び3値信号発生方法 |

Family Cites Families (26)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS58223916A (ja) | 1982-06-23 | 1983-12-26 | Nec Corp | 3値レベルクロツク発生回路 |

| JPS5985153A (ja) * | 1982-11-08 | 1984-05-17 | Hitachi Ltd | 冗長化制御装置 |

| JPH02125526A (ja) * | 1988-11-04 | 1990-05-14 | Nec Corp | 三値論理出力回路 |

| JP2789792B2 (ja) * | 1990-06-25 | 1998-08-20 | 日本電気株式会社 | パルス出力回路 |

| JPH06232702A (ja) * | 1991-05-10 | 1994-08-19 | Nec Corp | 3値レベルパルス発生回路 |

| FR2709217B1 (fr) * | 1993-08-19 | 1995-09-15 | Bull Sa | Procédé et dispositif d'adaptation d'impédance pour un émetteur et/ou récepteur, circuit intégré et système de transmission les mettant en Óoeuvre. |

| JPH0779155A (ja) * | 1993-09-06 | 1995-03-20 | Mitsubishi Electric Corp | 信号選択装置 |

| US5528168A (en) * | 1995-03-29 | 1996-06-18 | Intel Corporation | Power saving terminated bus |

| JPH09205351A (ja) * | 1996-01-25 | 1997-08-05 | Sony Corp | レベルシフト回路 |

| US5731711A (en) * | 1996-06-26 | 1998-03-24 | Lucent Technologies Inc. | Integrated circuit chip with adaptive input-output port |

| KR100207497B1 (ko) * | 1996-08-30 | 1999-07-15 | 윤종용 | 반도체장치의 신호 발생회로 |

| JP3867330B2 (ja) | 1997-01-08 | 2007-01-10 | ソニー株式会社 | 固体撮像装置とその製造方法 |

| US5710563A (en) * | 1997-01-09 | 1998-01-20 | National Semiconductor Corporation | Pipeline analog to digital converter architecture with reduced mismatch error |

| US6173424B1 (en) * | 1997-12-31 | 2001-01-09 | Micron Technology, Inc. | Programmable pulse generator and method for using same |

| JP3595153B2 (ja) * | 1998-03-03 | 2004-12-02 | 株式会社 日立ディスプレイズ | 液晶表示装置および映像信号線駆動手段 |

| US6166670A (en) * | 1998-11-09 | 2000-12-26 | O'shaughnessy; Timothy G. | Self calibrating current mirror and digital to analog converter |

| US6288563B1 (en) * | 1998-12-31 | 2001-09-11 | Intel Corporation | Slew rate control |

| US6204683B1 (en) * | 1999-05-18 | 2001-03-20 | Intel Corporation | Apparatus and method for reducing crosstalk in an integrated circuit which includes a signal bus |

| JP2001119009A (ja) | 1999-10-15 | 2001-04-27 | Fuji Film Microdevices Co Ltd | 固体撮像装置 |

| JP3600103B2 (ja) * | 2000-02-04 | 2004-12-08 | 三洋電機株式会社 | バッファ回路及びバッファ回路を備えるドライバ |

| US6366069B1 (en) * | 2001-02-01 | 2002-04-02 | Intel Corporation | Hysteretic-mode multi-phase switching regulator |

| JP2003169261A (ja) * | 2001-11-29 | 2003-06-13 | Fuji Film Microdevices Co Ltd | 駆動用集積回路 |

| US6747475B2 (en) * | 2001-12-17 | 2004-06-08 | Intel Corporation | Method and apparatus for driving a signal using switchable on-die termination |

| KR100486260B1 (ko) * | 2002-09-11 | 2005-05-03 | 삼성전자주식회사 | 동기식 디램의 고주파수 동작을 위한 비트라인 센스앰프구동 제어회로 및 그 구동 제어방법 |

| JP4155123B2 (ja) * | 2003-06-27 | 2008-09-24 | セイコーエプソン株式会社 | 半導体装置、これを用いた撮像装置および表示装置 |

| KR100610020B1 (ko) * | 2005-01-13 | 2006-08-08 | 삼성전자주식회사 | 반도체 메모리 장치에서의 셀 파워 스위칭 회로와 그에따른 셀 파워 전압 인가방법 |

-

2005

- 2005-10-26 JP JP2005310899A patent/JP2007124084A/ja active Pending

-

2006

- 2006-10-08 CN CNB2006101420617A patent/CN100512370C/zh not_active Expired - Fee Related

- 2006-10-19 US US11/583,250 patent/US7521979B2/en active Active

- 2006-10-24 TW TW095139107A patent/TW200721676A/zh not_active IP Right Cessation

- 2006-10-25 KR KR1020060103913A patent/KR100787326B1/ko active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| TWI329419B (zh) | 2010-08-21 |

| JP2007124084A (ja) | 2007-05-17 |

| US20070092026A1 (en) | 2007-04-26 |

| KR100787326B1 (ko) | 2007-12-21 |

| CN1956489A (zh) | 2007-05-02 |

| KR20070045113A (ko) | 2007-05-02 |

| US7521979B2 (en) | 2009-04-21 |

| TW200721676A (en) | 2007-06-01 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JPWO2008018363A1 (ja) | イメージセンサ駆動装置 | |

| US8847938B2 (en) | Imaging device, method for controlling the imaging device, and camera using the imaging device | |

| JPWO2006070524A1 (ja) | 電源回路、チャージポンプ回路、及び、これを備えた携帯機器 | |

| CN101465643B (zh) | 电平移位电路及使用该电路的驱动器和显示装置 | |

| CN100512370C (zh) | 三值脉冲发生电路 | |

| TWI531234B (zh) | 用於互補金氧半導體影像感測器之可變電壓列驅動器 | |

| KR100769450B1 (ko) | 드라이버 회로 | |

| JP2009284015A (ja) | 固体撮像装置および固体撮像装置の駆動方法 | |

| US20130321684A1 (en) | Image pickup device, image pickup system, and method of driving image pickup device | |

| JP4901252B2 (ja) | 負昇圧チャージポンプ回路、lcdドライバic、液晶表示装置 | |

| US8531569B2 (en) | CCD-type solid-state imaging device, driving method for CCD-type solid-state imaging device, and imaging system | |

| JP4696788B2 (ja) | 固体撮像装置 | |

| JP2006262070A (ja) | 光電変換装置及びcmosイメージセンサ | |

| US7053950B2 (en) | Drive unit for transferring CCD charge | |

| EP1465409B1 (en) | Image sensor, driving method and camera | |

| US11749159B2 (en) | Gate driver circuit and method for driving the same | |

| JP4102098B2 (ja) | 固体撮像装置 | |

| TWI822615B (zh) | 影像感測器、電壓準位轉換器電路及其操作方法 | |

| EP1353500B9 (en) | Image sensor | |

| JP4797600B2 (ja) | 固体撮像素子の出力バッファ回路およびこれを用いた固体撮像装置 | |

| JP5144177B2 (ja) | 情報処理装置 | |

| JPH10164311A (ja) | イメージセンサ | |

| TWI637597B (zh) | 輸出級電路 | |

| CN112752042A (zh) | 行驱动器及其构成的图像传感器 | |

| US8817155B2 (en) | Driving device for solid-state image pickup device capable of selecting parallel number of FETs |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090708 Termination date: 20211008 |