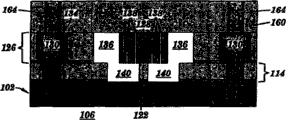

CN100423216C - 在线后端处理中形成悬空传输线结构的方法 - Google Patents

在线后端处理中形成悬空传输线结构的方法 Download PDFInfo

- Publication number

- CN100423216C CN100423216C CNB2005800134522A CN200580013452A CN100423216C CN 100423216 C CN100423216 C CN 100423216C CN B2005800134522 A CNB2005800134522 A CN B2005800134522A CN 200580013452 A CN200580013452 A CN 200580013452A CN 100423216 C CN100423216 C CN 100423216C

- Authority

- CN

- China

- Prior art keywords

- transmission line

- signal transmission

- ground plane

- dielectric layer

- sacrificial material

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01P—WAVEGUIDES; RESONATORS, LINES, OR OTHER DEVICES OF THE WAVEGUIDE TYPE

- H01P11/00—Apparatus or processes specially adapted for manufacturing waveguides or resonators, lines, or other devices of the waveguide type

- H01P11/001—Manufacturing waveguides or transmission lines of the waveguide type

- H01P11/003—Manufacturing lines with conductors on a substrate, e.g. strip lines, slot lines

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/7682—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing the dielectric comprising air gaps

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5222—Capacitive arrangements or effects of, or between wiring layers

- H01L23/5225—Shielding layers formed together with wiring layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/58—Structural electrical arrangements for semiconductor devices not otherwise provided for

- H01L2223/64—Impedance arrangements

- H01L2223/66—High-frequency adaptations

- H01L2223/6605—High-frequency electrical connections

- H01L2223/6616—Vertical connections, e.g. vias

- H01L2223/6622—Coaxial feed-throughs in active or passive substrates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2223/00—Details relating to semiconductor or other solid state devices covered by the group H01L23/00

- H01L2223/58—Structural electrical arrangements for semiconductor devices not otherwise provided for

- H01L2223/64—Impedance arrangements

- H01L2223/66—High-frequency adaptations

- H01L2223/6605—High-frequency electrical connections

- H01L2223/6627—Waveguides, e.g. microstrip line, strip line, coplanar line

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/19—Details of hybrid assemblies other than the semiconductor or other solid state devices to be connected

- H01L2924/1901—Structure

- H01L2924/1903—Structure including wave guides

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/709,357 US7005371B2 (en) | 2004-04-29 | 2004-04-29 | Method of forming suspended transmission line structures in back end of line processing |

| US10/709,357 | 2004-04-29 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1947234A CN1947234A (zh) | 2007-04-11 |

| CN100423216C true CN100423216C (zh) | 2008-10-01 |

Family

ID=35187662

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB2005800134522A Expired - Fee Related CN100423216C (zh) | 2004-04-29 | 2005-04-28 | 在线后端处理中形成悬空传输线结构的方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US7005371B2 (enExample) |

| EP (1) | EP1756862A4 (enExample) |

| JP (1) | JP4776618B2 (enExample) |

| KR (1) | KR101006286B1 (enExample) |

| CN (1) | CN100423216C (enExample) |

| TW (1) | TWI464840B (enExample) |

| WO (1) | WO2005112105A1 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102232104A (zh) * | 2009-06-15 | 2011-11-02 | 住友电木株式会社 | 用于半导体晶片的暂时粘合剂以及使用所述粘合剂制造半导体设备的方法 |

Families Citing this family (50)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3563030B2 (ja) * | 2000-12-06 | 2004-09-08 | シャープ株式会社 | 半導体装置の製造方法 |

| JP2005236107A (ja) * | 2004-02-20 | 2005-09-02 | Toshiba Corp | 上層メタル電源スタンダードセル、面積圧縮装置および回路最適化装置 |

| US7678682B2 (en) * | 2004-11-12 | 2010-03-16 | Axcelis Technologies, Inc. | Ultraviolet assisted pore sealing of porous low k dielectric films |

| FR2885735B1 (fr) * | 2005-05-10 | 2007-08-03 | St Microelectronics Sa | Circuit integre guide d'ondes |

| WO2007054867A2 (en) * | 2005-11-08 | 2007-05-18 | Nxp B.V. | Producing a covered through substrate via using a temporary cap layer |

| DE102006001253B4 (de) | 2005-12-30 | 2013-02-07 | Advanced Micro Devices, Inc. | Verfahren zur Herstellung einer Metallschicht über einem strukturierten Dielektrikum mittels einer nasschemischen Abscheidung mit einer stromlosen und einer leistungsgesteuerten Phase |

| US7755174B2 (en) | 2007-03-20 | 2010-07-13 | Nuvotonics, LLC | Integrated electronic components and methods of formation thereof |

| US7898356B2 (en) | 2007-03-20 | 2011-03-01 | Nuvotronics, Llc | Coaxial transmission line microstructures and methods of formation thereof |

| US8028406B2 (en) * | 2008-04-03 | 2011-10-04 | International Business Machines Corporation | Methods of fabricating coplanar waveguide structures |

| WO2009127914A1 (en) | 2008-04-17 | 2009-10-22 | Freescale Semiconductor, Inc. | Method of sealing an air gap in a layer of a semiconductor structure and semiconductor structure |

| US7838389B2 (en) * | 2008-05-30 | 2010-11-23 | Freescale Semiconductor, Inc. | Enclosed void cavity for low dielectric constant insulator |

| US7919388B2 (en) * | 2008-05-30 | 2011-04-05 | Freescale Semiconductor, Inc. | Methods for fabricating semiconductor devices having reduced gate-drain capacitance |

| US8138036B2 (en) * | 2008-08-08 | 2012-03-20 | International Business Machines Corporation | Through silicon via and method of fabricating same |

| US8035198B2 (en) * | 2008-08-08 | 2011-10-11 | International Business Machines Corporation | Through wafer via and method of making same |

| US8299566B2 (en) * | 2008-08-08 | 2012-10-30 | International Business Machines Corporation | Through wafer vias and method of making same |

| US8384224B2 (en) * | 2008-08-08 | 2013-02-26 | International Business Machines Corporation | Through wafer vias and method of making same |

| US8164397B2 (en) * | 2009-08-17 | 2012-04-24 | International Business Machines Corporation | Method, structure, and design structure for an impedance-optimized microstrip transmission line for multi-band and ultra-wide band applications |

| JP2011100989A (ja) * | 2009-10-09 | 2011-05-19 | Renesas Electronics Corp | 半導体装置 |

| US20110123783A1 (en) | 2009-11-23 | 2011-05-26 | David Sherrer | Multilayer build processses and devices thereof |

| US8232618B2 (en) | 2010-08-11 | 2012-07-31 | International Business Machines Corporation | Semiconductor structure having a contact-level air gap within the interlayer dielectrics above a semiconductor device and a method of forming the semiconductor structure using a self-assembly approach |

| US8530347B2 (en) | 2010-10-05 | 2013-09-10 | Freescale Semiconductor, Inc. | Electronic device including interconnects with a cavity therebetween and a process of forming the same |

| US8754338B2 (en) * | 2011-05-28 | 2014-06-17 | Banpil Photonics, Inc. | On-chip interconnects with reduced capacitance and method of afbrication |

| US8643187B1 (en) * | 2011-06-01 | 2014-02-04 | Banpil Photonics, Inc. | On-chip interconnects VIAS and method of fabrication |

| US8866300B1 (en) | 2011-06-05 | 2014-10-21 | Nuvotronics, Llc | Devices and methods for solder flow control in three-dimensional microstructures |

| KR101982887B1 (ko) | 2011-07-13 | 2019-05-27 | 누보트로닉스, 인크. | 전자 및 기계 구조체들을 제조하는 방법들 |

| US9075105B2 (en) | 2011-09-29 | 2015-07-07 | Broadcom Corporation | Passive probing of various locations in a wireless enabled integrated circuit (IC) |

| US9570420B2 (en) | 2011-09-29 | 2017-02-14 | Broadcom Corporation | Wireless communicating among vertically arranged integrated circuits (ICs) in a semiconductor package |

| US8670638B2 (en) | 2011-09-29 | 2014-03-11 | Broadcom Corporation | Signal distribution and radiation in a wireless enabled integrated circuit (IC) using a leaky waveguide |

| US8508029B2 (en) | 2011-09-29 | 2013-08-13 | Broadcom Corporation | Semiconductor package including an integrated waveguide |

| US9318785B2 (en) | 2011-09-29 | 2016-04-19 | Broadcom Corporation | Apparatus for reconfiguring an integrated waveguide |

| US9142497B2 (en) * | 2011-10-05 | 2015-09-22 | Harris Corporation | Method for making electrical structure with air dielectric and related electrical structures |

| US8664743B1 (en) * | 2012-10-31 | 2014-03-04 | Taiwan Semiconductor Manufacturing Company, Ltd. | Air-gap formation in interconnect structures |

| US9306255B1 (en) | 2013-03-15 | 2016-04-05 | Nuvotronics, Inc. | Microstructure including microstructural waveguide elements and/or IC chips that are mechanically interconnected to each other |

| US9306254B1 (en) | 2013-03-15 | 2016-04-05 | Nuvotronics, Inc. | Substrate-free mechanical interconnection of electronic sub-systems using a spring configuration |

| US9564355B2 (en) * | 2013-12-09 | 2017-02-07 | Taiwan Semiconductor Manufacturing Company, Ltd. | Interconnect structure for semiconductor devices |

| JP6535347B2 (ja) | 2014-01-17 | 2019-06-26 | ヌボトロニクス、インク. | ウエハースケールのテスト・インターフェース・ユニット:高速および高密度の混合信号インターコネクトおよびコンタクタのための低損失および高絶縁性の装置および方法 |

| US9385068B2 (en) * | 2014-03-05 | 2016-07-05 | Northrop Grumman Systems Corporation | Stacked interconnect structure and method of making the same |

| KR102190654B1 (ko) * | 2014-04-07 | 2020-12-15 | 삼성전자주식회사 | 반도체 장치 및 이의 제조 방법 |

| US9123738B1 (en) * | 2014-05-16 | 2015-09-01 | Xilinx, Inc. | Transmission line via structure |

| US10847469B2 (en) | 2016-04-26 | 2020-11-24 | Cubic Corporation | CTE compensation for wafer-level and chip-scale packages and assemblies |

| WO2016094129A1 (en) | 2014-12-03 | 2016-06-16 | Nuvotronics, Inc. | Systems and methods for manufacturing stacked circuits and transmission lines |

| DE102014117977A1 (de) * | 2014-12-05 | 2016-06-09 | GAT Gesellschaft für Antriebstechnik mbH | Streifenleiter für berührungslose Datenübertragung mit hohen Datenraten |

| US10256141B2 (en) * | 2015-09-23 | 2019-04-09 | Intel Corporation | Maskless air gap to prevent via punch through |

| US9449871B1 (en) | 2015-11-18 | 2016-09-20 | International Business Machines Corporation | Hybrid airgap structure with oxide liner |

| US10622309B2 (en) * | 2017-10-30 | 2020-04-14 | Qorvo Us, Inc. | Transmission line structure with high Q factor and low insertion loss for millimeter wave applications |

| US10319654B1 (en) | 2017-12-01 | 2019-06-11 | Cubic Corporation | Integrated chip scale packages |

| US10534888B2 (en) | 2018-01-03 | 2020-01-14 | International Business Machines Corporation | Hybrid back end of line metallization to balance performance and reliability |

| US11380622B2 (en) * | 2020-11-20 | 2022-07-05 | Globalfoundries U.S. Inc. | Method and related structure to authenticate integrated circuit with authentication film |

| JP2022144836A (ja) * | 2021-03-19 | 2022-10-03 | 株式会社東芝 | アイソレータ |

| CN117558707B (zh) * | 2023-11-01 | 2025-02-25 | 广芯微电子(广州)股份有限公司 | 一种防串扰的三维金属隔离布线结构及布线方法 |

Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1248064A (zh) * | 1998-09-14 | 2000-03-22 | 世大积体电路股份有限公司 | 形成相邻于信号线的屏蔽线的方法 |

| US6495445B2 (en) * | 1999-07-02 | 2002-12-17 | International Business Machines Corporation | Semi-sacrificial diamond for air dielectric formation |

| US6555467B2 (en) * | 2001-09-28 | 2003-04-29 | Sharp Laboratories Of America, Inc. | Method of making air gaps copper interconnect |

| US6597068B2 (en) * | 2000-05-09 | 2003-07-22 | International Business Machines Corporation | Encapsulated metal structures for semiconductor devices and MIM capacitors including the same |

| US6635506B2 (en) * | 2001-11-07 | 2003-10-21 | International Business Machines Corporation | Method of fabricating micro-electromechanical switches on CMOS compatible substrates |

Family Cites Families (23)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5619061A (en) | 1993-07-27 | 1997-04-08 | Texas Instruments Incorporated | Micromechanical microwave switching |

| EP0915513A1 (en) * | 1997-10-23 | 1999-05-12 | STMicroelectronics S.r.l. | High quality factor, integrated inductor and production method thereof |

| JPH11204637A (ja) * | 1998-01-07 | 1999-07-30 | Toshiba Corp | 半導体装置およびその製造方法 |

| US6175727B1 (en) * | 1998-01-09 | 2001-01-16 | Texas Instruments Israel Ltd. | Suspended printed inductor and LC-type filter constructed therefrom |

| DE69922722T2 (de) * | 1998-03-05 | 2005-12-15 | Nippon Telegraph And Telephone Corp. | Oberflächenform-Erkennungssensor und dessen Herstellungsverfahren |

| JP3318865B2 (ja) * | 1998-03-05 | 2002-08-26 | 日本電信電話株式会社 | 表面形状認識用センサおよびその製造方法 |

| US6025261A (en) * | 1998-04-29 | 2000-02-15 | Micron Technology, Inc. | Method for making high-Q inductive elements |

| KR100308871B1 (ko) * | 1998-12-28 | 2001-11-03 | 윤덕용 | 동축 구조의 신호선 및 그의 제조 방법 |

| SE516743C2 (sv) * | 1999-06-29 | 2002-02-26 | Ericsson Telefon Ab L M | Microbandledarkrets för förlustreducering |

| US6258688B1 (en) * | 2000-03-15 | 2001-07-10 | Taiwan Semiconductor Manufacturing Company | Method to form a high Q inductor |

| SG98398A1 (en) * | 2000-05-25 | 2003-09-19 | Inst Of Microelectronics | Integrated circuit inductor |

| JP3877132B2 (ja) * | 2000-11-20 | 2007-02-07 | 富士通株式会社 | 多層配線基板及び半導体装置 |

| US6534843B2 (en) * | 2001-02-10 | 2003-03-18 | International Business Machines Corporation | High Q inductor with faraday shield and dielectric well buried in substrate |

| US6635306B2 (en) | 2001-06-22 | 2003-10-21 | University Of Cincinnati | Light emissive display with a black or color dielectric layer |

| WO2003049514A2 (en) * | 2001-12-03 | 2003-06-12 | Memgen Corporation | Miniature rf and microwave components and methods for fabricating such components |

| US6943447B2 (en) * | 2002-01-10 | 2005-09-13 | Fujitsu Limited | Thin film multi-layer wiring substrate having a coaxial wiring structure in at least one layer |

| JP3903249B2 (ja) * | 2002-02-20 | 2007-04-11 | 富士通株式会社 | 半導体集積回路装置 |

| US6747340B2 (en) | 2002-03-15 | 2004-06-08 | Memx, Inc. | Multi-level shielded multi-conductor interconnect bus for MEMS |

| US6903001B2 (en) * | 2002-07-18 | 2005-06-07 | Micron Technology Inc. | Techniques to create low K ILD for BEOL |

| KR100525343B1 (ko) * | 2002-08-12 | 2005-11-02 | 학교법인 한국정보통신학원 | 3차원 초고주파 다층회로를 위한 공기 공동 제작방법 |

| JP2004128179A (ja) * | 2002-10-02 | 2004-04-22 | Hitachi Cable Ltd | 配線板及び電子装置、ならびに配線板の製造方法 |

| US7012489B2 (en) * | 2003-03-04 | 2006-03-14 | Rohm And Haas Electronic Materials Llc | Coaxial waveguide microstructures and methods of formation thereof |

| US6913946B2 (en) * | 2003-06-13 | 2005-07-05 | Aptos Corporation | Method of making an ultimate low dielectric device |

-

2004

- 2004-04-29 US US10/709,357 patent/US7005371B2/en not_active Expired - Fee Related

-

2005

- 2005-04-08 TW TW094111141A patent/TWI464840B/zh not_active IP Right Cessation

- 2005-04-28 CN CNB2005800134522A patent/CN100423216C/zh not_active Expired - Fee Related

- 2005-04-28 JP JP2007510982A patent/JP4776618B2/ja not_active Expired - Fee Related

- 2005-04-28 WO PCT/US2005/014645 patent/WO2005112105A1/en not_active Ceased

- 2005-04-28 EP EP05741890A patent/EP1756862A4/en not_active Withdrawn

- 2005-04-28 KR KR1020067020388A patent/KR101006286B1/ko not_active Expired - Fee Related

- 2005-12-05 US US11/164,765 patent/US7608909B2/en not_active Expired - Lifetime

Patent Citations (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN1248064A (zh) * | 1998-09-14 | 2000-03-22 | 世大积体电路股份有限公司 | 形成相邻于信号线的屏蔽线的方法 |

| US6495445B2 (en) * | 1999-07-02 | 2002-12-17 | International Business Machines Corporation | Semi-sacrificial diamond for air dielectric formation |

| US6597068B2 (en) * | 2000-05-09 | 2003-07-22 | International Business Machines Corporation | Encapsulated metal structures for semiconductor devices and MIM capacitors including the same |

| US6555467B2 (en) * | 2001-09-28 | 2003-04-29 | Sharp Laboratories Of America, Inc. | Method of making air gaps copper interconnect |

| US6635506B2 (en) * | 2001-11-07 | 2003-10-21 | International Business Machines Corporation | Method of fabricating micro-electromechanical switches on CMOS compatible substrates |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN102232104A (zh) * | 2009-06-15 | 2011-11-02 | 住友电木株式会社 | 用于半导体晶片的暂时粘合剂以及使用所述粘合剂制造半导体设备的方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1756862A4 (en) | 2011-03-02 |

| KR101006286B1 (ko) | 2011-01-06 |

| US20060197119A1 (en) | 2006-09-07 |

| WO2005112105A1 (en) | 2005-11-24 |

| JP4776618B2 (ja) | 2011-09-21 |

| CN1947234A (zh) | 2007-04-11 |

| EP1756862A1 (en) | 2007-02-28 |

| TWI464840B (zh) | 2014-12-11 |

| US7608909B2 (en) | 2009-10-27 |

| JP2007535825A (ja) | 2007-12-06 |

| KR20070018899A (ko) | 2007-02-14 |

| TW200603368A (en) | 2006-01-16 |

| US20050245063A1 (en) | 2005-11-03 |

| US7005371B2 (en) | 2006-02-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN100423216C (zh) | 在线后端处理中形成悬空传输线结构的方法 | |

| US10861788B2 (en) | Patterning approach for improved via landing profile | |

| KR101742925B1 (ko) | 다마신 구조물의 구조물 및 형성방법 | |

| US6057226A (en) | Air gap based low dielectric constant interconnect structure and method of making same | |

| US4776087A (en) | VLSI coaxial wiring structure | |

| US7091611B2 (en) | Multilevel copper interconnects with low-k dielectrics and air gaps | |

| JP4283106B2 (ja) | 犠牲材料を用いた半導体構造およびその製造方法並びに実施方法 | |

| US9478508B1 (en) | Microwave integrated circuit (MMIC) damascene electrical interconnect for microwave energy transmission | |

| US6486557B1 (en) | Hybrid dielectric structure for improving the stiffness of back end of the line structures | |

| CN101924093B (zh) | 半导体器件和制造半导体器件的方法 | |

| CN103811414B (zh) | 铜蚀刻集成方法 | |

| US9553017B2 (en) | Methods for fabricating integrated circuits including back-end-of-the-line interconnect structures | |

| US7294568B2 (en) | Formation of air gaps in an interconnect structure using a thin permeable hard mask and resulting structures | |

| CN109545735B (zh) | 金属内连线结构及其制作方法 | |

| US6410425B1 (en) | Integrated circuit with stop layer and method of manufacturing the same | |

| KR100688758B1 (ko) | 반도체 소자의 금속 배선용 갭필 형성 방법 | |

| US6750544B1 (en) | Metallization system for use in a semiconductor component | |

| CN223566625U (zh) | 集成电路装置 | |

| JP4413393B2 (ja) | 固体電子装置 | |

| KR100546940B1 (ko) | 반도체 소자의 구리 배선 형성 방법 | |

| KR100835423B1 (ko) | 반도체 제조 공정에서의 듀얼 다마신 패턴 형성 방법 | |

| CN119943813A (zh) | 一种半导体结构以及形成方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20081001 Termination date: 20120428 |