WO2012164474A2 - System and method for fast compensation programming of pixels in a display - Google Patents

System and method for fast compensation programming of pixels in a display Download PDFInfo

- Publication number

- WO2012164474A2 WO2012164474A2 PCT/IB2012/052651 IB2012052651W WO2012164474A2 WO 2012164474 A2 WO2012164474 A2 WO 2012164474A2 IB 2012052651 W IB2012052651 W IB 2012052651W WO 2012164474 A2 WO2012164474 A2 WO 2012164474A2

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- programming

- voltage

- transistor

- capacitor

- driving

- Prior art date

Links

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G5/00—Control arrangements or circuits for visual indicators common to cathode-ray tube indicators and other visual indicators

- G09G5/10—Intensity circuits

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3275—Details of drivers for data electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/08—Active matrix structure, i.e. with use of active elements, inclusive of non-linear two terminal elements, in the pixels together with light emitting or modulating elements

- G09G2300/0809—Several active elements per pixel in active matrix panels

- G09G2300/0842—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor

- G09G2300/0861—Several active elements per pixel in active matrix panels forming a memory circuit, e.g. a dynamic memory with one capacitor with additional control of the display period without amending the charge stored in a pixel memory, e.g. by means of additional select electrodes

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0224—Details of interlacing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0251—Precharge or discharge of pixel before applying new pixel voltage

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0243—Details of the generation of driving signals

- G09G2310/0259—Details of the generation of driving signals with use of an analog or digital ramp generator in the column driver or in the pixel circuit

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/02—Improving the quality of display appearance

- G09G2320/029—Improving the quality of display appearance by monitoring one or more pixels in the display panel, e.g. by monitoring a fixed reference pixel

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/04—Maintaining the quality of display appearance

- G09G2320/043—Preventing or counteracting the effects of ageing

- G09G2320/045—Compensation of drifts in the characteristics of light emitting or modulating elements

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

- G09G2320/0693—Calibration of display systems

Definitions

- the present disclosure generally relates to circuits and methods of driving, calibrating, and programming displays, particularly displays such as active matrix organic light emitting diode displays.

- Displays can be created from an array of light emitting devices each controlled by individual circuits (i.e., pixel circuits) having transistors for selectively controlling the circuits to be programmed with display information and to emit light according to the display information.

- Thin film transistors (“TFTs”) fabricated on a substrate can be incorporated into such displays. TFTs fabricated on poly-silicon tend to demonstrate non-uniform behavior across display panels and over time. Some displays therefore utilize compensation techniques to achieve image uniformity in poly-silicon TFT panels.

- Compensated pixel circuits generally have shortcomings when pushing speed, pixel-pitch ("pixel density"), and uniformity to the limit, which leads to design trade-offs to balance competing demands amongst programming speed, pixel-pitch, and uniformity.

- additional lines and transistors associated with each pixel circuit may allow for additional compensation leading to greater uniformity, yet undesirably decrease pixel-pitch.

- programming speed may be increased by biasing or pre-charging each pixel circuit with a relatively high biasing current or initial charge, however, uniformity is enhanced by utilizing a relatively low biasing current or initial charge.

- a display designer is forced to make trade-offs between competing demands for programming speed, pixel-pitch, and uniformity.

- Displays configured to display a video feed of moving images typically refresh the display at a regular frequency for each frame of the video feed being displayed.

- Displays incorporating an active matrix can allow individual pixel circuits to be programmed with display information during a program phase and then emit light according to the display information during an emission phase.

- displays operate with a duty cycle characterized by the relative durations of the program phase and the emission phase.

- the displays operate with a frequency that is characterized by the refresh rate of the display.

- the refresh rate of the display can also be influenced by the frame rate of the video stream.

- the display can be darkened during program phases while the pixel circuits are receiving programming information.

- the display is repeatedly darkened and brightened at the refresh rate of the display. A viewer of the display can undesirably perceive that the display is flickering depending on the frequency of the refresh rate.

- aspects of the present disclosure provide systems and methods for utilizing a current divider created by a storage capacitor within a pixel circuit and a capacitance associated with a data line coupled to the pixel circuit to divide a reference current applied to the data line.

- the divided current simultaneously calibrates the pixel circuit and discharges the data line prior to a driving interval.

- the portion of the reference current that discharges the data line can be of a greater magnitude than the portion of the reference current that calibrates the pixel circuit.

- the reference current is divided according to the relative capacitance of the storage capacitor and the capacitance of the data line.

- the data line is discharged quickly by a large current, while the current through a driving transistor within the pixel circuit remains small. Dividing the current in this manner simultaneously ensures that the data line is rapidly discharged and thus the pixel circuit is able to be programmed swiftly, while the current through the driving transistor is kept small to prevent the uniformity of the display from being adversely affected by the enhanced settling time.

- aspects of the present disclosure also advantageously allow for applying a reference current ("biasing current”) through a data programming line rather than a separate line. Utilizing the same line for multiple purposes thus allows the pixel density to be increased and thereby increase display resolution by decreasing pixel size.

- FIG. 1 Particular pixel circuit configurations suitable for implementation are provided, but it is recognized that the present disclosure applies to current programmed pixel circuits, pixel circuits with n-type or p-type transistors, and pixel circuits in a variety of possible configurations that allow for a storage capacitor to divide a reference current that is applied to a data line to simultaneously discharge the data line while calibrating the pixel circuit.

- Other suitable configurations may include storage capacitors having one terminal coupled to a data line, with another terminal of the storage capacitor coupled to a current path of a driving transistor.

- Aspects of the present disclosure further provide for methods of driving a display to decrease, or even eliminate, a perception of flickering in the display by increasing the refresh rate of the display.

- each frame in the video stream may be displayed more than once in order to increase the refresh rate of the display beyond the frame rate of the video stream and thereby decrease the perception of flickering experienced at the frame rate of the video.

- Aspects provide for implementations of the increased refresh rate in overlapping configurations where distinct portions of a display are updated sequentially during different refresh events, but all spanning a single frame time.

- the distinct portions can be odd and even rows of the display, or halves, thirds, etc. of the display (e.g., top and bottom halves, left and right halves, etc.).

- FIG. 1 is a diagram of an exemplary display system including includes an address driver, a data driver, a controller, a memory storage, and display panel.

- FIG. 2A is a block diagram of an example pixel circuit configuration for a display that incorporates a monitoring line.

- FIG. 2B is a circuit diagram including a pixel circuit for a display that is labeled to illustrate a current path during a program phase of the pixel circuit.

- FIG. 2C is a circuit diagram of the circuit shown in FIG. 2A, which is labeled to illustrate a current path during an emission phase of the pixel circuit.

- FIG. 2D is a timing diagram illustrating a programming and emission operation of the pixel circuit shown in FIGS. 2B and 2C.

- FIG. 2E is an alternate timing diagram for the pixel circuit in FIGS. 2B and 2C which includes a voltage pre-charge cycle.

- FIG. 2F is another alternate timing diagram for the pixel circuit in FIGS. 2B and 2C which includes a current pre-charge cycle.

- FIG. 3A illustrates a graph of simulation results for drive current error versus mobility variations at low grayscale programming values.

- FIG. 3B illustrates a graph of simulation results for drive current error versus mobility variations at high grayscale programming values.

- FIG. 4A is a block diagram of another example pixel circuit for a display.

- FIG. 4B is a circuit diagram including a pixel circuit for a display that is labeled to illustrate a current path during a pre-charge phase of the pixel circuit.

- FIG. 4C is a circuit diagram of the circuit shown in FIG. 4B, which is labeled to illustrate a current path during a program phase of the pixel circuit.

- FIG. 4D is a circuit diagram of the circuit shown in FIG. 4B, which is labeled to illustrate a current path during an emission phase of the pixel circuit.

- FIG. 4E is a timing diagram illustrating pre-charging, compensation, and emission cycles of the pixel shown in FIGS. 4B-4D.

- FIG. 4F is a timing diagram illustrating the change in voltage on the data line during the compensation phase shown schematically in FIG. 4C.

- FIG. 5 illustrates a circuit diagram for a portion of a display showing two pixel circuits in an example configuration suited to providing enhanced settling time.

- FIG. 6 illustrates a circuit diagram for a portion of a display showing two other pixel circuits in an example configuration also suited to providing enhanced settling time.

- FIG. 7 illustrates a circuit diagram for a portion of a display showing still two more pixel circuits in an example configuration also suited to providing enhanced settling time.

- FIG. 8A is a circuit diagram of a pixel circuit configured to provide the pre- charging and compensation cycle simultaneously.

- FIG. 8B is a timing diagram illustrating the operation of the simultaneous pre- charge and compensation cycle.

- FIG. 9A illustrates an additional configuration of a pixel circuit configured to program the pixel circuit via a programming capacitor connected to a gate terminal of a drive transistor via a first selection transistor.

- FIG. 9B is an alternative pixel circuit configured similarly to the pixel circuit shown in FIG. 9A, but with an additional switch transistor connected in series with the second switch transistor.

- FIG. 10 is a timing diagram describing an exemplary operation of the pixel circuit of FIG. 9A or the pixel circuit of FIG. 9B.

- FIG. 11 illustrates a circuit diagram of a portion of a display panel in which multiple pixel circuits are arranged to share a common programming capacitor.

- FIG. 12A is a timing diagram of an exemplary operation of the "kth" segment shown in FIG. 11.

- FIG. 12B is a timing diagram of another exemplary operation of the "kth" segment shown in FIG. 11.

- FIG. 13A is a timing diagram for driving a single frame of a segmented display.

- FIG. 13B is a flow chart corresponding to the timing diagram shown in FIG. 13 A.

- FIGS. 14A and 14B provide experimental results of percentage errors in pixel currents given variations in device parameters for pixel circuits such as those shown in FIGS. 9 A and 9B.

- FIG. 15A is a circuit diagram showing a portion of the gate driver including control lines (“CNTi") to regulate the first select lines for each segment.

- CNTi control lines

- FIG. 15B is a diagram of the first two gate outputs which are used to provide the first select lines for the first two segments.

- FIG. 16 is a timing diagram for a display array operated by an address driver utilizing control lines to generate the first select line signals.

- FIG. 17A is a block diagram of a source driver with an integrated voltage ramp generator for driving each data line in a display panel.

- FIG. 17B is a block diagram of another source driver that provides a ramp voltage for each data line in a display panel and includes a cyclic digital to analog converter.

- FIG. 18A is a display system including a demultiplexer to share multiple data lines with a single output terminal of the source driver.

- FIG. 18B is a timing diagram for the display array shown in FIG. 18A illustrating problems in setting pixels to new data values.

- FIG. 18C is a timing diagram for operation of the display system shown in FIG. 18A, which pre-charges data line capacitances before selecting rows for programming.

- FIG. 19A pictorially illustrates a programming and emission sequence for displaying a single frame with a 50% duty cycle.

- FIG. 19B pictorially illustrates an example programming and emission sequence for displaying a single frame with a 50% duty cycle, which is adapted to decrease flickering associated with the display.

- FIG. 20A pictorially illustrates another example programming and emission sequence for displaying a single frame with a 50%> duty cycle similar to FIG. 19B, but with a frame time two times as long as the frame time illustrated by FIG. 19B.

- FIG. 20B pictorially illustrates yet another example programming and emission sequence for displaying a single frame with a 50%> duty cycle similar to FIG. 19B, but with a frame time three times as long as the frame time illustrated by FIG. 19B.

- FIG. 21 A pictorially illustrates another example programming and emission sequence for displaying a single frame while separately programming portions of the display during distinct program phases.

- FIG. 2 IB pictorially illustrates another example programming and emission sequence for displaying a single frame while separately programming interlaced portions of the display during distinct program phases.

- FIG. 21C pictorially illustrates example programming and emission sequences for displaying a single frame where the sequence illustrated in FIG. 21B is followed by additional emission and idle phases or where the sequence illustrated in FIG. 2 IB is interrupted by additional programming and idle phases.

- FIG. 2 ID pictorially illustrates still another example programming and emission sequence for displaying a single frame where portions of the display are sorted into four interlaced groupings according to row numbers and each portion is separately programmed.

- FIG. 22A is a block diagram of a circuit layout for connecting alternating rows of a display panel to distinct data lines.

- FIG. 22B is a block diagram of a circuit layout for connecting interlaced pixels of a display panel to distinct data lines.

- FIG. 23A is a timing diagram for a display panel with distinct portions that are programmed in distinct intervals and which share data lines.

- FIG. 23B is a timing diagram for a display panel with distinct portions that are programmed in distinct intervals and which do not share data lines.

- FIG. 24 illustrates a bidirectional current source in accordance with an embodiment of the disclosure.

- FIG. 25 illustrates an example of a display system with the bidirectional current source of FIG. 24.

- FIG. 26 illustrates a further example of a display system with the bidirectional current source of FIG. 24.

- FIG. 27 illustrates a further example of a display system with the bidirectional current source of FIG. 24.

- FIG. 28 illustrates a further example of a display system with the bidirectional current source of FIG. 24.

- FIG. 29A illustrates an example of a current biased voltage programmed pixel circuit applicable to the display system of FIG. 28.

- FIG. 29B illustrates an example of a timing diagram for the pixel circuit of FIG.

- FIG. 30A illustrates simulation results for the pixel circuit of FIG. 29A.

- FIG. 30B illustrates further simulation results for the pixel circuit of FIG. 29A.

- Embodiments of the present invention are described using a display system that may be fabricated using different fabrication technologies including, for example, but not limited to, amorphous silicon, poly silicon, metal oxide, conventional CMOS, organic, anon/micro crystalline semiconductors or combinations thereof.

- the display system includes a pixel that may have a transistor, a capacitor and a light emitting device.

- the transistor may be implemented in a variety of materials systems technologies including, amorphous Si, micro/nano-crystalline Si, poly-crystalline Si, organic/polymer materials and related nanocomposites, semiconducting oxides or combinations thereof.

- the capacitor can have different structure including metal-insulator-metal and metal-insulator-semiconductor.

- the light emitting device may be, for example, but not limited to, an OLED.

- the display system may be, but not limited to, an AMOLED display system.

- pixel circuit and “pixel” may be used interchangeably.

- Each transistor may have a gate terminal and two other terminals (first and second terminals).

- one of the terminals or "first terminal” (the other terminal or “second terminal") of a transistor may correspond to, but not limited to, a drain terminal (a source terminal) or a source terminal (a drain terminal).

- FIG. 1 is a diagram of an exemplary display system 50.

- the display system 50 includes an address driver 8, a data driver 4, a controller 2, a memory storage 6, and a display panel 20.

- the display panel 20 includes an array of pixels 10 arranged in rows and columns. Each of the pixels 10 are individually programmable to emit light with individually programmable luminance values.

- the controller 2 receives digital data indicative of information to be displayed on the display panel 20 (such as a video stream).

- the controller 2 sends signals 32 to the data driver 4 and scheduling signals 34 to the address driver 8 to drive the pixels 10 in the display panel 20 to display the information indicated.

- the plurality of pixels 10 associated with the display panel 20 thus comprise a display array ("display screen") adapted to dynamically display information according to the input digital data received by the controller 2.

- the display screen can display, for example, video information from a stream of video data received by the controller 2.

- the supply voltage 14 can provide constant power voltage(s) or can be an adjustable voltage supply that is controlled by signals 38 from the controller 2.

- the display system 50 can also incorporate features from a current source or sink (e.g., the current source 134 in FIG. 2B or the current source 234 in FIG. 4C) to provide biasing currents to the pixels 10 in the display panel 20 to thereby decrease programming time for the pixels 10.

- the display system 50 in FIG. 1 is illustrated with only four pixels 10 in the display panel 20. It is understood that the display system 50 can be implemented with a display screen that includes an array of similar pixels, such as the pixels 10, and that the display screen is not limited to a particular number of rows and columns of pixels. For example, the display system 50 can be implemented with a display screen with a number of rows and columns of pixels commonly available in displays for mobile devices, monitor-based devices, and/or projection-devices.

- the pixel 10 is operated by a driving circuit (“pixel circuit") that generally includes a driving transistor and a light emitting device.

- the pixel 10 may refer to the pixel circuit.

- the light emitting device can optionally be an organic light emitting diode, but implementations of the present disclosure apply to pixel circuits having other electroluminescence devices, including current-driven light emitting devices.

- the driving transistor in the pixel 10 can include thin film transistors ("TFTs”), which an optionally be n- type or p-type amorphous silicon TFTs or poly-silicon TFTs. However, implementations of the present disclosure are not limited to pixel circuits having a particular polarity or material of transistor or only to pixel circuits having TFTs.

- the pixel circuit 10 can also include a storage capacitor for storing programming information and allowing the pixel circuit 10 to drive the light emitting device after being addressed.

- the display panel 20 can be an active matrix display array.

- the pixel 10 illustrated as the top-left pixel in the display panel 20 is coupled to a select line 24i, supply line 26i, 27i, a data line 22j, and a monitor line 28j.

- the first supply line 26i can be charged with VDD and the second supply line 27i can be charged with VSS.

- the pixel circuits 10 can be situated between the first and second supply lines to allow driving currents to flow between the two supply lines 26i, 27i during an emission cycle of the pixel circuit.

- the top-left pixel 10 in the display panel 20 can correspond to a pixel in the display panel in a "ith" row and "jth" column of the display panel 20.

- the top- right pixel 10 in the display panel 20 represents a "ith" row and “mth” column; the bottom- left pixel 10 represents an “nth” row and “jth” column; and the bottom-right pixel 10 represents an "nth” row and “mth” column.

- Each of the pixels 10 is coupled to appropriate select lines (e.g., the select lines 24i and 24n), supply lines (e.g., the supply lines 26i, 26n, and 27i, 27n), data lines (e.g., the data lines 22j and 22m), and monitor lines (e.g., the monitor lines 28j and 28m). It is noted that aspects of the present disclosure apply to pixels having additional connections, such as connections to additional select lines, including global select lines, and to pixels having fewer connections, such as pixels lacking a connection to a monitoring line.

- the select line 24i is provided by the address driver 8, and can be utilized to enable, for example, a programming operation of the pixel 10 by activating a switch or transistor to allow the data line 22j to program the pixel 10.

- the data line 22j conveys programming information from the data driver 4 to the pixel 10.

- the data line 22j can be utilized to apply a programming voltage or a programming current to the pixel 10 in order to program the pixel 10 to emit a desired amount of luminance.

- the programming voltage (or programming current) supplied by the data driver 4 via the data line 22j is a voltage (or current) appropriate to cause the pixel 10 to emit light with a desired amount of luminance according to the digital data received by the controller 2.

- the programming voltage can be applied to the pixel 10 during a programming operation of the pixel 10 so as to charge a storage device within the pixel 10, such as a storage capacitor, thereby enabling the pixel 10 to emit light with the desired amount of luminance during an emission operation following the programming operation.

- a storage device within the pixel 10 such as a storage capacitor

- the storage device in the pixel 10 can be charged during the programming operation to apply a voltage to one or more of a gate or a source terminal of the driving transistor during the emission operation, thereby causing the driving transistor to convey the driving current through the light emitting device according to the voltage stored on the storage device.

- the driving current that is conveyed through the light emitting device by the driving transistor during the emission operation of the pixel 10 is a current that is supplied by the first supply line 26i and is drained to the second supply line 27i.

- the first supply line 26i and the second supply line 27i are coupled to the voltage supply 14.

- the first supply line 26i can provide a positive supply voltage (e.g., the voltage commonly referred to in circuit design as "Vdd") and the second supply line 27i can provide a negative supply voltage (e.g., the voltage commonly referred to in circuit design as "Vss").

- Implementations of the present disclosure can be realized where one or the other of the supply lines (e.g., the supply lines 26i, 27i) are fixed at a ground voltage or at another reference voltage. Implementations of the present disclosure also apply to systems where the voltage supply 14 is implemented to adjustably control the voltage levels provided on one or both of the supply lines (e.g,. the supply lines 26i, 27i). The output voltages of the voltage supply 14 can be dynamically adjusted according to control signals 38 from the controller 2. Implementations of the present disclosure also apply to systems where one or both of the voltage supply lines 26i, 27i are shared by more than one row of pixels in the display panel 20.

- the display system 50 also includes a monitoring system 12. With reference again to the top left pixel 10 in the display panel 20, the monitor line 28j connects the pixel 10 to the monitoring system 12.

- the monitoring system 12 can be integrated with the data driver 4, or can be a separate stand-alone system. Furthermore, the monitoring system 12 can optionally be implemented by monitoring the current and/or voltage of the data line 22j during a monitoring operation of the pixel 10, and the monitor line 28j can be entirely omitted. Additionally, the display system 50 can be implemented without the monitoring system 12 or the monitor line 28j.

- the monitor line 28j allows the monitoring system 12 to measure a current and/or voltage associated with the pixel 10 and thereby extract information indicative of a degradation of the pixel 10.

- the monitoring system 12 can extract, via the monitor line 28j, a current flowing through the driving transistor within the pixel 10 and thereby determine, based on the measured current and based on the voltages applied to the driving transistor during the measurement, a threshold voltage of the driving transistor or a shift thereof. Furthermore, a voltage extracted via the monitoring lines 28j, 28m can be indicative of a degradation in the respective pixels 10 due to changes in the current-voltage characteristics of the pixels 10 or due to shifts in the operating voltages of light emitting devices situated within the pixels 10.

- the monitoring system 12 can also extract an operating voltage of the light emitting device (e.g., a voltage drop across the light emitting device while the light emitting device is operating to emit light). The monitoring system 12 can then communicate the signals 32 to the controller 2 and/or the memory 6 to allow the display system 50 to store the extracted degradation information in the memory 6. During subsequent programming and/or emission operations of the pixel 10, the degradation information is retrieved from the memory 6 by the controller 2 via the memory signals 36, and the controller 2 then compensates for the extracted degradation information in subsequent programming and/or emission operations of the pixel 10.

- an operating voltage of the light emitting device e.g., a voltage drop across the light emitting device while the light emitting device is operating to emit light.

- the monitoring system 12 can then communicate the signals 32 to the controller 2 and/or the memory 6 to allow the display system 50 to store the extracted degradation information in the memory 6.

- the degradation information is retrieved from the memory 6 by the controller 2 via the memory signals 36, and the controller 2 then compensates for the extracted degradation information in subsequent programming and

- the programming information conveyed to the pixel 10 during a subsequent programming operation can be appropriately adjusted such that the pixel 10 emits light with a desired amount of luminance that is independent of the degradation of the pixel 10.

- an increase in the threshold voltage of the driving transistor within the pixel 10 can be compensated for by appropriately increasing the programming voltage applied to the pixel 10.

- FIG. 2A is a block diagram of an example pixel circuit configuration 110 for the display system 50 that incorporates the monitoring line 28j.

- TFTs fabricated in poly-silicon tend to demonstrate non-uniform behavior across a display panel (e.g,. the display panel 20) and over time (e.g., over a display's operating life time). Compensation techniques to achieve image uniformity in poly-silicon TFT panels, as well as other TFT materials (e.g., amorphous silicon, etc.), are provided herein.

- the general functionality of compensation techniques relies on the application of a uniform reference current to the pixel circuit.

- the reference current is used to develop a gate-to-source voltage on the TFT drive device. This voltage is a function of threshold, mobility, and other parameters across panel, time and temperature variations.

- the developed voltage is stored on the storage element which is then used as a calibration factor to provide programming to the pixel.

- programming data is modified according to the calibration factor stored in the storage element.

- Such compensated pixel circuits thus have some shortcoming when pushing the programming speed, pixel density, and uniformity to their respective limits, and a display designer is therefore required to make design choices.

- Modified techniques and driving schemes are presented in this disclosure to tackle the challenges of compensation method(s) requiring such design trade-offs.

- the pixel circuit 110 of FIG. 2A features a dedicated monitor line 28j and a monitor switch 120 to apply the reference current to the selected pixel out of a vertical column of pixels (e.g., the pixels in the "jth" column) on the panel 20.

- the voltage on the voltage supply line 26i (“V DD ") is toggled low to V DDL by the voltage supply 14 during the programming cycle to avoid interference from the light emitting device 114 ("OLED").

- OLED light emitting device

- FIG. 2A illustrates a block diagram of a pixel circuit 110, which can be implemented as the pixel 10 in the display system 50 shown in FIG. 1.

- the pixel circuit 110 includes a drive device 112, which can be a drive transistor, a storage element 116, which can be a storage capacitor, an access switch 118, which can be a switch transistor, and a monitor switch 122.

- the drive transistor 112 conveys a driving current to the light emitting device 114 ("OLED") according to a programming voltage stored on the storage capacitor 116 and applied to the gate and/or source terminals of the drive transistor 112.

- the programming voltage is developed on the storage capacitor 116 by selectively connecting one and/or both terminals of the storage capacitor 116 to the data line 22j via the switch transistor 118.

- the switch transistor 118 is operated according to the select line 24i and/or the emission line 25, which can be a global select line that is shared by pixels in more than one row of the display array 20.

- FIG. 2B is a circuit diagram including an exemplary implementation of the pixel circuit 110 represented by the block diagram in FIG. 2A.

- the circuit diagram in FIG. 2B is labeled with an arrow 150 to illustrate a current path through the pixel circuit 110 during a programming cycle 160.

- the circuit diagram in FIB. 2C is labeled with an arrow 154 to illustrate a current path through the pixel circuit 110 during an emission cycle 164.

- Transistors illustrated in the circuit diagrams in FIGS. 2B and 2C which are turned off during the respectively illustrated operation cycles are illustrated with hashed marks to indicate they are turned off.

- a timing diagram illustrating the programming cycle 150 and emission cycle 160 is provided in FIG. 2D.

- the pixel circuit 110 illustrated in FIGS. 2B and 2C will thus be described in connection with the timing diagram in FIG. 2D.

- the reference current "(I REF ") flows directly through the drive device 112 ("drive transistor") which can be, for example, a poly- silicon TFT.

- drive transistor which can be, for example, a poly- silicon TFT.

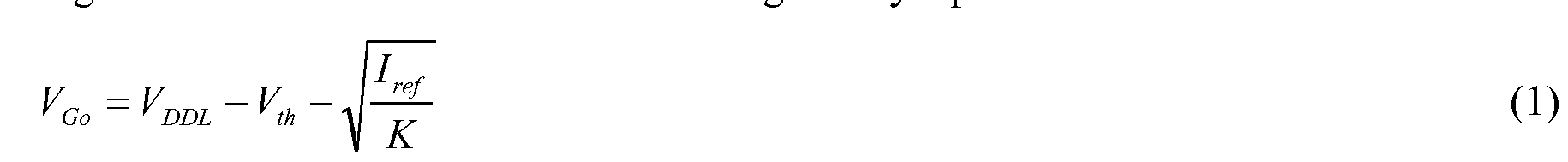

- K is the current factor of the drive TFT 112 which is a function of mobility ( ⁇ ), unit gate oxide (C ox ), and the aspect ratio of the device (W/L), as shown in equation 2:

- the voltage on the gate terminal (i.e., the gate voltage) on the drive transistor 112 also sets the voltage on one side of the storage element 116 ("storage capacitor Cs")- As shown in FIG. 2B, the gate node 112g, which is directly connected to both the gate terminal of the drive transistor 112 and one terminal of the storage capacitor 116, is labeled as having V GO - Meanwhile, during the programming cycle 150, the other side ("second terminal") of the storage capacitor 116 is set to the desired data voltage, V D , which is a representative of the grayscale luminance level to be programmed. The data voltage V D is programmed through the data line 22j by an output channel of the source driver 4. At the end of the programming cycle 150, the voltage stored on the storage capacitor 116 is given by equation 3:

- V C V D - V GO (3)

- the select transistor 118 and the monitor switch transistor 120 are deactivated by setting the select line 24i to a high level.

- An additional period 152 can then elapse while other rows (e.g., the "nth" row selected by the select line 24n) in the display panel 20 are programmed.

- An emission cycle 154 can then be commenced once all rows are programmed. Additionally or alternatively, the emission cycle 154 can be commenced once each individual row is programmed without waiting for other rows to be programmed during the period 152.

- the data line 22j is isolated from the source driver 6 and connected to a reference voltage V REF - AS shown in FIGS.

- isolating the data line 22j can be accomplished by coupling the data line 22j to the source driver 6 via a programming switch 130 operated according to a programming signal ("Prog") conveyed on a programming line 138.

- the reference voltage V REF can then be supplied to the data line 22j via a switch transistor 132 operated according to an emission signal (“EM”) conveyed on an emission control line 25.

- EM emission signal

- One or both of the emission control line 25 and the programming line 138 can be implemented as global signals to simultaneously control the connections to the data line 22j across the entire display panel 20, or to portions thereof.

- the voltage on the supply voltage line 26i is toggled to V DDH , which can be considered an operating voltage of the supply voltage line 26i which is sufficient to turn the OLED 114 on. Accordingly, the gate-source voltage of the drive transistor 112 is given by equation 5 :

- Equation 8 confirms that the above described compensation technique eliminates the first order effects of the threshold voltage variations from the drive current.

- FIG. 3A illustrates a graph of simulation results for drive current error versus mobility variations at low grayscale programming values.

- FIG. 3B illustrates a graph of simulation results for drive current error versus mobility variations at high grayscale programming values.

- the effectiveness of the compensation for mobility variations is affected by the amount of the reference current I REF -

- the compensation in both low and high grayscale levels, as shown in FIG. 3A and FIG. 3B, respectively, is more effective when a lower value of the reference current is utilized. Accordingly, to realize effective compensation across the display panel 20, a low reference current is preferred.

- the monitor line 28j introduces a significant parasitic capacitance 136 to the signal path of the reference current I REF - Accordingly, a large value of the reference current I REF is sought so as to achieve fast settling time. Therefore, in the compensation techniques described in reference to FIGS. 2A-2D, there is a trade-off between achievable uniformity and settling time when designing for a particular value of the reference current I REF .

- PPI pixel per inch

- a two cycle programming including a precharging cycle 160a, 161a and an adjustment cycle 160b, 161b is discussed below which can improve the effectiveness of compensation.

- the two cycle programming techniques are illustrated by the timing diagrams in FIGS. 2E and 2F, respectively.

- the modified compensation techniques disclosed next break the speed-uniformity trade-off and are fully compatible with available industry standards and driver components. These techniques therefore offer a significant performance improvement which can be implemented without substantial fabrication modifications that require extensive capital investments.

- One approach of implementing a two-phase compensation technique is to precharge the capacitance 136 of the monitor line 28j during a pre-charging cycle 150a and then allow some time (T p ) for the drive transistor 112 to adjust the voltage on the data line 22j during an adjustment cycle 160b.

- the monitor switch transistor 120 can disconnect the monitor line 28j from the pixel circuit 110 during the adjustment cycle 160b.

- the timing diagram in FIG. 2E illustrates the voltage pre-charging approach to pre-charge the capacitance 136.

- the precharging can be accomplished by setting the voltage on the monitor line 28j to a constant value Vp reQ . In this case, it can be shown that the drive current is given by equation 9:

- T p is the adjustment time

- Vp is the program voltage

- ⁇ is the time constant of the charge path through the drive device.

- Another alternative is to precharge the monitor line 28j by applying a relatively high reference current I REF to the monitor line 28j such that the settling requirement is achieved in spite of the parasitic capacitance 136 of the monitor line 28j.

- the reference current I REF can be applied during a pre-charging cycle 161a. Then, the reference current I REF is removed from the monitor line 28j and the drive device 112 is allowed to adjust the voltage on the data line 22j during an adjustment cycle 161b.

- the monitor switch transistor 120 can disconnect the monitor line 28j from the pixel circuit 110 during the adjustment cycle 151b. In this case, it can be shown that the drive current is given by equation 12:

- FIG. 4A illustrates a block diagram of a pixel circuit 210, which can be implemented as the pixel 10 in the display system 50 shown in FIG. 1.

- the pixel circuit 210 includes a drive device 212, which can be a drive transistor, a storage element 216, which can be a storage capacitor, an access switch 218, which can be a switch transistor, and a control switch 222.

- the drive transistor 212 conveys a driving current to the light emitting device 214 ("OLED") according to a programming voltage stored on the storage capacitor 216.

- the programming voltage is applied to the gate and/or source terminals of the drive transistor 212 to control the driving current.

- the programming voltage is developed on the storage capacitor 216 by selectively coupling a first terminal of the storage capacitor 216 to a second terminal of the drive transistor 212 via the switch transistor 218.

- the second terminal of the storage capacitor 216 is coupled to a data line 22j.

- a gate terminal of the drive transistor 212 is coupled to the first terminal of the storage capacitor 216 at a gate node 212g, and the first terminal of the drive transistor 212 is connected to the voltage supply line 26i.

- the switch transistor 218 is operated according to the select line 24i and/or the emission line 25, which can be a global select line that is shared by pixels in more than one row of the display array 20.

- the emission transistor 222 is controlled by the emission line 25 to be turned on during an emission cycle 266 of the pixel circuit 210, and to disconnect the light emitting device 214 from the drive transistor 212 during periods other than the emission cycle 266.

- FIG 4B illustrates an exemplary circuit diagram for the pixel circuit 210, which is labeled with an arrow 250 to show the current path through the pixel during a pre-charging cycle 260 of the pixel circuit.

- FIG. 4C illustrates the pixel circuit 210 shown in FIG. 4B, but labeled with arrows 252, 252L, and 252P to show the current path through the pixel during a compensation cycle 262 following the pre-charging cycle 260.

- FIG. 4D illustrates the pixel circuit 210 shown in FIG. 4A, but labeled with an arrow 256 to show the current path through the pixel during an emission cycle 266.

- FIG. 4E illustrates a timing diagram illustrating the operation of the pixel 210 during the pre-charging, compensation, and emission cycles 260, 262, 266.

- FIG. 4F provides an enhanced view of the voltage level on the data line 22j during the compensation cycle 262. Accordingly, the features illustrated by FIGS. 4A-4F will be described jointly below.

- a reference current I REF is applied through the data line 22j which introduces several advantages relative to the pixel circuit 110 shown in FIG. 2A.

- the dedicated monitor line 28j and monitor switch 120 are eliminated in the pixel circuit 210.

- a considerable amount of area is freed up on the display panel 20 which enables very high density pixel layout.

- a control switch 222 is placed in series with the OLED 214 to eliminate the need for toggling the voltage of the supply voltage line 26i during the programming phase.

- the voltage of the supply voltage line 26i (or the supply voltage line 27i) is toggled to a low voltage (or high voltage) during the programming cycle 150 to prevent the OLED 114 from emitting light during programming.

- the gate terminal of the drive transistor 212 is directly coupled to a first terminal of the storage capacitor 216 at a gate node 212g.

- the second terminal of the storage capacitor 216 is coupled to the data line 22j.

- the switch transistor 218 is connected between the gate node 212g and a second terminal (e.g., a drain terminal) of the drive transistor 212 while the first terminal (e.g., a source terminal) of the drive transistor 212 is coupled to the voltage supply line 26i.

- the three-cycle operation of the compensation technique is illustrated in FIGS.

- an emission transistor 222 situated in series with the OLED 214 turns the OLED 214 off during the pre- charging and compensation cycles 260, 262.

- operation begins with a precharge cycle 260.

- the emission line 25 is set high to keep the emission transistor 222 turned off.

- the emission line 25 is also coupled to a switch transistor 132 to keep the data line 22j disconnected from a reference voltage source during the pre-charging and programming cycles 260, 262.

- a desired row, such as the "ith" row is selected by setting the select line 24i low, which turns on the switch transistor 218, and the data line 22j is precharged to the given program voltage, Vp.

- the arrow 250 illustrates the current flow during the pre-charging cycle 260 to charge the capacitance 23j of the data line 22j. Simultaneously, because the select transistor 218 is turned on, current flows through the drive transistor 212 until the gate-source voltage of the drive transistor 212 settles at a level sufficient to turn off the drive transistor 212. At the end of the pre-charging cycle 260, the voltage that is developed on the gate terminal of the drive transistor 212 (i.e., at the gate node 212g) is given by equation 14:

- a reference current IREF is applied to the data line 22j.

- the pixel circuit 210 advantageously allows the reference current IREF to not flow directly through the drive transistor 212 of the pixel circuit 210. Instead, as will be described in reference to FIG. 4C, only a small portion (I p i xel ) of the reference current I RE F passes through the storage capacitor 216 and the drive transistor 212. A larger portion (Iii ne ) of the reference current IREF is utilized to charge/discharge the capacitance 23j of the data line 22j. Accordingly, a pixel circuit is realized providing both good compensation and fast settling concurrently ("simultaneously").

- the reference current I RE F is thus divided between the data line 22j and the driving transistor 212 by the configuration of the respective capacitances of the storage capacitor 216 and the capacitance 23j associated with the data line 22j.

- FIG. 4C is labeled with arrows 252, 252L, 252P to illustrate a current path during the compensation cycle 262 of the pixel circuit 210.

- the data switch transistor 130 is turned off by the program signal ("Prog") conveyed on the program line 138 and the reference current I RE F is applied to the data line 22j by the current source 234.

- I RE F is divided into two components: Iii ne which discharges the capacitance 23j of the data line 22j, and I p i Xe i which flows through the drive transistor 212 and across the storage capacitor 216.

- the current path of I p i xel is illustrated by the arrow 252P and the current path of Iii ne is illustrated by the arrow 252L.

- the currents Iii ne and I p i xel join at the data line 22j to cumulatively form the reference current I REF , which is illustrated by the arrow 252.

- the capacitance 23j of the data line 22j and the storage capacitor 216 thus act as a current divider for the reference current I REF -

- These components are constant portions of the reference current I REF as given by equations 15 and 16:

- Iii ne discharges the data line 22j at a constant rate during the compensation cycle 262. This creates a declining voltage on the data line 22j as shown in FIGS. 4E and 4F.

- FIG. 4F is an enhanced view of the voltage on the data line 22j during the compensation cycle 262 to better illustrate the declining voltage ramp.

- the total change in voltage on the data line 22j during the compensation cycle 22j is given by equation 17:

- t prog is the length of the compensation cycle 262.

- the I p i xel component of the reference current I REF develops a voltage across the gate-source terminals of the drive transistor 212 which is a function of its threshold voltage, mobility, oxide-thickness, and other second-order parameters (e.g. drain and source resistance).

- the resulting gate-source voltage on the drive transistor 212 is given by equation 18:

- the gate voltage of the drive transistor 212 (i.e., the voltage at the gate node 212g) is given by equation 19:

- the voltage stored on the storage capacitor 216 is equal to VP -VR -VG which is a function of both the pixel program voltage (VP) and the characteristics of the drive transistor 212 (e.g., due to the contribution of VG).

- the pre-charging cycle 260 and the compensation cycle 262 are repeated for every row of the panel 20 during the period 264.

- FIG. 4D is labeled with an arrow 256 to illustrate a current path during an emission cycle 266 of the pixel circuit 210.

- the emission cycle 266 begins by turning the switch transistor 132 on to set the data line 22j at the reference voltage V REF - Setting the data line 22j at the reference voltage V REF references the second terminal of the storage capacitor 216 to the reference voltage V REF -

- the reference voltage V REF can be chosen to be equal to VDD.

- the emission transistor 222 is also turned on during the emission cycle 266.

- both the switch transistor 132 and the emission transistor 222 can be controlled by an emission control line 25 conveying a global emission control signal.

- the gate-to-source over-drive voltage of the drive transistor 212 is Vov, as given by equation 20:

- the over-drive voltage Vov is thus independent of the threshold voltage of the drive transistor 212.

- the effective drive current of the pixel circuit 210 can hence be designed to be minimally affected by the variations of mobility, oxide thickness, and other varying TFT device parameters.

- FIG. 5 illustrates an exemplary circuit diagram for a portion of a display 20 showing two pixel circuits 210a, 211a in an example configuration that can implement the two-cycle compensation technique described in connection with FIG. 4E.

- the pixel architecture of FIG. 5 also offers a display designer the option of segmenting the display panel 20 into multiple segments that can be separately programmed or driven according to global select lines (e.g., the global select line 246) ("GSEL[k]").

- GSEL[k] global select lines

- the pixel circuit 210a is in the "ith" row and "jth” column of the display panel 20. Also illustrated is the pixel circuit 211a, which is in the next (i.e., "(i+l)th") row and the "jth” column. Both of the pixel circuits 210a and 211a are also in the "kth" segment of the display panel 20. Accordingly, the segmented data line 248 which is shared by the pixel circuits 210a, 211a is coupled to the data line 22j via the segment transistor 244. While the segment transistor 244 is turned on, the segment data line 248 receives voltages and currents applied to the data line 22j. However, while the segment transistor 244 is turned off (e.g., by setting the segment control line 246 high) the segment data line 248 is not connected to the data line 22j.

- This segmented feature illustrated by the configuration in FIG. 5 can allow the data line 22j to be utilized to program other segments of the display array 20 (which are selectively coupled to the data line 22j by their own respective segment transistors) while the "kth" segment is driven to emit light during an emission cycle for the "kth” segment.

- separate segments can be controlled to implement different operations simultaneously (i.e., in parallel) and thereby either increase the time available for pre-charging, programming, and/or compensating each row of the display array 20.

- the segmented driving scheme can allow the effective refresh rate of the display system 50 to be increased.

- the segmented arrangement allows parallel operations.

- half of the display panel 20 can be programmed during a first period while the other half is operated in an emission cycle, and then the second half of the display panel 20 can be programmed during a second period while the first half is operated in an emission cycle.

- the display array can be divided into segments consisting of two rows of pixels each such that each segmented data line (e.g., 248) can be used for two rows.

- the "ith" row of the display can be the "(2k)th” row and "(i+l)th” row of the display can be the "(2k+l)th” row, with k an integer between 0 and N/2 where N is the number of rows in the display panel 20.

- the display can be divided into a plurality of segments each including two or more rows of the display panel 20, and each of the segments having a respective segment transistor to selectively connect to the data line 22j.

- Such a segmented display panel 20 can then operated such that each segment is connected to the data line 22j, while the data line 22j conveys programming and/or compensation signals to the pixels in the segment, and then the respective segment can be disconnected while the data line 22j is fixed at a reference voltage V REF -

- FIG. 6 illustrates another circuit diagram for a portion of a display showing a first and second pixel circuit 210b and 211b configured suitably to implement the two-cycle pre- charging and compensation cycles 260, 262 described in connection with FIG. 4E.

- the pixel circuits 210b, 211b are arranged similarly to the pixel circuit 210 described in FIGS. 4B to 4D.

- the reference current source 234 can be arranged at one side (e.g., the top side) of the display panel 20 while the source driver 4 can be arranged at the other side (e.g., the bottom side) of the display panel.

- Each of the source driver 4 and the reference current source 234 are selectively connected to the data line 22j via respective calibration switch transistor 240 (operated by the calibration control line 242) and the programming switch transistor 130 (operated by the programming control line 138).

- FIG. 7 illustrates a circuit diagram for a portion of a display showing still two more pixel circuits 210c, 211c in an example configuration also suited to provide enhanced settling time via the two-cycle pre-charging and compensation scheme described in connection with FIG. 4E.

- the voltage of the voltage supply line 26i is toggled to prevent emission during the pre-charging and compensation cycles 260, 262.

- Toggling the voltage supply line 26i is not implemented for the pixel circuits shown in FIGS. 5 and 6, which incorporate emission control transistors 222.

- all three circuit configurations 210a-c are fully compatible with available source-driver and gate-driver microchips.

- Implementing the two-cycle programming technique may require modifications to timing controllers, such as the controller 2, the address driver 8, and/or the source driver 4 described in connection with the display system 50 of FIG. 1 in order to provide the functions described in connection with FIGS. 4A through 7.

- FIG. 8A illustrates an additional configuration of a pixel circuit 310 providing power supply voltage V DD via the data line 322j.

- the pixel circuit 310 can be implemented in the display system 50 described above in connection with FIG. 1. However, as shown, the pixel circuit 310 does not utilize a separate monitoring line. Furthermore, the pixel circuit 310 does not utilize a separate voltage supply line 26i.

- the pixel circuit 310 is configured to allow compensation for pixel aging to occur simultaneously with programming, and thereby increase the time available for programming and/or compensation in the pixel circuit 310, as well as decrease the requirements for switching speed of the transistors.

- the pixel circuit 310 includes a drive transistor 312 coupled in series with a light emitting device 314, which can be an organic light emitting diode ("OLED") or another current-driven light emissive device.

- the pixel circuit 310 also includes a storage capacitor 316 having a first terminal coupled to a gate terminal of the drive transistor 312. The first terminal of the storage capacitor 316 and the gate terminal of the drive transistor 312 are thus electrically connected to a common node 312g, which is referred to for convenience as a gate node 312g.

- a switch transistor 318 operated by the select line 24i selectively couples the gate node 312g (and thus the first terminal of the storage capacitor 316 and the gate terminal of the drive transistor 312) to a second terminal of the drive transistor 312, which can be a drain terminal.

- the second terminal of the storage capacitor 316 is connected to a bias line 329, which provides a bias current Ibias to provide compensation to the pixel circuit 310.

- the pixel circuits 210, 210a-c described above implement compensation and programming in a two-phase operation to first pre-charge the data line (in the pre-charging cycle 260) and then apply the bias current (e.g., the reference current I REF ) to provide compensation while simultaneously discharging the data line (during the compensation cycle 262).

- the pixel circuit 310 provides data programming via the data line 322j while simultaneously applying the bias current via the bias line 329 during a programming cycle 360.

- the data line 322j is also utilized to provide a power supply voltage V DD during the emission cycle 364 of the pixel circuit 210.

- the pixel circuit 310 also includes an emission control transistor 322 operated according to an emission control line 25.

- the emission control transistor 322 is arranged between the drain terminal of the drive transistor 312 and the light emitting device 314 so as to selectively connect the light emitting device 314 to the drive transistor 312.

- the emission control transistor 322 can be turned on during an emission cycle 364 of the pixel circuit 310 to allow the pixel circuit 310 to drive the light emitting device 314 to emit light according to programming information.

- the emission control transistor 322 can be turned off during cycles of the pixel circuit 310 other than an emission cycle 366, such as, for example, the programming cycle 360.

- the emission control transistor 322 is selectively turned on and off according to the emission control signal conveyed via the emission control line 25. It is specifically noted that the pixel circuit 310 can be implemented without the emission control transistor 322 by selectively adjusting the voltage of the supply line 27i to increase VSS during the programming cycle 360 so as to turn off the light emitting device 314.

- FIG. 8B is a timing diagram illustrating an exemplary operation of the pixel circuit 310 shown in FIG. 8 A.

- operation of the pixel circuit 310 includes two phases for each pixel: a programming and compensation cycle 360 and an emission cycle 364.

- the programming and compensation phase 360 is a time period during which a single row of a pixel array is programmed and compensated.

- the programming and compensation of other rows of the display panel 20 can be carried out during the time period 362.

- the select line 24i is set low to turn on the switch transistor 318 and the data line 322j is set to a programming voltage VP appropriate for the "ith" row.

- the emission control line 25 is maintained at a high level to keep the emission control transistor 322 turned off. It is specifically noted that the emission control line 25 can convey an emission control signal that is shared by multiple pixels in a pixel array. For example, the emission control signal may be simultaneously conveyed to emission control lines in pixels in more than one row of the display panel 20 or to all pixels in a pixel array of a display.

- the application of the programming voltage VP to the data line 322j causes a voltage to develop at the gate node 312g approximately equal to VP - Vth. That is, during the programming and compensation cycle 360, current flows from the data line 322j through the drive transistor 312 and the switch transistor 318 (which is turned on by the select line 24i) and develop a charge at the gate node 312g. The current continues to flow until the gate-source voltage of the drive transistor 312 is roughly equal to Vth, at which point the drive transistor 312 turns off and the current ceases flowing, leaving the voltage at the gate node 312g approximately equal to VP - Vth.

- the pixel circuit 310 is configured to allow a programming voltage VP to be applied to the pixel circuit 310 through the drive transistor 312. This arrangement ensures that the voltage developed on the gate node 312g of the drive transistor 312 and stored in the storage capacitor 316 automatically compensates for the threshold voltage Vth of the drive transistor 312.

- the threshold voltage Vth of the drive transistor 312 can vary across the panel 20 and over time due to variations in the usage of each pixel (i.e., the gate-source and drain-source voltage applied to each individual drive transistor over their lifetimes), temperature variations applied to each pixel, manufacturing variations in the developing of each pixel in a pixel array, etc.

- the pixel circuit 310 further accounts for degradation in the pixel 310 by applying the biasing current Ibias via the bias line 329 to the second terminal of the storage capacitor 316 while the programming voltage VP is applied through the drive transistor 312 to the first terminal of the storage capacitor 316.

- the bias current Ibias drains a small current through the drive transistor 312 (via the switch transistor 318 and the storage capacitor 316) to allow the gate-source voltage of the drive transistor 312 to be further adjusted.

- This further adjustment due to the bias current Ibias can account for variations (e.g., shifts, non-uniformities, etc.) in the voltage-current behavior of the drive transistor 312 (e.g., due to mobility, gate oxide, etc.).

- the select line 24i is set high to turn off the switch transistor 318 and the storage capacitor 316 is thus allowed to float between the bias line 329 and the gate node 312g.

- the emission cycle 364 is commenced by setting the bias line 329 to a high supply voltage VDD, setting the data line 322j to the high supply voltage VDD, and setting the emission control line 25 low to turn on the emission control transistor 322.

- the bias line 329 thereby references the second terminal of the storage capacitor 316 to the high supply voltage VDD while the first terminal of the storage capacitor 316 sets the gate voltage of the drive transistor 312.

- FIG. 9A illustrates an additional configuration of a pixel circuit 410 configured to program the pixel circuit 410 via a programming capacitor 416 ("Cprg") connected to a gate terminal of a drive transistor 412 via a first selection transistor 417.

- the pixel circuit 410 also includes a storage capacitor 415 ("Cs") connected directly to the gate terminal of the drive transistor 412.

- the pixel circuit 410 can be implemented in the display system 50 described above in connection with FIG. 1, and can be one of a plurality of similar pixel circuits arranged in rows and columns to form a display panel, such as the display panel 20 described in connection with FIG. 1. However, as shown, the pixel circuit 410 does not utilize a separate monitoring line for providing feedback.

- the pixel circuit 410 includes both a first select line 23i ("SEL1") and a second select line 24i (“SEL2").

- the pixel circuit 410 also includes a connection to an emission control line 25i (“EM”) and two voltage supply lines 26i, 27i for supplying a current source and/or sink for a driving current conveyed through the pixel circuit 410 according to programming information.

- the pixel circuit 410 includes a first switch transistor 417 operated according to the first select line 23 i and a second switch transistor 418 operated according to the second select line 24i.

- the pixel circuit 410 also includes the drive transistor 412, an emission control transistor 422 operated according to the emission control line 25i, and a light emitting device 414, such as an organic light emitting diode.

- the drive transistor 412, emission control transistor 422, and the light emitting device 414 are connected in series such that while the emission control transistor 422 is turned on, a current conveyed through the drive transistor 412 is also conveyed through the light emitting device 414.

- the pixel circuit 410 also includes a storage capacitor 415 having a first terminal connected to a gate terminal of the drive transistor 412 at a gate node 412g. A second terminal of the storage capacitor 415 is connected to the voltage supply line 26i.

- the second switch transistor 418 is connected between the gate node 412g and a connection point between the drive transistor 412 and the emission control transistor 422.

- the programming capacitor 416 is connected in series between the data line 22j and the first switch transistor 417.

- the first switch transistor 417 is connected between a first terminal of the programming capacitor 416 and a gate terminal of the drive transistor 412, while a second terminal of the programming capacitor 416 is connected to the data line 22j.

- Certain transistors in the pixel circuit 410 provide functions similar in some respects to corresponding transistors in the pixel circuit 210.

- the drive transistor 412 directs a current from the voltage supply line 26i from a first terminal (e.g., a source terminal) to a second terminal (e.g., a drain terminal) based on the voltage applied to the gate node 412g.

- the current directed through the drive transistor 412 is conveyed through the light emitting device 414, which emits light according to the current flowing through it similar to the light emitting device 214.

- the emission control transistor 422 selectively allows current flowing through the drive transistor to be directed to the light emitting device 414, and thereby increases a contrast ratio of the display by reducing accidental emissions of the light emitting device.

- the second switch transistor 418 is operated by the second select line 24i similarly to the switch transistor 218 so as to selectively connect the second terminal of the drive transistor 412 to the gate node 412g.

- the second switch transistor provides a current path is between the voltage supply line 26i to the gate node 412g, through the drive transistor 412. While the second switch transistor 418 is turned on, the voltage on the gate node 412g can thus adjust to a voltage suitable to convey a current through the drive transistor.

- FIG. 9B is an alternative pixel circuit 410' configured similarly to the pixel circuit 410 shown in FIG. 9A, but with an additional switch transistor 419 connected in series with the second switch transistor 418. Both the additional switch transistor 419 and the second switch transistor 418 are operated according to the second select line 24i, such that setting the second select line 24i at a voltage sufficient to turn on the transistors 418, 419 connects a second terminal (e.g., a drain terminal) of the drive transistor 412 to the gate node 412g.

- a second terminal e.g., a drain terminal

- activating the second select line 24i provides a current path from the supply voltage line 26i to the gate node 412g, through the drive transistor 412, similar to the pixel circuit 410 described in connection with FIG. 9A.

- the pixel circuit 410' offers superior resistance to leakage between the gate node 412g and the second terminal of the drive transistor 412 while the second select line 24i is set to turn off the transistors 418, 419.

- the description herein of the operation and function of the pixel circuit 410 accordingly applies to the pixel circuit 410' shown in FIG. 9B.

- the pixel circuit 410 shown in FIG. 9A includes the first switch transistor 417 for selectively connecting the programming capacitor 416 to the gate node 412g. Furthermore, the pixel circuit 410 includes the storage capacitor 415 connected between the gate node 412g and the voltage supply line 26i. The first switch transistor 417 allows the gate node 412g to be isolated (e.g,. not capacitively coupled) to the data line 22j during an emission operation of the pixel circuit 410.

- the pixel circuit 410 can be operated such that the first selection transistor 417 is turned off so as to disconnect the gate node 412g from the data line 22j whenever the pixel circuit 410 is not undergoing a compensation operation or a programming operation. Additionally, during an emission operation of the pixel circuit 410, the storage capacitor 415 holds a voltage based on programming information and applies the held voltage to the gate node 412g so as to cause the drive transistor 412 to drive a current through the light emitting device 414 according to the programming information.

- the capacitor 216 is allowed to float during the programming of other rows of the display while the selection transistor 218 is turned off.

- the data line 22j is set to an appropriate reference voltage (e.g. V REF ) to reference the second terminal of the capacitor 216 connected to the data line 22j such that the voltage applied to the gate terminal of the drive transistor 212 is based on the previously applied programming voltage.

- V REF an appropriate reference voltage

- the data line 22j is assigned to the reference voltage V REF during the emission period and thus programming and/or compensation cannot be carried out on some rows while other rows are driven to emit light.

- V REF the reference voltage

- one way to address the issue and provide the ability to conduct simultaneous operations in parallel on distinct segments of the display panel 20 is by segmenting the data line 22j into groups of pixels, such as sets of rows of the display panel. By allowing each segment to be independently connected to the data line 22j, and alternately connected to the reference voltage V REF , parallel operations can be performed on separate segments of the display panel 20.

- FIG. 9A Another configuration allowing for simultaneous operations is provided by the pixel circuit 410 described in FIG. 9A (or the pixel circuit 410' of FIG. 9B), the operation of which is described next.

- the simultaneous parallel operation of different functions (i.e., compensation, programming, and driving) on different rows of the display panel 20 allow for increased duty cycles, higher display refresh rates, longer programming and/or compensation operations, and combinations thereof.

- FIG. 9C is a timing diagram describing an exemplary operation of the pixel circuit 410 of FIG. 9A or the pixel circuit 410' of FIG. 9B.

- operation of the pixel circuit 410 includes a compensation cycle 440, a program cycle 450, and an emission cycle 460 (alternately referred to herein as a driving cycle).

- the entire duration that the data line 22j is manipulated to provide compensation and programming to the pixel circuit 410 is a time row period 436 having a duration t RO w.

- the duration of t RO w can be determined based on the number of rows in the display panel 20 and the refresh rate of the display system 50.

- the row period 436 is initiated by a first delay period 432, having duration tdl .

- the first delay period 432 provides a transition time to allow the data line 22j to be reset from its previous programming voltage (for another row) and set to a reference voltage Vref suitable for commencing the compensation cycle 440.

- the duration tdl of the first delay period 432 is determined based on the response times of the transistors in the display system 50 and the number of rows in the display panel 20.

- the compensation cycle 440 is carried out during a time interval with duration tcoMP-

- the program cycle 450 is carried out during a time interval with duration tpRG.

- the emission control line 25i (“EM") is set high to turn off the emission control transistor 422.

- the compensation cycle 440 includes a reference voltage period 442 and a ramp voltage period 444, which have durations of t REF and tRAMP, respectively.

- the first and second select lines 423i, 424i are each set low at the start of the compensation cycle 440 so as turn on the first and second selection transistors 417, 418.

- the data line 22j (“DATA[j]") is set with at a reference voltage Vref, during the reference voltage period 442.

- the reference voltage period 442 accordingly sets the voltage of the second terminal of the programming capacitor 416 to Vref.

- the reference voltage period 442 is followed by the ramp voltage period 444 where the voltage data line 22j is decreased from the reference voltage Vref to a voltage Vref - V A .

- the voltage on the data line 22j is decreased by an amount given by the voltage V A -

- the ramp voltage can be a voltage that decreases at a substantially constant rate (e.g., has a substantially constant time derivative) so as to generate a substantially constant current through the programming capacitor 416.

- the programming capacitor 416 thus provides a current Iprg through the drive transistor 412, via the second switch transistor 418 and the first switch transistor 417 during the voltage ramp period 444.

- the amount of the current Iprg thus applied to the pixel circuit 410 via the programming capacitor 416 can be determined based on the amount of V A , the duration tRAMP, and the capacitance of the programming capacitor 416, which can be referred to as Cprg.