WO2009093295A1 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- WO2009093295A1 WO2009093295A1 PCT/JP2008/003898 JP2008003898W WO2009093295A1 WO 2009093295 A1 WO2009093295 A1 WO 2009093295A1 JP 2008003898 W JP2008003898 W JP 2008003898W WO 2009093295 A1 WO2009093295 A1 WO 2009093295A1

- Authority

- WO

- WIPO (PCT)

- Prior art keywords

- film

- conductive portion

- insulating film

- semiconductor device

- active region

- Prior art date

Links

- 239000004065 semiconductor Substances 0.000 title claims abstract description 188

- 238000004519 manufacturing process Methods 0.000 title claims description 51

- 238000009413 insulation Methods 0.000 claims abstract description 14

- 239000010408 film Substances 0.000 claims description 888

- 229910052751 metal Inorganic materials 0.000 claims description 321

- 239000002184 metal Substances 0.000 claims description 321

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 140

- 229910052710 silicon Inorganic materials 0.000 claims description 140

- 239000010703 silicon Substances 0.000 claims description 140

- 238000000034 method Methods 0.000 claims description 95

- 239000012535 impurity Substances 0.000 claims description 72

- 239000000758 substrate Substances 0.000 claims description 47

- 239000004020 conductor Substances 0.000 claims description 21

- 150000002736 metal compounds Chemical class 0.000 claims description 19

- 238000002955 isolation Methods 0.000 claims description 18

- 238000000059 patterning Methods 0.000 claims description 16

- 239000010409 thin film Substances 0.000 claims description 16

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 claims description 9

- 239000002131 composite material Substances 0.000 claims description 8

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 claims description 6

- 229910003468 tantalcarbide Inorganic materials 0.000 claims description 5

- GPBUGPUPKAGMDK-UHFFFAOYSA-N azanylidynemolybdenum Chemical compound [Mo]#N GPBUGPUPKAGMDK-UHFFFAOYSA-N 0.000 claims description 3

- NFFIWVVINABMKP-UHFFFAOYSA-N methylidynetantalum Chemical compound [Ta]#C NFFIWVVINABMKP-UHFFFAOYSA-N 0.000 claims description 3

- 239000000203 mixture Substances 0.000 abstract description 16

- 239000000463 material Substances 0.000 abstract description 3

- 102000004129 N-Type Calcium Channels Human genes 0.000 description 50

- 108090000699 N-Type Calcium Channels Proteins 0.000 description 50

- 108091006146 Channels Proteins 0.000 description 45

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 30

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 27

- 229920005591 polysilicon Polymers 0.000 description 26

- 229910021332 silicide Inorganic materials 0.000 description 26

- FVBUAEGBCNSCDD-UHFFFAOYSA-N silicide(4-) Chemical compound [Si-4] FVBUAEGBCNSCDD-UHFFFAOYSA-N 0.000 description 26

- 238000002513 implantation Methods 0.000 description 25

- 238000012986 modification Methods 0.000 description 11

- 230000004048 modification Effects 0.000 description 11

- 230000000694 effects Effects 0.000 description 10

- 229910005883 NiSi Inorganic materials 0.000 description 8

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 8

- 238000004151 rapid thermal annealing Methods 0.000 description 8

- 229910052814 silicon oxide Inorganic materials 0.000 description 8

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 7

- 238000005229 chemical vapour deposition Methods 0.000 description 7

- 238000007796 conventional method Methods 0.000 description 7

- 230000007423 decrease Effects 0.000 description 7

- 238000001312 dry etching Methods 0.000 description 7

- 239000000969 carrier Substances 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- 238000005530 etching Methods 0.000 description 5

- 239000010410 layer Substances 0.000 description 5

- 238000000206 photolithography Methods 0.000 description 5

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- MHAJPDPJQMAIIY-UHFFFAOYSA-N Hydrogen peroxide Chemical compound OO MHAJPDPJQMAIIY-UHFFFAOYSA-N 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 229910052759 nickel Inorganic materials 0.000 description 3

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 150000002739 metals Chemical class 0.000 description 2

- 239000011259 mixed solution Substances 0.000 description 2

- 229910021334 nickel silicide Inorganic materials 0.000 description 2

- RUFLMLWJRZAWLJ-UHFFFAOYSA-N nickel silicide Chemical compound [Ni]=[Si]=[Ni] RUFLMLWJRZAWLJ-UHFFFAOYSA-N 0.000 description 2

- 239000012299 nitrogen atmosphere Substances 0.000 description 2

- 238000005192 partition Methods 0.000 description 2

- 229910052698 phosphorus Inorganic materials 0.000 description 2

- 239000011574 phosphorus Substances 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 239000000243 solution Substances 0.000 description 2

- 238000004544 sputter deposition Methods 0.000 description 2

- 229910010413 TiO 2 Inorganic materials 0.000 description 1

- -1 ZrO 2 Chemical class 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 150000004767 nitrides Chemical class 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 125000006850 spacer group Chemical group 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 230000005641 tunneling Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823437—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes

- H01L21/82345—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate conductors, e.g. particular materials, shapes gate conductors with different gate conductor materials or different gate conductor implants, e.g. dual gate structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1025—Channel region of field-effect devices

- H01L29/1029—Channel region of field-effect devices of field-effect transistors

- H01L29/1033—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure

- H01L29/105—Channel region of field-effect devices of field-effect transistors with insulated gate, e.g. characterised by the length, the width, the geometric contour or the doping structure with vertical doping variation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/43—Electrodes ; Multistep manufacturing processes therefor characterised by the materials of which they are formed

- H01L29/49—Metal-insulator-semiconductor electrodes, e.g. gates of MOSFET

- H01L29/51—Insulating materials associated therewith

- H01L29/517—Insulating materials associated therewith the insulating material comprising a metallic compound, e.g. metal oxide, metal silicate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S257/00—Active solid-state devices, e.g. transistors, solid-state diodes

- Y10S257/901—MOSFET substrate bias

Definitions

- the present invention relates to a semiconductor device and a method for manufacturing the same, and more particularly, to a semiconductor device including Multi-Vt type MISFETs (Metal, Insulator, Semiconductor, Field, Effect, Transistor) having different threshold voltages, and a method for manufacturing the same.

- Multi-Vt type MISFETs Metal, Insulator, Semiconductor, Field, Effect, Transistor

- MISFETs having the same conductivity type and different threshold voltages (hereinafter referred to as “MIS transistors”) are mounted together.

- a -Vt process is commonly used.

- the gate insulating film of the MIS transistor is being made thinner.

- a silicon oxide film is used as the gate insulating film, there is a problem that when the gate insulating film is thinned to a certain level or less, leakage due to direct tunneling increases dramatically and the current consumption of the chip increases. .

- a high dielectric constant insulating film such as HfO 2 or HfSiON having a dielectric constant three times or more that of the silicon oxide film instead of the silicon oxide film as the gate insulating film.

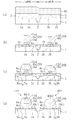

- FIGS. 10 (a) to 10 (d) are cross-sectional views of relevant steps showing a conventional method of manufacturing a semiconductor device in the order of steps.

- the Lvt region is a region where a P-type MIS transistor having a relatively low threshold voltage is formed

- the Hvt region is a region where a P-type MIS transistor having a relatively high threshold voltage is formed.

- an element isolation region 102 is formed on the silicon substrate 101.

- the region located in the Lvt region becomes the active region 101a in the Lvt region

- the region located in the Hvt region becomes the active region 101b in the Hvt region.

- an n-type channel region 103a having a first impurity concentration is formed above the active region 101a of the Lvt region, while a second impurity having a higher concentration than the first impurity concentration is formed above the active region 101b of the Hvt region.

- An n-type channel region 103b having an impurity concentration is formed.

- a high dielectric constant insulating film 104 and a metal film 105 are sequentially formed on the silicon substrate 101.

- a polysilicon film 111 is formed on the metal film 105.

- the Lvt region polysilicon film 111, the metal film 105, and the high dielectric constant insulating film 104 are sequentially patterned to form a high dielectric constant on the active region 101a in the Lvt region.

- a gate insulating film 104a made of an insulating film 104 and a gate electrode 120A made of a metal film 105a and a polysilicon film 111a are sequentially formed, and the polysilicon film 111, the metal film 105, and the high dielectric constant insulating film 104 in the Hvt region are formed.

- the gate insulating film 104b made of the high dielectric constant insulating film 104 and the gate electrode 120B made of the metal film 105b and the polysilicon film 111b are sequentially formed on the active region 101b in the Hvt region. Thereafter, a shallow p-type source / drain region 107a is formed in the active region 101a, and a shallow p-type source / drain region 107b is formed in the active region 101b.

- sidewalls 108a are formed on the side surfaces of the gate electrode 120A, and sidewalls 108b are formed on the side surfaces of the gate electrode 120B.

- a deep p-type source / drain region 109a is formed in the active region 101a

- a deep p-type source / drain region 109b is formed in the active region 101b.

- silicide films 110a1 and 110b1 are formed on the deep p-type source / drain regions 109a and 109

- silicide films 110a2 and 110b2 are formed on the polysilicon films 111a and 111b in the gate electrodes 120A and 120B.

- the impurity concentration of the channel region (see FIG. 10 (d): 103b) in the high threshold voltage MIS transistor is set to the channel region in the low threshold voltage MIS transistor. It is necessary to adjust it higher than the impurity concentration (see FIG. 10 (d): 103a). Thereby, the threshold voltage of the high threshold voltage system MIS transistor is controlled to be higher than the threshold voltage of the low threshold voltage system MIS transistor.

- the impurity concentration of the channel region in the high threshold voltage MIS transistor is relatively high, when the semiconductor device operates, the carriers collide with the conductive impurities contained in the channel region and scatter, resulting in a high threshold voltage.

- the MIS transistor there is a problem that the carrier mobility is reduced and the driving force is reduced.

- the impurity concentration of the channel region of the Lvt region and the channel region of the Hvt region can be uniformly reduced.

- the impurity concentration of the channel region of the Hvt region is set to the channel of the Lvt region.

- the method of adjusting the impurity concentration of the channel region is adopted as a method for controlling the threshold voltages of the MIS transistors having the same conductivity type, the driving capability of the high threshold voltage MIS transistor is lowered. The performance of the threshold voltage MIS transistor cannot be improved.

- the method of adjusting the Hf concentration of the gate insulating film it is very difficult to control the threshold voltage of the low and high threshold voltage MIS transistors. It cannot be realized with high accuracy. That is, no matter which method is used, MIS transistors having different threshold voltages cannot be realized with high accuracy and high performance.

- an object of the present invention is to realize MIS transistors having different threshold voltages with high accuracy and high performance in a semiconductor device including MIS transistors having the same conductivity type.

- a first semiconductor device includes a first MIS transistor and a second MIS transistor having a threshold voltage higher than that of the first MIS transistor.

- the first MIS transistor includes a first channel region formed in the first active region in the semiconductor substrate and a high dielectric constant insulation formed on the first channel region in the first active region.

- a first gate insulating film made of a film; a first conductive portion provided on and in contact with the first gate insulating film; and a second conductive portion formed on the first conductive portion.

- a second MIS transistor formed in a second active region of the semiconductor substrate, having a second channel region having the same conductivity type as the first channel region, and a second active region

- a second gate insulating film made of a high dielectric constant insulating film formed on the second channel region; a third conductive portion provided in contact with the second gate insulating film; and a third conductive portion

- a second gate electrode having a fourth conductive portion formed thereon, the third conductive portion being thinner than the first conductive portion and the same as the first conductive portion It consists of a composition material.

- the film thickness of the third conductive portion on which the fourth conductive portion is formed is the thickness of the first conductive portion on which the second conductive portion is formed.

- the threshold voltage of the second MIS transistor having the second gate electrode made up of the third conductive portion and the fourth conductive portion is reduced between the first conductive portion and the second conductive portion. It is controlled to be higher than the threshold voltage of the first MIS transistor having the first gate electrode formed of the conductive portion.

- the impurity concentration of the second channel region is not necessary to make the impurity concentration of the second channel region sufficiently higher than the impurity concentration of the first channel region as in the prior art, and the impurity concentration of the second channel region is reduced to that of the first channel region.

- the impurity concentration can be the same (or only slightly higher than the impurity concentration of the first channel region). Therefore, during operation of the semiconductor device, carriers can be prevented from colliding with the conductive impurities contained in the second channel region and scattered, so that in the second MIS transistor, leakage current can be reduced, and Thus, a high driving force can be achieved.

- the first and second MIS transistors are used instead of the conventional method of adjusting the Hf concentration of the gate insulating film constituting the MIS transistor. Since the method of adjusting the film thickness of the first and third conductive portions provided in contact with the first and second gate insulating films is adopted, the threshold value of the first and second MIS transistors is adopted. The voltage can be controlled easily and with high accuracy.

- the semiconductor device including the first and second MIS transistors having the same conductivity type the first and second MIS transistors having different threshold voltages can be improved in performance.

- the first conductive portion and the third conductive portion are made of metal or a metal compound, and the second conductive portion and the fourth conductive portion are made of silicon. .

- the second MIS transistor having the second gate insulating film and the second gate electrode is the first MIS having the first gate insulating film and the first gate electrode. It is preferable to have an effective work function close to that of silicon compared to a transistor.

- the first MIS transistor and the second MIS transistor are P-type MIS transistors, and the first conductive portion and the third conductive portion are 4.7 eV or more and 5 It is preferable to have a work function of .15 eV or less.

- the first MIS transistor and the second MIS transistor are P-type MIS transistors, and the first conductive portion and the third conductive portion are a titanium nitride film and a tantalum nitride.

- a film or a tantalum carbide film is preferable.

- the first MIS transistor and the second MIS transistor are P-type MIS transistors, and the first conductive portion and the third conductive portion are made of a titanium nitride film,

- the film thickness of the first conductive part is preferably 20 nm or more, and the film thickness of the third conductive part is preferably 15 nm or less.

- the first MIS transistor and the second MIS transistor are N-type MIS transistors, and the first conductive portion and the third conductive portion are 4.05 eV or more and 4 It preferably has a work function of .5 eV or less.

- the second channel region preferably has the same impurity concentration as the first channel region.

- the second gate insulating film has the same thickness as the first gate insulating film, and the fourth conductive portion has the same thickness as the second conductive portion. It is preferable to have.

- the thickness of the first gate electrode is preferably larger than the thickness of the second gate electrode.

- a second semiconductor device includes a first MIS transistor and a second MIS transistor having a threshold voltage higher than that of the first MIS transistor.

- the first MIS transistor includes a first channel region formed in the first active region in the semiconductor substrate and a high dielectric constant insulation formed on the first channel region in the first active region.

- the first conductive portion and the second conductive portion are made of materials having different compositions, so that the second gate electrode having the second conductive portion is provided.

- the threshold voltage of the second MIS transistor is controlled to be higher than the threshold voltage of the first MIS transistor including the first gate electrode having the first conductive portion.

- the impurity concentration of the second channel region is not necessary to make the impurity concentration of the second channel region sufficiently higher than the impurity concentration of the first channel region as in the prior art, and the impurity concentration of the second channel region is reduced to that of the first channel region.

- the impurity concentration can be the same (or only slightly higher than the impurity concentration of the first channel region). Therefore, during operation of the semiconductor device, carriers can be prevented from colliding with the conductive impurities contained in the second channel region and scattered, so that in the second MIS transistor, leakage current can be reduced, and Thus, a high driving force can be achieved.

- the first and second MIS transistors are used instead of the conventional method of adjusting the Hf concentration of the gate insulating film constituting the MIS transistor. Since the method of adjusting the conductive material of the first and second conductive portions provided in contact with the first and second gate insulating films is adopted, the threshold value of the first and second MIS transistors is adopted. The voltage can be controlled easily and with high accuracy.

- the semiconductor device including the first and second MIS transistors having the same conductivity type the first and second MIS transistors having different threshold voltages can be improved in performance.

- the second conductive portion has a work function closer to the silicon midgap work function than the first conductive portion.

- the first gate electrode is composed only of the first conductive portion

- the second gate electrode is composed only of the second conductive portion

- the first gate electrode has a third conductive portion formed on the first conductive portion, and the second gate electrode is on the second conductive portion. It is preferable to have the 4th electroconductive part formed in this.

- the first gate electrode is a fifth conductive portion made of the same conductive material as the second conductive portion between the first conductive portion and the third conductive portion. It is preferable to have.

- the second gate electrode includes a fifth conductive portion made of the same conductive material as the first conductive portion between the second conductive portion and the fourth conductive portion. It is preferable to have.

- the third conductive portion and the fourth conductive portion are made of silicon.

- the first conductive portion is made of the first metal or the first metal compound

- the second conductive portion is made of the second metal or the second metal compound. It is preferable.

- the first MIS transistor and the second MIS transistor are P-type MIS transistors

- the first conductive portion is a titanium nitride film

- the second conductive portion is A molybdenum nitride film or a tantalum nitride film is preferable.

- the second channel region preferably has the same impurity concentration as the first channel region.

- a first method of manufacturing a semiconductor device includes a first MIS transistor having a first gate electrode and a first threshold voltage higher than that of the first MIS transistor.

- a second gate insulating film made of a high dielectric constant insulating film on the second active region and forming a third conductive portion provided in contact with the second gate insulating film; And (d) forming a second gate electrode having a fourth conductive portion provided on the third conductive portion, wherein the third conductive portion is thinner than the first conductive portion. It has a film thickness and is made of the same composition material as that of the first conductive portion.

- the film thickness of the third conductive portion on which the fourth conductive portion is formed is the thickness of the third conductive portion on which the fourth conductive portion is formed.

- the effective work function of the second MIS transistor having the second gate electrode composed of the third conductive portion and the fourth conductive portion is changed to the first conductive portion.

- the effective work function of the second MIS transistor is changed to be closer to the mid gap than the effective work function of the first MIS transistor having the first gate electrode composed of the first and second conductive portions.

- the effective work function can be made closer to the “midgap work function of silicon”.

- the step (d) includes a step (d1) of forming a first metal film in contact with the high dielectric constant insulating film on the first active region, and a step ( a step (d2) of forming a first metal film and a second metal film in contact with the high dielectric constant insulating film on the second active region after d1), and a second metal after (d2)

- a silicon film, a second metal film, a first metal film, and a high dielectric constant insulating film on the first active region are formed.

- Patterning is performed to form a first gate insulating film made of a high dielectric constant insulating film, a first conductive part made of a first metal film and a second metal film, and a second conductive part made of a silicon film. And patterning the silicon film, the second metal film, and the high dielectric constant insulating film on the second active region.

- the step (d) includes a step (d1) of forming a metal film in contact with the high dielectric constant insulating film, and a second active region after the step (d1). Etching the upper portion of the upper metal film to form a metal thin film portion having a thickness smaller than that of the metal film, and after the step (d2), a silicon film is formed on the metal film and the metal thin film portion. After the forming step (d3) and the step (d3), the silicon gate, the metal film, and the high dielectric constant insulating film on the first active region are patterned to form a first gate made of the high dielectric constant insulating film.

- the insulating film, the first conductive portion made of a metal film, and the second conductive portion made of a silicon film are formed, and the silicon film, the metal thin film portion, and the high dielectric constant insulating film on the second active region are patterned.

- a second method of manufacturing a semiconductor device includes a first MIS transistor having a first gate electrode and a first threshold voltage higher than that of the first MIS transistor.

- first gate electrode having a first conductive portion provided on and in contact with the first gate insulating film, and forming a high dielectric constant insulating material on the second active region

- second gate insulating film made of a film

- second gate electrode having a second conductive portion provided in contact with the second gate insulating film (d).

- the second conductive portion is made of a composition material different from that of the first conductive portion.

- the first conductive portion and the second conductive portion are made of materials having different compositions, so that the work function of the second conductive portion is reduced to the first.

- the effective work function of the second MIS transistor having the second gate electrode having the second conductive portion is set to a work function close to the “silicon midgap work function” compared to the work function of the conductive portion of Compared to the effective work function of the first MIS transistor including the first gate electrode having the first conductive portion, the effective work function can be made closer to the “silicon mid-gap work function”.

- the step (d) includes a step (d1) of forming a first metal film in contact with the high dielectric constant insulating film on the first active region, and a second step. Forming a second metal film in contact with the high dielectric constant insulating film on the active region of the first active film after the step (d2) and the steps (d1) and (d2) And patterning the high dielectric constant insulating film to form a first gate insulating film made of the high dielectric constant insulating film and a first conductive portion made of the first metal film, and on the second active region Patterning the second metal film and the high dielectric constant insulating film to form a second gate insulating film made of the high dielectric constant insulating film and a second conductive part made of the second metal film ( d3).

- the step (d) includes a step (d1) of forming a first metal film in contact with the high dielectric constant insulating film on the first active region, and a second step. After the step (d2) of forming a second metal film in contact with the high dielectric constant insulating film on the active region, and after the steps (d1) and (d2), the first metal film and the second metal film After the step (d3) of forming a silicon film thereon and the step (d3), the silicon film, the first metal film, and the high dielectric constant insulating film on the first active region are patterned to obtain a high dielectric constant.

- Over gate insulating film preferably includes the second conductive portion made of the second metal film, and a step (d4) forming a fourth conductive portion made of a silicon film.

- the step (d) includes a step (d1) of forming a first metal film in contact with the high dielectric constant insulating film on the first active region, and a step ( After d1), a step (d2) of forming a first metal film and a second metal film in contact with the high dielectric constant insulating film on the second active region, and after the step (d2), the second metal film is formed.

- Forming a silicon film on the metal film (d3), and after the step (d3), the silicon film on the first active region, the second metal film, the first metal film, and the high dielectric constant insulating film The first gate insulating film made of a high dielectric constant insulating film, the first conductive part made of the first metal film, the fifth conductive part made of the second metal film, and the silicon film Forming a third conductive portion, a silicon film on the second active region, a second metal film, and a high dielectric constant isolation; Patterning the film to form a second gate insulating film made of a high dielectric constant insulating film, a second conductive part made of a second metal film, and a fourth conductive part made of a silicon film (d4) are preferably included.

- the film thickness of the conductive portion (or the conductive portion of the conductive portion) provided in contact with the first and second gate insulating films constituting the first and second MIS transistors By adjusting the conductive material, the effective work function of the second MIS transistor is controlled to be higher than the effective work function of the first MIS transistor. Therefore, in the semiconductor device having the first and second MIS transistors having the same conductivity type, the first and second MIS transistors having different threshold voltages can be realized with high accuracy and high performance.

- FIGS. 1A to 1D are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to the first embodiment of the present invention in the order of steps.

- 2 (a) to 2 (d) are cross-sectional views of relevant steps showing the semiconductor device manufacturing method according to the first embodiment of the present invention in the order of steps.

- FIGS. 3A to 3D are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to the second embodiment of the present invention in the order of steps.

- FIGS. 4A to 4D are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to the second embodiment of the present invention in the order of steps.

- FIGS. 1A to 1D are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to the first embodiment of the present invention in the order of steps.

- 2 (a) to 2 (d) are cross-sectional views of relevant steps showing the semiconductor device manufacturing method according to the first embodiment of the present invention in the order of

- FIGS. 5A to 5D are cross-sectional views of relevant parts showing a method of manufacturing a semiconductor device according to the third embodiment of the present invention in the order of steps.

- FIG. 6 is a diagram showing the relationship between the effective work function of the P-type MIS transistor and the thickness of the TiN film.

- FIGS. 7A to 7D are cross-sectional views of relevant parts showing a method of manufacturing a semiconductor device according to the fourth embodiment of the present invention in the order of steps.

- FIGS. 8A to 8D are cross-sectional views of relevant steps showing a semiconductor device manufacturing method according to the fourth embodiment of the present invention in the order of steps.

- 9A to 9D are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to a modification of the fourth embodiment of the present invention in the order of steps.

- 10 (a) to 10 (d) are cross-sectional views of relevant steps showing a conventional method of manufacturing a semiconductor device in the order of steps.

- the word “midgap work function of silicon” means an intermediate value of the bandgap energy of silicon. For example, it is an intermediate value between the work function (about 4.05 eV) of silicon doped with negative charge (N-type silicon) and the work function (about 5.15 eV) of silicon doped with positive charge (P-type silicon). It means about 4.6 eV.

- band edge means the end value of the band gap energy of silicon.

- N-type MIS transistor it means about 4.05 eV which is the work function of silicon doped with negative charge (N-type silicon), and in the case of a P-type MIS transistor, silicon doped with positive charge. It means about 5.15 eV which is the work function of (P-type silicon).

- the terms “near the gap” and “near the band edge” mean that in the case of an N-type MIS transistor, for example, a first work function (or effective work function) of 4.3 eV and a second work function of 4.5 eV. (Or effective work function), the first work function (or effective work function) is “near the band edge” and the second work function (or effective work function) is “middle gap”. means.

- the first work function is compared with the second work function (or effective work function) of 4.9 eV

- the first work function is compared. This means that the function (or effective work function) is “close to the mid gap” and the second work function (or effective work function) is “close to the band edge”.

- a work function (or effective work function) close to the silicon mid gap work function (that is, about 4.6 eV as shown in the above 1) is “mid gap”.

- the work function (or effective work function) close to the band edge ie, N-type MIS transistor: about 4.05 eV, P-type MIS transistor: about 5.15 eV) as shown in the above 2) is “band”. It means “close to the edge”.

- work function means a physical property value indicating a difference between a vacuum level and an energy level of a metal (or metal compound).

- the term “effective work function” means a work function that effectively acts to determine the threshold voltage of the MIS transistor.

- the “effective work function” of the MIS transistor differs from the physical work function of the metal (or metal compound) constituting the MIS transistor due to various factors in the MIS transistor.

- FIGS. 1A to 1D and FIGS. 2A to 2D are cross-sectional views of relevant parts showing a method of manufacturing a semiconductor device according to the first embodiment of the present invention in order of steps.

- the Lvt region is a region where a P-type MIS transistor having a relatively low threshold voltage (hereinafter referred to as “low threshold transistor”) is formed, and the Hvt region has a relatively high threshold voltage.

- low threshold transistor a P-type MIS transistor having a relatively low threshold voltage

- high threshold transistor a P-type MIS transistor

- a one-conductivity type substrate having a semiconductor region such as a silicon region hereinafter referred to as “semiconductor substrate”.

- An element isolation region 2 in which an insulating film is buried in a trench is selectively formed on the upper portion of 1.

- an n-type well and an n-type punch-through stopper are formed by ion-implanting n-type impurities into the semiconductor substrate 1.

- the n-type well implantation conditions are such that the implanted ion species is P (phosphorus), the implantation energy is 400 keV, the implantation dose amount is 1 ⁇ 10 13 cm ⁇ 2 , and the n-type punch-through stopper implantation condition is The implanted ion species is P (phosphorus), the implantation energy is 200 keV, and the implantation dose is 1 ⁇ 10 13 cm ⁇ 2 .

- an n-type impurity is ion-implanted into the semiconductor substrate 1 to form an n-type channel region 3a above the first active region 1a and an n-type channel region above the second active region 1b.

- 3b is formed.

- the implantation conditions of the n-type channel regions 3a and 3b are as follows: the implanted ion species is As (arsenic), the implantation energy is 100 keV, the implantation dose is 2 ⁇ 10 12 cm ⁇ 2 , and the n-type channel region 3a The n-type channel region 3b is formed with substantially the same impurity concentration profile.

- a buffer insulating film (not shown) made of, for example, a silicon oxide film having a thickness of 0.5 nm on the semiconductor substrate 1, for example, a film is formed on the buffer insulating film.

- the buffer insulating film is formed between the semiconductor substrate 1 and the high dielectric constant insulating film 4.

- the “high dielectric constant insulating film 4” appearing in the following description is the buffer insulating film on the lower surface. A formed film.

- the first metal film 5 has a work function (eg, 4.9 eV) of 4.70 eV or more and 5.15 eV or less, and a second metal film described later (FIG. 1 (c): 6

- a film made of a metal or a metal compound having a work function closer to the band edge than the work function of (see) is desirable.

- a resist pattern (not shown) that covers the Lvt region and opens the Hvt region is formed on the first metal film 5, and then the resist pattern is used as a mask.

- the first metal film 5 in the Hvt region is etched to remove the first metal film 5 on the second active region 1b, and then the resist pattern is removed. Thereby, the first metal film 5 can be selectively left on the first active region 1a. In this way, the first metal film 5 in contact with the high dielectric constant insulating film 4 on the first active region 1a is formed.

- a second metal film 6 made of, for example, a 100 nm-thick molybdenum nitride film (MoN film) is deposited on the entire surface of the semiconductor substrate 1 by, eg, CVD.

- the second metal film 6 has a work function (for example, 4.7 eV) of 4.6 eV or more and 5.05 eV or less, and is closer to the mid gap than the work function of the first metal film 5.

- a film made of a metal or metal compound having a work function is desirable.

- a tantalum nitride film (TaN film) may be used instead of the MoN film.

- the second metal film 6 is polished and removed by, for example, a chemical mechanical polishing (CMP) method until the upper surface of the first metal film 5 is exposed. A region of the second metal film 6 located above the upper surface of the first metal film 5 is removed. As a result, the second metal film 6 remains on the second active region 1b. Then, the upper surface of the second metal film 6 is planarized so that its height is the same as the upper surface height of the first metal film 5. In other words, the first metal film 5 and the second metal film 6 are formed with substantially the same film thickness. In this way, the second metal film 6 in contact with the high dielectric constant insulating film 4 on the second active region 1b is formed.

- CMP chemical mechanical polishing

- a resist pattern (not shown) having a gate pattern shape is formed on the first metal film 5 and the second metal film 6 by, for example, photolithography.

- the first metal film 5 and the high dielectric constant insulating film 4 in the Lvt region are sequentially patterned by dry etching using the resist pattern as a mask, and the high dielectric constant insulating film is formed on the first active region 1a.

- the first gate insulating film 4a made of 4 and the first conductive portion 5a made of the first metal film 5 are sequentially formed.

- the second metal film 6 and the high dielectric constant insulating film 4 in the Hvt region are sequentially patterned, and the second gate insulating film 4b made of the high dielectric constant insulating film 4 is formed on the second active region 1b.

- the 2nd electroconductive part 6b which consists of a 2nd metal film 6 is formed in order.

- 20A is formed in sequence, and a second gate insulating film 4b and a second conductive portion 6b provided on and in contact with the second gate insulating film 4b are provided on the second active region 1b.

- Gate electrodes 20B are sequentially formed.

- p-type impurities are ion-implanted into the first active region 1a using the first gate electrode 20A as a mask, and the second gate electrode is introduced into the second active region 1b.

- a p-type source / drain region (LDD region or extension) having a relatively shallow junction depth is formed laterally below the first gate electrode 20A in the first active region 1a.

- Region) 7a is formed in a self-aligned manner, and a p-type source / drain region (LDD region or extension region) 7b having a relatively shallow junction depth below the side of the second gate electrode 20B in the second active region 1b.

- the implantation conditions for the shallow p-type source / drain regions 7a and 7b are that the implanted ion species is B (boron), the implantation energy is 0.5 keV, and the implantation dose is 5 ⁇ 10 14 cm ⁇ 2 .

- the sidewall 8a is formed on the side surface of the first gate electrode 20A, and the sidewall 8b is formed on the side surface of the second gate electrode 20B.

- p-type impurities are ion-implanted into the first active region 1a using the first gate electrode 20A and the sidewall 8a as a mask, and the second active region 1b.

- a p-type impurity is ion-implanted using the second gate electrode 20B and the sidewall 8b as a mask.

- a spike RTA (Rapid Thermal Annealing) process is performed on the semiconductor substrate 1 at 1050 ° C., for example, and a shallow p-type source / drain region 7a is bonded to the outside of the sidewall 8a in the first active region 1a.

- a p-type source / drain region 9a having a junction depth deeper than the depth and having a relatively deep junction depth is formed in a self-aligned manner, and is shallow on the outer side of the sidewall 8b in the second active region 1b.

- a p-type source / drain region 9b having a junction depth deeper than that of the p-type source / drain region 7b and having a relatively deep junction depth is formed in a self-aligned manner.

- the implantation conditions for the deep p-type source / drain regions 9a and 9b are that the implanted ion species is B (boron), the implantation energy is 2.0 keV, and the implantation dose is 3 ⁇ 10 15 cm ⁇ 2 .

- a silicide metal film (not shown) made of a nickel film (Ni film) having a thickness of 10 nm, for example, is deposited on the entire surface of the semiconductor substrate 1 by sputtering.

- the first RTA treatment is performed on the semiconductor substrate 1 in, for example, a nitrogen atmosphere at 320 ° C. to react each silicon in the deep p-type source / drain regions 9a and 9b with nickel of the metal film for silicide.

- the semiconductor substrate 1 is immersed in an etching solution composed of a mixed solution of sulfuric acid and hydrogen peroxide solution, whereby the element isolation region 2, the first conductive portion 5a in the first gate electrode 20A, and the second gate.

- the unreacted silicide metal film remaining on the second conductive portion 6b and the side walls 8a and 8b in the electrode 20B is removed.

- the second RTA process is performed on the semiconductor substrate 1 at a temperature (for example, 550 ° C.) higher than the temperature in the first RTA process.

- a silicide film 10a1 made of a nickel silicide film (NiSi film) is formed on the deep p-type source / drain region 9a in the Lvt region, and a nickel silicide film (on the upper side of the deep p-type source / drain region 9b in the Hvt region).

- a silicide film 10b1 made of a NiSi film is formed.

- the semiconductor device according to the present embodiment that is, the low threshold transistor LTr having the first gate electrode 20A composed of the first conductive portion 5a having the work function close to the band edge, and the first conductive A semiconductor device including the high threshold transistor HTr having the second gate electrode 20B made of the second conductive portion 6b having a composition different from that of the portion 5a and having a work function close to the midgap can be manufactured.

- an element isolation region 2 in which an insulating film is embedded in a trench is formed so as to partition the first active region 1a and the second active region 1b.

- the semiconductor device includes a low threshold transistor LTr provided in the first active region 1a and a high threshold transistor MTr provided in the second active region 1b.

- the low threshold transistor LTr includes an n-type channel region 3a formed in the first active region 1a, a first gate insulating film 4a made of a high dielectric constant insulating film formed on the n-type channel region 3a, A first gate electrode 20A formed of a first conductive portion 5a provided in contact with the first gate insulating film 4a; a sidewall 8a formed on a side surface of the first gate electrode 20A; A shallow p-type source / drain region 7a formed under the first gate electrode 20A in the active region 1a and a deep p-type source / drain formed under the sidewall 8a in the first active region 1a. A region 9a and a silicide film 10a1 formed on the deep p-type source / drain region 9a are provided.

- the high threshold transistor HTr includes an n-type channel region 3b formed in the second active region 1b and a second gate insulating film 4b made of a high dielectric constant insulating film formed on the n-type channel region 3b.

- a second gate electrode 20B comprising a second conductive portion 6b provided in contact with the second gate insulating film 4b, a sidewall 8b formed on the side surface of the second gate electrode 20B, A shallow p-type source / drain region 7b formed laterally below the second gate electrode 20B in the second active region 1b, and a deep p-type formed laterally below the sidewall 8b in the second active region 1b.

- a source / drain region 9b and a silicide film 10b1 formed on the deep p-type source / drain region 9b are provided.

- the first conductive portion 5a constituting the first gate electrode 20A of the low threshold transistor LTr is made of a TiN film and has a work function (for example, 4.9 eV) closer to the band edge.

- the second conductive portion 6b constituting the second gate electrode 20B of the high threshold transistor HTr is made of a MoN film and has a work function (for example, 4.7 eV) close to the mid gap.

- the first conductive portion 5a and the second conductive portion 6b are made of metal films having different compositions.

- the first conductive portion 5a has a work function closer to the “band edge (about 5.15 eV, see 2 above)” than the second conductive portion 6b.

- the second conductive portion 6b has a work function that is closer to the “midgap work function of silicon (about 4.6 eV, see 1) above” than the first conductive portion 5a. That is, the second conductive portion 6b has a work function lower than that of the first conductive portion 5a.

- the first gate insulating film 4a in contact with the first conductive portion 5a and the second gate insulating film 4b in contact with the second conductive portion 6b are formed in the same process and in the same structure. It consists of high dielectric constant insulating films having the same film thickness.

- n-type channel region 3a in the Lvt region and the n-type channel region 3b in the Hvt region are formed in the same process and in the same structure, and have the same impurity concentration. Note that “same film thickness” and “same impurity concentration” appearing in this specification mean that variations in manufacturing that occur in the same process are included.

- the shallow p-type source / drain regions 7a and 7b, the deep p-type source / drain regions 9a and 9b, and the sidewalls 8a and 8b are also formed in the same process and the same structure. However, if there is a difference in height between the first and second gate electrodes 20A and 20B, the side wall 8a formed on the side surface of the first gate electrode 20A and the side surface of the second gate electrode 20B will be described.

- the side wall 8b to be formed may be formed at different heights.

- the first conductive portion 5a and the second conductive portion 6b are made of metal films having different compositions, so that the work function of the second conductive portion 6b can be changed to that of the first conductive portion 5a.

- the effective work function of the high-threshold transistor HTr having the second gate electrode 20B formed of the second conductive portion 6b is set to a work function closer to the “silicon mid-gap work function” than the work function.

- the effective work function of the low threshold transistor LTr having the first gate electrode 20A formed of the portion 5a can be made lower. That is, the threshold voltage of the high threshold transistor MTr can be made higher than the threshold voltage of the low threshold transistor LTr.

- the impurity concentration of the n-type channel region (see FIG. 10 (d): 103b) in the Hvt region is set to be higher than the impurity concentration of the n-type channel region (see FIG. 10 (d): 103a) in the Lvt region.

- the impurity concentration of the n-type channel region 3b can be made the same as the impurity concentration of the n-type channel region 3a. Therefore, it is possible to suppress the carriers from colliding with the n-type impurity contained in the n-type channel region 3b and scattering during the operation of the semiconductor device, thereby reducing the leakage current in the high threshold transistor HTr, and High driving force can be achieved.

- the method for adjusting the Hf concentration of the gate insulating film constituting the low and high threshold transistors as in the conventional method is not used.

- the threshold voltage of the low and high threshold transistors can be easily and accurately controlled.

- MIS transistors having different threshold voltages can be realized with high accuracy and high performance.

- the first and second metal films 5 and 6 constituting the first and second conductive portions 5a and 6b having different work functions are used as the first and second metals having different compositions.

- the films 5 and 6 for example, the first metal film 5: TiN film and the second metal film 6: MoN film

- the present invention is not limited to this. .

- the first and second metal films constituting the first and second conductive parts even when the first and second metal films having different formation methods are used, even if the compositions are the same, Alternatively, even when the first and second metal films having the same composition and the same formation method are used, the first and second conductive parts having different work functions are realized. be able to.

- the n-type channel region 3a in the Lvt region and the n-type channel region 3b in the Hvt region are formed in the same process as shown in FIG.

- the present invention is not limited to this.

- n-type channel regions having slightly different impurity concentrations may be formed.

- the first and second gate electrodes including the first and second conductive portions having different work functions are used.

- n-type channel regions having slightly different impurity concentrations may be used.

- the impurity concentration of the n-type channel region of the Hvt region only needs to be slightly higher than the impurity concentration of the n-type channel region of the Lvt region. It is only necessary to provide a very small impurity concentration difference between the n-type channel region and the n-type channel region of the Hvt region. Therefore, a large impurity concentration difference is caused between the n-type channel region of the Lvt region (see FIG.

- the second activity is formed as shown in FIG. 1D.

- the present invention is not limited to this.

- the first metal film may be formed on the first active region.

- the second metal film 6 is formed by CMP as shown in FIG. 1D.

- the metal film 6 is removed by polishing, and then, as shown in FIG. 2A, the first metal film 5 and the second metal film 6 are patterned to form the first conductive film made of the first metal film 5.

- the case of forming the first gate electrode 20A having only the portion 5a and the second gate electrode 20B having only the second conductive portion 6b made of the second metal film 6 has been described as a specific example. However, the present invention is not limited to this. For example, similarly to the step shown in FIG.

- the first metal film and the second metal film are not polished and removed by CMP. Patterning the second metal film to form a first gate electrode having a conductive portion made of the first metal film and a conductive portion made of the second metal film formed on the conductive portion; A second gate electrode having only a conductive portion made of the metal film may be formed.

- FIGS. 4 (a) to (d) are cross-sectional views of relevant steps showing a method of manufacturing a semiconductor device according to the second embodiment of the present invention in the order of steps.

- FIG. 3 (a) to FIG. 4 (d) the same constituent elements as those of the first embodiment are denoted by the reference numerals shown in FIG. 1 (a) to FIG.

- the Lvt region is a region where a low threshold transistor is formed

- the Hvt region is a region where a high threshold transistor is formed.

- the first metal film 5 made of a 100 nm-thick TiN film in the first embodiment instead of the first metal film 5 made of a 100 nm-thick TiN film in the first embodiment, as shown in FIG. 3A, the first metal film made of a 20-nm thick TiN film is used. 1 metal film 5 is formed.

- the first metal film 5 in this embodiment preferably has a thickness of 20 nm or more, and has a work function (eg, 4.9 eV) of 4.70 eV or more and 5.15 eV or less.

- a film made of a metal or a metal compound having a work function closer to the band edge than the work function of a second metal film see FIG. 3 (c): 6) described later is desirable.

- the resist pattern is used as a mask.

- the first metal film 5 in the Hvt region is etched to remove the first metal film 5 on the second active region 1b, and then the resist pattern is removed. Thereby, the first metal film 5 can be selectively left on the first active region 1a. In this way, the first metal film 5 in contact with the high dielectric constant insulating film 4 on the first active region 1a is formed.

- a second metal film 6 made of, for example, a 20 nm-thick MoN film is deposited on the entire surface of the semiconductor substrate 1 by, eg, CVD.

- the same process as the process shown in FIG. 1 (c) in the first embodiment is performed.

- the film thickness (for example, 20 nm) of the second metal film 6 made of the MoN film in this embodiment is larger than the film thickness (for example, 100 nm) of the second metal film 6 made of the MoN film in the first embodiment. thin.

- the second metal film 6 in the present embodiment preferably has a thickness of 20 nm or more, and has a work function (for example, 4.7 eV) of 4.6 eV or more and 5.05 eV or less.

- a film made of a metal or a metal compound having a work function closer to the mid gap than the work function of the first metal film 5 is desirable.

- a TaN film may be used instead of the MoN film.

- a resist pattern (not shown) that opens the Lvt region and covers the Hvt region is formed on the second metal film 6, and then the resist pattern is used as a mask. Dry etching is performed on the second metal film 6 in the Lvt region to remove the second metal film 6 on the first metal film 5, and then the resist pattern is removed. Thereby, the second metal film 6 can be selectively left on the second active region 1b. In this way, the second metal film 6 in contact with the high dielectric constant insulating film 4 on the second active region 1b is formed.

- a polysilicon film having a film thickness of, for example, 100 nm is formed on the first metal film 5 and the second metal film 6, and then a p-type impurity is ion-implanted into the polysilicon film.

- a silicon film 11 made of a silicon film is formed.

- the implantation conditions of the silicon film 11 are that the implanted ion species is B (boron), the implantation energy is 3 keV, and the implantation dose is 1 ⁇ 10 15 cm ⁇ 2 .

- a resist pattern (not shown) having a gate pattern shape is formed on the silicon film 11 by, eg, photolithography. Thereafter, by using the resist pattern as a mask, the silicon film 11, the first metal film 5, and the high dielectric constant insulating film 4 in the Lvt region are sequentially patterned by dry etching, on the first active region 1a.

- a first gate insulating film 4 a made of the high dielectric constant insulating film 4, a first conductive part 5 a made of the first metal film 5, and a third conductive part 11 a made of the silicon film 11 are sequentially formed.

- the silicon film 11, the second metal film 6, and the high dielectric constant insulating film 4 in the Hvt region are sequentially patterned to form the second dielectric layer 4 made of the high dielectric constant insulating film 4 on the second active region 1b.

- a gate insulating film 4b, a second conductive portion 6b made of the second metal film 6, and a fourth conductive portion 11b made of the silicon film 11 are sequentially formed.

- first gate insulating film 4a and the first conductive part 5a provided on and in contact with the first gate insulating film 4a on the first active region 1a, and the first conductive part

- a first gate electrode 20A having a third conductive portion 11a formed on 5a is sequentially formed, and a second gate insulating film 4b and a second gate insulation are formed on the second active region 1b.

- a second gate electrode 20B having a second conductive portion 6b provided in contact with the film 4b and a fourth conductive portion 11b formed on the second conductive portion 6b is sequentially formed.

- the first gate electrode 20A side in the first active region 1a is used.

- a p-type source / drain region 7a having a relatively shallow junction depth is formed in a self-aligned manner, and a relatively shallow junction depth is formed laterally below the second gate electrode 20B in the second active region 1b.

- a p-type source / drain region 7b is formed in a self-aligning manner.

- a side surface of the first gate electrode 20A is formed using a method similar to the method of forming the sidewall in the step shown in FIG. 2B in the first embodiment.

- a sidewall 8a is formed thereon, and a sidewall 8b is formed on the side surface of the second gate electrode 20B.

- a p-type source / drain region 9a having a relatively deep junction depth is formed in the region 1a outside the sidewall 8a in a self-aligned manner, and the junction depth is formed outside the sidewall 8b in the second active region 1b.

- a relatively deep p-type source / drain region 9b is formed in a self-aligned manner.

- a silicide metal film (not shown) made of, for example, a 10 nm-thickness Ni film is deposited on the entire surface of the semiconductor substrate 1 by sputtering. Thereafter, for example, the first RTA process is performed on the semiconductor substrate 1 in a nitrogen atmosphere at 320 ° C., and each of the deep p-type source / drain regions 9a and 9b and the third and fourth conductive portions 11a and 11b. Silicon is reacted with nickel of the metal film for silicide.

- the unreacted metal for silicide remaining on the element isolation region 2 and the sidewalls 8a and 8b by immersing the semiconductor substrate 1 in an etching solution made of a mixed solution of sulfuric acid and hydrogen peroxide. Remove the membrane. Thereafter, the second RTA process is performed on the semiconductor substrate 1 at a temperature (for example, 550 ° C.) higher than the temperature in the first RTA process.

- a temperature for example, 550 ° C.

- silicide films 10a1 and 10b1 made of NiSi film are formed on the deep p-type source / drain regions 9a and 9b, and the third and fourth conductive portions 11a in the first and second gate electrodes 20A and 20B are formed.

- 11b silicide films 10a2 and 10b2 made of NiSi film are formed.

- the semiconductor device that is, the first conductive portion 5a having the work function (for example, 4.9 eV) closer to the band edge and the first conductive portion 11a.

- a low threshold transistor LTr having a gate electrode 20A, a second conductive portion 6b having a work function (for example, 4.7 eV) close to a mid gap, and a second gate electrode 20B having a fourth conductive portion 11b.

- a semiconductor device including the high threshold transistor HTr can be manufactured.

- the first and second gate electrodes 20A and 20B in this embodiment have a so-called MIPS (Metal Insert Poly-Silicon) electrode structure composed of a metal film and a polysilicon film formed thereon. is doing.

- MIPS Metal Insert Poly-Silicon

- the first gate electrode 20A of the low threshold transistor LTr has a first conductive part 5a made of the first metal film 5 and a third conductive part 11a made of the silicon film 11.

- the second gate electrode 20B of the high threshold transistor HTr has a second conductive portion 6b made of the second metal film 6 and a fourth conductive portion 11b made of the silicon film 11.

- the first conductive portion 5a provided in contact with the first gate insulating film 4a and the second conductive portion 6b provided in contact with the second gate insulating film 4b have different compositions from each other. It is composed of a film (first conductive portion 5a: TiN film, second conductive portion 6b: MoN film), and the second conductive portion 6b is “a silicon midgap work function” as compared to the first conductive portion 5a. Has a work function close to.

- the third conductive portion 11a formed on the first conductive portion 5a and the fourth conductive portion 11b formed on the second conductive portion 6b have the same film thickness (for example, 100 nm), and And made of a silicon film having the same composition. That is, the first conductive portion 5a and the second conductive portion 6b are formed thereon with third and fourth conductive portions 11a and 11b made of silicon films having the same film thickness and the same composition.

- the first gate insulating film 4a in contact with the first conductive portion 5a and the second gate insulating film 4b in contact with the second conductive portion 6b are formed in the same process and in the same structure. It consists of high dielectric constant insulating films having the same film thickness.

- n-type channel region 3a in the Lvt region and the n-type channel region 3b in the Hvt region are formed in the same process and in the same structure, and have the same impurity concentration.

- the shallow p-type source / drain regions 7a and 7b, the deep p-type source / drain regions 9a and 9b, and the sidewalls 8a and 8b are also formed in the same process and the same structure. However, if there is a difference in height between the first and second gate electrodes 20A and 20B, the side wall 8a formed on the side surface of the first gate electrode 20A and the side surface of the second gate electrode 20B will be described.

- the side wall 8b to be formed may be formed at different heights.

- the first conductive portion 5a and the second conductive portion 6b are made of metal films having different compositions, so that the work function of the second conductive portion 6b can be reduced by the first conductive portion 5a.

- the effective function of the high threshold transistor HTr having the second gate electrode 20B composed of the second conductive portion 6b and the fourth conductive portion 11b is set to a work function closer to the “silicon midgap work function” than the work function.

- the work function can be made lower than the effective work function of the low threshold transistor LTr having the first gate electrode 20A composed of the first conductive portion 5a and the third conductive portion 11a. That is, the threshold voltage of the high threshold transistor MTr can be made higher than the threshold voltage of the low threshold transistor LTr. Therefore, the low and high threshold transistors LTr and HTr having different threshold voltages can be realized with high accuracy.

- the first gate electrode 20A is formed by patterning with the silicon film 11 formed on the first metal film 5, and the second metal film 6 is formed. Since the second gate electrode 20B can be formed by patterning with the silicon film 11 formed thereon, the patterning accuracy of the first and second gate electrodes 20A and 20B can be greatly improved.

- the first and second gate electrodes 20A and 20B patterned with high accuracy can be realized.

- the first gate electrode 20A in the present embodiment includes a first conductive portion 5a having a relatively thin film thickness and a third conductive portion that is easier to pattern than the first conductive portion 5a formed thereon. 11a.

- the second gate electrode 20B in this embodiment includes a second conductive portion 6b having a relatively small thickness and a fourth conductive pattern that is easier to pattern than the second conductive portion 6b formed thereon. Part 11b.

- the case where the second metal film 6 on the first metal film 5 is removed by dry etching has been described as a specific example.

- the invention is not limited to this.

- the second metal film 6 on the first metal film 5 may be polished and removed by the CMP method.

- the second activity is formed as shown in FIG. 3D.

- the present invention is not limited to this.

- the first metal film may be formed on the first active region.

- FIGS. 5 (a) to 5 (d) are cross-sectional views of relevant parts showing a method of manufacturing a semiconductor device according to the third embodiment of the present invention in the order of steps.

- FIGS. 5A to 5D the same components as those in the first embodiment or the second embodiment described above are shown in FIGS. 1A to 2 in the first embodiment.

- the same reference numerals as those shown in d) or the same reference numerals as those shown in FIGS. 3A to 4D in the second embodiment are given, and redundant description is omitted.

- the Lvt region is a region where a low threshold transistor is formed

- the Hvt region is a region where a high threshold transistor is formed.

- the first metal film 5 and the second metal film 6 are removed.

- the first metal film 6 on the first metal film 5 is not removed and the first metal film 11 is removed.

- the second metal film 6 is left on the metal film 5 to form a silicon film 11 on the second metal film 6.

- a polysilicon film having a thickness of, for example, 100 nm is formed on the second metal film 6

- p-type impurities are ion-implanted into the polysilicon film.

- a silicon film 11 made of a p-type polysilicon film is formed.

- the implantation conditions for the silicon film 11 are the same implantation conditions as in the second embodiment.

- a resist pattern (not shown) having a gate pattern shape is formed on the silicon film 11 by, eg, photolithography. Thereafter, by using the resist pattern as a mask, the silicon film 11, the second metal film 6, the first metal film 5, and the high dielectric constant insulating film 4 in the Lvt region are sequentially patterned by dry etching to obtain the first On the active region 1 a, a first gate insulating film 4 a made of the high dielectric constant insulating film 4, a first conductive portion 5 a made of the first metal film 5, and a fifth conductive made of the second metal film 6. A third conductive portion 11a made up of the portion 6a and the silicon film 11 is sequentially formed.

- the silicon film 11, the second metal film 6, and the high dielectric constant insulating film 4 in the Hvt region are sequentially patterned to form the second dielectric layer 4 made of the high dielectric constant insulating film 4 on the second active region 1b.

- a gate insulating film 4b, a second conductive portion 6b made of the second metal film 6, and a fourth conductive portion 11b made of the silicon film 11 are sequentially formed.

- first gate insulating film 4a and the first conductive part 5a provided on and in contact with the first gate insulating film 4a on the first active region 1a, and the first conductive part

- a first gate electrode 20A having a fifth conductive portion 6a formed on 5a and a third conductive portion 11a formed on the fifth conductive portion 6a is sequentially formed, and a second active portion

- a second gate electrode 20B having a conductive portion 11b is sequentially formed.

- the first gate electrode 20A side in the first active region 1a is used.

- a p-type source / drain region 7a having a relatively shallow junction depth is formed in a self-aligned manner, and a relatively shallow junction depth is formed laterally below the second gate electrode 20B in the second active region 1b.

- a p-type source / drain region 7b is formed in a self-aligning manner.

- the side surface of the first gate electrode 20A is formed using a method similar to the method of forming the sidewall in the step shown in FIG. 2B in the first embodiment.

- a sidewall 8a is formed thereon, and a sidewall 8b is formed on the side surface of the second gate electrode 20B.

- the outer side of the sidewall 8a in the first active region 1a is formed.