KR890004882B1 - 드라이에칭 방법 및 장치 - Google Patents

드라이에칭 방법 및 장치 Download PDFInfo

- Publication number

- KR890004882B1 KR890004882B1 KR1019840007903A KR840007903A KR890004882B1 KR 890004882 B1 KR890004882 B1 KR 890004882B1 KR 1019840007903 A KR1019840007903 A KR 1019840007903A KR 840007903 A KR840007903 A KR 840007903A KR 890004882 B1 KR890004882 B1 KR 890004882B1

- Authority

- KR

- South Korea

- Prior art keywords

- workpiece

- voltage

- voltage waveform

- potential

- dry etching

- Prior art date

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

- H01L21/306—Chemical or electrical treatment, e.g. electrolytic etching

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32917—Plasma diagnostics

- H01J37/32935—Monitoring and controlling tubes by information coming from the object and/or discharge

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32431—Constructional details of the reactor

- H01J37/32697—Electrostatic control

- H01J37/32706—Polarising the substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J37/00—Discharge tubes with provision for introducing objects or material to be exposed to the discharge, e.g. for the purpose of examination or processing thereof

- H01J37/32—Gas-filled discharge tubes

- H01J37/32917—Plasma diagnostics

- H01J37/3299—Feedback systems

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having at least one potential-jump barrier or surface barrier, e.g. PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic System or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/302—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to change their surface-physical characteristics or shape, e.g. etching, polishing, cutting

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01J—ELECTRIC DISCHARGE TUBES OR DISCHARGE LAMPS

- H01J2237/00—Discharge tubes exposing object to beam, e.g. for analysis treatment, etching, imaging

- H01J2237/32—Processing objects by plasma generation

- H01J2237/33—Processing objects by plasma generation characterised by the type of processing

- H01J2237/334—Etching

Abstract

내용 없음.

Description

제1a도는 종래의 드라이에칭 장치의 1실시예를 도시한 구성도.

제1b도는 제1a도의 장치에서 전위분포를 나타내는 곡선도.

제2a도는 종래의 드라이에칭 장치의 다른예를 도시한 구성도.

제2b도는 제2a도의 장치에서 전위분포를 나타내는 곡선도.

제3도는 제1도와 제2도의 장치에서 활성화이온의 수와 이온에너지 사이의 관계를 나타내는 분포곡선도.

제4a도는 본 발명의 1실시예에 의하여 얻어지는 활성화 이온의 수와 이온에너지 사이의 관계를 나타내는 분포 곡선도.

제4b도는 제4a도의 이온에너지 분포를 실현하는데 필요한 전위분포의 1실시예를 나타내는 곡선도.

제5a도는 플라즈마 에칭공정에서 피가공물의 표면에 축적된 전하를 도시한 구성도.

제5b도는 피가공물 주위의 전위분포를 도식적으로 나타낸 곡선도.

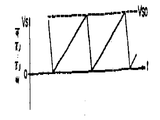

제6a도는 본 발명에 따른 드라이에칭 방법의 1실시예에서 전극에 가해지는 전압파형을 나타내는 곡선도.

제6b도는 제6a도의 전압이 전극에 가해질때 에칭시키는 동안 피가공물의 표면전위의 충전을 나타내는 곡선도.

제7도는 본 발명에 따른 드라이에칭 장치의 1실시예를 나타내는 블럭도.

제8도는 본 발명에 따른 드라이에칭 장치의 다른 실시예를 나타내는 블럭도.

* 도면의 주요부분에 대한 부호의 설명

11 : 기판 12 : 하측전극

13 : 상측전극 14 : 처리실

15 : RF전원 16 : 임피던스 정압회로

17 : 제어전압발생부 18 : 광대역 증폭기

19 : 커패시터 20 : 전압계

20A : 전위측정프로우브 20B : 절연물

20C : 수정판 32 : 입력장치

34 : μ컴퓨터 36 : D/A변환기

37 : A/D변환기

본 발명은 플라즈마를 사용한 드라이에칭 기술에 관한 것으로, 특히 플라즈마에서 생성되는 하전입자의 가속에너지를 제어할 수 있는 드라이에칭 기술에 관한 것이다.

드라이에칭은, 예를 들면 반도체 기술에서 중요한 공정중의 하나이며, 고집적도를 필요로 하는 자기버블 소자나 대규모 집적회로의 제조에 매우 중요하다.

드라이에칭에는 플라즈마 에칭, 반응성 이온에칭, 이온에칭이 있다. 그러나 플라즈마 에칭과 반응성 이온에칭은 피가공물, 대량 생산성, 에칭속도, 선택도등에 손상을 준다는 관점에서 특히 중요하다.

일반적으로 드라이에칭에 있어서 사이드에칭은 하지않고 마스크에 따라서 정확하게 정교한 패턴을 형성하고 높은 에칭속도, 우수한 선택도를 가질수 있는것(즉, 마스크 필름이나 바닥층에 대한 에칭속도로 에칭되는 피가공물에 대한 에칭속도의 비를 크게 하기위하여)이 바람직하다. 드라이에칭의 여러가지의 특성은 가스압력 및 플라즈마 여기력(예를들어, 고주파전력)과 같은 파라미터에 의해 결정된다. 무선주파수 방전가스 플라즈마가 사용되는 경우에 있어서 가스압력이 상승하면, 입자간에 충돌할 확률이 증가하고 각각의 하전입자의 활성에너지가 감소하여, 에칭의 화학적, 등방성경향이 강해진다. 즉, 바닥층이 쉽게 에칭되지 않도라도 사이드에칭을 감소시키는 것이 곤란하므로 에칭에의해 형성된 패턴의 정밀도가 저하된다. 고주파전력이 증가하면, 하전입자의 활성에너지가 증가하여 에칭의 물리적인 경향(즉, 스퍼터링 경향)이 강해진다. 즉, 에칭속도가 증가하여도 바닥층이 에칭될 염려가 있어 선택도가 저하된다.

상술한 바와같이, 에칭특성은 서로 연관되어 있다.

따라서, 다른 특성에 악영향을 끼치지 않고 단지 원하는 특성만을 제어하기는 어렵다.

드라이에칭의 에칭특성을 제어하기 위한 것으로써는 일본국 특허 공개공보 소화 56-33839호 및 57-131374호에 제안된 것이 있다. 그러나, 상술한 것으로써는 바닥층이나 마스크층에 대한 에칭속도를 느리게 유지하면서 에칭되는 층에 대한 에칭속도를 증가시키기는 곤란하다는 문제점이 잇었다.

본 발명의 목적은 상기한 종래 기술의 문제점을 해결하기 위해서 이루어진 것으로, 바닥막의 에칭속도를 증가시키지 않고 에칭막의 에칭속도를 증가시킬 수 있는 드라이에칭 방법 및 장치를 제공하는 것이다.

본 발명의 드라이에칭에서 활성화이온의 수와 이온에너지는 에칭특성을 결정하는 가장 중요한 요소이다.

활성화이온의 수는 주로 에칭속도와 관련되어 있으며, 이온 에너지는 주로 에칭의 선택도와 관련되어 있다.

따라서 활성화 이온의 수와 이온 에너지 그리고 이온에너지 분포를 서로 독립적으로 제어할 수 있다면 에칭속도와 선택도를 분리하여 제어할 수 있을 것이다.

여기서 본 발명은 이온에너지의 분포폭을 좁게 만들고 이온 에너지의 평균값을 소정의 값으로 고정시킴으로써 에칭속도와 별도로 에칭의 선택도를 제어하기 위하여 피가공물의 표면과 플라즈마 사이에 실질적으로 일정한 가속전압을 인가하는 것을 그 특징으로 한다.

본 발명의 상기 및 그밖의 목적과 새로운 특징은 본 명세서의 기술 및 첨부도면으로 명확하게 될것이다.

본 발명의 이해를 쉽게 하기 위하여 종래의 기술을 먼저 설명하기로 한다.

제1a도는 평행 플레이트 전극을 갖는 종래의 드라이에칭 장치의 1실시예를 도시한 것이다. 제1a도에서 상측전극(2)와 하측전극(3)은 처리실(4)내에 배치되어 있다. 또한, 상측전극(2)는 접지되어 있고, 하측전극(3)은 임피던스 정합상자(6)을 통해서, 예를들면 13.56MHz의 주파수를 갖는 전압을 발생하는 고주파전원(5)에 접속되어 있고, 또 반도체기판(1)과 같은 피가공물이 그 위에 탑재되어 있다. 처리실(4)는 배기계(도시하지 않음)에 의해 배기되고, 에칭가스를 도입하여 처리실(4)내에서 10∼0.05Torr(즉, 약 1300∼7Pa)의 압력으로 유지된다.

이 상태에서 고주파전압, 즉 무선주파수전압(이하 단순히 RF전압이라 한다) 이 가스 플라즈마를 발생시키기 위하여 하측전극(3)에 인가된다. 플라즈마에서 발생한 이온은 플라즈마와 하측전극(3) 사이에서 생성된 전계에 의해서 가속화되고, 저항 마스크의 구멍을 거쳐서 기판(1)에 수직으로 접촉해서 기판(1)의 노출부분을 에칭한다.

제1b도는 처리실(4)에서의 전위분포를 개략적으로 도시한 것이다. 제1a도에 도시한 바와같이 상측전극(2)가 접지되어 있으므로 전극(2)의 전위는 0이다.

하측전극(3)에는 DC관점에서 하측전극을 접지전위로부터 분리시키는 정합회로를 통해서 RF전압이 인가된다.

따라서, 전극(3)의 전위는 DC관점에서 자기 바이어스 전압이 가해져 RF전압에 따라서 정의 방향과 부의 방향으로 진동한다. 일반적으로 전자와 양이온은 플라즈마 내에서 공존한다. 그러나, 전자는 매우 작은 양이기 때문에 전계에 의해서 떨어져 나가기 쉽다. 따라서 플라즈마는 적은 양의 전위(즉, 플라즈마 전위 V0)를 가지고 있으며 전자로 충전된 하측전극은 부의 전위(자기바이어스 전압)을 가지고 있다. 전위값 V0이 제1b도에서 커지는 것은 주목할 만 하다. 그래서 플라즈마 전위 V0과 자기 바이어스 전압의 합계는 플라즈마와 하측전극(3) 사이에 인가되고, RF전압은 거기에 중첩된다. 플라즈마에 남아 있는 양이온은 플라즈마와 전극(3)사이에 형성된 장에 의하여 하측전극(3)의 방향으로 가속화된다. 기판(1)에 투사된 양이온의 에너지는 제3도에 도시한 바와같이 가속화된 전압과 입자사이의 충돌에 의해서 분산된다. 부수적으로 상측전극(2)와 근접해 있는 양이온은 작은 전위차 V0에 의해 가속화된다.

제3도를 참조하여, 산화 실리콘층의 폴리실리콘층이 그 위에 있는 저항마스크를 따라서 CCI4가스에 의해서 선택적으로 드라이에칭되는 경우를 생각해보기로 한다.

그리고, 실리콘을 에칭하는데 필요한 임계 이온 에너지와 Eth(SiO2)가 Eth(Si)보다 큰 상태에서 산화실리콘을 Eth(Si)와 Eth(SiO2)로 에칭되는데 필요한 임계 이온에너지에 대해서 알아보기로 한다.

하단의 산화실리콘층을 에칭하지 않고 폴리실리콘층을 에칭하기 위해서는 기판(1)에 투사되는 이온의 에너지를 Eth(Si)내지 Eth(SiO2)의 범위로 하여야 한다.

만약 기판위에 투사되는 양이온이 제3도의 곡선 B에 의해서 나타내어지는 에너지 분포를 가지고 있다고 가정하다. 그러면 Eth(SiO2)보다 큰 에너지를 가지고 있는 이온은 산화실리콘층의 하단부분을 에칭한다.

만약 플라즈마에 공급된 RF전력이 산화실리콘층의 하단부분의 부식을 방지하기 위하여 감소되었다면, 기판에 투사된 양이온은 제3도의 곡선 A가 나타내는 에너지 분포를 갖게된다. 즉, Eth(SiO2)보다 큰 에너지를 가지고 있는 이온의 수는 감소되어서 산화실리콘층의 하단부분의 에칭을 방지하게 되는 것이다. 그러나 Eth(Si)와 Eth(SiO2)사이에 에너지가 분포되어 있는 이온의 수는 감소되므로 폴리실리콘의 에칭속도도 감소된다. 반면에 에칭가스의 압력이 증가되면, 기판에 투사된 양이온도 제3도의 곡선 C로 나타내는 에너지분포를 갖게 된다. 즉, 에너지 분포곡선 B는 에너지가 적은 부분으로 옮겨지므로 산화실리콘층의 하단부분의 에칭속도 뿐만 아니라 폴리실리콘층의 에칭속도도 감소된다.

또, 가스압력이 증가될때, 에칭의 화학적, 등방성 경향이 강화되고 에칭의 방향성이 감소되어 패턴 정밀도가 감소되게 된다. 상술한 바와같이 선택도와 에칭속도, 패턴정밀도를 동시에 개선시키는 것은 매우 어렵다.

제2a도는 플라즈마 밀도의 이온에너지를 독립적으로 제어하는 기구를 갖춘 종래의 드라이에칭 장치의 1실시예이다. 제2a도에서, 상측전극(2)는 낮은 주파수에서 필터회로(6B)를 통하여 접지전위와 연결되고 높은 주파수에서 고주파전원(5B)에 연결되어 있다. 하측전극(3)은 높은 주파수에서 필터회로(6A)를 통하여 접지전위와 연결되고, 낮은 주파수에서 AC바이어스전원(5A)에 연결되어 있다.

즉, 하측전극(3)은 고주파전원(5B)(즉, RF전원)에서 볼때 접지전극이고, 상측 전극(2)는 바이어스 전원(5A)로 부터 볼때 접지전극이 된다.

필터회로(6A)와 (6B)는 전원 (5A)와 (5B)가 서로 간섭하는 것을 방지하는 저지회로로 사용된다.

RF전원(5B)의 출력전압의 주파수는 양이온이 출력전압을 따르지 않는 범위, 즉 13.56MHz내에 있어야 하고, AC바이어스 전원(5A)의 출력전압의 주파수는 양이온이 출력전압을 따를 수 있는 범위, 즉 400KHz내에 있어야 한다. RF전압이 RF전원(5B)부터 상측전극(2)에 인가될때 플라즈마가 발생된다.

제2b도에 도시한 바와같이 플라즈마는 양이온에 의하여 정전위에 위치해있고, 플라즈마 V0은 플라즈마와 접지전극과 같이 쓰이는 하측전극(3)사이에서 발생한다. 또 대략 400KHz의 주파수를 갖는 AC전압이 바이어스 전원(5A)에서 하측전극(3)으로 공급될때, 양이온은 AC바이어스 전압에 따라서 가속화된다.

그래서, 기판(1)에 투사된 이온의 에너지는 광범위하게 변화하고, 높은 에너지 이온의 많은 양이 발생될 수 있다. 상술한 바와같이 플라즈마 밀도는 주로 RF전원(5B)에 의하여 제어되고, 이온 에너지분포의 범위는 AC바이어스 전원(5A)에 의해서 확대될 수도 있다.

그러나 제3도의 에너지 분포곡선 C의 폭의 절반이 AC전원(5A)를 사용함으로써 확대된다면, Eth(Si)보다 큰 에너지를 가지고 있는 이온의 수 뿐만 아니라 Eth(SiO2)보다 큰 에너지를 가지고 있는 이온의 소도 증가할 것이다. 즉, 하단의 산화실리콘층의 에칭을 방해하는 동안 바닥층 취에 있는 폴리실리콘층의 에칭속도를 증가시키는 것은 어렵다.

본 발명은 이온에너지 분포범위를 제어함으로써 에칭특성을 증가시키려는데 그 의도가 있다.

제4a도는 본 발명에 따라 이온에너지를 분포시킨 1실시예를 도시한 것이다. 제4a도에 도시한 바와같이 기판위에 투사되는 이온의 에너지는 사실상 Eth(Si)와 Eth(SiO2)사이에 위치해 있다. 따라서 하단의 산화실리콘층은 에칭되지 않고 바닥층위에 놓인 폴리실리콘층만이 에칭된다. 분포곡선의 최고점이 높아지면, 폴리실리콘층에 대한 에칭속도도 증가한다. 즉, 이온에너지 분포곡선을 작은 폭으로 하는것에 의해 에칭속도를 에칭의 선택도와는 별개로 기대값 상태로 얻을 수 있다.

좁은 폭의 이온에너지 분포는 플라즈마와 피가공물 사이에 있는 일정한 전위차를 실질적으로 유지시킴으로써 얻을 수 있다. 제4b도는 처리실 안에서 전위분포의 1예를 도시한 것이다. 플라즈마와 피가공물의 표면 사이에 존재하는 전위차 Vac(즉, 순수이온 가속화전압)가 일정하게 유지되면, 피가공물에 투사도는 이온의 에너지는 만약 입자사이의 충돌로 인한 에너지 변화가 무시할 수 있을 정도로 작은 범위내라면 실질적으로 일정하다.

그런 상태는 피가공물의 표면을 원하는 부전위 -VAc로 유지함으로써 얻을 수 있다(대부분 |VAc|>|V0|과 Vac∼VAC이다). 드라이에칭을 하는 경우 절연체나 반절연체로 된 에칭마스크를 사용한다. 또, 산화실리콘층위의 폴리실리콘과 같은 전기적은 부유층이 종종 드라이에칭된다. 이러한 경우에 피가공물의 표면은 하측전극(3)과 전기적으로 연결되지 않는다. 따라서 양이온이 피가공물의 표면에 투사될때, 양전하가 표면에 축적되므로, 피가공물의 표면은 양성으로 충전된다. 즉, 출력전압이 시간에따라 증가하는 전압원 Vs가 제5a도에 도시한 바와같이, 바이어스 전압 VB인가된 가전극(3)과 피가공물의 표면 사이에 연결되어 있다고 간주될 수 있다. 제5b도는 이상태의 전위분포를 도시한 것이다. 양전하가 피가공물의 표면에 축적되므로, 순수이온 가속화전압 Vac가 감소되고 투사이온의 에너지도 감소된다. 그리하여 원하는 이온에너지 분포는 얻어지지 않고 에칭활동은 결과적으로 정지된다.

상술한 문제는 피가공물의 양끝에 걸리는 전압 |VS|의 크기에 따라서 바이어스전압 |VB|의 절대값을 증가시키고, 전압 |VS|의 증가를 막음으로 해결될 수 있다.

이 경우, 순수이온 가속화전압 Vac는 일정하게 유지되고 이온에너지 분포곡선은 제4a도에 도시한 바와같이, 원하는 에너지 값 주위에 좁은 범위를 형성한다.

그러나. ql이어스 전압 |VB|의 한계를 초과하는 값으로 증가시키는 것은 현실적으로 불가하다. 따라서 바이어스 전압의 크기가 어느정도 증가될때 피가공물의 표면은 전기적으로 중성을 띠게 된다. 양이온에 의한 표면전하는 전자와 같은 부전하에 의해서 중성화 될 수 있다.

이것을 달성하기 위하여 바이어스 전압은 부전하로 된 입자를 피가공물에 충돌시키기 위go 변화된다.

예를 들면, 하측전극(3)은 양전위로 유지된다. 여기서 전자의 온도는 낮은 온도의 플라즈마안에서 이온의 온도보다 높다. 따라서, 음극인 목표물로 전자들이 이동될 수 있다. 여기서 전극전위를 전자들이 이동될 수 있는 값으로 변화시키는 것이 필요하다. 그 다음 전자는 표면위에 투사되고, 그 곳의 전위는 감소하여 0또는 어떤 정의 값이나 부의 값으로 된다. 이 상태에서 다음의 바이어스 변화 주기가 시작된다. 따라서 드라이에칭을 동일한 이온 가속화전압에서 실시할 수 있다.

제6a도, 제6b도는 바이어스전압의 파형과 피가공물의 표면전위를 각각 도시한 것이다. 플라즈마 전위가 일정하기 때문에 순수 가속화전압안에서 변화는 상관이 없다.

따라서 접지전압 VAC에 대한 가속화전압은 Vac대신에 사용될 수 있다. 제6b도에 도시한 바와같이 전극(3)에 대해서 피가공물의 표면전위 VS는, 양이온의 축적에따라 선형적으로 증가한다. 전극(3)에 인가된 바이어스전압 Va는 제6a도에 도시한 바와같이 표면전위 VS가 증가함에 따라서 변화된다. 즉 크기가 |VAC|+|VS|와 같은 전압은 일정한 전위 VAC에서 피가공물의 표면을 유지하기 위하여 전극(3)에 인가된다.

표면전위의 크기 |VS|는 실질적으로 선형으로 증가하므로 바이어스전압의 크기는 제6a도의 파형의 부의 부분에 나타난 바와같이 |VAC|값에서부터 선형적으로 증가한다.

여기서, 중요한 것은 전압파형이 가속화전압성분 VAC와 피가공물의 전하축적에 따른 표면전위 VS에서의 변화효과를 상쇄하는 전하축적 보상성분을 포함한다는 것이다. 가속화전압성분 VAC는 에칭의 목적에 따라서 어느정도 변하는 것을 허용할 수 있다. 바이어스 전압의 크기가 VBO보다 작게 유지되어야 하는 경우, 바이어스 전압은 값 VBO에 도달하자 마자 정의 값으로 변화된다.

그러므로, 전자는 피가공물의 표면위에 투사되며 피가공물의 표면전하가 감소된다. 즉, 표면적위의 크기 VS가 감소된다. 전자의 크기는 양이온의 크기보다 훨씬 작으므로, 전자는 쉽게 가속이 되어 표면전하의 중성화가 급격히 일어난다. 따라서, 정의 부분에 존재하는 제6a도의 파형부분에서 바이어스 전압의 적분값 |VBdt|는 부의 부분에 존재하는 파형부분에서 적분값 |Vadt|보다 훨씬 작다. 표면전위 VS는 제6b도에 도시한 바와같이 상술한 중성화에 의하여 급격히 감소된다. 그와같은 중성화후에 바이어스 전압은 부의 값으로 되어 양이온이 피가공물의 표면에 충돌하게 한다.

원하는 주기동안 에칭동작을 계속하기 위하여 각각의 바이어스 변화주기의 최종상태를 초기상태와 같게 만드는 것이 필요하다.

예를들면, 표면전위가 0에서 VSO로 증가하고 제6b도에 도시한 바와같이 각 주기에서 0으로 감소되는 것이 바람직하다. 상술한 바와같이 전자 가속화전압이 반드시 정일 필요는 없다. 특히 중성화의 초기 기간에서 저장된 양전하는 정의 전압원으로 사용된다.

그러므로, 중성화단계에서 전극전위는 전자가 피가공물에 충돌하는 것이 허용된다면 0이거나 부이어도 좋다.

실제로 플라즈마 전위 VO은 수 볼트 내지 30볼트의 범위내에 있으며, 플라즈마 전위를 포함하지 않거나 접지전위에 대하여 정의되는 이온가속화전압 VAC는 약 50V∼1000V의 범위내에 있다. 반도체층이 에칭되는 경우에는 이온가속화전압을 약 50V∼800V의 범위내에 있게하는것이 바람직하며, 약 50V∼300V의 이온가속화전압은 특히 중요하다. 바이어스전압 Va의 반복주파수는 약 1KHz∼200KHz의 범위내에 있으며, 더욱 바람직하게는 약 7KHz∼20KHz의 범위에 있다.

반도체층이 에칭되는 경우에는 반복주파수를 약 7KHz∼10KHz의 범위로 하는 것이 특히 바람직하다.

제7도는 본 발명에 따른 드라이에칭 장치의 1실시예의 블럭도이다. 제7도에서 (11)은 피가공물, 즉 처리될 기판, (12)는 하측전극, (13)은 상측전극, (14)는 처리실, (15)는 RF전원, (16)은 임피던스 정합회로, (17)은 제어전압 발생부, (18)은 광대역 증폭기, (19)는 접지전위에 대하여 RF성붐을 리이드하기 위한 커패시터, (20)은 전압계, (20A)는 전위측정 프로우브, (20B)는 절연물, (20C)는 수정판이다. 제어전압 발생부(17)은 입력장치(32), 메모리와 프로세서를 포함하는 마이크로 점퓨터(34), D/A변환기(36), A/D변환기(37) 및 디스플레이(38)을 포함한다. 하측전극(12)와 상측전극(13)은 처리실(14)내에 배치되어 있다. 상측전극(13)은 임피던스 정합회로(16)을 거쳐서 RF전원(15)에 연결되어 있으며, RF전원(15)는 예를 들면 13.56MHZ주파수를 갖는 RF전압을 발생시킨다. 하측전극(12)는 커패시터(19)를 통하여 접지되고, 또한 광대역증폭기(19)에 연결된다. 수정판(20C)는 하측전극(12)위에 놓여 있고, 처리될 기판(11)은 전극(12)의 중앙부분에 놓여진다. 또한, 전위측정 프로우브(20A)는 절연물을 통하여 전극(12)의 위치에 장치되어 전극(12)위에 놓여진 수정판(20C)의 표면전위를 측정한다. 전압계(20)이 디지탈 출력을 발생할때 A/D변환기(37)은 없어도 된다. 전압계(20)의 출력단자는 제어전압 발생부(17)에 연결된다. VAC와 VSO(또는 VBO)와 같은 파형 파라미터들은 입력장치(32)에 의해서 제어전압 발생부(17)에 입력될 수 있다.

바이어스 전압의 파형이 프로우브(20A)에 의하여 조정되는 표면전위에 따라서 결정되지만, 위의 전압파형은 입력장치(32) 또는 기본파령(톱니파, 구형파, 정현파)을 적절히 결합시켜 입력되는 파형 파라미터에 따라 결정될 수도 있다. 이하, 바이어스 전압의 파형이 상술한 동작에 따라 결정되는 경우에 대해 설명한다.

처리실(14)는 진공화되어 에칭가스와 가스도입 파리프(도시하지 않음)를 통하여 처리실(14)에 도입되므로, 처리실(14)의 내부는 10∼0.05Torr의 가스압력으로 유지된다.

RF전원(15)로부터 RF전압이 상기한 상태에 있는 상측정극(13)에 인가될때, 플라즈마는 하측전극(12)와 상측전극(13)사이에서 발생된다. 프로우브(20A)와 하측전극(12)가 정연되었기 때문에 기판(11)의 표면과 같은 위치의 전위는 프로우브(20A)와 전압계(20)에 의해서 검출된다. 제어전압 발생부(17)에 의해 프리세트된 값을 갖는 가속화전압은 광대역증폭기(18)을 통하여 하측전극(12)에 인가된다. 상기의 전압에 의해서 가속화된 양이온은 처리될 기판(11)의 표면에서 충돌한다. 그리고 기판(11)의 표면전위는 증가된다. 따라서, 플라즈마와 기판(11)의 표면사이에 존재하는 전위차는 하측전극(12)에 인가된 전압과 기판(11)의 표면전위 사이에 존재하는 차이와 같다. 표면전위는 프로우브(20A)에 의해서 측정되고, 제어전압 발생부(17)은 표면전위의 증가에 대응하는 값에 의해서 좀더 부의 값으로 전극(12)에 인가된 전압을 변화시킨다.

즉, 하측전극(12)에 인가된 부의전압의 절대치는 표면전위의 증가에 대응하는 값에 의해서 증가된다.

상술한 전압이 -VBO값으로 감소될때, 하측전극(12)의 전위는 제6도 A에 도시한 바와같이 전자를 기판(11)과 하측전극(12)로 이동시켜서 표면전위를 OV로 감소시키기 이하여 정의값으로 변한다. OV의 표면전위가 프로우브(20A)에 의해서 검출될때, 하측전극(12)에 인가된 전압은 소정의 값으로 회복된다.

그러한 작용이 여러번 반복된다. 그러므로 이온 가속화전압은 일정하게 유지되고, 이온 에너지는 원하는 작은 범위내에서만 분포된다.

상기의 경우에서 가속화전압을 일정하게 유지시키기 위하여 제어전압 발생부(17)의 출력은 전위측정 프로우브(20A)로부터의 신호에 의하여 제어된다.

그러나 처리조건이 미리 결정되어 있는 경우에는 처리조건에 따라서 하측전극(12)에 인가된 전압의 파형을 결정하고, 전극(12)에서 얻게되는 파형을 적용시키는 것이 가능하다. 이 경우, 프로우브(20A)와 전압계(20)은 사용되지 않고 생략하여도 좋다.

제8도는 본 발명에 따른 드라이에칭 장치의 다른 실시예를 도시한 것이다. 본 실시예에서, 드라이에칭용 플라즈마는 전자 사리클로트론 공전기를 이용하여 발생된다. 제8도에서 (21)은, 피가공물, 즉 처리될 기판을 나타내고, (22)는 제어전극, (23)은 코일, (24)는 처리실, (25)는 마그네트론, (26)은 도파관, (27)은 제어전압 발생부, (28)은 광대역증폭기, (30)은 전압계 그리고 (30A)는 전위측정 프로우브이다.

마그네트론(25)는 도파관(26)의 한쪽끝에 장치되고, 다른 한쪽끝은 수정벽을 통하여 처리실(24)와 연결되어 있다. 자기코일(23)은 토파관(26)의 한쪽끝 주위에 장치된다. 프로우브(30A)를 갖추고 있는 제어전극(22)는 처리실(24)의 낮은 부분에 배치된다. 제어전극(22)는 광대역증폭기(28)에 연결되고, 제어전극(22)에 인가된 전압은 증폭기(28)을 거쳐 제어전압 발생부(27)과 전압계(30)에 의해서 제어된다. 제어전압 발생부(27)은 제7도의 제어전압 발생부(17)과 유가한 구조와 기능을 가지고 있다.

프라즈마는 마그네트론(25)와 코일(23)에 의해 형성되는 자계에 의해서 발생되는 마이크로파에 의해서 전자사이클로트론 동진의 조건에서 발생된다. 플라즈마와 처리될 기판(21)사이에 인가된 이온 가속화전압은 제7도의 실시예에서와 같은 방법으로 제어된다.

전자 사이클로트론 공진 방법을 이용한 종래의 드라이에칭 장치에 있어서, 플라즈마중에 있는 양이온은 그리드전극에 의해서 떨어져 나간다. 그러나 공간 전하와 그외의 것들 때문에 이온가속화전압을 대략 500V보다 적게 제어한다는 것이 어렵다. 본 실시예에 따르면, 플라즈마와 기판(21)의 표면사이에 인가된 이온가속화 전압은 일정하게 유지되고 좀더 원하는 값으로 설정할 수 있다. 그리고 본 실시예에서 금속으로 형성되고 플라즈마에 노출된 그리드전극은 사용할 필요가 없기때문에 금속에 의한 처리실(24)의 오염에 대한 염려도 없게 된다.

상술한 바와같이, 본 발명은 플라즈마가 평행 전극판 사이에서 발생되는 드라이에칭 장치에만 한정되지 않고, 다른 방법으로 플라즈마가 발생되는 드라이에칭 장치에도 적용이 가능하다.

상기 실시에서 이온가속화 전압을 실제적으로 유지하는 수단은 플라즈마를 발생시키는 수단과 별개의 것으로 마련된다. 그러나, 일정한 이온가속화 전압을 생성하는 수단은 플라즈마를 생성하는 수단과 공용으로 사용될 수도 있다.

상술한 바와같이 본 발명은 드라이에칭에 있어서 에칭특성을 크게 증가시킴으로서 반도체 웨이퍼의 제조분야에서 생산을 증가시키고 미세한 패턴을 만들 수 있다.

Claims (18)

- 처리실(14, 24)내에 배치된 전극(12, 22)위에 피가공물(11, 21)을 탑재하는 공정, 상기 처리실로 에칭가스를 도입하는 공정, 플라즈마를 발생시키기 위하여 상기 에칭가스를 여기시키는 공정 및 상기 전극에 주기적인 전압파형 V를 공급하는 공정을 포함하며, 상기 주기적인 전압파형 V는 피가공물에 전자가 충돌하게 하는 제1의 부분과 피가공물 쪽으로 양이온을 가속하는 제2의 부분을 갖고, 상기 파형의 제2부분은 일정한 가속장을 발생하기 위한 제1의 성분과 피가공물 표면에서 충전증가의 영향을 제거하기 위한 제2의 성분으로 되어, 양이온이 피가공물 표면에서 충전증가의 일정한 이온에너지를 독립적으로 가속화하는 드라이에칭 방법.

- 처리실(14, 24)내에 배치된 전극(12, 22)위에 피가공물(11, 21)을 탑재하는 공정, 상기 처리실로 에칭가스를 도입하는 공정, 플라즈마를 발생시키기 위하여 상기 에칭가스를 여기시키는 공종 및 상기 전극에 주기적인 전압파형 V를 공급하는 공정을 포함하고, 상기 주기적인 전압파형 V는 각각의 주기에서 제1의 극성의 제1부분과 제2의 극성의 제2부분을 갖고, 제1부분은 제1의 일정한 전압-시간곱 S1=|v(t)dt)|를 갖고, 제2의 부분은 상기 제1의 곱보다 큰 제2의 전압-시간곱 S2=|v(t)dt|를 가지며, 상기 부분에서 전압의 시간미분은 0이 아닌 상수이며 상기 플라즈마내의 상기 제1의 극성의 입자가 상기 전압파형의 상기 제2부분에 대응하는 시간의 길이로 상기 피가공물의 표면위에 충돌하고, 상기 시간의 길이에서 상기 전극에 공급된 전압의 크기는 상기 피가공물의 상기 표면에서 전하의 증가와 함께 증가하고, 상기 입자는 전압에 의해 일정하게 가속되고, 상기 피가공물의 상기 표면에서 상기 전하는 상기 전압파형의 상기 제1의 부분에 대응하는 시간의 길이에서 상기 제2의 극성의 입자에 의해 중성화되는 드라이에칭방법.

- 특허청구의 범위 제2항에 있어서, 상기 주기적인 전압파형의 상기 제2의 부분에서 전압의 크기는 제1의 소정의 값보다 작지 않은 드라이에칭방법.

- 특허청구의 범위 제3항에 있어서, 상기 주기적인 전압파형의 상기 제2의 부분에서 전압의 크기는 제2의 소정의 값보다 크지 않은 드라이에칭방법.

- 특허청구의 범위 제2항에 있어서, 또 상기 주기적인 전압파형의 상기 제2의 부분에서 전압의 크기의 상한과 하한을 각가 지정하기 위해 제1 및 제2의 값을 설정하는 공정을 포함하는 드라이에칭방법.

- 특허청구의 범위 제5항에 있어서, 또 상기 전극위에 배치된 상기 피가공물의 상기 표면과 동등한 곳에서 전위를 측정하는 공정, 상기 피가공물의 상기 표면에서 일정한 전위를 생성하기 위해 측정된 전위에따라 상기 전압파형의 상기 제2의 부분의 전압을 결정하기 위한 공정을 포함하는 드라이 에칭방법.

- 특허청구의 범위 제6항에 있어서, 또 상기 전압파형의 상기 제1의 부분이 인가된후에 상기 측정된 전위의 크기가 0으로 저감되는 시간을 검출하는 스텝, 상기 전압파형의 상기 제2의 부분이 인가된 후에 상기 측정된 전위의 크기가 상기 제2의 값에 대응하는 값에 접근하는 시간을 검출하는 스텝을 포함하는 드라이 에칭방법.

- 특허청구의 범위 제2항에 있어서, 또 입력장치(32)에 의해 상기 주기적인 전압파형을 결정하고 입력하는 공정을 포함하는 드라이에칭방법.

- 진공이 가능한 처리실(14, 24), 상기 처리실에 배치되고 전압이 인가되며, 그 위에 피가공물(11, 21)을 탑재하기 위해 배열된 전극(12, 22), 상기 처리실(14, 24)내로 에칭가스를 도입하기 위한 가스도입수단, 상기 처리실내에서 플라즈마를 발생시키도록 상기 에칭가스를 여기하기 위한 플라즈마 발생수단, 주기적인 전압파형을 발생해서 상기 전극에 상기 파형을 인가하는 수단을 포함하며, 상기 파형은 피가공물의 표면에 전자가 충돌하게 하는 제1의 부분과 상기 피가공물 쪽으로 양의 입자를 가속화하는 제2의 부분을 갖고, 상기 파형의 제2의 부분은 일정하게 가속하는 장을 발생하기 위한 제1의 성분과 상기 피가공물의 표면에서 충전증가의 영향을 제거하하기 위한 제1의 성분과 중첩된 제2의 성분으로 되어 이온이 상기 피가공물 표면에서 충전증가의 일정한 이온에너지를 독립적으로 가속화하는 드라이에칭 장치.

- 진공이 가능한 처리실(14, 24), 상기 처리실에 위치되고 전압이 인가되며, 그위에 피가공물(11, 21)을 탑재하기 위해 배열된 전극(12, 22), 상기 처리실(12, 24)내로 에칭가스를 도입하기 위한 가스도입수단, 상기 처리실내에서 플라즈마를 발생시키도록 상기 에칭가스를 여기하기 위한 플라즈마 발생수단(15, 16, 25, 26), 상기 전극에 공급하기 위해 주기적인 전압파형을 발생하는 수단(17, 27)을 포함하며, 상기 주기적인 전압파형은 각각의 기간에서 제1의 극성의 제1의 부분과 제2의 극성의 제2의 부분을 갖고, 상기 제1의 부분에서 제1의 일정한 전압-시간 곱 S1=|∫v(t)dt|이 얻어지고, 제2의 부분에서 상기 제1의 곱보다 큰 제2의 전압-시간 곱 S2=|∫v(t)dt|가 얻어지며, 시간에 대해 상기 제2의 부분에서 전압의 미분이 0이 아닌 상수이며, 상기 플라즈마내의 상기 제1의 극성의 입자가 상기 전압파형의 상기 제2의 부분에 대응하는 시간의 길이로 상기 피가공물의 표면위에 충돌하고, 상기 시간의 길이에서 상기 전극에 공급된 전압의 크기는 상기 표면에서 전하의 증가와 함께 증가하고, 상기 입자는 전압에의해 일정하게 가속되고, 상기 전하는 상기표면에서 상기 전압파형의 상기 제1의 위치에 대응하는 시간의 길이에서 상기 제2의 극성의 입자에 의해 중성화되는 드라이에칭방법.

- 특허청구의 범위 제10항에 있어서, 상기 주기적인 전압파형의 상기 제2의 부분에서 전압의 크기는 제1의 소정의 값보다 작지 않은 드라이에칭장치.

- 특허청구의 범위 제10항에 있어서, 상기 주기적인 전압파형 발생수단(17, 27)은 여러가지의 파형피라미터를 입력하는 입력장치(32)를 포함하는 드라이에칭방법.

- 특허청구의 범위 제12항에 있어서, 또 상기 전압파형발생수단은 메모리수단, 논리연산부, 상기 전압파형의 출력신호를 형성하는 출력 수단(36)을 포함하는 드라이에칭장치.

- 특허청구의 범위 제10항에 있어서, 상기 피가공물의 상기 표면과 동등한 상기 처리실내에서 전위를 측정하는 측정수단(20A, 30A)를 포함하는 드라이에칭방법.

- 특허청구의 범위 제14항에 있어서, 상기 전위측정수단에 의한 측정의 결과가 상기 전압파형 발생수단에 공급되어 상기 주기적인 전압파형을 제어하고, 상기 측정수단과 상기 전압파형 발생수단은 부의 귀환루프를 형성하는 드라이에칭장치.

- 소정의 압력으로 처리실에 처리가스를 도입하고, 피가공물에 바이어스 전압을 인가하는 동안 상기 피가공물을 처리하기 위해 플라즈마를 발생하도록 상기 가스를 여기시키는 것에 의해 처리실에 배치된 피가공물을 드라이 에칭하는 방법에 있어서, 상기 피가공물의 전위를 검출하는 공정과 상기 피가공물에 AC전압을 인가하여 DC성분만 남도록 상기 피가공물의 검출된 전위에서 변화를 보상하는 공정을 포함하는 드라이에칭방법.

- 특허청구의 범위 제16항에 있어서, 상기 피가공물의 전위를 검출하고, 상기 피가공물에 AC전압을 인가하기 위한 부의 귀환루프를 형성하는 공정을 포함하는 드라이에칭방법.

- 처리실, 처리실로 처리가스를 도입하고, 소정의 레벨에서 상기 가스의 압력을 유지하는 수단, 플라즈마를 발생하도록 상기 가스를 여기시키는 수단, DC성분만 남도록 상기 피가공물의 전위에서 변화를 보상하는 상기 처리실내의 피가공물에 AC전압을 공급하는 전원수단, 상기 피가공물의 전압을 검출하는 검출수단, 상기 검출수단으로부터 신호를 입력하고, 부의 귀화루프를 마련하기 위해 상기 전원수단으로 제어신호를 공급하.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP58234319A JPS60126832A (ja) | 1983-12-14 | 1983-12-14 | ドライエツチング方法および装置 |

| JP58-234319 | 1983-12-14 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR850005145A KR850005145A (ko) | 1985-08-21 |

| KR890004882B1 true KR890004882B1 (ko) | 1989-11-30 |

Family

ID=16969143

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1019840007903A KR890004882B1 (ko) | 1983-12-14 | 1984-12-13 | 드라이에칭 방법 및 장치 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US4622094A (ko) |

| EP (1) | EP0145015B1 (ko) |

| JP (1) | JPS60126832A (ko) |

| KR (1) | KR890004882B1 (ko) |

| DE (1) | DE3479843D1 (ko) |

Families Citing this family (72)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2603217B2 (ja) * | 1985-07-12 | 1997-04-23 | 株式会社日立製作所 | 表面処理方法及び表面処理装置 |

| JPS62125626A (ja) * | 1985-11-27 | 1987-06-06 | Hitachi Ltd | ドライエツチング装置 |

| JPH0643637B2 (ja) * | 1986-05-30 | 1994-06-08 | 株式会社日立製作所 | プラズマ制御装置 |

| KR900007687B1 (ko) * | 1986-10-17 | 1990-10-18 | 가부시기가이샤 히다찌세이사꾸쇼 | 플라즈마처리방법 및 장치 |

| US4767496A (en) * | 1986-12-11 | 1988-08-30 | Siemens Aktiengesellschaft | Method for controlling and supervising etching processes |

| JPH0828345B2 (ja) * | 1987-07-10 | 1996-03-21 | 株式会社日立製作所 | ドライエッチング方法および装置 |

| US4793895A (en) * | 1988-01-25 | 1988-12-27 | Ibm Corporation | In situ conductivity monitoring technique for chemical/mechanical planarization endpoint detection |

| US4950377A (en) * | 1988-09-23 | 1990-08-21 | Siemens Aktiengesellschaft | Apparatus and method for reactive ion etching |

| KR900013595A (ko) * | 1989-02-15 | 1990-09-06 | 미다 가쓰시게 | 플라즈마 에칭방법 및 장치 |

| US5145554A (en) * | 1989-02-23 | 1992-09-08 | Seiko Epson Corporation | Method of anisotropic dry etching of thin film semiconductors |

| US5236537A (en) * | 1989-04-07 | 1993-08-17 | Seiko Epson Corporation | Plasma etching apparatus |

| US5133830A (en) * | 1989-04-07 | 1992-07-28 | Seiko Epson Corporation | Method of pretreatment and anisotropic dry etching of thin film semiconductors |

| DE69017744T2 (de) * | 1989-04-27 | 1995-09-14 | Fujitsu Ltd | Gerät und Verfahren zur Bearbeitung einer Halbleitervorrichtung unter Verwendung eines durch Mikrowellen erzeugten Plasmas. |

| US5194119A (en) * | 1989-05-15 | 1993-03-16 | Seiko Epson Corporation | Method of anisotropic dry etching of thin film semiconductors |

| US5163458A (en) * | 1989-08-03 | 1992-11-17 | Optek, Inc. | Method for removing contaminants by maintaining the plasma in abnormal glow state |

| US5198072A (en) * | 1990-07-06 | 1993-03-30 | Vlsi Technology, Inc. | Method and apparatus for detecting imminent end-point when etching dielectric layers in a plasma etch system |

| US5707486A (en) * | 1990-07-31 | 1998-01-13 | Applied Materials, Inc. | Plasma reactor using UHF/VHF and RF triode source, and process |

| US5316645A (en) * | 1990-08-07 | 1994-05-31 | Canon Kabushiki Kaisha | Plasma processing apparatus |

| JP2859721B2 (ja) * | 1990-08-07 | 1999-02-24 | キヤノン株式会社 | プラズマ処理装置 |

| JP2830978B2 (ja) * | 1990-09-21 | 1998-12-02 | 忠弘 大見 | リアクティブイオンエッチング装置及びプラズマプロセス装置 |

| JP2543642B2 (ja) * | 1991-01-18 | 1996-10-16 | アプライド マテリアルズ インコーポレイテッド | 高周波交流電気エネルギ―と相対的に低い周波数の交流電気的エネルギ―を有する、工作物を処理するためのシステムおよび方法 |

| US5302882A (en) * | 1991-09-09 | 1994-04-12 | Sematech, Inc. | Low pass filter for plasma discharge |

| US5330615A (en) * | 1991-11-04 | 1994-07-19 | Cheng Chu | Symmetric double water plasma etching system |

| US5175472A (en) * | 1991-12-30 | 1992-12-29 | Comdel, Inc. | Power monitor of RF plasma |

| US5523955A (en) * | 1992-03-19 | 1996-06-04 | Advanced Energy Industries, Inc. | System for characterizing AC properties of a processing plasma |

| US5458732A (en) * | 1992-04-14 | 1995-10-17 | Texas Instruments Incorporated | Method and system for identifying process conditions |

| US5325019A (en) * | 1992-08-21 | 1994-06-28 | Sematech, Inc. | Control of plasma process by use of harmonic frequency components of voltage and current |

| JP3799073B2 (ja) * | 1994-11-04 | 2006-07-19 | 株式会社日立製作所 | ドライエッチング方法 |

| FR2738984B1 (fr) * | 1995-09-19 | 1997-11-21 | Centre Nat Rech Scient | Procede et dispositif de mesure d'un flux d'ions dans un plasma |

| US5860350A (en) * | 1997-01-29 | 1999-01-19 | Rexroad; John | Flat braid with web core |

| US6174450B1 (en) * | 1997-04-16 | 2001-01-16 | Lam Research Corporation | Methods and apparatus for controlling ion energy and plasma density in a plasma processing system |

| US6356097B1 (en) * | 1997-06-20 | 2002-03-12 | Applied Materials, Inc. | Capacitive probe for in situ measurement of wafer DC bias voltage |

| EP0908535B1 (fr) * | 1997-10-08 | 2003-07-23 | RECHERCHE ET DEVELOPPEMENT DU GROUPE COCKERILL SAMBRE, en abrégé: RD-CS | Procédé pour le décapage de la surface d'un substrat et installation pour la mise en oeuvre de ce procédé |

| US6265831B1 (en) | 1999-03-31 | 2001-07-24 | Lam Research Corporation | Plasma processing method and apparatus with control of rf bias |

| US6201208B1 (en) | 1999-11-04 | 2001-03-13 | Wisconsin Alumni Research Foundation | Method and apparatus for plasma processing with control of ion energy distribution at the substrates |

| JP4306149B2 (ja) * | 2001-05-28 | 2009-07-29 | 株式会社デンソー | 半導体装置の製造方法 |

| US6677711B2 (en) * | 2001-06-07 | 2004-01-13 | Lam Research Corporation | Plasma processor method and apparatus |

| JP4219628B2 (ja) * | 2001-07-27 | 2009-02-04 | 東京エレクトロン株式会社 | プラズマ処理装置および基板載置台 |

| JP3795044B2 (ja) | 2001-09-14 | 2006-07-12 | メシルジーン、インコーポレイテッド | ヒストンデアセチラーゼの阻害剤 |

| JP4830288B2 (ja) * | 2004-11-22 | 2011-12-07 | 富士電機株式会社 | プラズマ制御方法およびプラズマ制御装置 |

| US7713430B2 (en) * | 2006-02-23 | 2010-05-11 | Micron Technology, Inc. | Using positive DC offset of bias RF to neutralize charge build-up of etch features |

| US7875859B2 (en) * | 2008-03-31 | 2011-01-25 | Tokyo Electron Limited | Ion energy analyzer and methods of manufacturing and operating |

| US9287092B2 (en) | 2009-05-01 | 2016-03-15 | Advanced Energy Industries, Inc. | Method and apparatus for controlling ion energy distribution |

| US9435029B2 (en) | 2010-08-29 | 2016-09-06 | Advanced Energy Industries, Inc. | Wafer chucking system for advanced plasma ion energy processing systems |

| US11615941B2 (en) | 2009-05-01 | 2023-03-28 | Advanced Energy Industries, Inc. | System, method, and apparatus for controlling ion energy distribution in plasma processing systems |

| US9767988B2 (en) | 2010-08-29 | 2017-09-19 | Advanced Energy Industries, Inc. | Method of controlling the switched mode ion energy distribution system |

| US9287086B2 (en) | 2010-04-26 | 2016-03-15 | Advanced Energy Industries, Inc. | System, method and apparatus for controlling ion energy distribution |

| FR2951026B1 (fr) * | 2009-10-01 | 2011-12-02 | St Microelectronics Sa | Procede de fabrication de resonateurs baw sur une tranche semiconductrice |

| US9309594B2 (en) | 2010-04-26 | 2016-04-12 | Advanced Energy Industries, Inc. | System, method and apparatus for controlling ion energy distribution of a projected plasma |

| US9362089B2 (en) | 2010-08-29 | 2016-06-07 | Advanced Energy Industries, Inc. | Method of controlling the switched mode ion energy distribution system |

| WO2012135351A2 (en) | 2011-03-28 | 2012-10-04 | Tokyo Electron Limited | Ion energy analyzer, methods of electrical signaling therein, and methods of manufacturing and operating the same |

| US9210790B2 (en) | 2012-08-28 | 2015-12-08 | Advanced Energy Industries, Inc. | Systems and methods for calibrating a switched mode ion energy distribution system |

| CN104782233B (zh) * | 2012-08-28 | 2018-12-25 | 先进能源工业公司 | 控制开关模式离子能量分布系统的方法 |

| US9685297B2 (en) | 2012-08-28 | 2017-06-20 | Advanced Energy Industries, Inc. | Systems and methods for monitoring faults, anomalies, and other characteristics of a switched mode ion energy distribution system |

| WO2014036000A1 (en) | 2012-08-28 | 2014-03-06 | Advanced Energy Industries, Inc. | Wide dynamic range ion energy bias control; fast ion energy switching; ion energy control and a pulsed bias supply; and a virtual front panel |

| WO2016130672A1 (en) * | 2015-02-11 | 2016-08-18 | President And Fellows Of Harvard College | Methods for nano and micro-patterning |

| US20170358431A1 (en) * | 2016-06-13 | 2017-12-14 | Applied Materials, Inc. | Systems and methods for controlling a voltage waveform at a substrate during plasma processing |

| KR101913684B1 (ko) * | 2016-10-21 | 2018-11-01 | 주식회사 볼트크리에이션 | 건식 에칭장치 및 그 제어방법 |

| PL3711080T3 (pl) | 2017-11-17 | 2023-12-11 | Aes Global Holdings, Pte. Ltd. | Zsynchronizowane pulsowanie źródła przetwarzania plazmy oraz polaryzacji podłoża |

| TWI767088B (zh) | 2017-11-17 | 2022-06-11 | 新加坡商Aes全球公司 | 電漿處理系統,用於調變其中的電源的控制方法及相關的電漿處理控制系統 |

| KR20200100642A (ko) | 2017-11-17 | 2020-08-26 | 에이이에스 글로벌 홀딩스 피티이 리미티드 | 플라즈마 프로세싱을 위한 이온 바이어스 전압의 공간 및 시간 제어 |

| JP7134695B2 (ja) * | 2018-04-27 | 2022-09-12 | 東京エレクトロン株式会社 | プラズマ処理装置、及び電源制御方法 |

| US10555412B2 (en) * | 2018-05-10 | 2020-02-04 | Applied Materials, Inc. | Method of controlling ion energy distribution using a pulse generator with a current-return output stage |

| KR102592922B1 (ko) * | 2018-06-21 | 2023-10-23 | 삼성전자주식회사 | 기판 처리 장치, 신호 소스 장치, 물질막의 처리 방법, 및 반도체 소자의 제조 방법 |

| CN110896019A (zh) * | 2018-09-12 | 2020-03-20 | 北京北方华创微电子装备有限公司 | 等离子体刻蚀设备及刻蚀方法 |

| CN114222958B (zh) | 2019-07-12 | 2024-03-19 | 先进工程解决方案全球控股私人有限公司 | 具有单个受控开关的偏置电源 |

| US11615966B2 (en) | 2020-07-19 | 2023-03-28 | Applied Materials, Inc. | Flowable film formation and treatments |

| US11887811B2 (en) * | 2020-09-08 | 2024-01-30 | Applied Materials, Inc. | Semiconductor processing chambers for deposition and etch |

| US11699571B2 (en) * | 2020-09-08 | 2023-07-11 | Applied Materials, Inc. | Semiconductor processing chambers for deposition and etch |

| US11670487B1 (en) | 2022-01-26 | 2023-06-06 | Advanced Energy Industries, Inc. | Bias supply control and data processing |

| US11942309B2 (en) | 2022-01-26 | 2024-03-26 | Advanced Energy Industries, Inc. | Bias supply with resonant switching |

| US20240079210A1 (en) * | 2022-09-01 | 2024-03-07 | Advanced Energy Industries, Inc. | Transition control in a bias supply |

Family Cites Families (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4233109A (en) * | 1976-01-16 | 1980-11-11 | Zaidan Hojin Handotai Kenkyu Shinkokai | Dry etching method |

| US4222838A (en) * | 1978-06-13 | 1980-09-16 | General Motors Corporation | Method for controlling plasma etching rates |

| JPS55118637A (en) * | 1979-03-06 | 1980-09-11 | Chiyou Lsi Gijutsu Kenkyu Kumiai | Plasma etching apparatus |

| JPS5613480A (en) * | 1979-07-13 | 1981-02-09 | Hitachi Ltd | Dry etching apparatus |

| FR2463975A1 (fr) * | 1979-08-22 | 1981-02-27 | Onera (Off Nat Aerospatiale) | Procede et appareil pour la gravure chimique par voie seche des circuits integres |

| JPS5681678A (en) * | 1979-12-05 | 1981-07-03 | Toshiba Corp | Method and apparatus for plasma etching |

| JPS5687672A (en) * | 1979-12-15 | 1981-07-16 | Anelva Corp | Dry etching apparatus |

| US4333814A (en) * | 1979-12-26 | 1982-06-08 | Western Electric Company, Inc. | Methods and apparatus for improving an RF excited reactive gas plasma |

| DE3006694C2 (de) * | 1980-02-22 | 1982-07-29 | Bergwerksverband Gmbh, 4300 Essen | Verfahren zur Herstellung von Nadelkoks |

| JPS5812347B2 (ja) * | 1981-02-09 | 1983-03-08 | 日本電信電話株式会社 | プラズマエッチング装置 |

| US4327123A (en) * | 1981-02-20 | 1982-04-27 | Rca Corporation | Method of metallizing a phosphor screen |

| JPS58200529A (ja) * | 1982-05-19 | 1983-11-22 | Hitachi Ltd | プラズマ処理装置 |

| US4464223A (en) * | 1983-10-03 | 1984-08-07 | Tegal Corp. | Plasma reactor apparatus and method |

| US4496448A (en) * | 1983-10-13 | 1985-01-29 | At&T Bell Laboratories | Method for fabricating devices with DC bias-controlled reactive ion etching |

| US4585516A (en) * | 1985-03-04 | 1986-04-29 | Tegal Corporation | Variable duty cycle, multiple frequency, plasma reactor |

-

1983

- 1983-12-14 JP JP58234319A patent/JPS60126832A/ja active Granted

-

1984

- 1984-12-12 DE DE8484115200T patent/DE3479843D1/de not_active Expired

- 1984-12-12 EP EP84115200A patent/EP0145015B1/en not_active Expired

- 1984-12-12 US US06/680,838 patent/US4622094A/en not_active Expired - Lifetime

- 1984-12-13 KR KR1019840007903A patent/KR890004882B1/ko not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| EP0145015A2 (en) | 1985-06-19 |

| JPS60126832A (ja) | 1985-07-06 |

| DE3479843D1 (en) | 1989-10-26 |

| JPH0527244B2 (ko) | 1993-04-20 |

| EP0145015B1 (en) | 1989-09-20 |

| KR850005145A (ko) | 1985-08-21 |

| US4622094A (en) | 1986-11-11 |

| EP0145015A3 (en) | 1986-08-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR890004882B1 (ko) | 드라이에칭 방법 및 장치 | |

| US4795529A (en) | Plasma treating method and apparatus therefor | |

| US5779925A (en) | Plasma processing with less damage | |

| JP3381916B2 (ja) | 低周波誘導型高周波プラズマ反応装置 | |

| US6777037B2 (en) | Plasma processing method and apparatus | |

| US6197151B1 (en) | Plasma processing apparatus and plasma processing method | |

| CN111819664A (zh) | 控制方法和等离子体处理装置 | |

| US20020069971A1 (en) | Plasma processing apparatus and plasma processing method | |

| US6909087B2 (en) | Method of processing a surface of a workpiece | |

| JP7231671B2 (ja) | プラズマ処理装置 | |

| KR101191698B1 (ko) | 저압력 플라즈마를 점화시키는 방법 및 장치 | |

| JPH09120957A (ja) | プラズマ装置及びプラズマ処理方法 | |

| JPS6136589B2 (ko) | ||

| JPH08255782A (ja) | プラズマ表面処理装置 | |

| US6501082B1 (en) | Plasma deposition apparatus and method with controller | |

| JP3085151B2 (ja) | プラズマ処理方法および装置 | |

| KR100234902B1 (ko) | 2차전위에 의한 방전을 제거한 플라즈마 처리장치 | |

| GB2049560A (en) | Plasma etching | |

| JPH07193049A (ja) | エッチング装置及びエッチング方法 | |

| JP7439288B2 (ja) | プラズマ処理装置及びプラズマ処理方法 | |

| JP2023158802A (ja) | プラズマ処理装置及びプラズマ処理方法 | |

| JP3704423B2 (ja) | 表面処理装置 | |

| JPH0480368A (ja) | プラズマ処理方法 | |

| CN117936352A (en) | Plasma processing apparatus | |

| JPH07283207A (ja) | プラズマ処理方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E902 | Notification of reason for refusal | ||

| G160 | Decision to publish patent application | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 19971227 Year of fee payment: 12 |

|

| LAPS | Lapse due to unpaid annual fee |