KR100716378B1 - 조정가능한 시간 응답을 갖는 디지털-대-아날로그 인터페이스 회로 - Google Patents

조정가능한 시간 응답을 갖는 디지털-대-아날로그 인터페이스 회로 Download PDFInfo

- Publication number

- KR100716378B1 KR100716378B1 KR1020027011563A KR20027011563A KR100716378B1 KR 100716378 B1 KR100716378 B1 KR 100716378B1 KR 1020027011563 A KR1020027011563 A KR 1020027011563A KR 20027011563 A KR20027011563 A KR 20027011563A KR 100716378 B1 KR100716378 B1 KR 100716378B1

- Authority

- KR

- South Korea

- Prior art keywords

- signal

- modulator

- time response

- filter

- digital

- Prior art date

Links

- 230000004044 response Effects 0.000 title claims abstract description 146

- 238000000034 method Methods 0.000 claims description 23

- 230000008859 change Effects 0.000 claims description 13

- 238000001914 filtration Methods 0.000 claims description 6

- 230000001934 delay Effects 0.000 abstract description 6

- 239000003990 capacitor Substances 0.000 description 16

- 238000010586 diagram Methods 0.000 description 16

- 230000006872 improvement Effects 0.000 description 8

- 230000007704 transition Effects 0.000 description 7

- 230000003111 delayed effect Effects 0.000 description 6

- 230000006870 function Effects 0.000 description 6

- 238000013139 quantization Methods 0.000 description 6

- 230000000694 effects Effects 0.000 description 5

- 230000001413 cellular effect Effects 0.000 description 4

- 230000007246 mechanism Effects 0.000 description 4

- 238000012546 transfer Methods 0.000 description 4

- 238000004458 analytical method Methods 0.000 description 3

- 238000013459 approach Methods 0.000 description 3

- 230000005540 biological transmission Effects 0.000 description 3

- 238000004891 communication Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 230000002238 attenuated effect Effects 0.000 description 2

- 230000001010 compromised effect Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 229920005994 diacetyl cellulose Polymers 0.000 description 2

- 230000009467 reduction Effects 0.000 description 2

- 230000003321 amplification Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 230000001143 conditioned effect Effects 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000003199 nucleic acid amplification method Methods 0.000 description 1

- 238000005457 optimization Methods 0.000 description 1

- 230000008569 process Effects 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 238000004088 simulation Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K7/00—Modulating pulses with a continuously-variable modulating signal

- H03K7/08—Duration or width modulation ; Duty cycle modulation

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/20—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers

- H03F3/24—Power amplifiers, e.g. Class B amplifiers, Class C amplifiers of transmitter output stages

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03G—CONTROL OF AMPLIFICATION

- H03G3/00—Gain control in amplifiers or frequency changers

- H03G3/20—Automatic control

- H03G3/30—Automatic control in amplifiers having semiconductor devices

- H03G3/3036—Automatic control in amplifiers having semiconductor devices in high-frequency amplifiers or in frequency-changers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/322—Continuously compensating for, or preventing, undesired influence of physical parameters

- H03M3/368—Continuously compensating for, or preventing, undesired influence of physical parameters of noise other than the quantisation noise already being shaped inherently by delta-sigma modulators

- H03M3/37—Compensation or reduction of delay or phase error

- H03M3/374—Relaxation of settling time constraints, e.g. slew rate enhancement

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2200/00—Indexing scheme relating to amplifiers

- H03F2200/331—Sigma delta modulation being used in an amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M3/00—Conversion of analogue values to or from differential modulation

- H03M3/30—Delta-sigma modulation

- H03M3/50—Digital/analogue converters using delta-sigma modulation as an intermediate step

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M7/00—Conversion of a code where information is represented by a given sequence or number of digits to a code where the same, similar or subset of information is represented by a different sequence or number of digits

- H03M7/30—Compression; Expansion; Suppression of unnecessary data, e.g. redundancy reduction

- H03M7/3002—Conversion to or from differential modulation

- H03M7/3004—Digital delta-sigma modulation

- H03M7/3015—Structural details of digital delta-sigma modulators

- H03M7/3031—Structural details of digital delta-sigma modulators characterised by the order of the loop filter, e.g. having a first order loop filter in the feedforward path

Landscapes

- Engineering & Computer Science (AREA)

- Theoretical Computer Science (AREA)

- Power Engineering (AREA)

- Compression, Expansion, Code Conversion, And Decoders (AREA)

- Analogue/Digital Conversion (AREA)

- Control Of Amplification And Gain Control (AREA)

- Amplifiers (AREA)

- Electronic Switches (AREA)

Abstract

디지털 신호를 아날로그 신호로 전환하는 인터페이스 회로가 제시된다. 이러한 인터페이스 회로는 시간 응답 조정 회로, 변조기, 및 필터를 포함한다. 이러한 시간 응답 조정 회로는 디지털 신호를 수신하여 조정된 신호를 발생시킨다. 변조기는 시간 응답 조정 회로와 결합되어, 조정된 신호를 수신하고, 변조기 신호를 발생시킨다. 필터는 변조기와 결합되어, 변조기 신호를 수신하고, 아날로그 신호를 발생시킨다. 아날로그 신호는 시간 응답 조정 회로에 의해 수정된 시간 응답을 갖는다. 실시예에서, 시간 응답 조정 회로는 이득 엘리먼트, 지연 엘리먼트, 및 합산기를 포함한다. 이득 엘리먼트는 디지털 신호를 수신하여 스케일 인자로 이를 스케일한다. 지연 엘리먼트는 디지털 신호를 수신하여 이를 시간 지연만큼 지연시킨다. 합산기는 이득 엘리먼트 및 지연 엘리먼트와 결합되어, 이득 엘리먼트로부터 스케일된 신호 및 지연 엘리먼트로부터의 지연 신호를 합산하여 조정된 신호를 발생시킨다.

Description

본원발명은 전기회로에 관한 것으로서, 특히 조정가능한 시간 응답을 갖는 아날로그 신호를 제공하는 인터페이스 회로에 관한 것이다.

디지털-대-아날로그 인터페이스 회로가 아날로그 회로 엘리먼트를 구동하는 아날로그 신호를 제공하기 위해 많은 전기 회로들에서 일반적으로 사용된다. 이러한 인터페이스 회로는 일반적으로 디지털 회로로부터 디지털 신호를 수신하고 아날로그 신호를 제공하기 위해 필터링되는 대응 중간 신호를 발생시키는 펄스 밀도 변조(PDA) 또는 펄스 폭 변조(PWM)를 사용한다. PWM 또는 PDM은 디지털 및 아날로그 회로 사이에서 인터페이스로서 동작한다.

기존의 PWM 또는 PDM은 N-비트 디지털 값을 갖는 시퀀스로 구성되는 디지털 신호를 수신하고 각각의 값에 대해 대응하는 파형을 발생시킨다. 각각의 파형은 소정 주기를 갖고 입력 디지털 값에 의해 결정된 다수의 하이(1) 및 로우(0) 값들을 포함한다. 예를 들어 9-비트 PWM 또는 PDM에 대해, 입력 디지털 값은 0에서 511의 범위를 가질 수 있고 각각의 파형은 512 클록 사이클을 가지며 0에서 511의 하이 값들을 포함한다. 예를 들어 128의 입력 디지털 값은 128 하이 값 및 384 로우 값을 갖는 파형에 상응한다. PWM에 있어서, 하이 값들은 각 파형의 시작에서 함께 그룹화되고, PDM에 있어서 하이 값들은 파형에 걸쳐 랜덤하게 확산된다. 쉬운 구현을 위해서, 일부 PDM들은 하이 값들을 균일하지 않은 의사-랜덤 방식으로 확산시킨다. 파형들은 본질상 디지털이고 아날로그 신호를 발생시키기 위해 필터링된다.

인터페이스 회로에 대한 일반적인 응용예 중 하나는 제어 루프이다. 예를 들어, 통신 시스템용 수신기 또는 송신기에 있어서, 인터페이스 회로는 캐리어 트랙킹 루프, 비트 타이밍 루프, 자동 이득 제어(AGC) 루프, 바이어스 제어 루프, 전력 제어 루프, DC 오프셋 조정 루프 등의 용도로 사용될 수 있다. 이러한 루프들 각각에 대해, 루프 제어 회로는 그 루프와 관련된 인터페이스 회로 내의 PWM 또는 PDM에 제공되는 디지털 제어 신호를 발생시킨다. PWM 또는 PDM은 디지털 제어 신호의 값에 따라 일련의 파형 시퀀스를 발생시킨다. 이러한 파형들은 필터링되어 제어 엘리먼트(예를 들면, 전압-제어된 발진기, 가변 이득 증폭기, 합산 엘리먼트 등)를 구동시키는데 사용되는 아날로그 제어 신호를 발생시킨다.

PWM 또는 PDM과 결합되어 발생된 이러한 아날로그 제어 신호들은 일반적으로 다양한 규격을 만족시킬 것이 요구된다. 일반적인 규격은 계단 입력에 대한 응답 시간(즉, 세틀링 타임) 및 제어 신호에 대한 리플 진폭을 포함한다. 고속 응답 시간 및 작은 리플이 많은 응용예들에서 바람직하다. 고속 응답 시간은 광대역 제어 루프 및 입력 조건의 고속 변화에 대한 신속한 응답을 가능케 하여 준다. 제어 신호에 대한 리플은 잡음에 해당하고, 적은 양의 리플이 일반적으로 요구된다. 그러나 고속 응답 시간 및 작은 양의 리플은 상충적이다. 고속 응답 시간에 대한 최적화는 종종 제어 신호에 대한 큰 리플 진폭을 야기시킨다.

살펴본 바와 같이, 작은 리플 진폭을 유지하면서 (보다 빠른 응답 시간을 제공하기 위해) 조정가능한 시간 응답을 갖는 인터페이스 회로가 요구된다.

본 발명은 조정가능한 시간 응답을 갖는 아날로그 신호를 발생시키고 아날로그 신호에 대한 최소의 부가 리플을 도입하는 디지털-대-아날로그 인터페이스 회로를 제공하는 것이다. 이러한 인터페이스 회로는 디지털 신호를 수신하고, 요구되는 시간 응답 특성(즉, 고속 시간 응답)을 획득하기 위해 디지털 신호를 수정(조정)하고, 조정된 신호를 아날로그 신호로 전환하는 뒤이은 회로에 조정된 신호를 제공하는 시간 응답 조정 회로를 포함한다. 예를 들어, 고속 응답 시간을 제공하기 위해 상기 시간 응답 조정 회로는 디지털 신호의 변화에 상응하는 오버드라이브 펄스들을 부가할 수 있다. 이러한 오버드라이브 펄스들은 필터 응답을 가속하는 뒤이은 필터에 대한 부가적인 구동을 제공한다.

본 발명의 특정 실시예는 디지털 신호를 아날로그 신호로 전환하는 인터페이스 회로를 제공한다. 이러한 인터페이스 회로는 시간 응답 조정 회로, 변조기, 및 필터를 포함한다. 시간 응답 조정 회로는 디지털 신호를 수신하여 조정된 신호를 발생시킨다. 변조기는 시간 응답 조정 회로와 결합되고, 조정된 신호를 수신하며, 변조기 신호를 발생시킨다. 필터는 변조기와 결합되고, 변조기 신호를 수신하며, 아날로그 신호를 발생시킨다. 아날로그 신호는 시간 응답 조정 회로에 의해 수정된 시간 응답을 갖는다. 실시예에서, 시간 응답 조정 회로는 이득 엘리먼트, 지연 엘리먼트, 및 합산기를 포함한다. 이득 엘리먼트는 디지털 신호를 수신하여 스케일 인자만큼 이를 스케일 한다. 지연 엘리먼트는 디지털 신호를 수신하여 이를 시간 지연만큼 지연시킨다. 합산기는 이들 엘리먼트 및 지연 엘리먼트와 결합된다. 합산기는 스케일된(또는 이득화된) 신호로부터 지연 신호를 감산시켜서 조정된 신호를 발생시킨다.

본 발명의 다른 실시예는 아날로그 신호의 시간 응답을 수정하는 방법을 제공한다. 이러한 방법은 (1) 디지털 신호를 수신하는 단계; (2) 디지털 신호 및 디지털 신호의 변화에 따라 조정된 신호를 발생시키는 단계; (3) 조정된 신호에 따라 변조기 신호를 발생시키는 단계; (4) 아날로그 신호를 획득하기 위해 변조기 신호를 필터링하는 단계를 포함한다. 아날로그 신호는 예를 들어 디지털 신호의 크기 변화에 따라 수정된 시간 응답을 갖는다. 이러한 수정은 조정된 신호에서 이루어지고, 예를 들면 디지털 신호에서의 변화에 상응하는 오버드라이브 펄스들을 포함할 수 있다.

본 발명은 예를 들어 수신기 또는 송신기 제어 루프를 포함하는 다양한 응용예들에서 사용될 수 있다.

본 발명은 하기 실시예, 도면, 청구항을 참조하여 상세히 기술될 것이다.

도1은 통신 시스템용 트랜시버의 실시예에 대한 블록 다이아그램이다.

도2A 및 2B는 기존의 제어루프 부분 및 본 발명의 인터페이스 회로를 포함하 는 제어 루프 부분을 각각 보여주는 블록 다이아그램이다.

도3A는 본 발명의 인터페이스 회로의 특정 실시예에 대한 다이아그램이다.

도3B 및 3C는 시간 응답 조정 회로의 2개의 특정 실시예들에 대한 다이아그램이다.

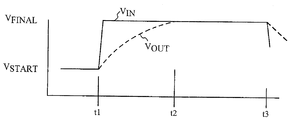

도4A 및 4B는 기존의 인터페이스 회로 및 본 발명의 시간 응답 조정 회로를 포함하는 인터페이스 각각의 계단 응답 플랏을 보여주는 도이다.

도5는 본 발명의 시간 응답 조정 회로의 특정 실시예에 대한 다이아그램이다.

도6은 1차 시그마-델타 변조기의 특정 실시예에 대한 다이아그램이다.

도7은 본 발명의 인터페이스에 대한 특정 실시예의 다이아그램이다.

도8A 및 8B는 오버드라이브 펄스가 클리핑되지 않는 경우 및 오버드라이브 펄스가 클리핑되는 경우에 대한 계단 응답의 플랏을 보여주는 도이다.

도8C 및 8D는 2개의 특정 인터페이스 회로 구현에 대한 모든 가능한 입력 디지털 값의 피크-투-피크 리플 진폭을 보여주는 도이다.

본 발명의 인터페이스 회로는 아날로그 신호를 제어 또는 인터페이싱하는 아날로그 신호를 발생시키기 위한 다양한 응용예들에서 사용될 수 있다. 예를 들어, 이러한 인터페이스 회로는 다양한 제어 루프들에서 사용되는 아날로그 제어 신호들을 발생시키는데 사용될 수 있다. 이러한 인터페이스 회로는 기준 전압, 적응된 파형, 및 다른 신호들을 발생시키는데 사용될 수 있다.

도1은 통신 시스템용 트랜시버(100)에 대한 실시예를 보여주는 블록 다이아그램이다. 도1에 제시된 송신기 및 수신기는 셀룰러 폰, HDTV, 케이블 TV 등을 포함하는 다양한 응용예들에서 사용될 수 있다.

수신된 경로 내에서, 전송된 신호(즉 기지국으로부터의 신호)는 안테나(112)에 의해 수신되고, 듀플렉서(114)를 통해 라우팅되며, 가변 감쇠기(116)에 의해 감쇠되며, 저잡음 증폭기(118) 및 스위치(120)의 병렬 결합으로 제공된다. 요구되는 이득에 따라, 신호는 증폭기(118)에 의해 증폭되거나 스위치(120)를 통해 바이패스된다. 증폭기(118) 출력으로부터의 신호는 필터(122)에 의해 필터링되어 저잡음 증폭기(124) 및 스위치(126)의 제2 병렬 결합으로 제공된다. 다시, 요구되는 이득에 따라 신호는 증폭기(124)에 의해 증폭되거나 또는 스위치(126)를 통해 바이패스된다. 증폭기(124)로부터의 신호는 위상 동기 루프(PLL) 회로(130)로부터 국부 발진기(LO)를 사용하여 중간 주파수(IF)로 신호를 다운컨버팅하는 믹서(128)로 제공된다. 국부 발진기는 전압-제어된-온도-보상-크리스털-발진기(VCTCXO)로부터 기준 클록으로 위상 동기된다.

믹서(128)로부터의 IF 신호는 밴드패스 필터(134)에 의해 필터링되고, 가변 이득 증폭기(VGA)(136)에 의해 증폭되어, 믹서(140a,140b)로 제공된다. 믹서(140a,140b)는 각각 위상 시프터(142)로부터 동위상 사인파 및 수신기 IF 위상 동기 루프(Rx IF PLL)(144)로부터 직교위상 사인파를 통해 IF 신호를 다운컨버팅한다. 믹서(140a,140b)들 각각으로부터의 베이스밴드 신호는 로패스 필터(146)에 의해 필터링되고 합산기(148)에 의해 DC 오프셋 조정되며, 아날로그-대-디지털 컨버터(ADC)(150)에 의해 샘플링된다. ADC(150a,150b)로부터의 디지털 샘플들은 출력 데이터 및 요구되는 제어 신호들을 발생시키기 위해 샘플들을 처리하는 신호 처리기(160)로 제공된다.

전송 경로 내에서, 신호 처리기(160)로부터의 전송 데이터 샘플들은 데이터 샘플들에 상응하는 아날로그 베이스밴드 신호들을 발생시키는 디지털-대-아날로그 컨버터(DAC)(162a,162b)로 제공된다. DAC(162a,162b) 각각으로부터의 아날로그 신호들은 필터(164)에 의해 필터링되어 믹서(166)로 제공된다. 믹서(166a,166b)는 각각 위상 시프터(168)로부터의 동위상 사인파 및 전송기 IF 위상 동기 루프(Tx IF PLL)(170)로부터의 직교위상 사인파를 통해 필터링된 베이스밴드 신호들을 IF로 업컨버팅한다. 믹서(166a)로부터의 동위상 신호 및 믹서(166b)로부터의 직교위상 신호는 합산기(172)에 의해 합산된다. 그에 따른 IF 신호는 가변 이득 증폭기(VGA)(174)에 의해 증폭되고, 필터(176)에 의해 필터링되며, PLL(130)로부터의 제2 국부 발진기 신호를 가지고 믹서(178)에 의해 업컨버팅된다. 믹서(178)로부터의 무선 주파수(RF) 신호는 드라이버(180)에 의해 증폭되고 듀플렉서(114)를 통해 안테나를 구동하는 전력 증폭기(PA)(182)에 의해 버퍼링된다.

도1은 트랜시버(100) 내의 다양한 제어 루프들을 보여준다. 예를 들어, 수신 신호 경로에서, 하나 또는 그 이상의 이득 제어 루프들은 안테나(116) 및 VGA(136) 이득을 세팅하고(바이패스 또는 LNA 경로 사이에서 선택할 수 있음), 바이어스 제어 루프는 증폭기(118,124)의 바이어스 전류를 세팅하며, 주파수 트랙킹 루프는 VCTCXO(132) 주파수를 세팅하며, DC 오프셋 루프는 필터(146)로부터 필터링된 신호의 DC 오프셋을 제거한다. 특정 구현에서, 필터(146)는 높은 DC 이득을 제공하고 필터링된 신호에서 큰 DC 오프셋을 잠재적으로 발생시킬 수 있는 액티브 필터이다. DC 오프셋 루프는 필터(146)에 의해 발생된 DC 오프셋을 제거하여 오프셋 보상된 신호가 ADC(150a,150b) 입력 범위 내에 있도록 한다. 전송 신호 경로에서, 이득 제어 루프는 VGA(174) 이득을 세팅한다. 다른 트랜시버 구현들은 도1보다 많은, 작은, 또는 상이한 제어 루프들을 포함할 수 있다.

예로서, 신호레벨을 개선된 신호대잡음(SNR) 성능으로 유지하기 위해 수신 신호 경로 내에서 VGA(136) 이득을 설정하는 AGC 루프를 고려해보자. 수신된 신호가 너무 높으면, AGC 루프는 VGA 이득을 감소시킨다. 이와는 달리, 수신된 신호가 너무 낮으면, AGC 루프는 VGA 이득을 증가시킨다. AGC 루프는 신호 레벨이 대략 ADC의 입력에서 일정하도록 요구되는 신호 레벨(즉 방해 신호레벨이 아닌)을 조정한다. 그렇지 않으면, 너무 높은 신호 레벨은 ADC에 의한 클리핑을 야기시키고 너무 낮은 신호 레벨은 잡음 레벨을 증가시켜서, 결과적으로 둘 모두 SNR의 감소를 야기시킨다.

제어 루프의 제어 섹션들은 일반적으로 디지털 회로 내에서(즉 신호 처리기(160)) 구현된다. 루프 제어 회로로부터의 디지털 제어 신호들은 도1에 제시된 다양한 엘리먼트들을 구동하는데 사용되는 대응 아날로그 제어 신호들을 발생시키는 인터페이스 회로로 제공된다. 루프 제어 이론 및 루프 제어 회로의 구현은 공지되어 있으므로 기술하지 않는다.

각각의 트랜시버 디자인은 인터페이스 회로의 성능에 대한 특정 세트의 요구 조건들을 부가한다. 이러한 요구조건들은 일반적으로 응답 시간 및 제어 신호 각각에 대한 리플의 양을 포함한다. 예를 들어, 인터페이스 회로의 대역폭은 일반적으로 제어루프의 폐쇄 루프 대역폭보다 매우 클 것이 요구된다(3배 내지 10배). 이는 인터페이스 회로가 과도한 위상을 제어루프에 부가하지 않고 루프 응답을 왜곡시키지 않기 위해서 요구된다. 또한, 제어신호의 리플은 제어 루프의 성능을 저하시키는 잡음으로서 동작한다. 이러한 리플들은 특정 루프의 요구조건에 의해 규정된 소정 진폭으로 감소될 필요가 있다.

도2A는 기존 제어 루프의 부분에 대한 블록 다이아그램이다. 루프 제어 회로(210)는 인터페이스 회로(220)로 제공되는 디지털 신호를 발생시킨다. 인터페이스 회로(220) 내에서, 펄스 폭 변조(PWM) 또는 "기존의" PDM(222)은 디지털 신호를 수신하고 디지털 신호 값에 상응하는 파형 시퀀스를 발생시킨다. 로패스 필터(224)는 이러한 파형을 수신 및 필터링하여 아날로그 신호를 제공한다. 도2A에 제시된 루프 제어 회로(210)는 도1 및 위에서 제시된 임의의 루프에 대한 루프 제어 회로일 수 있다.

인터페이스 회로(220)는 기존의 PWM 및 PDM과 관련되어 몇 가지 단점이 존재한다. 디지털 신호의 각 디지털 값에 대해서, PWM은 그 디지털 값에 대응하는 특정 파형을 발생시킨다. N-비트 PWM에 대해서, 2N 클록 사이클이 N비트 값을 표현하는데 필요하기 때문에 2N 클록 사이클 주기를 갖는 PWM 파형을 야기시킨다. 각 파형에 대한 하이(1) 및 로우(0) 값들의 수는 입력 디지털 값에 의해 결정된다. PWM으로부터 하이값들은 일반적으로 함께 그룹화된다. 예를 들어, 128 디지털 값은 512 클록 사이클 중 첫 번째 128에 대해 하이인 PWM 파형에 대응한다. 이러한 구현은 PWM 파형의 주기에 상응하는 주기성, 또는 2N 클록 사이클의 주기성을 갖는 아날로그 신호를 야기시킨다.

펄스 폭 및 펄스 밀도 변조기의 중요한 특성은 하이 값들이 파형 내에 균일하게 분포되어 있을 때 최소 리플 양이 발생한다는 것이다. 이는 변조기 출력에 결합된 필터의 커패시터가 하이 및 로우 값들의 각각의 세트를 충전 및 방전하는데 동일한 시간 양을 가지기 때문이다. 하이 값이 균일하게 있으면, 결과 출력의 최소치가 로우로부터 하이로의 전이 바로 전에 발생하고, 최대치는 하이로부터 로우로의 전이 바로 전에 발생하여 정상 상태에서 최소 리플 양을 야기시킨다. 하이 값들이 균일하게 분포되지 않으면, 커패시터는 비대칭 충전 및 방전 시간을 가지기 때문에 증가된 정상 상태 리플 진폭을 야기시킨다.

도2B는 본 발명의 인터페이스 회로를 포함하는 제어 루프의 부분에 대한 블록 다이아그램이다. 루프 제어 회로(230)는 인터페이스 회로(240)에 제공되는 디지털 신호를 발생시킨다. 인터페이스 회로(240) 내에, 시간 응답 조정 회로(242)는 디지털 신호를 수신하고 아래에서 설명되듯이 조정된 시간 응답을 갖는 "조정된" 신호를 발생시킨다. 시그마-델타 변조기(244)는 조정된 신호를 수신하고 조정된 신호의 값에 상응하는 파형 시퀀스를 구성하는 변조기 신호를 발생시킨다. 로패스 필터(246)는 파형을 수신 및 필터링하여 아날로그 신호를 제공한다.

비용을 절감시키고 인터페이스 회로를 구현하는데 필요한 컴포넌트들의 수를 최소화하기 위해서, 인터페이스 회로의 일부 엘리먼트들은 디지털 하드웨어(즉, 신호 처리기(160) 내에서)에서 구현되고, 일부는 아날로그 컴포넌트를 사용하여 구현된다. 제어될 회로 엘리먼트들은 일반적으로 본질상 아날로그이기 때문에, 아날로그 컴포넌트들은 디지털 신호로부터 아날로그 신호를 발생시키기 위해 요구되는 신호 조건을 제공한다. 구현에 있어서, 시간 응답 조정 회로(242) 및 시그마-델타 변조기(244)는 시스템에 의해 요구되는 다른 기능을 또한 제공하는 디지털 IC 내에서 통합된다.

도3A는 본 발명의 인터페이스 회로(310)의 특정 실시예에 대한 다이아그램이다. 인터페이스 회로(310)는 시간 응답 조정 회로(312), 1차 시그마-델타 변조기(314), 및 2차 로패스 필터(316)를 포함한다. 디지털 신호는 조정된 신호를 발생시키는 시간 응답 조정 회로(312)에 제공된다. 실시예에서, 조정된 신호는 고속 또는 수정된 시간 응답을 제공하는 디지털 신호에 대한 수정을 포함한다.

시간 응답 조정 회로(312) 내에서, 디지털 신호(X[n])가 이득 엘리먼트(320) 및 지연 엘리먼트(322)로 제공된다. 이득 엘리먼트(320)는 고정되거나 프로그램화될 수 있는 스케일 인자(Av)로 디지털 신호를 스케일한다. 특정 실시예에서, 스케일링 인자는 2이다. 지연 엘리먼트(322)는 고정되거나 프로그램화 될 수 있는 시간 주기만큼 디지털 신호를 지연시킨다. 스케일링 인자 및 지연량은 인터페이스 회로가 사용되는 특정 응용예의 요구조건들에 따른다. 이득 엘리먼트(320)로부터의 스케일된 신호 및 지연 엘리먼트(322)로부터의 지연된 신호는 스케일된 신호로부터 지연된 신호를 감산하는 합산기(324)로 제공된다. 실시예에서, 합산기(324)는 출력을 N-비트 값들로 제한하여 뒤이은 시그마-델타 변조기(314)의 입력 범위 내에 존재하게 하는 포화(saturation) 합산기이다. 합산기(324)로부터의 조정된 신호(y[n])는 시그마-델타 변조기(314)로 제공된다.

시그마-델타 변조기(314) 내에서, 조정된 신호는 조정된 신호를 레지스터(332)로부터의 N 최하위 비트들(LSB)과 가산하는 합산기(330)로 제공된다. 합산기로부터의 (N+1) 비트 출력은 레지스터로 제공되어 저장된다. 레지스터(332)로부터의 최상위 비트(MSB)는 필터(316)로 제공되는 변조기 신호(k[n])를 포함한다. 도3A에 제시된 실시예에서, 지연 엘리먼트(322) 및 레지스터(332) 모두 동일한 클록 신호(CLK)에 의해 클록화된다.

필터(316)는 변조기(314)로부터 변조기 신호를 필터링하여 아날로그 신호를 발생시킨다. 도3A에 제시된 실시예에서, 필터(316)는 2개의 레지스터 및 2개의 커패시터를 갖는 2차 로패스 필터이다.

도3B는 시간 응답 조정 회로(342a)의 다른 특정 실시예에 대한 다이아그램이다. 인터페이스 회로(342a)는 도3A에 제시된 인터페이스 회로(312)의 이득 엘리먼트(320), 지연 엘리먼트(322), 및 합산기(324)에 대응하는 이득 엘리먼트(350), 지연 엘리먼트(352), 및 합산기(354)를 포함한다. 인터페이스 회로(342a)는 또한 (Av-1)의 이득을 갖고 회로 입력 및 지연 엘리먼트(352) 사이에 결합된 제2 이득 엘리먼트(356)를 포함한다. 제2 이득 엘리먼트(356)는 합산기(354)로부터의 조정된 신호(y[n])가 지연 엘리먼트(352)에 의해 제공된 지연 주기 MㆍTs 후에 디지털 신호(x[n])와 동일하게 되도록 적절한 이득을 제공한다.

도3C는 시간 응답 조정 회로(342b)의 또 다른 실시예에 대한 다이아그램이다. 인터페이스 회로(342b)는 도3B의 이득 엘리먼트(350), 지연 엘리먼트(352), 및 합산기(354)를 포함한다. 인터페이스 회로(342b)는 또한 이득 엘리먼트(350)의 출력과 결합된 비-반전 입력 및 상기 회로입력에 결합된 반전 입력을 갖는 제2 합산기(358)를 포함한다. 인터페이스 회로(342b)는 도3B와 동일한 전달 함수를 제공한다.

시간 응답 조정 회로

PWM, PDM, 또는 시그마-델타 변조기로부터의 파형들은 그 본질상 디지털이고 요구되는 아날로그 신호를 제공하기 위해 아날로그 필터에 의해 필터링된다. 기존에, 디지털 신호에서의 계단 변화로 기인한 아날로그 신호의 계단 응답은 아날로그 필터에 의해 결정된다. 광대역폭을 갖는 필터는 고속 응답 시간을 제공하지만, 아날로그 신호에서의 큰 리플 진폭을 초래한다. 따라서, 상기 필터는 일반적으로 수용가능한 리플 진폭을 초래하는(즉, 리플 규격을 만족시키는) 가장 높은 대역폭에서 세팅된다. 이러한 필터 대역폭과 관련된 시간 응답은 인터페이스 회로에 의해 달성가능한 가능한 가장 빠른 응답 시간을 나타낸다.

넓은 루프 대역폭을 갖는 제어 루프들과 같은 일부 응용예에서, 기존의 인터페이스 회로를 통해 달성가능한 응답 시간은 수용가능하지 않다. 예를 들어, 도1을 참조하면, 전송 AGC 루프의 드라이버(180)는 고속 전이 시간을 갖는 디지털 신호에 의해 제어된다. 드라이버(180)가 저 이득 상태에 및 고 이득 상태 사이에서 스위칭될 때, 신호 경로에서의 이득이 변화하고 VGA(174)의 이득을 조정함으로써 보상될 필요가 있다. 만약 Tx AGC 제어 신호가 저속 응답 시간을 가지면(즉, 이러한 제어 신호를 제공하는 아날로그 필터에 의해 부과된 제한들로 인해), 드라이버 및 VGA(174)의 응답 시간은 매칭되지 않는다. 이러한 미스매치는 드라이버(180) 이득이 스위칭될 때 신호 이득의 범프(bump)를 야기시킨다.

도4A는 기존 인터페이스 회로의 계단 응답을 도시한다. 디지털 신호가 시간 t1에서 출발 값으로부터 최종값으로 전이한다. 필터 출력은 t1 바로 후에 출발값(Vstart)으로부터 전이하기 시작하여 점근적으로 Vfinal 에 접근한다. 시간 t3에서, 디지털 신호는 다시 변화하고 필터는 그에 따라 응답한다.

도5는 본 발명의 시간 응답 조정 회로(512)의 특정 실시예에 대한 다이아그램을 보여준다. 특정 필터에 대해서, 응답 시간은 시간 응답 조정 회로에 의해 발생된 신호(또는 펄스)를 통해 변조기를 일시적으로 오버드라이빙함으로써 증가(또는 고속화)될 수 있다. 시간 응답 조정 회로(512) 내에서, 디지털 신호는 이득 엘리먼트(520) 및 지연 엘리먼트(522)로 제공된다. 도5에 제시된 실시예에서, 이득 엘리먼트(520)는 스케일 인자 2만큼 디지털 신호(x[n])을 스케일하고 지연 엘리먼트(522)는 클록 신호(CLK)의 M 사이클만큼 디지털 신호를 지연시킨다. 스케일링 인자 및 지연 주기는 프로그램화될 수 있다. 이득 엘리먼트(520)로부터 스케일된 신호 및 지연 엘리먼트(522)로부터 지연된 신호는 스케일된 신호로부터 지연된 신호를 감산하는 포화 합산기(524)로 제공된다. 합산기(524)는 조정된 신호(y[n])를 N-비트 값으로 제한한다.

특정 실시예에서, 디지털 신호(x[n])은 부호변화가 없는 이진 형태이다(즉, 9비트 구현에 있어서 0에서 512까지의 범위를 가짐). 다른 특정 실시예에서, 디지털 신호(x[n])은 부호변화를 갖는 이진 수이다(9비트 구현에 있어서 -256에서 256까지의 범위를 가짐). 디지털 신호(x[n])는 지연 엘리먼트 및 뒤이은 변조기를 클록하는데 사용되는 클록 신호(CLK)보다 훨씬 낮은 속도로 변화된다. 예를 들어, 9비트 변조기에 있어서 디지털 신호는 클록 신호의 1/512의 속도 또는 그 이하의 속도로 변화된다.

시간 응답 조정 회로(512)는 다음 방식으로 동작한다. MㆍTs의 소정 지연 주기에 있어서(여기서 M은 지연 클록 사이클들의 수이고 Ts는 클록 신호(CLK)의 주기임), 시간 응답 조정 회로(512)로부터 조정된 신호(y[n])는 다음과 같다;

y[n]=2x[n]-x[n-M] 또는, (1)

y[n]=x[n]+(x[n]-x[n-M]) (2)

여기서 x[n-M]은 M 클록 주기들에 의해 지연된 디지털 신호이다. 특정 n에 대해서 y[n]은 x[n]과 동일하거나 또는 이보다 크다. 사실, y[n]은 지연주기동안 x[n]의 현재 디지털 값보다 (x[n]-x[n-M])만큼 크다. 지연 주기 종결시에, x[n]의 현재 디지털 값이 지연 엘리먼트(522)로부터 일단 제공되면, 합산기(522)로부터의 출력은 y[n]=x[n]이 된다. 따라서, 응답 시간 조정 회로(512)는 계단 응답과 동일한 진폭을 갖는 "오버드라이브" 펄스 트레인(p[n])(즉, p[n]=△x[n]=x[n]-x[n-M])을 발생시킨다. 각각의 오버드라이브 펄스는 지연 엘리먼트에 의해 결정된 MㆍTs 듀레이션을 갖는다.

변조기를 통해 시간 응답 조정 회로에 결합된 필터는 현재 및 이전 입력 값 사이의 차이(즉, y[n]-y[n-1])에 응답한다. 시간 응답 조정 회로(512)는 효과적으로 (y[n]-y[n-1])=(x[n]-x[n-1])로부터 (y[n]-y[n-1])=2(x[n]-x[n-1])로 지연 주기 동안 필터 드라이브를 배가시킨다. 이러한 높은 y[n]은 필터에 대한 보다 많은 드라이브를 야기시키고, 이는 응답 시간을 가속시킨다. MㆍTs후, 지연 주기 종결시에, 시간 응답 조정 회로(512)는 입력 디지털 값에 대해 영향을 미치지 않고 y[n]은 x[n]이 된다.

도4B는 시간 응답 조정 회로(512)를 사용하는 인터페이스 회로의 계단 응답을 플랏하는 도이다. 처음에, 조정된 신호는 출발값에서 새로운 값으로 시간 t1에서 전이한다. 그러나 도4B에 제시된 바와 같이, 변조기는 시간 응답 조정 회로(512)에 의해 (2Vfinal-Vstart)에 상응하는 조정된 값으로 오버드라이브되고, 이는 디지털 신호(x[n-M])의 변화의 2배이다. 필터로부터의 아날로그신호는 t1 바로 직후 출발값(Vstart)으로부터 (2Vfinal-Vstart)로 전이를 시작하고 고속으로 Vfinal에 도달한다. 아날로그 신호가 시간 t4에서 Vfinal로 접근함에 따라, 오버드라이브 펄스는 제거되고 조정된 신호는 Vfinal 값으로 리턴한다. 그리고 나서 필터는 그 최종값 Vfinal로 전이한다. 도4B에 제시된 바와 같이, 오버드라이브 펄스는 입력값의 변화(△V=Vfinal-Vstart)와 동일한 진폭 및 (t4-t1)의 듀레이션을 갖는다.

입력 디지털 신호에서의 일부 변화에 있어서, 오버드라이브 펄스의 진폭은 도4B에 제시된 바와 같이 디지털 신호의 변화와 동일하다(즉, p[n]=△x[n]=x[n]-x[n-M]). 이러한 결과는 (p[n]=△x[n]) 진폭을 갖는 오버드라이브 펄스를 제공하기 위해서 현재 디지털 값으로부터 충분한 헤드룸이 존재하는 경우에 발생한다. 특히, 만약 (x[n-M]+2△x[n])이 변조기의 입력 범위 내에 존재하면, 오버드라이브 펄스 진폭은 계단 변화와 동일하다. 이러한 조건을 만족시키는 디지털 신호의 모든 변화들에 있어서, 응답 시간의 개선량은 (이론적으로) 동일하다.

그러나 뒤이은 회로(예를 들면, 시그마-델타 변조기)의 유효 입력 범위 내로 조정된 신호(y[n])을 유지하기 위해서 합산기(524)에 의해 이루어지는 포화로 인해서, 오버드라이브 펄스 진폭은 디지털 신호의 일부 변화들에 대해 △x[n]보다 작다. 이는 △x[n] 진폭을 갖는 오버드라이브 펄스를 제공하기 위해 x[n]의 현재 값으로부터 불충분한 헤드룸이 존재하는 경우에 발생한다. 그리고 나서 오버드라이브 펄스는 제공되는 헤드룸과 관련된 양에 의해 클리핑된다. 펄스 진폭이 클리핑되면, 펄스 진폭이 클리핑되지 않을 때만큼 빠르지 않다. 응답 시간을 추가로 개선하기 위해서(즉, 고속화하기 위해), 오버드라이브 펄스의 듀레이션이 증가될 수 있다. 실시예에서, 오버드라이브 펄스 듀레이션이 클리핑 양에 따라 (M의 공칭 펄스 듀레이션으로부터) 증가된다. 예를 들어, 절반만큼 클리핑된 펄스(즉, p[n]=0.5△x[n])는 1/4만큼 클리핑된 펄스(즉, p[n]=0.75△x[n])보다 긴 듀레이션을 갖는다.

도8A 및 8B는 아날로그 신호에서 계단 응답에 대한 클리핑의 효과를 보여준다. 도8A는 오버드라이브 펄스가 클리핑되지 않는 경우에 있어서 계단 응답의 플랏을 보여주고, 도8B는 오버드라이브 펄스가 클리핑되는 경우에 있어서 계단 응답의 플랏을 보여준다. 도8A에 대응하는 특정 구현에 있어서, 오버드라이브 펄스가 클리핑되지 않으면, 오버드라이브 펄스 듀레이션은 112 칩 ×8 또는 11.4㎲이며, 최종 값의 70%까지의 계단 응답 시간은 대략 10㎲이다. 동일한 구현에 있어서, 오버드라이브 펄스가 100퍼센트 클리핑되면(즉, 어떠한 오버드라이브 펄스도 제공되지 않으면), 최종 값의 70%까지의 계단 응답 시간은 대략 24㎲이다. 위에서 지적된 바와 같이, 계단 응답 시간은 클리핑이 발생하는 경우 오버드라이브 펄스 듀레이션을 증가시킴으로써 개선될 수 있다.

도3 및 5에 제시된 바와 같이, 응답 시간은 이득 엘리먼트의 이득 또는/및 지연 엘리먼트의 지연을 조정함으로써 제어될 수 있다. 특정 이득에 대해서, 지연이 너무 짧으면, 짧은 오버드라이브 펄스가 발생되고 시간 응답 조정 회로는 응답 시간에 대해 보다 적은 영향을 미친다. 지연이 0인 경우(M=0), 시간 응답 조정회로의 출력은 단순히 x[n]이고 어떠한 영향도 가지지 않는다. 시간 응답을 가속하기 위해서, 상기 지연은 가능한 한 많이 증가되어야 한다. 그러나 지연이 너무 길게 되면, 너무 많은 오버드라이브로 인해 아날로그 신호가 최종값을 오버슈트하는 바람직하지 않은 결과를 야기할 수 있게 된다. 오버슈트없이 가능한 가장 빠른 응답 시간을 초래하는 지연은 시뮬레이션 또는 계산에 의해 실험적으로 결정될 수 있다.

유사하게, 특정 지연 주기 MㆍTs 에 대해서, 이득 엘리먼트의 이득이 너무 작으면(즉, 거의 제로에 가까움), 작은 오버드라이브 펄스가 발생되고 시간 응답 조정 회로는 응답 시간에 거의 영향을 주지 않는다. 이득이 제로로 설정되면, 시 간 응답 조정 회로는 응답 시간에 어떠한 영향도 주지 않는다.

실시예에서, 이득 엘리먼트 및 지연 엘리먼트는 모두 프로그램화가 가능하다. 다른 실시예에서, 이득 지연은 디지털 신호의 변화량에 따라 조정된다. 예를 들어, 높은 이득 및/또는 긴 지연은 큰 변화를 위해 사용되고 낮은 이득 및/또는 짧은 지연은 작은 변화를 위해 사용된다. 또 다른 실시예에서, 입력 디지털 신호에서의 각각의 변화는 오버슈트없이 가장 빠른 응답 시간을 야기시키는 한 세트의 프로그램된 이득 및 지연값과 관련될 수 있다.

도3 및 5는 본 발명에 따른 시간 응답 조정 회로의 일 실시예를 보여준다. 시간 응답 조정 회로는 디지털 회로로 구현될 수 있다. 시간 응답 조정 회로는 랜덤 액세스 메모리(RAM) 또는 판독 전용 액세스 메모리(ROM)와 같은 메모리 엘리먼트로 구현될 수 있다. 디지털 값에서의 특정 변화에 대해서, 메모리 엘리먼트는 요구되는 시간 응답 특성(즉, 오버슈트 없는 고속 응답 시간)을 제공하는 일련의 값들을 제공한다.

비록 본 발명의 시간 응답 조정 메커니즘이 디지털 회로를 사용하여 구현되는 것으로 기술되었지만, 본 발명은 프로세서(즉, 신호 처리기(160))에 의해 실행되는 마이크로 코드 또는 소프트웨어로 구현될 수도 있다. 또한, 시간 응답 조정 메커니즘이 오버드라이브 펄스가 고속 응답 시간을 획득하기 위해 발생되는 특정 응용예에 대해 기술되었다. 본 발명의 시간 응답 조정 메커니즘은 특정 파형 특성을 획득하기 위해 시간 응답 파형을 조정하는 것과 같은 다른 응용예들에 사용될 수 있다. 따라서, 본 발명의 시간 응답 조정 메커니즘은 기존의 변조기 및 필터 조합에 의해 발생되는 아날로그 신호의 시간 응답 특성에 대한 모든 변형을 포함한다.

시그마-델타 변조기

시그마-델타 변조기는 그 입력에서 조정된 신호(y[n])에 상응하는 하이 및 로우 값들의 시퀀스(즉, 출력 파형 시퀀스)로 구성되는 변조기 신호(k[n])를 제공한다. 하이 값들은 출력 파형에서 균일하게 분포된다. 이러한 특성은 변조기에 결합된 필터의 커패시터가 하이 및 로우값 각각의 세트를 충전 및 방전하는데 동일한 시간량을 가지기 때문에 작은 리플 진폭을 야기시킨다.

도6은 제1차 시그마-델타 변조기(600)의 특정 실시예를 보여주는 도이다. N-비트 조정된 신호(y[n])가 합산기(612)로 제공되고 상기 합산기는 이러한 신호를 레지스터(614)로부터 N 최하위 비트들(LSB)을 통해 합산한다. 합산기(612)로부터의 최상위 비트(MSB)는 배타적 논리합(XOR) 게이트(616)의 입력으로 제공되고, 합산기(612)로부터의 N 최하위 비트들은 레지스터(614)로 전달되어 저장된다. 극성 제어 신호(Polarity)는 XOR 게이트(616)의 제2 입력으로 제공된다. XOR 게이트(616)는 극성 제어 신호의 상태(예를 들면, 하이=토글, 로우=비 토글)에 따라 합산기(612)로부터의 MSB의 극성을 토글한다. XOR 게이트(616)로부터의 출력은 레지스터(618)로 제공되고 상기 레지스터는 그 출력을 클록 신호(CLK)와 동기시킨다. 레지스터(618)로부터의 출력은 시그마-델타 변조기(600)로부터의 변조기 신호를 포함한다.

시그마-델타 변조기(600)는 하이 값들 사이의 공간을 균일하게 분포시켜 기존의 PDM에 비해 개선된 정상상태 리플 성능을 제공한다. 분석은 9비트 분석능(N=9)에서 시그마-델타 변조기가 대략 인자 3 정도로 열악한 피크-투-피크 리플 진폭을 감소시킬 수 있음을 보여준다.

오버샘플링에 의해 리플 에너지를 주파수상에서 균일하게 분포시킬 뿐만 아니라, 시그마-델타 변조기(600)는 또한 피드백을 이용하여 리플 에너지를 노이즈 새이핑(noise shape)한다. 이러한 노이즈 새이핑을 통해, 리플 에너지의 대부분은 고 주파수대로 이동하고 뒤이은 필터에 의해 필터링되며, 결과적으로 관심의 대상이 되는 필터링되지 않는 저 주파수에서 리플이 감소하게 된다. 시그마-델타 변조기(600)에 의해 노이즈 새이핑은 다음 표현으로 제시된다.

K(z)=z-1Y(Z)+(1-z-1)EQ(z) (3)

여기서 Y(z),K(z), 및 EQ(z)는 변조기 입력, 변조기 출력, 및 양자화 에러의 z-변환이다. 변조기 전달 함수(HY(z)=K(z)/Y(z))는 다음과 같다;

HY(z)=z-1 (4)

그리고 양자화 에러 함수(HE(z)=K(z)/EQ(z))는 다음과 같다;

HE(z)=(1-z-1) (5)

z-1는 DC 주파수에서 1이 되고, fCLK/2에서 -1이 되기 때문에, 양자화 에러 함수(HE(z))는 DC 주파수에서 제로 이득(또는 무한 감쇠)을 제공하고 저 주파수에서 큰 감쇠를 제공하며, 고 주파수에서 상대적인 증폭을 제공한다. 양자화 잡음은 필터링이 보다 쉽게 이루어지는 곳에서 저주파수로부터 고주파수로 효과적으로 이동된다.

단일 차수 시그마-델타 변조기는 각각의 유효 입력 디지털 값에 대해 특정 파형을 출력한다. 각 파형은 파형의 하이 및 로우 값들의 위치에 따라 특정한 리플 특성을 갖는다.

도8C 및 8D는 2개의 특정 인터페이스 회로 구현에 있어서 모든 가능한 입력 디지털 값에 대한 피크-투-피크 리플 진폭을 플랏하는 도이다. 도8C에 제시된 바와 같이, 시그마-델타 변조기는 9비트 분석능을 갖는다. 리플 진폭은 입력 디지털 값에 따라 변화하고 0 및 511의 극값(extreme value) 근처에서 더욱 높다. 5 내지 508의 입력 값에 대해, 열악한 경우 리플 진폭은 도8C에서 1.7mV 이다. 리플 진폭은 추가적인 필터링을 제공함으로써 감소될 수 있다(즉, 시그마-델타 변조기에 결합된 필터의 대역폭을 낮춤). 도8C와 동일한 인터페이스 회로 구현에 있어서, 필터 대역폭이 폴의 위치를 p1=9.33kHz 및 p2=54.34kHz 에서 p1=624Hz 및 p2=32.48kHz로 이동함으로써 대역폭이 감소될 때, 열악한 경우 리플 진폭은 300㎶로 감소된다.

리플 성능은 변조기 타입, 로패스 필터의 대역폭, 및 변조기 클록의 속도에 따른다. 하나의 LSB의 100% 이하의 리플에 대해, 제2차 RC-RC 필터로부터 아날로그 신호의 리플량은 다음 관계식을 따른다;

계단 사이즈의 %로서의 리플 ≒ 480%ㆍ(2NㆍfC/fCLK)2 (6)

또는 등가적으로

풀 스케일의 %로서의 리플 ≒ 480%ㆍ2N(fC/fCLK)2 (7)

여기서, fC는 필터의 코너 주파수이다. 이러한 관계식으로부터, 시그마 델타 변조기의 클록 주파수(fCLK)를 가속시키면 리플량의 감소를 초래함을 알 수 있다. 리플 성능에서의 개선은 아날로그 필터의 대역폭을 증가시킴으로써 고속 응답 시간과 타협된다.

비록 본 발명은 제1차 시그마-델타 변조기와 관련되어 기술되었지만, 고차 시그마-델타 변조기(즉, 2차 또는 3차 변조기)가 사용될 수도 있다. 일반적으로 고차 시그마-델타 변조기는 보다 많은 인-밴드 양자화 잡음을 고주파수로 밀어내고, 여기서는 필터링이 보다 쉽게 수행된다. 시그마-델타 변조기의 차수가 아날로그 필터의 차수보다 높아지면, 아웃-오브-밴드 양자화 잠음이 충분히 필터링되지 않고 아날로그 신호가 아웃-오브 밴드 잡음의 상당량을 포함할 수 있게 되어 시스템의 성능을 저하시킬 수 있다. 시그마-델타 변조기의 차수는 사용되는 아날로그 필터의 차수를 고려하여 선택된다.

본 발명의 시간 응답 조정 회로는 시그마-델타 변조기와 함께 사용되는 경우에 보다 개선된 성능을 제공할 수 있다. 그러나 시간 응답 조정 회로는 PWM, PDM, 또는 M-비트 DAC와 함께 사용될 수 있다.

아날로그 필터

단일 차수 로패스 필터는 일반적으로 변조기로부터 변조기 신호를 필터링하기 위해 사용된다. 이러한 단일 차수 필터는 하나의 레지스터 및 하나의 커패시터로 구현될 수 있다. 비록 단일 차수 필터가 낮은 컴포넌트 카운트를 초래하지만, 응답 시간 및 리플 성능이 일부 응용예들에서는 만족스럽지 못하다.

본 발명과 관련하여, 2차 또는 그 이상의 고차 필터가 고속 응답 시간 및/또는 작은 리플량을 제공하는데 사용될 수 있다. 2차 로패스 필터를 사용함으로써 단일 차수 필터에 비해 이루어지는 성능 개선이 아래에서 기술된다. 특정 실시예에서, 2차 필터는 도3A에 제시된 바와 같이 2개의 레지스터 및 2개의 커패시터를 갖는 RC-RC 필터로 구현된다. 이러한 구현은 단일 차수 RC 필터보다 단지 약간의 복잡성을 제공하지만 본 발명의 시간 응답 조정 회로와 결합되어 사용되는 경우 상당한 성능개선을 달성할 수 있다.

상당한 동작 범위 상에서(즉, 필터의 폴 주파수(fP=1/RC) 보다 넓은 주파수에 대해서) 1차 RC 필터를 사용하면, 리플은 RC 필터의 컷오프 주파수(fP)에 비례한다. 이는 RC 필터의 주파수 응답 크기가 폴 주파수 위에서 1/f로 떨어지기 때문이다. 아날로그 신호에서의 리플은 파형의 주기와 동일한 가장 낮은 기본 주파수 또는 fripple=fCLK/2N, 을 가지며, 여기서 fCLK는 변조기를 클록시키는데 사용되는 클록 신호의 주파수이다.

2차 로패스 필터의 일반적인 전달 함수는 다음과 같이 표현된다;

H(S)=ωn

2/(s2+2ζωns+ωn

2) (8)

여기서 폴들은 다음과 같이 주어진다;

p1,2=-ζωn ±ωn(ζ2-1)1/2 (9)

도3A에 제시된 2차 RC-RC 로패스 필터에 있어서, ζ〉1, p1 및 p2는 실수이고, 전달 함수는 다음과 같다;

H(s)=p1p2/{(s-p1)(s-p2)} (10)

2개의 폴을 갖는 2차 필터에 있어서, 필터의 주파수 응답은 제1 및 제2 폴 주파수 사이에서 1/f로 떨어지고, 제2 폴 주파수 후에 1/f2으로 떨어진다. 2개 폴들의 주파수들을 리플 컴포넌트보다 작게 선택함으로써(즉, fP1 및 fP2 〈 fripple

), 리플은 40dB/decade 경사도로 감쇠하고, 이는 1차 필터를 통해 달성되는 20dB/decade 경사도보다 빠르다. 리플에서의 개선은 필터의 응답 시간의 개선을 위해 절충된다. 달리 말하면, 특정 리플 요구조건을 만족시키기 위해, 2차 필터의 폴들은 단일 차수 필터의 폴보다 높게 증가될 수 있고, 이를 통해 리플 성능을 희생함이 없이 고속 응답 시간을 달성할 수 있다.

식 (8)을 살펴보면, 자연 주파수(ωn)는 2차 필터의 시간 스케일을 제어한다. 작은 리플 진폭 및 응답 시간에 대한 요구는 이러한 파라미터에 대한 상충하 는 요구조건을 제공한다. 2차 필터에 있어서, 임계 감쇠 상태는 오버슈트 없는 고속 계단 응답을 초래한다. 2차 필터에 있어서, 임계 감쇠 상태는 ζ=1 에 대해서 발생하고, 이는 풀들이 실수축의 동일한 위치(p1=p2)에 위치하는 것을 초래한다.

특정 리플 크기에 대해 고속 응답 시간을 요구하는 응용예에서, RC-RC 필터는 임계 감쇠 상태에 근접하도록(즉, ζ가 가능한 한 1에 근접하도록) 설계될 수 있고, 자연 주파수(ωn)는 특정 리플 성능에 의해 허용되는 만큼 높게 증가될 수 있다. 2차 임계 감쇠 필터를 사용함으로써, 필터의 응답 시간이 LSB의 30%의 리플 진폭 규격에 있어서 단일 차수 필터의 그것에 비해 10배만큼 가속될 수 있다는 것을 분석이 보여준다. 이러한 시간 응답 개선은 보다 작은 리플 진폭에 대해서는 보다 크다.

추가적인 응답 시간의 개선은 고차 필터(예를 들면, 3차, 4차 등)를 통해 달성될 수 있다.

도3A는 레지스터 및 커패시터만으로 구성된 필터의 구현을 보여준다. 다른 리액티브 컴포넌트들(예를 들면, 인덕터)을 사용하는 필터들이 또한 설계될 수 있다. 예를 들어, 2차 필터가 하나의 인덕터 및 하나의 커패시터를 사용하여 설계될 수 있다. LC 필터들은 이러한 필터들에 대한 감쇠 ζ가 ζ〉1로 제한되는 RC 필터들과는 달리 모든 값들을 가질 수 있기 때문에 추가적인 유연성을 제공한다. 따라서, LC 필터는 일부 오버슈트를 갖는 보다 빠른 응답 시간을 제공하기 위해 과소감쇠(즉 ζ〈 1)로 설계될 수 있다. 이러한 필터는 공지된 방식으로 액티브 필터로서 구현될 수도 있다. 다양한 필터 구현들이 본 발명의 영역 내에 존재한다.

인터페이스 회로의 특정 구현

도7은 예를 들어 CDMA 셀룰러 폰용 송신기 AGC 루프로 사용되는 본 발명의 인터페이스 회로(710)에 대한 특정 실시예의 다이아그램을 보여주는 도이다. 인터페이스 회로(710)는 시간 응답 조정 회로(712), 1차 시그마-델타 변조기(714), 및 2차 로패스 필터(716)를 포함한다.

시간 응답 조정 회로(712) 내에서, 디지털 신호(x[n])는 이득 엘리먼트(720) 및 레지스터(722)로 제공된다. 이득 엘리먼트(720)는 2x[n]을 발생시키기 위해 인자 2만큼 스케일링함으로써 디지털 신호를 스케일한다. 레지스터(722)는 버스 상에서 지연값(Delay_Val)에 의해 결정된 지연 주기 후에 디지털 신호(x[n])를 래치한다. 레지스터(722)는 새로운 값이 래치되기 전까지 이전 값을 보유한다. 카운터(726)는 지연 값으로 로딩되고 지연 값에 의해 표시된 지연 주기 후에 레지스터(722)에 대한 인에이블 신호를 제공한다. 이득 엘리먼트(720)로부터의 스케일된 신호 및 지연 엘리먼트(722)로부터 지연 신호는 합산기(724)로 제공되고 합산기는 스케일된 신호로부터 지연된 신호를 감산한다. 합산기(724)는 시그마-델타 변조기(714)의 입력 범위 내의 값을 갖는 N-비트 값을 갖는 조정된 신호(y[n])을 발생시킨다. 조정된 신호는 시그마-델타 변조기(714)로 제공된다.

시그마-델타 변조기(714)는 N=9를 갖는 도6에 제시된 변조기와 그 구현이 유사하다. 로패스 필터(716)는 아날로그 신호를 발생시키기 위해 변조기(714)로부터 변조기 신호를 필터링한다. 도7에 제시된 실시예에서, 로패스 필터(716)는 도3에 제시된 것과 유사한 2차 RC-RC 필터이다.

다수의 셀룰러 전화기들은 하나의 동작 모드 이상에서 동작한다. 예를 들어, 듀얼-밴드 전화기는 디지털 모드 또는 아날로그 모드에서 동작할 수 있다. 디지털 모드는 GSM 신호와 같은 시분할다중접속(TDMA) 신호 또는 코드분할다중접속(CDMA) 신호의 전송에 의해 특성화될 수 있다. 아날로그 모드는 주파수 변조(FM) 신호 또는 진폭 변조 신호(AM)의 전송에 의해 특성화될 수 있다.

종종, 디지털 모드 및 아날로그 모드의 요구조건들이 상이하다. 예를 들면, 고속 응답 시간은 디지털(예를 들면, CDMA) 모드에서 요구되고 낮은 리플 진폭은 아날로그(예를 들면, FM) 모드에서 요구된다. 결과적으로, 아날로그 필터의 대역폭은 고속 응답 시간을 달성하기 위해서 아날로그 신호에 대해 보다 넓고 낮은 리플 진폭을 달성하기 위해 아날로그 모드에 대해서 보다 좁다. 양 모드에서 동작하는 셀룰러 전화기는 양 모드의 이러한 규격을 만족시킬 것이 요구되고, 결합된 요구조건들은 듀얼-모드 전화기의 설계를 복잡하게 할 수 있다.

도7에 제시된 바와 같이 필터(716)는 스위치(750)와 직렬로 결합된 부가적인 커패시터(748)를 포함하고, 이들의 조합은 커패시터(746)와 병렬로 결합된다. 디지털 모드에서 넓은 대역폭이 고속 응답 시간을 위해 요구될 때, 스위치(750)는 개방되고 커패시터(748)는 RC-RC 필터의 부분이 아니다. 아날로그 모드에서 좁은 대역폭이 작은 리플 진폭을 위해 요구될 때, 스위치는 폐쇄되고 커패시터(748)는 보다 많은 커패시턴스를 제공하기 위해 커패시터(746)와 병렬로 결합된다. 특정 실시예에서, 다음 값들이 레지스터들 및 커패시터들에 대해 선택된다:R1=R2=1㏀, C1=10nF, C2=5nF(CDMA 모드에 대해), 및 C3=120nF(FM 모드에 대해). 이러한 구현을 통해, 동일한 기본 RC-RC 필터(R1=R2=1㏀, C1=10nF, C2=5nF)가 양 모드들에 대해 사용되고 부가적인 커패시터(748)(C3=120nF)가 아날로그 모드를 위해 커패시터(746)와 병렬로 스위치된다. 스위치(750)는 바이폴라 트랜지스터, 메탈-옥사이드-세미컨덕터(MOS) 게이트, 또는 다른 회로 엘리먼트들로 구현될 수 있다.

상이한 시간 응답 특성들은 부분적으로 변조기 클록에 대한 적절한 주파수(fCLK)를 선택함으로써 달성될 수 있다. 특정 실시예에서, 9-비트 변조기 구현에서 CDMA 용으로 fCLK=19.6608MHz 이고 FM 모드 용으로 fCLK=19.68MHz 이다. AGC 제어 루프에 대해서, 가장 낮은 기본 주파수(fCLK/512)는 일반적으로 CDMA 및 FM 모드 모두에 대해서 38.4MHz 이다. 2차 RC 필터의 폴들은 이러한 RC-RC 필터들이 리플 규격을 만족시키도록 적절한 리플 감쇠를 제공하도록 선택된다. FM 모드에 있어서, 리플 규격을 만족시키는 것이 보다 어렵고, FM RC-RC 필터는 보다 많은 감쇠를 제공하도록 디자인된다. 따라서, FM RC-RC 필터의 폴들은 리플 기본 주파수가 p1 및 p2보다 높은 주파수에 존재하고 40dB/decade로 감쇠되도록 낮은 주파수에서 설정된다(예를 들면, p1=624Hz, p2=32.48kHz). CDMA 모드에 있어서, 리플 필터링에 대한 제한은 보다 자유로워서 p1 및 p2가 높은 주파수에서 설정되는 것이 가능하다(예를 들면, p1=9.33kHz, p2=54.34kHz). p1 및 p2 사이에 위치하는 가장 낮은 기본 주파수가 20dB/decade에서 감쇠하고 p1 및 p2보다 큰 주파수에서의 나머지 리플 기본 주파수는 40dB/decade에서 감쇠한다.

이상에서 기술된 실시예는 당업자가 본 발명을 이해하는 것을 돕기 위해 기술되었다. 본 발명은 상기 실시예들로 제한되지 않으며 다양한 변형이 가능하다. 예를 들면, 본 발명은 새이핑된 계단 응답 및 다른 특성을 제공하기 위해 사용될 수 있다. 따라서 본원발명은 하기 청구항에 따라 가장 넓은 범위를 갖는다.

Claims (25)

- 인터페이스 회로로서,디지털 신호를 수신하여 조정된 신호를 발생시키는 시간 응답 조정 회로;상기 시간 응답 조정 회로와 결합되어 상기 조정된 신호를 수신하고 변조기 신호를 발생시키는 변조기; 및상기 변조기에 결합되어 상기 변조기 신호를 수신하고 아날로그 신호를 발생시키는 필터를 포함하며,상기 아날로그 신호는 상기 시간 응답 조정 회로에 의해 수정된 시간 응답을 갖는, 인터페이스 회로.

- 제1항에 있어서,상기 시간 응답 조정 회로는 디지털 신호의 변동에 대응하는 오버드라이브 펄스를 발생시키는 것을 특징으로 하는 인터페이스 회로.

- 제2항에 있어서,상기 오버드라이브 펄스는 상기 디지털 신호의 변동 진폭의 두 배의 진폭을 갖는 것을 특징으로 하는 인터페이스 회로.

- 제2항에 있어서,상기 오버드라이브 펄스는 상기 디지털 신호의 변동 크기에 의해 결정된 진폭을 갖는 것을 특징으로 하는 인터페이스 회로.

- 제2항에 있어서,상기 오버드라이브 펄스는 상기 디지털 신호의 변동 크기에 의해 결정된 시간 듀레이션을 갖는 것을 특징으로 하는 인터페이스 회로.

- 제2항에 있어서,상기 오버드라이브 펄스는 변조기의 입력 범위 내로 클리핑되는 것을 특징으로 하는 인터페이스 회로.

- 제6항에 있어서,상기 클리핑된 오버드라이브 펄스의 시간 듀레이션은 클리핑량에 따라 확장되는 것을 특징으로 하는 인터페이스 회로.

- 제1항에 있어서,상기 변조기는 시그마-델타 변조기인 것을 특징으로 하는 인터페이스 회로.

- 제8항에 있어서,상기 시그마-델타 변조기는 1차 변조기인 것을 특징으로 하는 인터페이스 회로.

- 제1항에 있어서,상기 필터는 2차 RC 로패스 필터인 것을 특징으로 하는 인터페이스 회로.

- 제1항의 인터페이스 회로를 포함하는 제어루프.

- 제1항의 인터페이스 회로를 포함하는 수신기.

- 인터페이스 회로로서,디지털 신호를 수신하여 조정된 신호를 발생시키는 시간 응답 조정 회로;상기 시간 응답 조정 회로에 결합되어 상기 조정된 신호를 수신하고 변조기 신호를 발생시키는 변조기; 및상기 변조기에 결합되어 상기 변조기 신호를 수신하고 아날로그 신호를 발생시키는 필터를 포함하며,상기 시간 응답 조정 회로는,상기 디지털 신호를 수신하여 이를 스케일 인자만큼 스케일링 하는 이득 엘리먼트;상기 디지털 신호를 수신하여 이를 시간 지연만큼 지연시키는 지연 엘리먼트; 및상기 이득 엘리먼트 및 상기 지연 엘리먼트에 결합된 합산기를 포함하고,상기 아날로그 신호는 상기 시간 응답 조정 회로에 의해 수정된 시간 응답을 갖는, 인터페이스 회로.

- 제13항에 있어서,상기 스케일 인자는 2인 것을 특징으로 하는 인터페이스 회로.

- 제13항에 있어서,상기 시간 지연은 제어신호에 대한 값에 의해 결정되는 것을 특징으로 하는 인터페이스 회로.

- 제13항에 있어서,상기 시간 지연은 부분적으로 상기 디지털 신호의 변동 크기에 따라 결정되는 것을 특징으로 하는 인터페이스 회로.

- 제13항에 있어서,상기 스케일 인자 및 시간 지연은 프로그램화가 가능한 것을 특징으로 하는 인터페이스 회로.

- 제13항에 있어서,상기 변조기 신호 및 극성 신호를 수신하여 정확한 극성을 갖는 변조기 신호를 발생시키는 배타적 논리합(XOR) 게이트를 추가로 포함하며,상기 필터는 상기 정확한 극성을 갖는 변조기 신호를 수신하는 것을 특징으로 하는 인터페이스 회로.

- 아날로그 신호의 시간 응답을 수정하는 방법으로서,디지털 신호를 수신하는 단계;상기 디지털 신호 및 상기 디지털 신호의 변동에 따라 조정된 신호를 발생시키는 단계;상기 조정된 신호에 따라 변조기 신호를 발생시키는 단계; 및상기 변조기 신호를 필터링하여 아날로그 신호를 획득하는 단계를 포함하며,상기 아날로그 신호는 수정된 시간 응답을 갖는, 아날로그 신호 시간 응답 수정 방법.

- 제19항에 있어서,상기 아날로그 신호의 시간 응답은 상기 변조기를 클록시키는데 사용되는 클록 신호의 주파수 조정에 의해 수정되는 것을 특징으로 하는 아날로그 신호 시간 응답 수정 방법.

- 제19항에 있어서,상기 아날로그 신호의 시간 응답은 상기 필터의 대역폭 조정에 의해 수정되는 것을 특징으로 하는 아날로그 신호 시간 응답 수정 방법.

- 제19항에 있어서,상기 아날로그 신호의 시간 응답은 상기 디지털 신호의 크기 변동에 따라 수정되는 것을 특징으로 하는 아날로그 신호 시간 응답 수정 방법.

- 제22항에 있어서,상기 아날로그 신호의 시간 응답은 상기 시간 응답 조정 회로의 스케일 인자 및 시간 지연에 따라 추가로 수정되는 것을 특징으로 하는 아날로그 신호 시간 응답 수정 방법.

- 제19항에 있어서,상기 조정된 신호는 상기 디지털 신호의 변동에 상응하는 오버드라이브 펄스를 포함하는 것을 특징으로 하는 아날로그 신호 시간 응답 수정 방법.

- 수신기로서,가변 이득 엘리먼트; 및상기 가변 이득 엘리먼트의 이득을 세팅하는 이득 제어 루프를 포함하며,상기 이득 제어 루프는,디지털 제어 신호를 발생시키는 루프 제어 회로;상기 루프 제어 회로에 결합되어 상기 디지털 제어 신호를 수신하고 조정된 신호를 발생시키는 시간 응답 조정 회로;상기 시간 응답 조정 회로에 결합되어 상기 조정된 신호를 수신하고 변조기 신호를 발생시키는 변조기; 및상기 변조기에 결합되어 상기 변조기 신호를 수신하고 아날로그 제어 신호를 발생시키는 필터를 포함하며,상기 가변 이득 엘리먼트의 이득은 상기 아날로그 제어 신호에 따라 조정되는, 수신기.

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/517,766 US6292122B1 (en) | 2000-03-04 | 2000-03-04 | Digital-to-analog interface circuit having adjustable time response |

| US09/517,766 | 2000-03-04 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| KR20020086601A KR20020086601A (ko) | 2002-11-18 |

| KR100716378B1 true KR100716378B1 (ko) | 2007-05-11 |

Family

ID=24061141

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| KR1020027011563A KR100716378B1 (ko) | 2000-03-04 | 2001-03-02 | 조정가능한 시간 응답을 갖는 디지털-대-아날로그 인터페이스 회로 |

Country Status (9)

| Country | Link |

|---|---|

| US (1) | US6292122B1 (ko) |

| EP (1) | EP1264394B1 (ko) |

| JP (4) | JP2003526979A (ko) |

| KR (1) | KR100716378B1 (ko) |

| CN (1) | CN1423859A (ko) |

| AU (1) | AU2001240015A1 (ko) |

| CA (1) | CA2401893C (ko) |

| HK (1) | HK1054631A1 (ko) |

| WO (1) | WO2001067591A2 (ko) |

Families Citing this family (22)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6369735B1 (en) * | 2000-10-02 | 2002-04-09 | Lsi Logic Corporation | Digital-to-analog converter with high dynamic range |

| JP3772970B2 (ja) * | 2001-10-29 | 2006-05-10 | ソニー株式会社 | D/a変換器および出力増幅回路 |

| KR100493031B1 (ko) * | 2002-11-08 | 2005-06-07 | 삼성전자주식회사 | 액정 표시 장치를 구동하는 반응 시간 가속 장치 및 그 방법 |

| US6940189B2 (en) | 2003-07-31 | 2005-09-06 | Andrew Roman Gizara | System and method for integrating a digital core with a switch mode power supply |

| US6885322B2 (en) * | 2003-08-05 | 2005-04-26 | Motorola, Inc. | Apparatus and method for transmitter phase shift compensation |

| US7203511B2 (en) * | 2004-01-20 | 2007-04-10 | Broadcom Corporation | Control of transmit power of a radio frequency integrated circuit |

| KR100638592B1 (ko) * | 2004-12-11 | 2006-10-26 | 한국전자통신연구원 | Ofdm 시스템의 단말의 수신기용 dc 오프셋 제거 장치및 그 방법 |

| JP4116005B2 (ja) * | 2005-02-18 | 2008-07-09 | シャープ株式会社 | デルタシグマ変調器およびそれを用いたスイッチング増幅回路 |

| US20060217082A1 (en) * | 2005-03-22 | 2006-09-28 | Georg Fischer | Shaping noise in power amplifiers of duplex communication systems |

| US7889019B2 (en) * | 2006-10-13 | 2011-02-15 | Andrew Roman Gizara | Pulse width modulation sequence generating a near critical damped step response |

| WO2008048865A2 (en) * | 2006-10-13 | 2008-04-24 | Ipower Holdings Llc | Pulse width modulation sequence generating a near critical damped step response |

| US7719336B2 (en) * | 2006-10-31 | 2010-05-18 | Andrew Roman Gizara | Pulse width modulation sequence maintaining maximally flat voltage during current transients |

| EP2194684B1 (en) * | 2007-09-26 | 2012-12-19 | Fujitsu Limited | Transmitter-receiver amplifier and method for compensating delay deviation |

| DE102008026019B4 (de) * | 2008-05-30 | 2010-04-08 | Micronas Gmbh | Digital-Analog-Wandler-Schaltungsanordnung |

| JP6308796B2 (ja) * | 2014-02-14 | 2018-04-11 | セイコーNpc株式会社 | ディジタル温度補償発振器 |

| US20150341158A1 (en) * | 2014-05-23 | 2015-11-26 | Mediatek Inc. | Loop gain calibration apparatus for controlling loop gain of timing recovery loop and related loop gain calibration method |

| JP6460458B2 (ja) * | 2014-12-05 | 2019-01-30 | セイコーNpc株式会社 | デジタル温度補償型発振器 |

| JP6425581B2 (ja) * | 2015-02-26 | 2018-11-21 | セイコーNpc株式会社 | ディジタル温度補償発振器 |

| EP3382969A1 (en) * | 2017-03-31 | 2018-10-03 | Intel IP Corporation | Modulation circuit and apparatus, demodulation circuit and apparatus, transmitter, receiver, system, radio frequency circuit, mobile terminal, methods and computer programs for modulating and demodulating |

| KR102553262B1 (ko) * | 2017-11-17 | 2023-07-07 | 삼성전자 주식회사 | 기준 전압 생성기 및 이를 포함하는 메모리 장치 |

| CN111697952B (zh) * | 2020-06-22 | 2023-11-10 | 四川新先达测控技术有限公司 | 一种基于数字pzc系统调节脉冲宽度的方法及系统 |

| CN115514363B (zh) * | 2022-11-09 | 2023-01-20 | 南方电网数字电网研究院有限公司 | 低功耗模数转换电路 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0424294A1 (fr) * | 1989-10-20 | 1991-04-24 | Simu | Panneau isolant à double vitrage avec dispositif motorisé d'écran interposé entre les deux parois transparentes |

| US5504457A (en) | 1990-09-06 | 1996-04-02 | Motorola, Inc. | Pulsed power amplifier for amplifying RF signals |

| WO1999063661A1 (en) * | 1998-06-05 | 1999-12-09 | Nokia Mobile Phones Limited | Control of a variable gain amplifier with a delta sigma modulator d/a converter |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2317851B2 (de) * | 1973-04-10 | 1975-04-24 | Grundig E.M.V. Elektro-Mechanische Versuchsanstalt Max Grundig, 8510 Fuerth | Digital-Analog-Wandler |

| JPH0758912B2 (ja) * | 1986-12-29 | 1995-06-21 | 株式会社アドバンテスト | 高速セトリングd/a変換器 |

| JPS63274214A (ja) * | 1987-05-01 | 1988-11-11 | Kokusai Electric Co Ltd | ディジタル・アナログ変換回路 |

| JPH01186019A (ja) * | 1988-01-20 | 1989-07-25 | Victor Co Of Japan Ltd | D/a変換装置 |

| JPH0225116A (ja) * | 1988-07-14 | 1990-01-26 | Toshiba Corp | シグマーデルタ変調回路 |

| FI87028C (fi) * | 1989-12-22 | 1992-11-10 | Nokia Mobile Phones Ltd | Metod foer att reglera effekt hos en spaenningsstyrd effektfoerstaerkare och koppling foer anvaendning i metoden |

| JPH03201812A (ja) * | 1989-12-28 | 1991-09-03 | Toshiba Corp | レベル調整回路 |

| JPH0537385A (ja) * | 1991-07-08 | 1993-02-12 | Yokogawa Electric Corp | Σδd/a変換器およびσδ変調器 |

| JP3125225B2 (ja) * | 1992-03-25 | 2001-01-15 | オンキヨー株式会社 | デジタル/アナログ変換器 |

| JPH0685680A (ja) * | 1992-09-01 | 1994-03-25 | Yokogawa Electric Corp | Σδデータコンバータ |

| US5337338A (en) * | 1993-02-01 | 1994-08-09 | Qualcomm Incorporated | Pulse density modulation circuit (parallel to serial) comparing in a nonsequential bit order |

| JPH07106964A (ja) * | 1993-08-12 | 1995-04-21 | Toshiba Corp | パルス増幅器およびd/a変換装置 |

| JPH09284586A (ja) * | 1996-04-19 | 1997-10-31 | Toshiba Corp | 垂直鋸波生成回路およびこれを備えた映像モニタ装置並びにテレビジョン受信機 |

| US6148046A (en) * | 1998-01-20 | 2000-11-14 | Texas Instruments Incorporated | Blind automatic gain control system for receivers and modems |

| JPH11317668A (ja) * | 1998-03-03 | 1999-11-16 | Sony Corp | 振幅変換装置及びデータ加算装置 |

| US6147634A (en) * | 1998-12-15 | 2000-11-14 | Sigmatel, Inc. | Method and apparatus for digital to analog conversion with reduced noise |

-

2000

- 2000-03-04 US US09/517,766 patent/US6292122B1/en not_active Expired - Lifetime

-

2001

- 2001-03-02 EP EP01914651A patent/EP1264394B1/en not_active Expired - Lifetime

- 2001-03-02 AU AU2001240015A patent/AU2001240015A1/en not_active Abandoned

- 2001-03-02 KR KR1020027011563A patent/KR100716378B1/ko not_active IP Right Cessation

- 2001-03-02 CA CA002401893A patent/CA2401893C/en not_active Expired - Fee Related

- 2001-03-02 WO PCT/US2001/006803 patent/WO2001067591A2/en active Application Filing

- 2001-03-02 JP JP2001566252A patent/JP2003526979A/ja active Pending

- 2001-03-02 CN CN01808123A patent/CN1423859A/zh active Pending

-

2003

- 2003-09-23 HK HK03106818.4A patent/HK1054631A1/zh unknown

-

2011

- 2011-10-28 JP JP2011237247A patent/JP2012075130A/ja not_active Withdrawn

-

2013

- 2013-09-09 JP JP2013186816A patent/JP5752764B2/ja not_active Expired - Fee Related

-

2015

- 2015-03-11 JP JP2015048790A patent/JP2015146604A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP0424294A1 (fr) * | 1989-10-20 | 1991-04-24 | Simu | Panneau isolant à double vitrage avec dispositif motorisé d'écran interposé entre les deux parois transparentes |

| US5504457A (en) | 1990-09-06 | 1996-04-02 | Motorola, Inc. | Pulsed power amplifier for amplifying RF signals |

| WO1999063661A1 (en) * | 1998-06-05 | 1999-12-09 | Nokia Mobile Phones Limited | Control of a variable gain amplifier with a delta sigma modulator d/a converter |

Also Published As

| Publication number | Publication date |

|---|---|

| US6292122B1 (en) | 2001-09-18 |

| KR20020086601A (ko) | 2002-11-18 |

| WO2001067591A9 (en) | 2003-01-09 |

| WO2001067591A2 (en) | 2001-09-13 |

| JP5752764B2 (ja) | 2015-07-22 |

| HK1054631A1 (zh) | 2003-12-05 |

| CN1423859A (zh) | 2003-06-11 |

| JP2015146604A (ja) | 2015-08-13 |

| JP2003526979A (ja) | 2003-09-09 |

| JP2012075130A (ja) | 2012-04-12 |

| EP1264394A2 (en) | 2002-12-11 |

| AU2001240015A1 (en) | 2001-09-17 |

| CA2401893C (en) | 2008-10-14 |

| EP1264394B1 (en) | 2012-08-22 |

| WO2001067591A3 (en) | 2002-03-07 |

| CA2401893A1 (en) | 2001-09-13 |

| JP2014039276A (ja) | 2014-02-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR100716378B1 (ko) | 조정가능한 시간 응답을 갖는 디지털-대-아날로그 인터페이스 회로 | |

| US6002352A (en) | Method of sampling, downconverting, and digitizing a bandpass signal using a digital predictive coder | |

| CA2739554C (en) | Transmitter architectures for communications systems | |

| US5584059A (en) | DC offset reduction in a zero-if transmitter | |

| AU759884B2 (en) | Method and apparatus for D.C. offset correction in digital-to-analog converters | |

| US6459398B1 (en) | Pulse modulated digital to analog converter (DAC) | |

| EP2304874A2 (en) | Dithering a digitally-controlled oscillator output in a phase-locked loop | |

| KR20030020436A (ko) | 수신기에서 dc 오프셋을 감소시키는 장치 | |

| US8198929B2 (en) | Dynamic element matching for time-to-digital converters | |

| EP1055283B1 (en) | Phase modulating transmitter | |

| US7062244B2 (en) | Speed-up mode implementation for direct conversion receiver | |

| Brannon et al. | Redefining the role of ADCs in wireless | |

| EP0704978B1 (en) | Selection device for selecting electric cells and apparatus using the same | |

| Lee | Quad-band global system for mobile communications complementary metal-oxide-semiconductor transmitter | |

| WO2005064877A1 (en) | Digital rf modulator comprising a phase or frequency return path |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A201 | Request for examination | ||

| E701 | Decision to grant or registration of patent right | ||

| GRNT | Written decision to grant | ||

| FPAY | Annual fee payment |

Payment date: 20130429 Year of fee payment: 7 |

|

| FPAY | Annual fee payment |

Payment date: 20140430 Year of fee payment: 8 |

|

| FPAY | Annual fee payment |

Payment date: 20160330 Year of fee payment: 10 |

|

| FPAY | Annual fee payment |

Payment date: 20170711 Year of fee payment: 11 |

|

| FPAY | Annual fee payment |

Payment date: 20180329 Year of fee payment: 12 |

|

| LAPS | Lapse due to unpaid annual fee |