JP7547518B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP7547518B2 JP7547518B2 JP2023000656A JP2023000656A JP7547518B2 JP 7547518 B2 JP7547518 B2 JP 7547518B2 JP 2023000656 A JP2023000656 A JP 2023000656A JP 2023000656 A JP2023000656 A JP 2023000656A JP 7547518 B2 JP7547518 B2 JP 7547518B2

- Authority

- JP

- Japan

- Prior art keywords

- gate

- electrode

- film

- source

- drain

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10W20/495—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/015—Manufacture or treatment of FETs having heterojunction interface channels or heterojunction gate electrodes, e.g. HEMT

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/47—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having 2D charge carrier gas channels, e.g. nanoribbon FETs or high electron mobility transistors [HEMT]

- H10D30/471—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT]

- H10D30/475—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having wider bandgap layer formed on top of lower bandgap active layer, e.g. undoped barrier HEMTs such as i-AlGaN/GaN HEMTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/40—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels

- H10D30/47—FETs having zero-dimensional [0D], one-dimensional [1D] or two-dimensional [2D] charge carrier gas channels having 2D charge carrier gas channels, e.g. nanoribbon FETs or high electron mobility transistors [HEMT]

- H10D30/471—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT]

- H10D30/475—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having wider bandgap layer formed on top of lower bandgap active layer, e.g. undoped barrier HEMTs such as i-AlGaN/GaN HEMTs

- H10D30/4755—High electron mobility transistors [HEMT] or high hole mobility transistors [HHMT] having wider bandgap layer formed on top of lower bandgap active layer, e.g. undoped barrier HEMTs such as i-AlGaN/GaN HEMTs having wide bandgap charge-carrier supplying layers, e.g. modulation doped HEMTs such as n-AlGaAs/GaAs HEMTs

-

- H10D64/011—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/111—Field plates

- H10D64/112—Field plates comprising multiple field plate segments

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/257—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are characterised by top-view geometrical layouts, e.g. interdigitated, semi-circular, annular or L-shaped electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/258—Source or drain electrodes for field-effect devices characterised by the relative positions of the source or drain electrodes with respect to the gate electrode

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

- H10D64/513—Disposition of the gate electrodes, e.g. buried gates within recesses in the substrate, e.g. trench gates, groove gates or buried gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/517—Gate electrodes for field-effect devices for FETs for IGFETs characterised by the conducting layers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

- H10D62/8503—Nitride Group III-V materials, e.g. AlN or GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/256—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are recessed in semiconductor bodies

Landscapes

- Junction Field-Effect Transistors (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

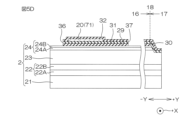

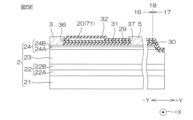

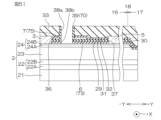

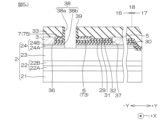

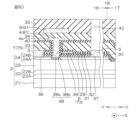

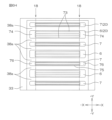

第1保護膜31、第2保護膜32および第1層間絶縁膜33は、本願の装置発明の絶縁層に相当する。第2層間絶縁膜34は、本願の製造方法の発明における第1絶縁層に相当する。第3層間絶縁膜35は、本願の製造方法の発明における第2絶縁層に相当する。

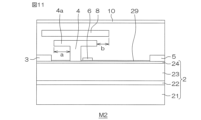

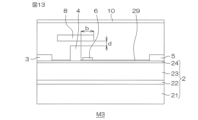

2 半導体積層構造

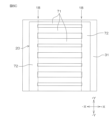

3 ソース電極

4 ゲート電極

4a オーバーラップ部

5 ドレイン電極

6 第1ソースフィールドプレート

7 フローティングプレート

8 第2ソースフィールドプレート

9 ソース配線

10 ドレイン配線

11 ゲート配線

12 ドレインパッド

13 ソースパッド

14 ゲートパッド

15 基板コンタクト部

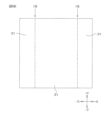

16 アクティブエリア

17 ノンアクティブエリア

18 素子分離線

20 プレート膜

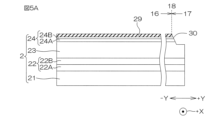

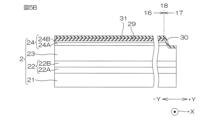

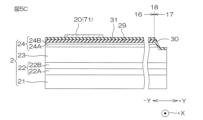

21 基板

22 バッファ層

23 電子走行層

24 電子供給層

25 二次元電子ガス

29 パッシベーション膜

31 第1保護膜

32 第2保護膜

33 第1層間絶縁膜

34 第2層間絶縁膜

35 第3層間絶縁膜

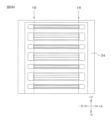

36 ソースコンタクトホール

37 ドレインコンタクトホール

38 ゲート開口部

38a 第1開口部

38b 第2開口部

39 サイドウォール

40 ゲート絶縁膜

41 第1ソースビアホール

42 第1ドレインビアホール

43 第1ゲートビアホール

44 第1SFP用ビアホール

45 第2SFP用ビアホール

51 ソースビアメタル

52 ドレインビアメタル

53 ゲートビアメタル

54 第1SFP用ビアメタル

55 第2SFP用ビアメタル

61 第4層間絶縁膜

62 第2ドレインビアホール

63 基板コンタクトホール

64 基板コンタクトメタル

65 第3保護膜

66 ドレインパッド開口部

67 樹脂層

72 ベース部

73 電極部(第1ソースフィールドプレート6)

74 ベース部

75 電極部(フローティングプレート7)

76 ベース部

81 電極部(ゲート電極4)

82 ベース部

91 電極部(第2ソースフィールドプレート8)

92 ベース部

Claims (16)

- 半導体積層構造上に配置されたソース電極、ゲート電極およびドレイン電極と、前記ソース電極に電気的に接続されたソース配線、前記ドレイン電極に電気的に接続されたドレイン配線および前記ゲート電極に電気的に接続されたゲート配線とを有する半導体装置であって、

第1導電膜と、前記ソース電極と電気的に接続された第2導電膜と、前記ソース電極と電気的に接続された第3導電膜とを含み、

ある断面において、

前記第1導電膜は、前記ソース電極と前記ゲート電極の間に配置され、

前記第2導電膜は、前記ゲート電極と前記ドレイン電極との間に配置され、かつその最上面が前記ゲート電極の最上面よりも前記半導体積層構造に対して近接して配置されており、

前記第3導電膜は、前記ゲート電極の上方であって前記ドレイン配線の下方に配置されており、

前記第1導電膜は、前記半導体積層構造の表面と水平な方向に延出する部分を有し、

前記第2導電膜は、前記半導体積層構造の表面と水平な方向に延出する部分を有し、

前記第3導電膜は、前記半導体積層構造の表面と水平な方向に延出する部分を有し、

前記第1導電膜は、前記第2導電膜と同一のレイヤーに形成されており、

前記ソース配線は、前記ソース電極とは材料が異なるソースビアメタルを介して、前記ソース電極に接続され、

前記ドレイン配線は、前記ドレイン電極とは材料が異なるドレインビアメタルを介して、前記ドレイン電極に接続され、

前記ゲート配線は、前記ゲート電極とは材料が異なるゲートビアメタルを介して、前記ゲート電極に接続されており、

前記ソース電極および前記ドレイン電極は、Ti膜、AlSiCu膜、Ti膜およびTiN膜が、下層からその順に積層されたTi/AlSiCu/Ti/TiN積層膜から構成されている、半導体装置。 - 前記ゲート電極は、TiN膜、W膜、AlCu膜およびTiN膜が、下層からその順に積層されたTiN/W/AlCu/TiN積層膜から構成されている、請求項1に記載の半導体装置。

- 前記ソース配線、前記ドレイン配線および前記ゲート配線は、TiN膜、AlCu膜およびTiN膜が、下層からその順に積層されたTiN/AlCu/TiN積層膜から構成されている、請求項2に記載の半導体装置。

- 前記ソース電極、前記ゲート電極および前記ドレイン電極は、所定定の第1方向に延びており、

前記第3導電膜は、前記ゲート電極の上面に沿って前記第1方向に延びている、請求項3に記載の半導体装置。 - 前記第3導電膜の幅が前記ゲート電極の上面の幅よりも大きく、平面視において、前記第3導電膜の各側縁が、前記ゲート電極の上面の対応する側縁よりも外方に突出している、請求項4に記載の半導体装置。

- 前記第3導電膜の各側縁の前記ゲート電極の上面の対応する側縁からの突出量が、0.3μm以上0.9μm以下である、請求項5に記載の半導体装置。

- 前記ゲート電極の上面と前記第3導電膜の下面との間の距離が、0.15μm以上0.25μm以下である、請求項6に記載の半導体装置。

- 前記ソース電極および前記ドレイン電極は、前記ゲート電極を挟むように、前記ゲート電極から離れて配置されている、請求項7に記載の半導体装置。

- 前記半導体積層構造は、前記ソース電極および前記ドレイン電極で前記ゲート電極を挟むことによって構成された素子構造を含むアクティブエリアと、前記アクティブエリア外のノンアクティブエリアとを含み、

前記ノンアクティブエリアにおいて、前記ソース配線と前記第3導電膜とが電気的に接続されている、請求項8に記載の半導体装置。 - 前記半導体積層構造は、電子走行層と、前記電子走行層上に形成され、前記電子走行層に達する下側開口部が形成された電子供給層とを含み、

前記半導体積層構造上には、前記下側開口部に連通する上側開口部を有する絶縁層が形成されており、

前記絶縁層の表面および前記下側開口部および前記上側開口部からなるゲート開口部の底部および側部を覆うように、ゲート絶縁膜が形成されており、

前記ゲート電極は、前記ゲート開口部内で前記ゲート絶縁膜上に形成されている、請求項9に記載の半導体装置。 - 前記第2導電膜は、前記ゲート電極と前記ドレイン電極との間で前記絶縁層に埋め込まれ、前記ゲート電極から絶縁され、前記ソース電極に電気的に接続されており、

前記第2導電膜は、前記ゲート開口部の一側部の高さ中間位置で露出している、請求項10に記載の半導体装置。 - 前記第1導電膜は、前記ゲート電極と前記ソース電極との間で前記絶縁層に埋め込まれ、前記ゲート電極および前記ソース電極から絶縁されている、請求項11に記載の半導体装置。

- 前記ゲート絶縁膜と前記ゲート開口部の側部との間に配置された絶縁性のサイドウォールをさらに含む、請求項12に記載の半導体装置。

- 前記ゲート電極は、前記ゲート開口部の周縁において、前記ゲート絶縁膜上に形成されたオーバーラップ部を含む、請求項13に記載の半導体装置。

- 前記ソースビアメタル、前記ドレインビアメタルおよび前記ゲートビアメタルは、それぞれソースビアホール、ドレインビアホールおよびゲートビアホールに埋め込まれており、

前記ソースビアメタル、前記ドレインビアメタルおよび前記ゲートビアメタルは、対応するビアホールの側壁に形成されるTiNバリア膜と、前記TiNバリア膜の内側に埋め込まれるタングステンとから構成される、請求項14に記載の半導体装置。 - 前記第1導電膜は、前記ソース電極、前記ゲート電極および前記ドレイン電極のいずれの電極にも電気的に接続されていない、請求項15に記載の半導体装置。

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018007397 | 2018-01-19 | ||

| JP2018007397 | 2018-01-19 | ||

| JP2019565755A JP7208167B2 (ja) | 2018-01-19 | 2018-12-05 | 半導体装置およびその製造方法 |

| PCT/JP2018/044754 WO2019142529A1 (ja) | 2018-01-19 | 2018-12-05 | 半導体装置およびその製造方法 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019565755A Division JP7208167B2 (ja) | 2018-01-19 | 2018-12-05 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2023040154A JP2023040154A (ja) | 2023-03-22 |

| JP7547518B2 true JP7547518B2 (ja) | 2024-09-09 |

Family

ID=67302147

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019565755A Active JP7208167B2 (ja) | 2018-01-19 | 2018-12-05 | 半導体装置およびその製造方法 |

| JP2023000656A Active JP7547518B2 (ja) | 2018-01-19 | 2023-01-05 | 半導体装置 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019565755A Active JP7208167B2 (ja) | 2018-01-19 | 2018-12-05 | 半導体装置およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US11694954B2 (ja) |

| JP (2) | JP7208167B2 (ja) |

| WO (1) | WO2019142529A1 (ja) |

Families Citing this family (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP7177660B2 (ja) * | 2018-10-26 | 2022-11-24 | 株式会社東芝 | 半導体装置 |

| JP7366576B2 (ja) * | 2019-04-15 | 2023-10-23 | 株式会社東芝 | 半導体装置 |

| JP7368107B2 (ja) * | 2019-05-22 | 2023-10-24 | 株式会社東芝 | 半導体装置 |

| CN114664725B (zh) * | 2020-12-23 | 2025-07-29 | 华润微电子(重庆)有限公司 | GaN器件互联结构及其制备方法 |

| JP7705048B2 (ja) * | 2022-03-15 | 2025-07-09 | 富士通株式会社 | 半導体装置、半導体装置の製造方法及び電子装置 |

| US20240128328A1 (en) * | 2022-10-12 | 2024-04-18 | Globalfoundries U.S. Inc. | Device with field plates |

| US20240194680A1 (en) * | 2022-12-09 | 2024-06-13 | Globalfoundries U.S. Inc. | Bidirectional device |

| CN117457735A (zh) * | 2023-12-22 | 2024-01-26 | 英诺赛科(珠海)科技有限公司 | 一种晶体管结构及其制作方法、芯片 |

Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2010047016A1 (ja) | 2008-10-21 | 2010-04-29 | パナソニック株式会社 | 双方向スイッチ |

| JP2010118556A (ja) | 2008-11-13 | 2010-05-27 | Furukawa Electric Co Ltd:The | 半導体装置および半導体装置の製造方法 |

| US20100259321A1 (en) | 2009-04-14 | 2010-10-14 | Triquint Semiconductor, Inc. | Field effect transistor having a plurality of field plates |

| JP2012178595A (ja) | 2005-03-11 | 2012-09-13 | Cree Inc | ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ |

| JP2013131758A (ja) | 2011-12-21 | 2013-07-04 | Power Integrations Inc | 半導体装置 |

| WO2014073295A1 (ja) | 2012-11-09 | 2014-05-15 | シャープ株式会社 | 電界効果トランジスタ |

| WO2014188651A1 (ja) | 2013-05-20 | 2014-11-27 | パナソニックIpマネジメント株式会社 | 半導体装置 |

| JP2016134599A (ja) | 2015-01-22 | 2016-07-25 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5735099B2 (ja) | 2011-04-01 | 2015-06-17 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法ならびに携帯電話機 |

| JP5827529B2 (ja) | 2011-09-15 | 2015-12-02 | ローム株式会社 | 窒化物半導体装置およびその製造方法 |

| JP2014072379A (ja) * | 2012-09-28 | 2014-04-21 | Fujitsu Ltd | 化合物半導体装置及びその製造方法 |

| TWI566328B (zh) * | 2013-07-29 | 2017-01-11 | 高效電源轉換公司 | 具有用於產生附加構件之多晶矽層的氮化鎵電晶體 |

| US10236236B2 (en) * | 2013-09-10 | 2019-03-19 | Delta Electronics, Inc. | Heterojunction semiconductor device for reducing parasitic capacitance |

| JP6332021B2 (ja) * | 2014-12-26 | 2018-05-30 | 株式会社デンソー | 半導体装置 |

| TWI626742B (zh) * | 2015-06-18 | 2018-06-11 | 台達電子工業股份有限公司 | 半導體裝置 |

| JP6642883B2 (ja) * | 2015-10-08 | 2020-02-12 | ローム株式会社 | 窒化物半導体装置およびその製造方法 |

| US9741840B1 (en) * | 2016-06-14 | 2017-08-22 | Semiconductor Components Industries, Llc | Electronic device including a multiple channel HEMT and an insulated gate electrode |

| US9673311B1 (en) * | 2016-06-14 | 2017-06-06 | Semiconductor Components Industries, Llc | Electronic device including a multiple channel HEMT |

| US10263085B2 (en) * | 2016-12-30 | 2019-04-16 | Texas Instruments Incorporated | Transistor with source field plates and non-overlapping gate runner layers |

| US10461161B1 (en) * | 2017-01-23 | 2019-10-29 | Navitas Semiconductor, Inc. | GaN device with floating field plates |

| JP7316757B2 (ja) * | 2018-02-23 | 2023-07-28 | ローム株式会社 | 半導体装置 |

| TWI811394B (zh) * | 2019-07-09 | 2023-08-11 | 聯華電子股份有限公司 | 高電子遷移率電晶體及其製作方法 |

-

2018

- 2018-12-05 WO PCT/JP2018/044754 patent/WO2019142529A1/ja not_active Ceased

- 2018-12-05 JP JP2019565755A patent/JP7208167B2/ja active Active

- 2018-12-05 US US16/962,762 patent/US11694954B2/en active Active

-

2023

- 2023-01-05 JP JP2023000656A patent/JP7547518B2/ja active Active

- 2023-05-16 US US18/318,423 patent/US12199028B2/en active Active

-

2024

- 2024-12-04 US US18/967,990 patent/US20250096110A1/en active Pending

Patent Citations (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012178595A (ja) | 2005-03-11 | 2012-09-13 | Cree Inc | ゲート−ソースフィールドプレートを含むワイドバンドギャップトランジスタ |

| WO2010047016A1 (ja) | 2008-10-21 | 2010-04-29 | パナソニック株式会社 | 双方向スイッチ |

| JP2010118556A (ja) | 2008-11-13 | 2010-05-27 | Furukawa Electric Co Ltd:The | 半導体装置および半導体装置の製造方法 |

| US20100259321A1 (en) | 2009-04-14 | 2010-10-14 | Triquint Semiconductor, Inc. | Field effect transistor having a plurality of field plates |

| JP2013131758A (ja) | 2011-12-21 | 2013-07-04 | Power Integrations Inc | 半導体装置 |

| WO2014073295A1 (ja) | 2012-11-09 | 2014-05-15 | シャープ株式会社 | 電界効果トランジスタ |

| WO2014188651A1 (ja) | 2013-05-20 | 2014-11-27 | パナソニックIpマネジメント株式会社 | 半導体装置 |

| JP2016134599A (ja) | 2015-01-22 | 2016-07-25 | ローム株式会社 | 半導体装置および半導体装置の製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2019142529A1 (ja) | 2019-07-25 |

| US20200357736A1 (en) | 2020-11-12 |

| JP7208167B2 (ja) | 2023-01-18 |

| JP2023040154A (ja) | 2023-03-22 |

| US12199028B2 (en) | 2025-01-14 |

| US20230326846A1 (en) | 2023-10-12 |

| JPWO2019142529A1 (ja) | 2021-01-07 |

| US20250096110A1 (en) | 2025-03-20 |

| US11694954B2 (en) | 2023-07-04 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7547518B2 (ja) | 半導体装置 | |

| JP7539447B2 (ja) | 半導体装置 | |

| CN104009075B (zh) | 半导体装置 | |

| JP5348364B2 (ja) | ヘテロ接合型電界効果半導体装置 | |

| US20220285541A1 (en) | Nitride semiconductor device | |

| JP6496149B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP7464763B2 (ja) | 窒化物半導体装置 | |

| CN101299437A (zh) | 场效应晶体管 | |

| CN107887448A (zh) | 半导体器件 | |

| JP2017073499A (ja) | 窒化物半導体装置およびその製造方法 | |

| CN110785836A (zh) | 半导体装置 | |

| JP7161915B2 (ja) | 半導体装置 | |

| CN105453273A (zh) | 具有匹配阈值电压的集成电路及其制造方法 | |

| TW202145345A (zh) | 氮化物半導體裝置 | |

| JP2008034522A (ja) | 電界効果トランジスタ | |

| JP5985162B2 (ja) | 窒化物系半導体装置 | |

| CN103314438A (zh) | 氮化物系半导体装置 | |

| JP2011192944A (ja) | 半導体装置及び半導体装置の動作方法 | |

| JP7512326B2 (ja) | 半導体装置 | |

| JP6689424B2 (ja) | 半導体装置 | |

| JP2024116730A (ja) | 窒化物半導体装置 | |

| WO2023224092A1 (ja) | 窒化物半導体装置 | |

| JP2024012856A (ja) | 窒化物半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20230105 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20240328 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20240521 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20240822 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20240828 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7547518 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |