JP7319102B2 - 表示パネル - Google Patents

表示パネル Download PDFInfo

- Publication number

- JP7319102B2 JP7319102B2 JP2019113976A JP2019113976A JP7319102B2 JP 7319102 B2 JP7319102 B2 JP 7319102B2 JP 2019113976 A JP2019113976 A JP 2019113976A JP 2019113976 A JP2019113976 A JP 2019113976A JP 7319102 B2 JP7319102 B2 JP 7319102B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- display panel

- groove

- counter electrode

- display area

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000010410 layer Substances 0.000 claims description 407

- 239000002346 layers by function Substances 0.000 claims description 70

- 239000000758 substrate Substances 0.000 claims description 44

- 238000005538 encapsulation Methods 0.000 claims description 32

- 239000000463 material Substances 0.000 claims description 19

- 238000007789 sealing Methods 0.000 claims description 10

- 238000002347 injection Methods 0.000 claims description 6

- 239000007924 injection Substances 0.000 claims description 6

- 229910052751 metal Inorganic materials 0.000 claims description 5

- 239000002184 metal Substances 0.000 claims description 5

- 230000005525 hole transport Effects 0.000 claims description 4

- 239000010408 film Substances 0.000 description 39

- 239000010409 thin film Substances 0.000 description 36

- 239000012212 insulator Substances 0.000 description 28

- 230000004888 barrier function Effects 0.000 description 25

- 101150049521 NDA1 gene Proteins 0.000 description 24

- 101100290413 Schizosaccharomyces pombe (strain 972 / ATCC 24843) mcm2 gene Proteins 0.000 description 24

- 239000003990 capacitor Substances 0.000 description 17

- 238000003860 storage Methods 0.000 description 17

- 239000004417 polycarbonate Substances 0.000 description 15

- 229920000515 polycarbonate Polymers 0.000 description 15

- 239000004642 Polyimide Substances 0.000 description 11

- 229910052581 Si3N4 Inorganic materials 0.000 description 11

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 11

- 230000003287 optical effect Effects 0.000 description 11

- 229920001721 polyimide Polymers 0.000 description 11

- 229920000642 polymer Polymers 0.000 description 11

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 11

- 229910052814 silicon oxide Inorganic materials 0.000 description 11

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 10

- -1 region Substances 0.000 description 10

- 239000004065 semiconductor Substances 0.000 description 10

- 239000002356 single layer Substances 0.000 description 9

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 8

- 239000011229 interlayer Substances 0.000 description 8

- 229910052710 silicon Inorganic materials 0.000 description 8

- 239000010703 silicon Substances 0.000 description 8

- 125000006850 spacer group Chemical group 0.000 description 8

- 239000011368 organic material Substances 0.000 description 7

- 101150104968 NDA2 gene Proteins 0.000 description 6

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 description 6

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 description 6

- BASFCYQUMIYNBI-UHFFFAOYSA-N platinum Chemical compound [Pt] BASFCYQUMIYNBI-UHFFFAOYSA-N 0.000 description 6

- 229920003002 synthetic resin Polymers 0.000 description 6

- 239000010936 titanium Substances 0.000 description 6

- 229910010272 inorganic material Inorganic materials 0.000 description 5

- 239000011147 inorganic material Substances 0.000 description 5

- 230000000149 penetrating effect Effects 0.000 description 5

- 239000002952 polymeric resin Substances 0.000 description 5

- 239000011787 zinc oxide Substances 0.000 description 5

- 229920008347 Cellulose acetate propionate Polymers 0.000 description 4

- 239000004697 Polyetherimide Substances 0.000 description 4

- 239000004734 Polyphenylene sulfide Substances 0.000 description 4

- 229910052782 aluminium Inorganic materials 0.000 description 4

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 4

- 238000005229 chemical vapour deposition Methods 0.000 description 4

- 239000011651 chromium Substances 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 239000010931 gold Substances 0.000 description 4

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 4

- 239000004973 liquid crystal related substance Substances 0.000 description 4

- 239000011777 magnesium Substances 0.000 description 4

- 229920001230 polyarylate Polymers 0.000 description 4

- 229920001601 polyetherimide Polymers 0.000 description 4

- 229920000139 polyethylene terephthalate Polymers 0.000 description 4

- 239000005020 polyethylene terephthalate Substances 0.000 description 4

- 229920000069 polyphenylene sulfide Polymers 0.000 description 4

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 3

- 239000012790 adhesive layer Substances 0.000 description 3

- 239000011248 coating agent Substances 0.000 description 3

- 238000000576 coating method Methods 0.000 description 3

- 239000004020 conductor Substances 0.000 description 3

- 238000010586 diagram Methods 0.000 description 3

- 239000011521 glass Substances 0.000 description 3

- 229910000449 hafnium oxide Inorganic materials 0.000 description 3

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 description 3

- 239000012528 membrane Substances 0.000 description 3

- 238000000034 method Methods 0.000 description 3

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- BPUBBGLMJRNUCC-UHFFFAOYSA-N oxygen(2-);tantalum(5+) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Ta+5].[Ta+5] BPUBBGLMJRNUCC-UHFFFAOYSA-N 0.000 description 3

- 238000005192 partition Methods 0.000 description 3

- 239000002861 polymer material Substances 0.000 description 3

- 230000008569 process Effects 0.000 description 3

- 229910001936 tantalum oxide Inorganic materials 0.000 description 3

- 238000002207 thermal evaporation Methods 0.000 description 3

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 3

- 229920002284 Cellulose triacetate Polymers 0.000 description 2

- VYZAMTAEIAYCRO-UHFFFAOYSA-N Chromium Chemical compound [Cr] VYZAMTAEIAYCRO-UHFFFAOYSA-N 0.000 description 2

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- FYYHWMGAXLPEAU-UHFFFAOYSA-N Magnesium Chemical compound [Mg] FYYHWMGAXLPEAU-UHFFFAOYSA-N 0.000 description 2

- ZOKXTWBITQBERF-UHFFFAOYSA-N Molybdenum Chemical compound [Mo] ZOKXTWBITQBERF-UHFFFAOYSA-N 0.000 description 2

- 229910052779 Neodymium Inorganic materials 0.000 description 2

- URLKBWYHVLBVBO-UHFFFAOYSA-N Para-Xylene Chemical group CC1=CC=C(C)C=C1 URLKBWYHVLBVBO-UHFFFAOYSA-N 0.000 description 2

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 2

- 239000004793 Polystyrene Substances 0.000 description 2

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 2

- NNLVGZFZQQXQNW-ADJNRHBOSA-N [(2r,3r,4s,5r,6s)-4,5-diacetyloxy-3-[(2s,3r,4s,5r,6r)-3,4,5-triacetyloxy-6-(acetyloxymethyl)oxan-2-yl]oxy-6-[(2r,3r,4s,5r,6s)-4,5,6-triacetyloxy-2-(acetyloxymethyl)oxan-3-yl]oxyoxan-2-yl]methyl acetate Chemical compound O([C@@H]1O[C@@H]([C@H]([C@H](OC(C)=O)[C@H]1OC(C)=O)O[C@H]1[C@@H]([C@@H](OC(C)=O)[C@H](OC(C)=O)[C@@H](COC(C)=O)O1)OC(C)=O)COC(=O)C)[C@@H]1[C@@H](COC(C)=O)O[C@@H](OC(C)=O)[C@H](OC(C)=O)[C@H]1OC(C)=O NNLVGZFZQQXQNW-ADJNRHBOSA-N 0.000 description 2

- 230000003667 anti-reflective effect Effects 0.000 description 2

- 239000011575 calcium Substances 0.000 description 2

- HKQOBOMRSSHSTC-UHFFFAOYSA-N cellulose acetate Chemical compound OC1C(O)C(O)C(CO)OC1OC1C(CO)OC(O)C(O)C1O.CC(=O)OCC1OC(OC(C)=O)C(OC(C)=O)C(OC(C)=O)C1OC1C(OC(C)=O)C(OC(C)=O)C(OC(C)=O)C(COC(C)=O)O1.CCC(=O)OCC1OC(OC(=O)CC)C(OC(=O)CC)C(OC(=O)CC)C1OC1C(OC(=O)CC)C(OC(=O)CC)C(OC(=O)CC)C(COC(=O)CC)O1 HKQOBOMRSSHSTC-UHFFFAOYSA-N 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 230000001066 destructive effect Effects 0.000 description 2

- JAONJTDQXUSBGG-UHFFFAOYSA-N dialuminum;dizinc;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[O-2].[O-2].[Al+3].[Al+3].[Zn+2].[Zn+2] JAONJTDQXUSBGG-UHFFFAOYSA-N 0.000 description 2

- 230000009975 flexible effect Effects 0.000 description 2

- 230000014509 gene expression Effects 0.000 description 2

- PCHJSUWPFVWCPO-UHFFFAOYSA-N gold Chemical compound [Au] PCHJSUWPFVWCPO-UHFFFAOYSA-N 0.000 description 2

- 229910052737 gold Inorganic materials 0.000 description 2

- 229910052741 iridium Inorganic materials 0.000 description 2

- GKOZUEZYRPOHIO-UHFFFAOYSA-N iridium atom Chemical compound [Ir] GKOZUEZYRPOHIO-UHFFFAOYSA-N 0.000 description 2

- 229910052749 magnesium Inorganic materials 0.000 description 2

- 229910052750 molybdenum Inorganic materials 0.000 description 2

- 239000011733 molybdenum Substances 0.000 description 2

- 239000000178 monomer Substances 0.000 description 2

- QEFYFXOXNSNQGX-UHFFFAOYSA-N neodymium atom Chemical compound [Nd] QEFYFXOXNSNQGX-UHFFFAOYSA-N 0.000 description 2

- 229910052759 nickel Inorganic materials 0.000 description 2

- 229910052763 palladium Inorganic materials 0.000 description 2

- 229910052697 platinum Inorganic materials 0.000 description 2

- 229920003229 poly(methyl methacrylate) Polymers 0.000 description 2

- 229920000767 polyaniline Polymers 0.000 description 2

- 239000011112 polyethylene naphthalate Substances 0.000 description 2

- 239000004926 polymethyl methacrylate Substances 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 239000011347 resin Substances 0.000 description 2

- 229920005989 resin Polymers 0.000 description 2

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical compound [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 2

- 229910052709 silver Inorganic materials 0.000 description 2

- 239000004332 silver Substances 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910052719 titanium Inorganic materials 0.000 description 2

- ILJSQTXMGCGYMG-UHFFFAOYSA-N triacetic acid Chemical compound CC(=O)CC(=O)CC(O)=O ILJSQTXMGCGYMG-UHFFFAOYSA-N 0.000 description 2

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 239000004925 Acrylic resin Substances 0.000 description 1

- OYPRJOBELJOOCE-UHFFFAOYSA-N Calcium Chemical compound [Ca] OYPRJOBELJOOCE-UHFFFAOYSA-N 0.000 description 1

- IMROMDMJAWUWLK-UHFFFAOYSA-N Ethenol Chemical compound OC=C IMROMDMJAWUWLK-UHFFFAOYSA-N 0.000 description 1

- YCKRFDGAMUMZLT-UHFFFAOYSA-N Fluorine atom Chemical compound [F] YCKRFDGAMUMZLT-UHFFFAOYSA-N 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 239000004698 Polyethylene Substances 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 150000001408 amides Chemical class 0.000 description 1

- 229910021417 amorphous silicon Inorganic materials 0.000 description 1

- 150000008378 aryl ethers Chemical class 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- 229910052791 calcium Inorganic materials 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- AJNVQOSZGJRYEI-UHFFFAOYSA-N digallium;oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[Ga+3].[Ga+3] AJNVQOSZGJRYEI-UHFFFAOYSA-N 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 239000003822 epoxy resin Substances 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 239000011737 fluorine Substances 0.000 description 1

- 229910052731 fluorine Inorganic materials 0.000 description 1

- 229910001195 gallium oxide Inorganic materials 0.000 description 1

- 150000003949 imides Chemical class 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 229910003437 indium oxide Inorganic materials 0.000 description 1

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000004519 manufacturing process Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 238000005259 measurement Methods 0.000 description 1

- 239000007769 metal material Substances 0.000 description 1

- 239000000203 mixture Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 239000005416 organic matter Substances 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 239000012466 permeate Substances 0.000 description 1

- ISWSIDIOOBJBQZ-UHFFFAOYSA-N phenol group Chemical group C1(=CC=CC=C1)O ISWSIDIOOBJBQZ-UHFFFAOYSA-N 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229920000058 polyacrylate Polymers 0.000 description 1

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 1

- 229920000647 polyepoxide Polymers 0.000 description 1

- 229920000573 polyethylene Polymers 0.000 description 1

- 229920005591 polysilicon Polymers 0.000 description 1

- 229920002223 polystyrene Polymers 0.000 description 1

- 239000002096 quantum dot Substances 0.000 description 1

- 239000002990 reinforced plastic Substances 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 238000009751 slip forming Methods 0.000 description 1

- 210000002784 stomach Anatomy 0.000 description 1

- 239000000057 synthetic resin Substances 0.000 description 1

- 238000007740 vapor deposition Methods 0.000 description 1

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

- H10K50/844—Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K50/00—Organic light-emitting devices

- H10K50/80—Constructional details

- H10K50/84—Passivation; Containers; Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

- H10K59/1213—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements the pixel elements being TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/122—Pixel-defining structures or layers, e.g. banks

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/123—Connection of the pixel electrodes to the thin film transistors [TFT]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/124—Insulating layers formed between TFT elements and OLED elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/30—Devices specially adapted for multicolour light emission

- H10K59/35—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels

- H10K59/351—Devices specially adapted for multicolour light emission comprising red-green-blue [RGB] subpixels comprising more than three subpixels, e.g. red-green-blue-white [RGBW]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/87—Passivation; Containers; Encapsulations

- H10K59/873—Encapsulations

- H10K59/8731—Encapsulations multilayered coatings having a repetitive structure, e.g. having multiple organic-inorganic bilayers

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/80—Constructional details

- H10K59/88—Dummy elements, i.e. elements having non-functional features

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K2102/00—Constructional details relating to the organic devices covered by this subclass

- H10K2102/301—Details of OLEDs

- H10K2102/351—Thickness

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/10—OLED displays

- H10K59/12—Active-matrix OLED [AMOLED] displays

- H10K59/121—Active-matrix OLED [AMOLED] displays characterised by the geometry or disposition of pixel elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10K—ORGANIC ELECTRIC SOLID-STATE DEVICES

- H10K59/00—Integrated devices, or assemblies of multiple devices, comprising at least one organic light-emitting element covered by group H10K50/00

- H10K59/60—OLEDs integrated with inorganic light-sensitive elements, e.g. with inorganic solar cells or inorganic photodiodes

- H10K59/65—OLEDs integrated with inorganic image sensors

Description

前記第1層は、有機物を含み、前記第2層は、無機物を含み得る。

前記第2層は、無機絶縁層又は金属を含み得る。

前記グルーブは、前記第1層の第1ホール又は第1リセスと、前記第2層の第2ホールと、を含み、前記第2ホールは、前記第1ホール又は前記第1リセスに連結され得る。

前記一対の先端部間の距離は、前記第1ホール又は前記第1リセスの深さよりも長くあり得る。

前記第1ホール又は前記第1リセスの深さは、前記先端部のそれぞれの長さよりも深くあり得る。

前記第1ホール又は前記第1リセスの深さに対する前記先端部のそれぞれの長さは、0.05<(l/dp)<0.50であり得る(ここで、lは前記先端部のそれぞれの長さを示し、dpは前記第1ホール又は前記第1リセスの深さを示す)。

前記第1ホール又は前記第1リセスの深さは、前記第1層の厚みと同じであるか又はそれよりも浅くあり得る。

前記表示パネルは、前記画素電極と前記発光層との間の第1機能層、及び前記発光層と前記対向電極との間の第2機能層のうちの少なくともいずれか1層を更に含み、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層と前記対向電極とは、それぞれ前記一対の先端部を中心に断絶され、前記第1ホール又は前記第1リセスの深さは、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層の厚みと前記対向電極の厚みとの和よりも深くあり得る。

前記対向電極上のキャッピング層を更に含み、前記第1ホール又は前記第1リセスの深さは、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層の厚み、前記対向電極の厚み、及び前記キャッピング層の厚みの和よりも深くあり得る。

前記表示パネルは、基板、及び前記基板上に配置されて前記画素電極に電気的に連結される薄膜トランジスタを具備する画素回路を更に含み得る。

前記基板は、前記多層膜を含み得る。前記多層膜は、前記基板上に位置し得る。

前記第1層を通過する部分の深さは、前記第1層の厚みと同じであるか又はそれよりも浅くあり得る。

前記一対の先端部間の距離は、前記第1層を通過する部分の深さよりも長くあり得る。

前記第1層を通過する部分の深さに対する前記先端部のそれぞれの長さは、0.05<(l/dp)<0.5であり得る(ここで、lは前記先端部のそれぞれの長さを示し、dpは前記第1層を通過する部分の深さを示す)。

前記表示パネルは、前記画素電極と前記発光層との間の第1機能層、及び前記発光層と前記対向電極との間の第2機能層のうちの少なくともいずれか1層を更に含み、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層と前記対向電極とは、それぞれ前記一対の先端部を中心に断絶され、前記第1層を通過する部分の深さは、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層の厚みと前記対向電極の厚みとの和よりも深くあり得る。

前記表示パネルは、前記対向電極上のキャッピング層を更に含み、前記第1層を通過する部分の深さは、前記第1機能層及び前記第2機能層のうちの少なくともいずれか1層の厚み、前記対向電極の厚み、及び前記キャッピング層の厚みの和よりも深くあり得る。

前記第1層を通過する部分の深さは、2μmであるか又はそれよりも深くあり得る。

前記表示パネルは、基板、及び前記基板上に位置して前記画素電極に電気的に連結される薄膜トランジスタを具備する画素回路を更に含み得る。

前記基板は、前記多層膜を含み得る。前記多層膜は、前記基板上に位置し得る。

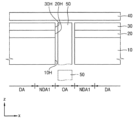

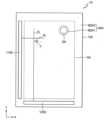

10、10’ 表示パネル

10H、20H、30H 第1、第2、第3開口

20 入力感知部材

30 光学的機能部材

40 ウィンドウ

50 コンポーネント

100 基板

101、103 第1、第2ベース層

102、104 第1、第2バリア層

200 絶縁層

201 バッファ層

203 ゲート絶縁層

205、207 第1、第2層間絶縁層

209 第1絶縁層

211、211’ 第2絶縁層

213 スペーサ

221 画素電極

222 中間層

222’ 中間層のサブ層

222a、222c 第1、第2機能層

222b 発光層

223 対向電極

230 キャッピング層

300 薄膜封止層

310、330 第1、第2無機封止層

320 有機封止層

410 平坦化層

410E 平坦化層の端

510、520 第1、第2隔壁

1100 スキャンドライバ

1200 データドライバ

Act 半導体層

CE1、CE2 下部、上部電極

Cst ストレージキャパシタ

DA 表示領域

DE ドレイン電極

DL データライン

ELVDD、ELVSS 第1、第2電源電圧

G グルーブ

GE ゲート電極

H2 第2ホール

L1、L2 第1、第2層

LL 下部層

ML 多層膜

NDA 非表示領域

NDA1 第1非表示領域

NDA2 第2非表示領域

OA 開口領域

OLED 有機発光ダイオード

P 画素

PC 画素回路

PL 駆動電圧線

PT 一対の先端部(庇)

R1 第1リセス

SE ソース電極

SL スキャンライン

SNDA1 第1サブ非表示領域

SNDA2 第2サブ非表示領域

T1 第1薄膜トランジスタ

T2 第2薄膜トランジスタ

TFT 薄膜トランジスタ

Claims (19)

- 開口を有する基板と、

前記開口を取り囲む表示領域に配置された複数の発光ダイオードと、

前記発光ダイオード上の封止層と、

前記開口と前記表示領域との間に配置された非表示領域に位置して深さ方向に沿って形成されたグルーブを有する多層膜と、を備え、

前記封止層は、第1無機封止層、前記第1無機封止層上の有機封止層、及び前記有機封止層上の第2無機封止層を含み、

前記多層膜は、第1層と前記第1層上の第2層とを有し、

前記グルーブ内の前記第2層は、前記第1層の側面と前記第2層の底面とが出会う地点を超えて前記基板の上面に平行な水平方向に前記グルーブの中心に向けて突出する先端部を有し、

前記地点と前記先端部の側面との間の距離である、前記先端部の長さは0μmよりも大きく2μm未満であり、

平面上において、前記グルーブは、前記基板の前記開口を全体として取り囲むことを特徴とする表示パネル。

- 前記第1層の材料は、前記第2層の材料とは異なることを特徴とする請求項1に記載の表示パネル。

- 前記第2層は、金属を含むことを特徴とする請求項2に記載の表示パネル。

- 前記第2層の厚さは、前記第1層の厚さよりも小さいことを特徴とする請求項1に記載の表示パネル。

- 前記複数の発光ダイオードの各々は、

画素電極と、

前記画素電極に重畳する発光層と、

前記複数の発光ダイオードに対応する対向電極の一部と、

前記画素電極と前記対向電極の一部との間の、前記複数の発光ダイオードに対応する機能層の一部と、を含むことを特徴とする請求項1に記載の表示パネル。 - 前記機能層及び前記対向電極の各々は、前記第2層の先端部によって断絶されることを特徴とする請求項5に記載の表示パネル。

- 前記第1層の厚さは、前記機能層の厚さと前記対向電極の厚さとの和よりも大きいことを特徴とする請求項6に記載の表示パネル。

- 前記第2層の上面にある前記機能層及び前記対向電極の一部は、第1無機封止層によってカバーされることを特徴とする請求項6に記載の表示パネル。

- 前記第1無機封止層は、前記先端部の側面及び底面と前記第1層の側面とを連続的にカバーするように延長されることを特徴とする請求項8に記載の表示パネル。

- 前記有機封止層は、前記先端部によって断絶された前記機能層及び前記対向電極にそれぞれ重畳することを特徴とする請求項6に記載の表示パネル。

- 前記機能層は、正孔輸送層(HTL)、正孔注入層(HIL)、電子輸送層(ETL)、及び電子注入層(EIL)から選択される1つ以上を含むことを特徴とする請求項5に記載の表示パネル。

- 開口を有する基板と、

前記開口を取り囲む表示領域に配置された複数の発光ダイオードと、

前記発光ダイオード上の封止層と、

前記開口と前記表示領域との間に配置された非表示領域に位置して深さ方向に沿って形成されたグルーブを有する多層膜と、を備え、

前記多層膜は、第1層と前記第1層上の第2層とを有し、

前記第2層の厚さは、前記第1層の厚さよりも小さく、

前記グルーブ内の前記第2層は、前記第1層の側面と前記第2層の底面とが出会う地点を超えて前記基板の上面に平行な水平方向に前記グルーブの中心に向けて突出する先端部を有し、

前記地点と前記先端部の側面との間の距離である、前記先端部の長さは0μmよりも大きく2μm未満であり、

平面上において、前記グルーブは、前記基板の前記開口を全体として取り囲むことを特徴とする表示パネル。

- 前記第1層の材料は、前記第2層の材料とは異なり、

前記第2層は、金属を含むことを特徴とする請求項12に記載の表示パネル。 - 前記複数の発光ダイオードの各々は、

画素電極と、

前記画素電極に重畳する発光層と、

前記複数の発光ダイオードに対応する対向電極の一部と、

前記画素電極と前記対向電極の一部との間の、前記複数の発光ダイオードに対応する機能層の一部と、を含むことを特徴とする請求項12に記載の表示パネル。 - 前記機能層及び前記対向電極の各々は、前記第2層の先端部によって断絶されることを特徴とする請求項14に記載の表示パネル。

- 前記第1層の厚さは、前記機能層の厚さと前記対向電極の厚さとの和よりも大きいことを特徴とする請求項15に記載の表示パネル。

- 前記封止層は、第1無機封止層と前記第1無機封止層上の有機封止層とを含み、

前記第1無機封止層は、前記第2層の上面にある前記機能層及び前記対向電極の一部をカバーし、前記先端部の側面及び底面と前記第1層の側面とを連続的にカバーするように延長されることを特徴とする請求項15に記載の表示パネル。 - 前記有機封止層は、前記先端部によって断絶された前記機能層及び前記対向電極にそれぞれ重畳することを特徴とする請求項17に記載の表示パネル。

- 前記機能層は、正孔輸送層(HTL)、正孔注入層(HIL)、電子輸送層(ETL)、及び電子注入層(EIL)から選択される1つ以上を含むことを特徴とする請求項15に記載の表示パネル。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2023118127A JP2023139118A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル |

| JP2023118128A JP2023153857A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル及びこれを含む電子装置 |

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| KR1020180121197A KR20200041420A (ko) | 2018-10-11 | 2018-10-11 | 표시 패널 |

| KR10-2018-0121197 | 2018-10-11 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023118127A Division JP2023139118A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル |

| JP2023118128A Division JP2023153857A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル及びこれを含む電子装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2020061354A JP2020061354A (ja) | 2020-04-16 |

| JP2020061354A5 JP2020061354A5 (ja) | 2022-06-28 |

| JP7319102B2 true JP7319102B2 (ja) | 2023-08-01 |

Family

ID=70159058

Family Applications (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019113976A Active JP7319102B2 (ja) | 2018-10-11 | 2019-06-19 | 表示パネル |

| JP2023118128A Pending JP2023153857A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル及びこれを含む電子装置 |

| JP2023118127A Pending JP2023139118A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2023118128A Pending JP2023153857A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル及びこれを含む電子装置 |

| JP2023118127A Pending JP2023139118A (ja) | 2018-10-11 | 2023-07-20 | 表示パネル |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US10862068B2 (ja) |

| JP (3) | JP7319102B2 (ja) |

| KR (1) | KR20200041420A (ja) |

| CN (1) | CN111048551A (ja) |

Families Citing this family (43)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102631731B1 (ko) * | 2018-07-31 | 2024-01-30 | 엘지디스플레이 주식회사 | 표시장치 및 이의 제조방법 |

| KR102465374B1 (ko) * | 2018-09-12 | 2022-11-10 | 삼성디스플레이 주식회사 | 표시 패널 및 이를 포함하는 표시 장치 |

| KR20200041420A (ko) | 2018-10-11 | 2020-04-22 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR20200060594A (ko) * | 2018-11-21 | 2020-06-01 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR102642791B1 (ko) * | 2018-12-04 | 2024-02-29 | 엘지디스플레이 주식회사 | 표시 영역 내에 관통-홀을 구비한 전계 발광 표시장치 |

| CN110164916B (zh) * | 2018-12-05 | 2021-02-02 | 京东方科技集团股份有限公司 | 显示面板、显示设备及制造显示面板的方法 |

| US20200235180A1 (en) * | 2019-01-18 | 2020-07-23 | Samsung Display Co., Ltd. | Display panel |

| KR20200115834A (ko) * | 2019-03-27 | 2020-10-08 | 삼성디스플레이 주식회사 | 표시 패널 |

| CN110098234B (zh) * | 2019-05-07 | 2021-08-27 | 京东方科技集团股份有限公司 | 电致发光器件、其制备方法、检测方法及显示装置 |

| KR20200136548A (ko) * | 2019-05-27 | 2020-12-08 | 삼성디스플레이 주식회사 | 표시장치 |

| KR20200145902A (ko) * | 2019-06-19 | 2020-12-31 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR20200145954A (ko) * | 2019-06-21 | 2020-12-31 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN110335964B (zh) * | 2019-06-26 | 2020-11-10 | 武汉华星光电半导体显示技术有限公司 | 一种显示面板 |

| KR20210003990A (ko) * | 2019-07-02 | 2021-01-13 | 삼성디스플레이 주식회사 | 전자 장치 및 이의 제조 방법 |

| KR20210010778A (ko) * | 2019-07-19 | 2021-01-28 | 삼성디스플레이 주식회사 | 플렉서블 디스플레이 장치 |

| CN110265583B (zh) * | 2019-07-26 | 2022-08-12 | 京东方科技集团股份有限公司 | 一种显示面板及其制备方法、显示装置 |

| CN110600526B (zh) * | 2019-09-30 | 2021-08-03 | 武汉华星光电半导体显示技术有限公司 | 显示面板及显示装置 |

| US11244994B2 (en) * | 2019-10-23 | 2022-02-08 | Wuhan China Star Optoelectronics Semiconductor Display Technology Co., Ltd. | Thin film transistor array substrate and organic light emitting diode panel |

| KR20210086888A (ko) * | 2019-12-31 | 2021-07-09 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 제조방법 |

| KR20210088042A (ko) * | 2020-01-03 | 2021-07-14 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20210103614A (ko) * | 2020-02-13 | 2021-08-24 | 삼성디스플레이 주식회사 | 표시 장치 |

| US11322720B2 (en) * | 2020-02-27 | 2022-05-03 | Wuhan China Star Optoelectronics Semiconductor Display Technology Co., Ltd. | Display panel having a grooved non-display area |

| CN111326559B (zh) * | 2020-02-28 | 2023-09-29 | 武汉华星光电半导体显示技术有限公司 | 一种显示面板及显示装置 |

| CN111430566A (zh) * | 2020-03-30 | 2020-07-17 | 武汉华星光电半导体显示技术有限公司 | Oled显示面板及显示装置 |

| KR20210130893A (ko) | 2020-04-22 | 2021-11-02 | 삼성디스플레이 주식회사 | 표시 장치 |

| CN114127945B (zh) * | 2020-04-29 | 2023-07-14 | 京东方科技集团股份有限公司 | 有机发光显示基板及其制作方法、有机发光显示装置 |

| KR20210134172A (ko) * | 2020-04-29 | 2021-11-09 | 삼성디스플레이 주식회사 | 표시 패널 및 이를 구비한 표시 장치 |

| CN115411080A (zh) * | 2020-04-29 | 2022-11-29 | 京东方科技集团股份有限公司 | 有机发光显示基板及其制作方法、有机发光显示装置 |

| CN113950712B (zh) * | 2020-05-09 | 2023-09-29 | 京东方科技集团股份有限公司 | 显示基板、显示面板、显示装置及显示面板的制造方法 |

| KR20220004856A (ko) * | 2020-07-02 | 2022-01-12 | 삼성디스플레이 주식회사 | 디스플레이 패널과, 이의 제조방법 |

| CN111769153B (zh) * | 2020-07-13 | 2023-04-18 | 京东方科技集团股份有限公司 | 显示面板、显示面板的制造方法与显示装置 |

| US20220020955A1 (en) * | 2020-07-15 | 2022-01-20 | Samsung Display Co., Ltd. | Display device |

| US11600800B2 (en) * | 2020-07-31 | 2023-03-07 | Innolux Corporation | Electronic device having a curved profile interface corresponding to a recess |

| KR20220017568A (ko) * | 2020-08-04 | 2022-02-14 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| CN111969027B (zh) * | 2020-08-28 | 2023-07-25 | 合肥维信诺科技有限公司 | 显示面板以及显示装置 |

| KR20220033611A (ko) * | 2020-09-08 | 2022-03-17 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20220037550A (ko) * | 2020-09-17 | 2022-03-25 | 삼성디스플레이 주식회사 | 디스플레이 장치 및 그 제조방법 |

| CN112164760B (zh) * | 2020-09-28 | 2023-05-30 | 京东方科技集团股份有限公司 | 显示面板和电子装置 |

| KR20220051097A (ko) * | 2020-10-16 | 2022-04-26 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR20220094303A (ko) * | 2020-12-28 | 2022-07-06 | 삼성디스플레이 주식회사 | 표시 장치 및 표시 장치의 제조방법 |

| CN112786804B (zh) * | 2021-01-08 | 2022-07-12 | 武汉华星光电半导体显示技术有限公司 | 显示面板及其制作方法 |

| KR20220120793A (ko) * | 2021-02-23 | 2022-08-31 | 삼성디스플레이 주식회사 | 디스플레이 장치 및 그 제조방법 |

| CN113658994B (zh) * | 2021-09-10 | 2023-01-10 | 武汉华星光电半导体显示技术有限公司 | 显示面板及显示装置 |

Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20170031323A1 (en) | 2015-07-29 | 2017-02-02 | Lg Display Co., Ltd. | Organic light emitting display device |

| US20170148856A1 (en) | 2015-11-20 | 2017-05-25 | Samsung Display Co., Ltd | Organic light-emitting display and method of manufacturing the same |

| JP2018087863A (ja) | 2016-11-28 | 2018-06-07 | 株式会社ジャパンディスプレイ | 表示装置 |

Family Cites Families (31)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3813217B2 (ja) * | 1995-03-13 | 2006-08-23 | パイオニア株式会社 | 有機エレクトロルミネッセンスディスプレイパネルの製造方法 |

| JP3875401B2 (ja) * | 1998-05-12 | 2007-01-31 | Tdk株式会社 | 有機el表示装置及び有機el素子 |

| JP2006040801A (ja) | 2004-07-29 | 2006-02-09 | Nippon Seiki Co Ltd | 有機elパネル |

| JP2008010275A (ja) | 2006-06-28 | 2008-01-17 | Kyocera Corp | 画像表示装置 |

| KR20110058356A (ko) | 2009-11-26 | 2011-06-01 | 엘지디스플레이 주식회사 | 어레이 기판 및 이의 제조방법 |

| KR101717933B1 (ko) * | 2010-04-14 | 2017-03-21 | 삼성디스플레이 주식회사 | 표시기판 및 그 제조방법 |

| US8947627B2 (en) | 2011-10-14 | 2015-02-03 | Apple Inc. | Electronic devices having displays with openings |

| KR20160076688A (ko) | 2014-12-23 | 2016-07-01 | 엘지디스플레이 주식회사 | 유기 발광 표시 장치 및 유기 발광 표시 장치 제조 방법 |

| JP2016219125A (ja) * | 2015-05-15 | 2016-12-22 | ソニー株式会社 | 発光素子及び表示装置 |

| KR102386706B1 (ko) | 2015-06-11 | 2022-04-14 | 삼성디스플레이 주식회사 | 표시 장치 및 이를 구비한 시계 |

| US20170026553A1 (en) | 2015-07-24 | 2017-01-26 | Apple Inc. | Displays With Camera Window Openings |

| KR102376966B1 (ko) | 2015-08-11 | 2022-03-22 | 삼성디스플레이 주식회사 | 디스플레이 장치 및 이의 제조 방법 |

| KR102457252B1 (ko) | 2015-11-20 | 2022-10-24 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR102552272B1 (ko) | 2015-11-20 | 2023-07-07 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 그 제조 방법 |

| KR102388722B1 (ko) | 2015-11-20 | 2022-04-21 | 삼성디스플레이 주식회사 | 표시 장치 및 유기 발광 표시 장치 |

| KR102465379B1 (ko) | 2015-12-02 | 2022-11-10 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| KR102490891B1 (ko) | 2015-12-04 | 2023-01-25 | 삼성디스플레이 주식회사 | 표시 장치 |

| KR102465377B1 (ko) | 2016-02-12 | 2022-11-10 | 삼성디스플레이 주식회사 | 표시 장치 및 이의 제조 방법 |

| KR102421577B1 (ko) * | 2016-04-05 | 2022-07-18 | 삼성디스플레이 주식회사 | 디스플레이 장치 |

| KR102545553B1 (ko) | 2016-05-13 | 2023-06-20 | 엘지디스플레이 주식회사 | 플렉서블 유기전계발광표시 장치 |

| KR102605208B1 (ko) | 2016-06-28 | 2023-11-24 | 삼성디스플레이 주식회사 | 유기 발광 표시 장치 및 유기 발광 표시 장치의 제조 방법 |

| KR102601207B1 (ko) | 2016-07-29 | 2023-11-13 | 삼성디스플레이 주식회사 | 표시장치 |

| KR102103962B1 (ko) | 2016-09-02 | 2020-06-01 | 삼성디스플레이 주식회사 | 디스플레이 장치 및 제조 방법 |

| KR102589245B1 (ko) | 2016-11-30 | 2023-10-12 | 엘지디스플레이 주식회사 | 표시장치와 그의 제조방법 |

| KR20180077767A (ko) | 2016-12-29 | 2018-07-09 | 엘지디스플레이 주식회사 | 보조 전극을 포함하는 디스플레이 장치 |

| CN107579171B (zh) | 2017-08-31 | 2019-07-30 | 京东方科技集团股份有限公司 | 有机电致发光显示基板及其制作方法、显示装置 |

| KR102448325B1 (ko) * | 2017-11-16 | 2022-09-30 | 삼성디스플레이 주식회사 | 표시패널 및 이를 포함하는 전자장치 |

| KR102514205B1 (ko) * | 2017-12-07 | 2023-03-27 | 엘지디스플레이 주식회사 | 유기발광 표시장치 |

| KR20200015865A (ko) | 2018-08-02 | 2020-02-13 | 삼성디스플레이 주식회사 | 표시 패널 및 이를 포함하는 전자 장치 |

| KR20200041420A (ko) | 2018-10-11 | 2020-04-22 | 삼성디스플레이 주식회사 | 표시 패널 |

| KR20210049253A (ko) | 2019-10-24 | 2021-05-06 | 삼성디스플레이 주식회사 | 표시 장치 |

-

2018

- 2018-10-11 KR KR1020180121197A patent/KR20200041420A/ko not_active Application Discontinuation

-

2019

- 2019-05-02 US US16/401,536 patent/US10862068B2/en active Active

- 2019-06-19 JP JP2019113976A patent/JP7319102B2/ja active Active

- 2019-08-05 CN CN201910716259.9A patent/CN111048551A/zh active Pending

-

2020

- 2020-11-30 US US17/106,719 patent/US11424429B2/en active Active

-

2022

- 2022-08-04 US US17/817,429 patent/US11974456B2/en active Active

-

2023

- 2023-07-20 JP JP2023118128A patent/JP2023153857A/ja active Pending

- 2023-07-20 JP JP2023118127A patent/JP2023139118A/ja active Pending

Patent Citations (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20170031323A1 (en) | 2015-07-29 | 2017-02-02 | Lg Display Co., Ltd. | Organic light emitting display device |

| US20170148856A1 (en) | 2015-11-20 | 2017-05-25 | Samsung Display Co., Ltd | Organic light-emitting display and method of manufacturing the same |

| JP2018087863A (ja) | 2016-11-28 | 2018-06-07 | 株式会社ジャパンディスプレイ | 表示装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2023153857A (ja) | 2023-10-18 |

| US11974456B2 (en) | 2024-04-30 |

| US20210143370A1 (en) | 2021-05-13 |

| KR20200041420A (ko) | 2020-04-22 |

| US20220393137A1 (en) | 2022-12-08 |

| US10862068B2 (en) | 2020-12-08 |

| JP2023139118A (ja) | 2023-10-03 |

| CN111048551A (zh) | 2020-04-21 |

| JP2020061354A (ja) | 2020-04-16 |

| US11424429B2 (en) | 2022-08-23 |

| US20200119304A1 (en) | 2020-04-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7319102B2 (ja) | 表示パネル | |

| KR102626939B1 (ko) | 표시 장치 | |

| US11139451B2 (en) | Display panel | |

| KR102661469B1 (ko) | 표시 패널 | |

| US11335867B2 (en) | Display panel including a groove between an opening and a display area | |

| US11069761B2 (en) | Display panel and display apparatus including the same | |

| CN111755474A (zh) | 显示设备 | |

| US20220020957A1 (en) | Display panel | |

| KR20200113092A (ko) | 표시 패널 | |

| KR20200145902A (ko) | 표시 패널 | |

| KR102653424B1 (ko) | 표시 패널 | |

| KR20200107026A (ko) | 표시 패널 | |

| US11793051B2 (en) | Display apparatus | |

| KR20200094877A (ko) | 표시장치 | |

| KR20210049253A (ko) | 표시 장치 | |

| KR20240017884A (ko) | 표시 패널 | |

| KR20240063079A (ko) | 표시 패널 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220620 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20220620 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20230208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20230214 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20230511 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230620 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230720 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7319102 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |