JP7242527B2 - 光検出素子およびその製造方法 - Google Patents

光検出素子およびその製造方法 Download PDFInfo

- Publication number

- JP7242527B2 JP7242527B2 JP2019527577A JP2019527577A JP7242527B2 JP 7242527 B2 JP7242527 B2 JP 7242527B2 JP 2019527577 A JP2019527577 A JP 2019527577A JP 2019527577 A JP2019527577 A JP 2019527577A JP 7242527 B2 JP7242527 B2 JP 7242527B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- type

- conductivity type

- substrate

- view

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 72

- 239000004065 semiconductor Substances 0.000 claims description 551

- 239000000758 substrate Substances 0.000 claims description 213

- 230000005684 electric field Effects 0.000 claims description 75

- 239000012535 impurity Substances 0.000 claims description 53

- 230000002093 peripheral effect Effects 0.000 claims description 36

- 150000002500 ions Chemical class 0.000 claims description 30

- 238000002955 isolation Methods 0.000 claims description 25

- 238000009792 diffusion process Methods 0.000 claims description 23

- 239000011159 matrix material Substances 0.000 claims description 20

- 238000000926 separation method Methods 0.000 claims description 17

- 238000005468 ion implantation Methods 0.000 claims description 15

- 238000000034 method Methods 0.000 claims description 14

- 238000009825 accumulation Methods 0.000 claims description 2

- 238000001514 detection method Methods 0.000 claims description 2

- 239000010408 film Substances 0.000 description 93

- 238000005516 engineering process Methods 0.000 description 47

- 239000002184 metal Substances 0.000 description 21

- 229910052751 metal Inorganic materials 0.000 description 21

- 238000010586 diagram Methods 0.000 description 18

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 5

- 238000005286 illumination Methods 0.000 description 5

- 229910052698 phosphorus Inorganic materials 0.000 description 5

- 239000011574 phosphorus Substances 0.000 description 5

- 230000015556 catabolic process Effects 0.000 description 4

- 239000010949 copper Substances 0.000 description 4

- 230000000694 effects Effects 0.000 description 4

- 230000003287 optical effect Effects 0.000 description 4

- 230000035945 sensitivity Effects 0.000 description 4

- 239000007790 solid phase Substances 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- 238000000098 azimuthal photoelectron diffraction Methods 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 238000006243 chemical reaction Methods 0.000 description 3

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 description 2

- 230000015572 biosynthetic process Effects 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 229910052593 corundum Inorganic materials 0.000 description 2

- CJNBYAVZURUTKZ-UHFFFAOYSA-N hafnium(IV) oxide Inorganic materials O=[Hf]=O CJNBYAVZURUTKZ-UHFFFAOYSA-N 0.000 description 2

- 238000002513 implantation Methods 0.000 description 2

- 239000007769 metal material Substances 0.000 description 2

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 2

- 229910052721 tungsten Inorganic materials 0.000 description 2

- 239000010937 tungsten Substances 0.000 description 2

- 229910001845 yogo sapphire Inorganic materials 0.000 description 2

- 240000007594 Oryza sativa Species 0.000 description 1

- 235000007164 Oryza sativa Nutrition 0.000 description 1

- 238000003491 array Methods 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 238000009826 distribution Methods 0.000 description 1

- 239000012528 membrane Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- 235000009566 rice Nutrition 0.000 description 1

- 238000004904 shortening Methods 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 230000001629 suppression Effects 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/18—Complementary metal-oxide-semiconductor [CMOS] image sensors; Photodiode array image sensors

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/76—Addressed sensors, e.g. MOS or CMOS sensors

- H04N25/77—Pixel circuitry, e.g. memories, A/D converters, pixel amplifiers, shared circuits or shared components

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N25/00—Circuitry of solid-state image sensors [SSIS]; Control thereof

- H04N25/70—SSIS architectures; Circuits associated therewith

- H04N25/79—Arrangements of circuitry being divided between different or multiple substrates, chips or circuit boards, e.g. stacked image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F30/00—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors

- H10F30/20—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/011—Manufacture or treatment of image sensors covered by group H10F39/12

- H10F39/014—Manufacture or treatment of image sensors covered by group H10F39/12 of CMOS image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/10—Integrated devices

- H10F39/12—Image sensors

- H10F39/199—Back-illuminated image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/802—Geometry or disposition of elements in pixels, e.g. address-lines or gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/805—Coatings

- H10F39/8057—Optical shielding

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/806—Optical elements or arrangements associated with the image sensors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/806—Optical elements or arrangements associated with the image sensors

- H10F39/8063—Microlenses

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F39/00—Integrated devices, or assemblies of multiple devices, comprising at least one element covered by group H10F30/00, e.g. radiation detectors comprising photodiode arrays

- H10F39/80—Constructional details of image sensors

- H10F39/807—Pixel isolation structures

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

Description

本技術の第1の側面においては、マトリクス状に配置された複数の画素が設けられ、前記画素には、画素境界近傍の外周部に形成された第1導電型の第1半導体層と、平面視において前記第1半導体層の内側に前記第1半導体層と接触して形成された、前記第1導電型と反対の第2導電型の第2半導体層と、平面視において前記第2半導体層の内側に前記第2半導体層と接触して形成された、前記第2半導体層よりも不純物濃度が低い前記第2導電型の第3半導体層とが設けられ、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、断面視で基板の深さ方向に縦長に形成されるように構成される。

本技術の第2の側面においては、マトリクス状に配置された複数の画素が設けられ、前記画素には、画素境界近傍の外周部に形成された第1導電型の第1半導体層と、平面視において前記第1半導体層の内側に前記第1半導体層と接触して形成された、前記第1導電型と反対の第2導電型の第2半導体層とが設けられ、前記第2半導体層には、基板の表面に向かって不純物濃度が濃くなる電位勾配が形成され、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、断面視で前記基板の深さ方向に縦長に形成されるように構成される。

本技術の第3の側面においては、マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層が形成され、平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層が形成され、前記第2導電型のイオンを含んだ第1酸化膜を埋め込み、熱拡散によって前記第2半導体層を形成した後、前記第1酸化膜を除去して、その除去された部分に、前記第1導電型のイオンを含んだ第2酸化膜を埋め込み、熱拡散によって前記第1半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成される。

本技術の第4の側面においては、マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層が形成され、平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層が形成され、前記第1導電型のイオンを含んだ第1酸化膜を埋め込み、前記第2導電型のイオンを含んだ第2酸化膜を前記第1酸化膜とは別の領域に埋め込み、熱拡散によって前記第1半導体層と前記第2半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成される。

本技術の第5の側面の光検出素子の製造方法は、マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層を形成し、平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層を形成し、基板の前記画素の境界に、前記基板の所定の深さまで掘り込んだトレンチを形成し、前記トレンチの側面から前記第1導電型のイオン注入と前記第2導電型のイオン注入を行うことで、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、前記基板の深さ方向に形成されるように構成される。

本技術の第5の側面においては、マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層が形成され、平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層が形成され、基板の前記画素の境界に、前記基板の所定の深さまで掘り込んだトレンチを形成し、前記トレンチの側面から前記第1導電型のイオン注入と前記第2導電型のイオン注入を行うことで、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、前記基板の深さ方向に形成されるように構成される。

1.第1実施の形態(光検出素子の基本構成例)

2.第2実施の形態(分離部を備える構成例)

3.第3実施の形態(分離部を備える裏面照射型の構成例)

4.第4実施の形態(内側に低濃度N型半導体層を備える構成例)

5.第5実施の形態(基板表面にSTIを備える構成例)

6.第6実施の形態(アノードおよびカソードを対角に離した構成例)

7.第7実施の形態(STIとアノードおよびカソードを対角に配置した構成例)

8.第8実施の形態(隣接縦方向に低濃度N型半導体層を備える構成例)

9.第9実施の形態(隣接縦方向に低濃度P型半導体層を備える構成例)

10.第10実施の形態(N型半導体層が電位勾配を有する構成例)

11.第11実施の形態(深さ方向の一部に高電界領域を備える構成例)

12.第12実施の形態(画素毎にOCLを備える構成例)

13.第13実施の形態(1画素に複数のOCLを備える構成例)

14.第14実施の形態(複数画素に1個のOCLを備える構成例)

15.第15実施の形態(隣接画素の信号を共有する構成例)

16.第16実施の形態(信号をゲート制御する構成例)

17.第1の製造方法(イオン注入で形成する製造方法)

18.第2の製造方法(イオン注入と固相拡散で形成する製造方法)

19.第3の製造方法(高濃度基板と固相拡散で形成する製造方法)

20.第4の製造方法(2回の固相拡散で形成する製造方法)

21.第5の製造方法(1回の固相拡散で形成する製造方法)

22.第6の製造方法(表面からトレンチ形成し、イオン注入する製造方法)

23.第7の製造方法(裏面からトレンチ形成し、イオン注入する製造方法)

24.まとめ

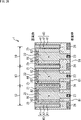

図1は、本技術を適用した光検出素子としてのフォトダイオードアレイの第1実施の形態の構成例を示している。

図3は、本技術を適用した光検出素子としてのフォトダイオードアレイの第2実施の形態の構成例を示している。

図5は、本技術を適用した光検出素子としてのフォトダイオードアレイの第3実施の形態の構成例を示している。

図7は、本技術を適用した光検出素子としてのフォトダイオードアレイの第4実施の形態の構成例を示している。

図12は、本技術を適用した光検出素子としてのフォトダイオードアレイの第5実施の形態の構成例を示している。

図13は、本技術を適用した光検出素子としてのフォトダイオードアレイの第6実施の形態の構成例を示している。

図14は、本技術を適用した光検出素子としてのフォトダイオードアレイの第7実施の形態の構成例を示している。

図15は、本技術を適用した光検出素子としてのフォトダイオードアレイの第8実施の形態の構成例を示している。

図20は、本技術を適用した光検出素子としてのフォトダイオードアレイの第9実施の形態の構成例を示している。

図25は、本技術を適用した光検出素子としてのフォトダイオードアレイの第10実施の形態の構成例を示している。

図26は、本技術を適用した光検出素子としてのフォトダイオードアレイの第11実施の形態の構成例を示している。

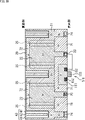

図31乃至図38で説明する第12乃至第15実施の形態は、光の入射面側にOCL(On Chip Lenz)を追加した構成例を示している。図31乃至図38において、半導体基板内の構成については、図21に示した第9実施の形態の構成を採用した例で説明するが、その他の実施の形態の構成も採用可能である。

図33は、本技術を適用した光検出素子としてのフォトダイオードアレイの第13実施の形態の構成例を示している。

図34は、本技術を適用した光検出素子としてのフォトダイオードアレイの第14実施の形態の構成例を示している。

図38は、本技術を適用した光検出素子としてのフォトダイオードアレイの第15実施の形態の構成例を示している。

図39は、本技術を適用した光検出素子としてのフォトダイオードアレイの第16実施の形態の構成例を示している。

次に、図41を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第1の製造方法について説明する。この第1の製造方法は、例えば、図1および図2に示した第1実施の形態に適用することができる。

次に、図42を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第2の製造方法について説明する。この第2の製造方法は、図3の第2実施の形態のように、画素10の境界に、分離部43を設ける場合に適用できる。

次に、図43を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第3の製造方法について説明する。この第3の製造方法も、画素10の境界に、分離部43を設ける場合の製造方法である。

次に、図44を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第4の製造方法について説明する。この第4の製造方法も、画素10の境界に、分離部43を設ける場合の製造方法である。

次に、図45を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第5の製造方法について説明する。この第5の製造方法も、画素10の境界に、分離部43を設ける場合の製造方法である。

次に、図46を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第6の製造方法について説明する。この第6の製造方法は、図9に示した第4実施の形態のように、テーパ形状の分離部43を基板表面側から掘り込んで形成する場合の製造方法である。

次に、図47および図48を参照して、フォトダイオードアレイ1の半導体基板に、P+型第1半導体層21およびN+型第2半導体層22を形成する第7の製造方法について説明する。この第7の製造方法は、図24に示した第9実施の形態のように、テーパ形状の分離部43を基板裏面側から掘り込んで形成する場合の製造方法である。

以上説明したように、第1乃至第16実施の形態に係るフォトダイオードアレイ1は、マトリクス状に配置された複数の画素10を備え、画素境界近傍の外周部に形成された第1導電型(例えば、P型)の第1半導体層(P+型第1半導体層21)と、平面視において第1半導体層の内側に形成された、第1導電型と反対の第2導電型(例えば、N型)の第2半導体層(N+型第2半導体層22)とを備え、逆バイアス電圧が印加されたときに第1半導体層と第2半導体層とで形成される高電界領域25が基板の深さ方向に形成されるように構成される。

(1)

マトリクス状に配置された複数の画素を備え、

前記画素は、

画素境界近傍の外周部に形成された第1導電型の第1半導体層と、

平面視において前記第1半導体層の内側に形成された、前記第1導電型と反対の第2導電型の第2半導体層と

を備え、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成された

光検出素子。

(2)

画素境界に、隣接する画素間を絶縁分離する分離部をさらに備え、

前記高電界領域は、前記分離部に隣接して形成されるように構成された

前記(1)に記載の光検出素子。

(3)

平面視において前記第2半導体層の内側に、前記第2半導体層よりも不純物濃度が低い前記第2導電型の第3半導体層をさらに備える

前記(1)または(2)に記載の光検出素子。

(4)

前記第2半導体層は、前記基板の表面に向かって不純物濃度が濃くなる電位勾配を有する

前記(1)乃至(3)のいずれかに記載の光検出素子。

(5)

前記第2半導体層の前記基板の深さ方向に隣接して、不純物濃度が低い前記第1導電型または前記第2導電型の第4半導体層をさらに備える

前記(1)乃至(4)のいずれかに記載の光検出素子。

(6)

前記第4半導体層は、前記第2半導体層に対して前記基板の表面側に隣接し、前記第2導電型である

前記(5)に記載の光検出素子。

(7)

前記第4半導体層は、前記第2半導体層に対して前記基板の裏面側に隣接し、前記第2導電型である

前記(5)または(6)に記載の光検出素子。

(8)

前記第4半導体層は、前記第2半導体層に対して前記基板の表面側に隣接し、前記第1導電型である

前記(5)に記載の光検出素子。

(9)

前記第4半導体層は、前記第2半導体層に対して前記基板の裏面側に隣接し、前記第1導電型である

前記(5)または(8)に記載の光検出素子。

(10)

前記基板の表面に形成された前記第1導電型のウェル内に、読み出し回路をさらに備える

前記(1)乃至(9)のいずれかに記載の光検出素子。

(11)

前記読み出し回路は、複数の画素で共有される

前記(10)に記載の光検出素子。

(12)

前記第2半導体層に隣接し、かつ、前記基板の表面に、前記第1導電型の第5半導体層をさらに備える

前記(10)または(11)に記載の光検出素子。

(13)

前記読み出し回路は、ゲート電極を制御することによって、信号の蓄積と読み出しを切り替える

前記(10)乃至(12)のいずれかに記載の光検出素子。

(14)

マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層を形成し、

平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層を形成し、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成された

光検出素子の製造方法。

(15)

前記第2導電型のウェル内の前記画素の境界近傍の外周部に、第1導電型のイオン注入を行うことによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とを形成する

前記(14)に記載の光検出素子の製造方法。

(16)

前記第2導電型のウェルは、前記基板にイオン注入を行うことによって形成される

前記(15)に記載の光検出素子の製造方法。

(17)

前記第2導電型のウェルとして、前記第2導電型の前記基板が用いられる

前記(15)に記載の光検出素子の製造方法。

(18)

前記第2導電型のイオンを含んだ第1酸化膜を埋め込み、熱拡散によって前記第2半導体層を形成した後、前記第1酸化膜を除去して、その除去された部分に、前記第1導電型のイオンを含んだ第2酸化膜を埋め込み、熱拡散によって前記第1半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とを形成する

前記(15)に記載の光検出素子の製造方法。

(19)

前記第1導電型のイオンを含んだ第1酸化膜を埋め込み、前記第2導電型のイオンを含んだ第2酸化膜を前記第1酸化膜とは別の領域に埋め込み、熱拡散によって前記第1半導体層と前記第2半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とを形成する

前記(15)に記載の光検出素子の製造方法。

(20)

前記基板の前記画素の境界に、前記基板の所定の深さまで掘り込んだトレンチを形成し、前記トレンチの側面から前記第1導電型のイオン注入と前記第2導電型のイオン注入を行うことで、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とを形成する

前記(15)に記載の光検出素子の製造方法。

Claims (15)

- マトリクス状に配置された複数の画素を備え、

前記画素は、

画素境界近傍の外周部に形成された第1導電型の第1半導体層と、

平面視において前記第1半導体層の内側に前記第1半導体層と接触して形成された、前記第1導電型と反対の第2導電型の第2半導体層と、

平面視において前記第2半導体層の内側に前記第2半導体層と接触して形成された、前記第2半導体層よりも不純物濃度が低い前記第2導電型の第3半導体層と

を備え、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、断面視で基板の深さ方向に縦長に形成されるように構成された

光検出素子。 - マトリクス状に配置された複数の画素を備え、

前記画素は、

画素境界近傍の外周部に形成された第1導電型の第1半導体層と、

平面視において前記第1半導体層の内側に前記第1半導体層と接触して形成された、前記第1導電型と反対の第2導電型の第2半導体層と

を備え、

前記第2半導体層は、基板の表面に向かって不純物濃度が濃くなる電位勾配を有し、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、断面視で前記基板の深さ方向に縦長に形成されるように構成された

光検出素子。 - 画素境界に、隣接する画素間を絶縁分離する分離部をさらに備え、

前記高電界領域は、前記分離部に隣接して形成されるように構成された

請求項1または2に記載の光検出素子。 - 前記第2半導体層の前記基板の深さ方向に隣接して、不純物濃度が低い前記第1導電型または前記第2導電型の第4半導体層をさらに備える

請求項1または2に記載の光検出素子。 - 前記第4半導体層は、前記第2半導体層に対して前記基板の表面側に隣接し、前記第1導電型または前記第2導電型のいずれかである

請求項4に記載の光検出素子。 - 前記第4半導体層は、前記第2半導体層に対して前記基板の裏面側に隣接し、前記第1導電型または前記第2導電型のいずれかである

請求項4に記載の光検出素子。 - 前記分離部の断面視の形状は、テーパ形状である

請求項3に記載の光検出素子。 - 画素内の対向する前記高電界領域の平面方向の距離が前記基板の表面側と裏面側とで異なる

請求項1乃至7のいずれかに記載の光検出素子。 - 前記基板の表面に形成された前記第1導電型のウェル内に、読み出し回路をさらに備える

請求項1または2に記載の光検出素子。 - 前記読み出し回路は、複数の前記画素で共有される

請求項9に記載の光検出素子。 - 前記第2半導体層に隣接し、かつ、前記基板の表面に、前記第1導電型の第5半導体層をさらに備える

請求項9に記載の光検出素子。 - 前記読み出し回路は、ゲート電極を制御することによって、信号の蓄積と読み出しを切り替える

請求項11に記載の光検出素子。 - マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層を形成し、

平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層を形成し、

前記第2導電型のイオンを含んだ第1酸化膜を埋め込み、熱拡散によって前記第2半導体層を形成した後、前記第1酸化膜を除去して、その除去された部分に、前記第1導電型のイオンを含んだ第2酸化膜を埋め込み、熱拡散によって前記第1半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成された

光検出素子の製造方法。 - マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層を形成し、

平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層を形成し、

前記第1導電型のイオンを含んだ第1酸化膜を埋め込み、前記第2導電型のイオンを含んだ第2酸化膜を前記第1酸化膜とは別の領域に埋め込み、熱拡散によって前記第1半導体層と前記第2半導体層を形成することによって、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、基板の深さ方向に形成されるように構成された

光検出素子の製造方法。 - マトリクス状に配置される画素の境界近傍の外周部に、第1導電型の第1半導体層を形成し、

平面視において前記第1半導体層の内側に、前記第1導電型と反対の第2導電型の第2半導体層を形成し、

基板の前記画素の境界に、前記基板の所定の深さまで掘り込んだトレンチを形成し、前記トレンチの側面から前記第1導電型のイオン注入と前記第2導電型のイオン注入を行うことで、前記外周部の前記第1半導体層と、その内側の前記第2半導体層とが形成され、

逆バイアス電圧が印加されたときに前記第1半導体層と前記第2半導体層とで形成される高電界領域が、前記基板の深さ方向に形成されるように構成された

光検出素子の製造方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2017219685 | 2017-11-15 | ||

| JP2017219685 | 2017-11-15 | ||

| PCT/JP2018/040660 WO2019098035A1 (ja) | 2017-11-15 | 2018-11-01 | 光検出素子およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2019098035A1 JPWO2019098035A1 (ja) | 2020-10-01 |

| JP7242527B2 true JP7242527B2 (ja) | 2023-03-20 |

Family

ID=66540222

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2019527577A Active JP7242527B2 (ja) | 2017-11-15 | 2018-11-01 | 光検出素子およびその製造方法 |

Country Status (7)

| Country | Link |

|---|---|

| US (2) | US11264420B2 (ja) |

| EP (1) | EP3553824B1 (ja) |

| JP (1) | JP7242527B2 (ja) |

| KR (2) | KR102615816B1 (ja) |

| CN (1) | CN110050348B (ja) |

| DE (1) | DE112018005850T5 (ja) |

| WO (1) | WO2019098035A1 (ja) |

Families Citing this family (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN110050348B (zh) | 2017-11-15 | 2024-05-14 | 索尼半导体解决方案公司 | 光检测元件及其制造方法 |

| JP2021052130A (ja) * | 2019-09-26 | 2021-04-01 | ソニーセミコンダクタソリューションズ株式会社 | 半導体装置及びその製造方法、並びに電子機器 |

| TWI867078B (zh) * | 2019-11-19 | 2024-12-21 | 日商索尼半導體解決方案公司 | 固態攝像裝置及電子機器 |

| JP2021114538A (ja) * | 2020-01-20 | 2021-08-05 | ソニーセミコンダクタソリューションズ株式会社 | 撮像素子および撮像装置 |

| US11508867B2 (en) | 2020-01-28 | 2022-11-22 | Adaps Photonics Inc. | Single photon avalanche diode device |

| TWI872166B (zh) * | 2020-03-16 | 2025-02-11 | 日商索尼半導體解決方案公司 | 受光元件及測距系統 |

| US11329087B2 (en) * | 2020-03-25 | 2022-05-10 | Globalfoundries U.S. Inc. | Photodetectors with adjacent anode-cathode pairs |

| US11621287B2 (en) * | 2020-04-16 | 2023-04-04 | Vanguard International Semiconductor Corporation | Optical sensor device with reduced thickness and method for forming the same |

| CN112086524A (zh) * | 2020-08-28 | 2020-12-15 | 北京智创芯源科技有限公司 | 一种红外探测装置及制备方法 |

| JP7775219B2 (ja) * | 2020-12-02 | 2025-11-25 | ソニーセミコンダクタソリューションズ株式会社 | 光検出装置及び測距システム |

| JP7653793B2 (ja) * | 2021-01-22 | 2025-03-31 | キヤノン株式会社 | 光電変換装置、光電変換システムおよび移動体 |

| US12154992B2 (en) * | 2021-08-13 | 2024-11-26 | Texas Instruments Incorporated | Photodiode integrated with circuit |

| US20230083263A1 (en) * | 2021-09-15 | 2023-03-16 | Kabushiki Kaisha Toshiba | Light detector, light detection system, lidar device, and mobile body |

| CN114335230B (zh) * | 2021-12-29 | 2024-03-15 | 上海集成电路研发中心有限公司 | 雪崩光电二极管及其制作方法 |

| JP7799488B2 (ja) * | 2022-01-01 | 2026-01-15 | キヤノン株式会社 | 光電変換装置、光電変換システム、および機器 |

| JP2023120672A (ja) * | 2022-02-18 | 2023-08-30 | ソニーセミコンダクタソリューションズ株式会社 | 光検出装置及び電子機器 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2006068184A1 (ja) | 2004-12-24 | 2006-06-29 | Hamamatsu Photonics K.K. | ホトダイオードアレイ |

| US20100177223A1 (en) | 2009-01-05 | 2010-07-15 | Sony Corporation | Solid-state imaging device and camera |

| US20110241149A1 (en) | 2010-03-30 | 2011-10-06 | Stmicroelectronics S.R.L. | Geiger-mode avalanche photodiode with high signal-to-noise ratio, and corresponding manufacturing process |

| WO2012032353A2 (en) | 2010-09-08 | 2012-03-15 | The University Court Of The University Of Edinburgh | Single photon avalanche diode for cmos circuits |

| JP2015041746A (ja) | 2013-08-23 | 2015-03-02 | 株式会社豊田中央研究所 | シングルフォトンアバランシェダイオード |

| WO2017047422A1 (ja) | 2015-09-17 | 2017-03-23 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子、電子機器、及び、固体撮像素子の製造方法 |

Family Cites Families (18)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6359293B1 (en) * | 1999-08-17 | 2002-03-19 | Agere Systems Guardian Corp. | Integrated optoelectronic device with an avalanche photodetector and method of making the same using commercial CMOS processes |

| JP4595464B2 (ja) * | 2004-09-22 | 2010-12-08 | ソニー株式会社 | Cmos固体撮像素子の製造方法 |

| JP4691990B2 (ja) * | 2005-01-05 | 2011-06-01 | ソニー株式会社 | 固体撮像装置及びその製造方法 |

| TWI443817B (zh) | 2006-07-03 | 2014-07-01 | 濱松赫德尼古斯股份有限公司 | Photodiode array |

| IT1392366B1 (it) * | 2008-12-17 | 2012-02-28 | St Microelectronics Rousset | Fotodiodo operante in modalita' geiger con resistore di soppressione integrato e controllabile, schiera di fotodiodi e relativo procedimento di fabbricazione |

| IT1393781B1 (it) * | 2009-04-23 | 2012-05-08 | St Microelectronics Rousset | Fotodiodo operante in modalita' geiger con resistore di soppressione integrato e controllabile ad effetto jfet, schiera di fotodiodi e relativo procedimento di fabbricazione |

| IT1399075B1 (it) * | 2010-03-23 | 2013-04-05 | St Microelectronics Srl | Metodo di rilevazione di posizioni di fotoni che impingono su un fotodiodo a valanga geiger-mode, relativi fotodiodi a valanga geiger-mode e processo di fabbricazione |

| JP2012049289A (ja) * | 2010-08-26 | 2012-03-08 | Sony Corp | 固体撮像装置とその製造方法、並びに電子機器 |

| JP5935237B2 (ja) * | 2011-03-24 | 2016-06-15 | ソニー株式会社 | 固体撮像装置および電子機器 |

| TW201405792A (zh) * | 2012-07-30 | 2014-02-01 | 新力股份有限公司 | 固體攝像裝置、固體攝像裝置之製造方法及電子機器 |

| JP2014127519A (ja) * | 2012-12-25 | 2014-07-07 | Sony Corp | 固体撮像素子、及び、電子機器 |

| JP2015153772A (ja) * | 2014-02-10 | 2015-08-24 | 株式会社東芝 | 固体撮像装置 |

| JP2016015430A (ja) * | 2014-07-03 | 2016-01-28 | ソニー株式会社 | 固体撮像素子および電子機器 |

| JP2016162917A (ja) * | 2015-03-03 | 2016-09-05 | ソニー株式会社 | 固体撮像素子および電子機器 |

| EP3516692B1 (en) * | 2016-09-23 | 2022-02-16 | Apple Inc. | Stacked backside illuminated spad array |

| EP3309847B1 (en) * | 2016-10-13 | 2024-06-05 | Canon Kabushiki Kaisha | Photo-detection apparatus and photo-detection system |

| US10312275B2 (en) * | 2017-04-25 | 2019-06-04 | Semiconductor Components Industries, Llc | Single-photon avalanche diode image sensor with photon counting and time-of-flight detection capabilities |

| CN110050348B (zh) | 2017-11-15 | 2024-05-14 | 索尼半导体解决方案公司 | 光检测元件及其制造方法 |

-

2018

- 2018-11-01 CN CN201880004653.3A patent/CN110050348B/zh active Active

- 2018-11-01 EP EP18878386.4A patent/EP3553824B1/en active Active

- 2018-11-01 WO PCT/JP2018/040660 patent/WO2019098035A1/ja not_active Ceased

- 2018-11-01 US US16/463,760 patent/US11264420B2/en active Active

- 2018-11-01 KR KR1020197015124A patent/KR102615816B1/ko active Active

- 2018-11-01 KR KR1020237042986A patent/KR20230170996A/ko not_active Ceased

- 2018-11-01 DE DE112018005850.6T patent/DE112018005850T5/de not_active Withdrawn

- 2018-11-01 JP JP2019527577A patent/JP7242527B2/ja active Active

-

2022

- 2022-01-19 US US17/579,391 patent/US11791359B2/en active Active

Patent Citations (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2006068184A1 (ja) | 2004-12-24 | 2006-06-29 | Hamamatsu Photonics K.K. | ホトダイオードアレイ |

| JP2006179828A (ja) | 2004-12-24 | 2006-07-06 | Hamamatsu Photonics Kk | ホトダイオードアレイ |

| US20090121306A1 (en) | 2004-12-24 | 2009-05-14 | Yoshitaka Ishikawa | Photodiode Array |

| US20100177223A1 (en) | 2009-01-05 | 2010-07-15 | Sony Corporation | Solid-state imaging device and camera |

| JP2010157665A (ja) | 2009-01-05 | 2010-07-15 | Sony Corp | 固体撮像素子、カメラ |

| US20110241149A1 (en) | 2010-03-30 | 2011-10-06 | Stmicroelectronics S.R.L. | Geiger-mode avalanche photodiode with high signal-to-noise ratio, and corresponding manufacturing process |

| WO2012032353A2 (en) | 2010-09-08 | 2012-03-15 | The University Court Of The University Of Edinburgh | Single photon avalanche diode for cmos circuits |

| US20130193546A1 (en) | 2010-09-08 | 2013-08-01 | The University Court Of The University Of Edinburg | Single photon avalanche diode for cmos circuits |

| JP2015041746A (ja) | 2013-08-23 | 2015-03-02 | 株式会社豊田中央研究所 | シングルフォトンアバランシェダイオード |

| WO2017047422A1 (ja) | 2015-09-17 | 2017-03-23 | ソニーセミコンダクタソリューションズ株式会社 | 固体撮像素子、電子機器、及び、固体撮像素子の製造方法 |

| US20180182789A1 (en) | 2015-09-17 | 2018-06-28 | Sony Semiconductor Solutions Corporation | Solid-state image sensing device, electronic device, and method for manufacturing solid-state image sensing device |

Also Published As

| Publication number | Publication date |

|---|---|

| JPWO2019098035A1 (ja) | 2020-10-01 |

| EP3553824A1 (en) | 2019-10-16 |

| US11264420B2 (en) | 2022-03-01 |

| DE112018005850T5 (de) | 2020-08-13 |

| CN110050348B (zh) | 2024-05-14 |

| KR20200083373A (ko) | 2020-07-08 |

| US20210183917A1 (en) | 2021-06-17 |

| US20220149090A1 (en) | 2022-05-12 |

| EP3553824A4 (en) | 2020-04-08 |

| US11791359B2 (en) | 2023-10-17 |

| EP3553824B1 (en) | 2022-07-20 |

| KR102615816B1 (ko) | 2023-12-21 |

| WO2019098035A1 (ja) | 2019-05-23 |

| KR20230170996A (ko) | 2023-12-19 |

| CN110050348A (zh) | 2019-07-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP7242527B2 (ja) | 光検出素子およびその製造方法 | |

| US7928478B2 (en) | Image sensor with improved color crosstalk | |

| TWI718760B (zh) | Cmos圖像感測器及形成圖像感測器的方法 | |

| US9806121B2 (en) | Solid-state imaging device | |

| US20160218138A1 (en) | Solid-state image pickup device and method for manufacturing a solid-state image pickup device | |

| US12183767B2 (en) | Complementary metal-oxide-semiconductor image sensor and method of making | |

| CN102804377A (zh) | 具有偏压正侧和背侧的影像传感器 | |

| US20170200758A1 (en) | Cmos image sensor and fabrication method thereof | |

| KR20170068842A (ko) | 이미지 센서 및 그 제조 방법 | |

| KR20170100225A (ko) | 격리 구조물 및 이를 포함하는 이미지 센서 | |

| JP2020064912A (ja) | 撮像装置の製造方法 | |

| CN116799017A (zh) | 具有防高光溢出结构的像素单元及图像传感器 | |

| US20250016471A1 (en) | Imaging device | |

| JP7199013B2 (ja) | 光検出器 | |

| WO2023190406A1 (ja) | 半導体装置、固体撮像装置 | |

| KR20230021300A (ko) | 후면조사 이미지센서에서의 spad 픽셀 구조 | |

| JP2020161775A (ja) | 光検出器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20210913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20220712 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20220822 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20221004 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20221124 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20230207 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20230308 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 7242527 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |