JP6929282B2 - 時間ベースの遅延ラインアナログ・デジタルコンバータ - Google Patents

時間ベースの遅延ラインアナログ・デジタルコンバータ Download PDFInfo

- Publication number

- JP6929282B2 JP6929282B2 JP2018523813A JP2018523813A JP6929282B2 JP 6929282 B2 JP6929282 B2 JP 6929282B2 JP 2018523813 A JP2018523813 A JP 2018523813A JP 2018523813 A JP2018523813 A JP 2018523813A JP 6929282 B2 JP6929282 B2 JP 6929282B2

- Authority

- JP

- Japan

- Prior art keywords

- digital

- circuit

- current

- delay

- delay line

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/004—Reconfigurable analogue/digital or digital/analogue converters

- H03M1/007—Reconfigurable analogue/digital or digital/analogue converters among different resolutions

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

- H02M3/156—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only with automatic control of output voltage or current, e.g. switching regulators

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/131—Digitally controlled

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K5/13—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals

- H03K5/14—Arrangements having a single output and transforming input signals into pulses delivered at desired time intervals by the use of delay lines

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/10—Calibration or testing

- H03M1/1009—Calibration

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/10—Calibration or testing

- H03M1/1009—Calibration

- H03M1/1028—Calibration at two points of the transfer characteristic, i.e. by adjusting two reference values, e.g. offset and gain error

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/10—Calibration or testing

- H03M1/1009—Calibration

- H03M1/1033—Calibration over the full range of the converter, e.g. for correcting differential non-linearity

- H03M1/1057—Calibration over the full range of the converter, e.g. for correcting differential non-linearity by trimming, i.e. by individually adjusting at least part of the quantisation value generators or stages to their nominal values

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/10—Calibration or testing

- H03M1/1071—Measuring or testing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/18—Automatic control for modifying the range of signals the converter can handle, e.g. gain ranging

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/34—Analogue value compared with reference values

- H03M1/38—Analogue value compared with reference values sequentially only, e.g. successive approximation type

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K5/00—Manipulating of pulses not covered by one of the other main groups of this subclass

- H03K2005/00013—Delay, i.e. output pulse is delayed after input pulse and pulse length of output pulse is dependent on pulse length of input pulse

- H03K2005/00019—Variable delay

- H03K2005/00058—Variable delay controlled by a digital setting

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03M—CODING; DECODING; CODE CONVERSION IN GENERAL

- H03M1/00—Analogue/digital conversion; Digital/analogue conversion

- H03M1/12—Analogue/digital converters

- H03M1/50—Analogue/digital converters with intermediate conversion to time interval

- H03M1/502—Analogue/digital converters with intermediate conversion to time interval using tapped delay lines

Description

本願は、各々が2016年4月12日に出願された米国仮出願第62/321,668号、62/321,685号、62/321,687号,62/321,694号に対する優先権を主張するものであり、これらは、全体が参照により本明細書中に援用される。

本開示は、時間ベースの遅延ラインアナログ・デジタルコンバータ(ADC)に関し、特に、背景較正、レンジ調節、およびレンジ外推定を伴う、そのようなコンバータに関する。

本発明は、例えば、以下を提供する。

(項目1)

差動デジタル遅延ラインアナログ・デジタルコンバータ(ADC)であって、

複数の差動デジタル遅延ラインと、

前記差動デジタル遅延ライン内に含まれる遅延要素のセットを備える第1の回路と、

前記差動デジタル遅延ライン内に含まれる遅延要素の別のセットを備える第2の回路と

を備え、

前記第1の回路は、入力のアナログ・デジタル変換を表すデータを発生させるように構成され、

前記第2の回路は、前記差動デジタル遅延ラインへのソースを較正するように構成される、

ADC。

(項目2)

前記第1の回路は、入力電圧と基準電圧との間の差異を測定するように構成される、項目1または3−10のいずれかに記載のADC。

(項目3)

前記差動デジタル遅延ラインのそれぞれへの基準電流を反映するように構成される電流ソース回路をさらに備える、項目1−2または5−10のいずれかに記載のADC。

(項目4)

前記差動デジタル遅延ラインのそれぞれへの基準電流を反映するように構成される電流ソース回路をさらに備え、前記第2の回路は、前記基準電流を調節し、誤差を最小限にするように構成される、項目1−2または5−10のいずれかに記載のADC。

(項目5)

入力差動電圧を差動電流に変換するように構成されるトランスコンダクタをさらに備え、前記第1の回路は、前記差動電流を測定し、前記差動電圧を表すデータを発生させるように構成される、項目1−4または6−10のいずれかに記載のADC。

(項目6)

入力差動電圧を差動電流に変換することと、

前記複数の差動デジタル遅延ラインに基づいて、入力を受け取り、電圧・電流レンジを調節することと

を行うように構成される、トランスコンダクタ

をさらに備える、項目1−5または7−10のいずれかに記載のADC。

(項目7)

各差動デジタル遅延ラインは、電流限定バッファ鎖を含む、項目1−6または8−10のいずれかに記載のADC。

(項目8)

所与の差動デジタル遅延ラインが、前記所与の差動デジタル遅延ラインに適用される差動電流に従って、ある速度で動作するように構成され、

前記ADCはさらに、ラッチを備え、

前記ラッチは、より高速の差動デジタル遅延ラインの完了に応じて、より低速の差動デジタル遅延ラインからのデータを保存するように構成される、

項目1−7または9−10のいずれかに記載のADC。

(項目9)

前記差動デジタル遅延ライン内に含まれる遅延要素のさらに別のセットを備える第3の回路をさらに備え、前記第3の回路は、前記ADCへの入力が入力レンジから外れている程度を示すデータを生成するように構成される、項目1−8または10のいずれかに記載のADC。

(項目10)

相互から独立して前記デジタル遅延ラインの長さを調節することによって前記ADCを較正するための第4の回路をさらに備える、項目1−9のいずれかに記載のADC。

(項目11)

差動デジタル遅延ラインアナログ・デジタルコンバータ(ADC)であって、

複数の差動デジタル遅延ラインと、

前記差動デジタル遅延ライン内に含まれる遅延要素のセットを備える第1の回路と、

前記差動デジタル遅延ライン内に含まれる遅延要素の別のセットを備える第2の回路と

を備え、

前記第1の回路は、入力のアナログ・デジタル変換を表すデータを発生させるように構成され、

前記第2の回路は、前記ADCへの入力が入力レンジから外れている程度を示すデータを生成するように構成される、

ADC。

(項目12)

前記第1の回路は、入力電圧と基準電圧との間の差異を測定するように構成される、項目11または13−20のいずれかに記載のADC。

(項目13)

前記差動デジタル遅延ラインのそれぞれへの基準電流を反映するように構成される電流ソース回路をさらに備える、項目11−12または15−20のいずれかに記載のADC。

(項目14)

前記差動デジタル遅延ラインのそれぞれへの基準電流を反映するように構成される電流ソース回路をさらに備え、前記第2の回路は、前記基準電流を調節し、誤差を最小限にするように構成される、項目11−12または15−20のいずれかに記載のADC。

(項目15)

入力差動電圧を差動電流に変換するように構成されるトランスコンダクタをさらに備え、前記第1の回路は、前記差動電流を測定し、前記差動電圧を表すデータを発生させるように構成される、項目11−14または16−20のいずれかに記載のADC。

(項目16)

入力差動電圧を差動電流に変換することと、

前記複数の差動デジタル遅延ラインに基づいて、入力を受け取り、電圧・電流レンジを調節することと

を行うように構成される、トランスコンダクタ

をさらに備える、項目11−15または17−20のいずれかに記載のADC。

(項目17)

各差動デジタル遅延ラインは、電流限定バッファ鎖を含む、項目11−16または18−20のいずれかに記載のADC。

(項目18)

所与の差動デジタル遅延ラインが、前記所与の差動デジタル遅延ラインに適用される差動電流に従って、ある速度で動作するように構成され、

前記ADCはさらに、ラッチを備え、

前記ラッチは、より高速の差動デジタル遅延ラインの完了に応じて、より低速の差動デジタル遅延ラインからのデータを保存するように構成される、

項目11−17または19−20のいずれかに記載のADC。

(項目19)

前記差動デジタル遅延ライン内に含まれる遅延要素のさらに別のセットを備える第3の回路をさらに備え、前記第3の回路は、前記差動デジタル遅延ラインへのソースを較正するように構成される、項目11−18または20のいずれかに記載のADC。

(項目20)

相互から独立して前記デジタル遅延ラインの長さを調節することによって前記ADCを較正するための第4の回路をさらに備える、項目11−19のいずれかに記載のADC。

(項目21)

差動デジタル遅延ラインアナログ・デジタルコンバータ(ADC)であって、

複数の差動デジタル遅延ラインと、

前記差動デジタル遅延ライン内に含まれる遅延要素のセットを備える第1の回路と、

トランスコンダクタであって、

入力差動電圧を差動電流に変換することと、

前記複数の差動デジタル遅延ラインに基づいて、入力を受け取り、電圧・電流レンジを調節することと

を行うように構成される、トランスコンダクタと

を備える、ADC。

(項目22)

前記差動デジタル遅延ライン内に含まれる遅延要素のさらに別のセットを備える、第2の回路をさらに備え、前記第2の回路は、前記ADCへの入力が入力レンジから外れている程度を示すデータを生成するように構成される、項目21に記載のADC。

(項目23)

項目1−22に記載のADCのいずれかを備える、マイクロコントローラ。

(項目24)

項目1−22に記載のADCの構成のいずれかの動作を含む、方法。

本開示の追加、変更、修正、または他の順列が、当業者の知識、技術、および理解に従って行われ得る。

Claims (14)

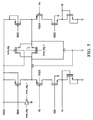

- 差動デジタル遅延ラインアナログ・デジタルコンバータであって、

入力回路と、

ソースからの入力差動電圧を差動電流に変換するように構成されるトランスコンダクタ入力段と、

2つのデジタル遅延ラインであって、前記2つのデジタル遅延ラインは、それぞれ、前記差動電流の第1の電流または第2の電流のどちらかを受信し、各デジタル遅延ラインは、

第1の回路であって、前記第1の回路は、遅延要素のセットを備え、各々、前記第1の電流または前記第2の電流によってバイアスされ、デジタル信号を遅延させるように構成され、前記入力回路は、前記2つのデジタル遅延ラインの第1のデジタル遅延ラインおよび第2のデジタル遅延ラインにデジタル信号をフィードし、前記第1のデジタル遅延ラインと前記第2のデジタル遅延ラインとの間の時間遅延が、前記第1の回路によって測定され、これにより、前記入力差動電圧のアナログ・デジタル変換を表すサーモメータコードを発生させる、第1の回路と、

前記第1の回路と直列に結合される構成可能な第2の回路であって、前記第2の回路は、遅延要素の別のセットを備え、各々、前記第1の電流または前記第2の電流によってバイアスされ、前記デジタル信号を遅延させるように構成される、第2の回路と

を備える、2つのデジタル遅延ラインと

を備え、

前記第2の回路は、前記2つのデジタル遅延ラインの前記第1のデジタル遅延ラインまたは前記第2のデジタル遅延ラインの長さを前記2つのデジタル遅延ラインのうちの他方のデジタル遅延ラインに対して個々に調節するように制御可能な関連付けられたマルチプレクサの有効化を通じて前記デジタル遅延ラインの各々において追加の遅延要素を追加するように構成される、アナログ・デジタルコンバータ。 - 前記第1の回路(706)は、入力電圧と基準電圧との間の差異を測定するように構成される、請求項1に記載のアナログ・デジタルコンバータ。

- 前記トランスコンダクタ入力段(200)は、前記デジタル遅延ラインの各々へのバイアス電流を反映するように構成される制御可能な電流ソース回路をさらに備える、請求項1に記載のアナログ・デジタルコンバータ。

- 各マルチプレクサの入力は、関連付けられた追加の遅延要素(116;118)の入力および出力に結合され、各マルチプレクサは、追加の遅延要素をそれぞれのデジタル遅延ラインに含めるまたは排除するように、インデックス化されたコマンドを通して制御される、請求項1に記載のアナログ・デジタルコンバータ。

- オーバーフローを示すために各デジタル遅延ラインのための別の遅延要素(116、118)をさらに備え、前記トランスコンダクタ入力段は、前記別の遅延要素(116、118)の出力信号(オーバーフロー)を受信し、電圧・電流レンジを調節するように構成される、請求項4に記載のアナログ・デジタルコンバータ。

- 各遅延要素は、電流スターブ型バッファによって形成され、前記電流スターブ型バッファは、それぞれの第1の電流または第2の電流が前記電流スターブ型バッファに到達すると、その入力を伝搬するようにアクティブ化する、請求項1に記載のアナログ・デジタルコンバータ。

- 前記第1の回路のそれぞれの遅延要素から出力信号を受信する複数のNANDゲートと、

前記NANDゲートの出力と結合されるラッチと

をさらに備え、

前記ラッチは、前記デジタル遅延ラインのうちのより高速なものの完了に応じて、前記デジタル遅延ラインのうちのより低速のものからのデータを保存するように構成される、請求項1〜6のいずれかに記載のアナログ・デジタルコンバータ。 - 各遅延ラインの最後の遅延要素の出力と結合されるORゲートをさらに備え、前記ORゲートの出力は、前記ラッチを制御する信号を発生させる、請求項7に記載のアナログ・デジタルコンバータ。

- 各デジタル遅延ラインは、前記第1の回路および前記第2の回路と直列に結合される第3の回路をさらに備え、前記第3の回路は、遅延要素のさらに別のセットを備え、各々、前記第1の電流または前記第2の電流によってバイアスされる、請求項1に記載のアナログ・デジタルコンバータ。

- 前記第1の回路のそれぞれの遅延要素から出力信号を受信する複数のNANDゲートと、

前記NANDゲートの出力と結合されるラッチであって、前記ラッチは、前記デジタル遅延ラインのうちのより高速なものの完了に応じて、前記デジタル遅延ラインのうちのより低速のものからのデータを保存するように構成される、ラッチと

各遅延ラインの最後の遅延要素の出力と結合されるORゲートであって、前記ORゲートの出力は、前記ラッチを制御する信号を発生させるORゲートと

をさらに備え、前記アナログ・デジタルコンバータは、前記第3の回路のそれぞれの遅延要素から出力信号を受信する複数のさらなるNANDゲートをさらに備え、前記第3の回路の前記遅延要素の出力は、前記アナログ・デジタルコンバータへの入力が所定の入力レンジから外れている程度を示すオーバーフローデータを生成する、請求項9に記載のアナログ・デジタルコンバータ。 - 差動デジタル遅延ラインアナログ・デジタルコンバータを作動させるための方法であって、前記方法は、

ソースからの入力差動電圧を差動電流に変換することと、

第1のデジタル遅延ラインおよび第2のデジタル遅延ラインに前記差動電流をフィードすることであって、各デジタル遅延ラインは、第1の遅延要素のセットを備える第1の回路を備え、各々、前記差動電流のうちの第1の電流または第2の電流によってバイアスされ、デジタル信号を遅延させるように構成される、ことと、

前記第1の電流によって前記第1のデジタル遅延ラインの前記第1の回路の遅延要素をバイアスし、前記第2の電流によって前記第2のデジタル遅延ラインの前記第1の回路の遅延要素をバイアスすることと、

前記第1のデジタル遅延ラインおよび前記第2のデジタル遅延ラインにデジタル信号をフィードすることであって、前記第1のデジタル遅延ラインと前記第2のデジタル遅延ラインとの間の時間遅延が前記第1の回路によって測定され、それによって、前記入力差動電圧のアナログ・デジタル変換を表すサーモメータコードを発生させ、各デジタル遅延ラインは、前記第1の回路と直列に結合される構成可能な第2の回路をさらに備え、前記第2の回路は、遅延要素の別のセットを備え、各々、前記第1の電流または前記第2の電流によってバイアスされ、前記デジタル信号を遅延させるように構成される、ことと、

前記第1のデジタル遅延ラインまたは前記第2のデジタル遅延ラインの長さを他方のデジタル遅延ラインに対して調節するように、それぞれのマルチプレクサを通じて追加の遅延要素を前記第1のデジタル遅延ラインまたは前記第2のデジタル遅延ラインに個々に追加するように前記第2の回路を構成することと

を含む、方法。 - 各マルチプレクサは、追加の遅延要素をそれぞれのデジタル遅延ラインに含めるまたは排除するように、インデックス化されたコマンドを通して制御される、請求項11に記載の方法。

- 各デジタル遅延ラインは、前記第1の回路および前記第2の回路と直列に結合される第3の回路をさらに備え、前記第3の回路は、遅延要素のさらに別のセットを備え、各々、前記第1の電流または前記第2の電流によってバイアスされ、前記第3の回路の前記遅延要素は、前記アナログ・デジタルコンバータへの入力が入力レンジから外れている程度を示すオーバーフローデータを生成するように構成される、請求項11に記載の方法。

- 前記アナログ・デジタルコンバータへの入力が入力レンジから外れている程度を示す前記データによって、前記差動電流を発生させるために使用される電流ソースを制御することをさらに含む、請求項13に記載の方法。

Applications Claiming Priority (11)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201662321668P | 2016-04-12 | 2016-04-12 | |

| US201662321685P | 2016-04-12 | 2016-04-12 | |

| US201662321687P | 2016-04-12 | 2016-04-12 | |

| US201662321694P | 2016-04-12 | 2016-04-12 | |

| US62/321,687 | 2016-04-12 | ||

| US62/321,668 | 2016-04-12 | ||

| US62/321,685 | 2016-04-12 | ||

| US62/321,694 | 2016-04-12 | ||

| US15/484,949 | 2017-04-11 | ||

| US15/484,949 US9948317B2 (en) | 2016-04-12 | 2017-04-11 | Time-based delay line analog to digital converter |

| PCT/US2017/027191 WO2017180732A1 (en) | 2016-04-12 | 2017-04-12 | Time-based delay line analog to digital converter |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2019520716A JP2019520716A (ja) | 2019-07-18 |

| JP2019520716A5 JP2019520716A5 (ja) | 2020-04-30 |

| JP6929282B2 true JP6929282B2 (ja) | 2021-09-01 |

Family

ID=59998462

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018523787A Active JP7036717B2 (ja) | 2016-04-12 | 2017-04-12 | デジタル遅延ラインアナログ・デジタルコンバータおよびデジタルコンパレータを有するマイクロコントローラ |

| JP2018523754A Pending JP2019514230A (ja) | 2016-04-12 | 2017-04-12 | 可変分解能を有する時間ベースの遅延ラインアナログ・デジタルコンバータ |

| JP2018523815A Active JP6934866B2 (ja) | 2016-04-12 | 2017-04-12 | デジタル遅延ラインアナログ・デジタルコンバータを有するマイクロコントローラ |

| JP2018523813A Active JP6929282B2 (ja) | 2016-04-12 | 2017-04-12 | 時間ベースの遅延ラインアナログ・デジタルコンバータ |

Family Applications Before (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018523787A Active JP7036717B2 (ja) | 2016-04-12 | 2017-04-12 | デジタル遅延ラインアナログ・デジタルコンバータおよびデジタルコンパレータを有するマイクロコントローラ |

| JP2018523754A Pending JP2019514230A (ja) | 2016-04-12 | 2017-04-12 | 可変分解能を有する時間ベースの遅延ラインアナログ・デジタルコンバータ |

| JP2018523815A Active JP6934866B2 (ja) | 2016-04-12 | 2017-04-12 | デジタル遅延ラインアナログ・デジタルコンバータを有するマイクロコントローラ |

Country Status (7)

| Country | Link |

|---|---|

| US (7) | US9923570B2 (ja) |

| EP (4) | EP3443670A1 (ja) |

| JP (4) | JP7036717B2 (ja) |

| KR (4) | KR20180127958A (ja) |

| CN (4) | CN108432143B (ja) |

| TW (4) | TW201810955A (ja) |

| WO (4) | WO2017180771A1 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US9923570B2 (en) * | 2016-04-12 | 2018-03-20 | Microchip Technology Incorporated | Time-based delay line analog-to-digital converter with variable resolution |

| FI128846B (fi) * | 2017-03-20 | 2021-01-29 | Beamex Oy Ab | Automaattinen mittauspiirin kalibrointi |

| GB2567420B (en) * | 2017-10-02 | 2020-07-08 | Advanced Risc Mach Ltd | Adaptive voltage scaling methods and systems therefor |

| DE102017223466A1 (de) * | 2017-12-20 | 2019-06-27 | Dialog Semiconductor (Uk) Limited | Analog-digital-wandler mit selbst-verfolgung und selbst-rangingfenster |

| TWI696344B (zh) | 2018-11-16 | 2020-06-11 | 財團法人工業技術研究院 | 線性度改善系統及線性度改善方法 |

| TWI670939B (zh) * | 2018-12-03 | 2019-09-01 | 新唐科技股份有限公司 | 具有校正功能的延遲線電路及其校正方法 |

| CN109660302B (zh) * | 2018-12-05 | 2021-08-03 | 中国人民解放军国防科技大学 | 一种基于数字延时线单元的射频脉宽调制器及调制方法 |

| CN109639281A (zh) * | 2018-12-18 | 2019-04-16 | 四川长虹电器股份有限公司 | 一种用于放大器前端的可控制增益的电压编码电路 |

| US10892746B2 (en) * | 2019-01-14 | 2021-01-12 | Texas Instruments Incorporated | Switch on-time controller with delay line modulator |

| CN115280690B (zh) * | 2020-03-10 | 2024-03-19 | 哲库科技(上海)有限公司 | 用于基于延迟线的收发器校准的方法、装置、系统和介质 |

| IT202000013627A1 (it) | 2020-06-08 | 2021-12-08 | St Microelectronics Srl | Un circuito di controllo per un convertitore elettronico, relativo circuito integrato, convertitore elettronico e procedimento |

| CN114070316B (zh) * | 2021-11-17 | 2023-04-14 | 苏州迅芯微电子有限公司 | 一种多相位时钟产生电路及模数转换器 |

Family Cites Families (44)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4471340A (en) * | 1981-06-02 | 1984-09-11 | The United States Of America As Represented By The Secretary Of The Navy | Analog to digital converter |

| EP0272347B1 (en) * | 1986-12-24 | 1989-06-07 | Hewlett-Packard GmbH | Method of and apparatus for adjusting the intensity profile of an ultrasound beam |

| US4998109A (en) * | 1989-12-13 | 1991-03-05 | Lechevalier Robert E | Analog to digital conversion device by charge integration using delay-line time measurement |

| US5140531A (en) * | 1990-08-01 | 1992-08-18 | General Electric Company | Analog neural nets supplied digital synapse signals on a bit-slice basis |

| US5412349A (en) * | 1992-03-31 | 1995-05-02 | Intel Corporation | PLL clock generator integrated with microprocessor |

| JP4229482B2 (ja) * | 1997-10-24 | 2009-02-25 | 株式会社ルネサステクノロジ | フラッシュメモリ内蔵マイクロコンピュータ |

| WO2000044098A1 (en) * | 1999-01-19 | 2000-07-27 | Steensgaard Madsen Jesper | Residue-compensating a / d converter |

| US6316987B1 (en) * | 1999-10-22 | 2001-11-13 | Velio Communications, Inc. | Low-power low-jitter variable delay timing circuit |

| US7595686B2 (en) * | 2001-11-09 | 2009-09-29 | The Regents Of The University Of Colorado | Digital controller for high-frequency switching power supplies |

| US7346638B2 (en) * | 2003-11-21 | 2008-03-18 | Board Of Regents, The University Of Texas System | Filtering, equalization, and power estimation for enabling higher speed signal transmission |

| US6977605B2 (en) * | 2003-11-26 | 2005-12-20 | Texas Instruments Incorporated | Dummy delay line based DLL and method for clocking in pipeline ADC |

| US20060038596A1 (en) * | 2004-08-18 | 2006-02-23 | Binan Wang | Delay locked loop circuitry and method for optimizing delay timing in mixed signal systems |

| CA2483378A1 (en) * | 2004-10-01 | 2006-04-01 | Aleksandar Prodic | A digital controller for dc-dc switching converters that allows operation at ultra-high constant switching frequencies |

| US7456620B2 (en) * | 2004-12-03 | 2008-11-25 | The Regents Of The University Of Colorado | Determining dead times in switched-mode DC-DC converters |

| US7315270B2 (en) * | 2005-03-04 | 2008-01-01 | The Regents Of The University Of Colorado | Differential delay-line analog-to-digital converter |

| US7902803B2 (en) * | 2005-03-04 | 2011-03-08 | The Regents Of The University Of Colorado | Digital current mode controller |

| WO2007054902A1 (en) * | 2005-11-11 | 2007-05-18 | Nxp B.V. | Integrating analog to digital converter |

| JP4702179B2 (ja) * | 2006-05-22 | 2011-06-15 | 株式会社デンソー | A/d変換回路 |

| US7414553B1 (en) | 2006-11-17 | 2008-08-19 | Zilog, Inc. | Microcontroller having in-situ autocalibrated integrating analog-to-digital converter (IADC) |

| US7652604B2 (en) * | 2007-02-28 | 2010-01-26 | Exar Corporation | Programmable analog-to-digital converter for low-power DC-DC SMPS |

| US7525471B2 (en) * | 2007-02-28 | 2009-04-28 | Exar Corporation | Wide-input windowed nonlinear analog-to-digital converter for high-frequency digitally controlled SMPS |

| DE102007026684B4 (de) * | 2007-06-08 | 2009-03-19 | Gesellschaft für Schwerionenforschung mbH | Zeit-Amplituden-Konverter-Bauelement |

| KR100921815B1 (ko) * | 2007-06-18 | 2009-10-16 | 주식회사 애트랩 | 지연시간 측정회로 및 지연시간 측정 방법 |

| US8022849B2 (en) * | 2008-04-14 | 2011-09-20 | Qualcomm, Incorporated | Phase to digital converter in all digital phase locked loop |

| TWI392241B (zh) * | 2009-02-18 | 2013-04-01 | Realtek Semiconductor Corp | 迴音處理裝置與其相關方法 |

| KR101069671B1 (ko) * | 2009-04-15 | 2011-10-04 | 주식회사 하이닉스반도체 | 신호 주파수 변경 회로 및 그 주파수 변경 방법 |

| US7893861B2 (en) * | 2009-06-30 | 2011-02-22 | International Business Machines Corporation | Time-to-digital based analog-to-digital converter architecture |

| EP2330744A1 (en) * | 2009-11-30 | 2011-06-08 | Nxp B.V. | Analog to digital conversion circuit and method |

| JP2011160369A (ja) * | 2010-02-04 | 2011-08-18 | Sony Corp | 電子回路、電子機器、デジタル信号処理方法 |

| US8283950B2 (en) * | 2010-08-11 | 2012-10-09 | Micron Technology, Inc. | Delay lines, amplifier systems, transconductance compensating systems and methods of compensating |

| US8289062B2 (en) * | 2010-09-16 | 2012-10-16 | Micron Technology, Inc. | Analog delay lines and adaptive biasing |

| US8487806B2 (en) * | 2010-11-26 | 2013-07-16 | Electronics And Telecommunications Research Institute | Voltage-time converters and time-domain voltage comparators including the same |

| US8542138B2 (en) * | 2011-01-28 | 2013-09-24 | The Regents Of The University Of California | Ring oscillator delta sigma ADC modulator with replica path nonlinearity calibration |

| KR101202742B1 (ko) * | 2011-04-05 | 2012-11-19 | 연세대학교 산학협력단 | 시간-디지털 변환기 및 변환방법 |

| US8786338B2 (en) * | 2011-11-14 | 2014-07-22 | Texas Instruments Incorporated | Delay locked loop |

| CN102522994B (zh) * | 2011-12-07 | 2015-01-14 | 清华大学 | 一种用于高速和高精度模数转换器的时钟产生电路 |

| US9098072B1 (en) * | 2012-09-05 | 2015-08-04 | IQ-Analog Corporation | Traveling pulse wave quantizer |

| US8797079B2 (en) * | 2012-09-28 | 2014-08-05 | Intel Mobile Communications GmbH | Differential delay line, ring oscillator and mobile communication device |

| JP6085523B2 (ja) * | 2013-05-30 | 2017-02-22 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の動作方法 |

| KR101503732B1 (ko) * | 2013-06-14 | 2015-03-20 | 연세대학교 산학협력단 | 시간-디지털 변환기 |

| JP6071840B2 (ja) | 2013-10-25 | 2017-02-01 | 株式会社東芝 | A/dコンバータ及び半導体集積回路 |

| US9312840B2 (en) * | 2014-02-28 | 2016-04-12 | Analog Devices Global | LC lattice delay line for high-speed ADC applications |

| JP2015167278A (ja) * | 2014-03-03 | 2015-09-24 | 株式会社デンソー | A/d変換装置の出力切替方法及びa/d変換装置 |

| US9923570B2 (en) * | 2016-04-12 | 2018-03-20 | Microchip Technology Incorporated | Time-based delay line analog-to-digital converter with variable resolution |

-

2017

- 2017-04-11 US US15/485,020 patent/US9923570B2/en active Active

- 2017-04-11 US US15/484,965 patent/US10090850B2/en active Active

- 2017-04-11 US US15/484,987 patent/US9906235B2/en active Active

- 2017-04-11 US US15/484,949 patent/US9948317B2/en active Active

- 2017-04-12 TW TW106112232A patent/TW201810955A/zh unknown

- 2017-04-12 WO PCT/US2017/027250 patent/WO2017180771A1/en active Application Filing

- 2017-04-12 KR KR1020187015386A patent/KR20180127958A/ko unknown

- 2017-04-12 EP EP17718779.6A patent/EP3443670A1/en not_active Ceased

- 2017-04-12 WO PCT/US2017/027191 patent/WO2017180732A1/en active Application Filing

- 2017-04-12 JP JP2018523787A patent/JP7036717B2/ja active Active

- 2017-04-12 EP EP17732613.9A patent/EP3443672A1/en not_active Ceased

- 2017-04-12 KR KR1020187015387A patent/KR20180127959A/ko unknown

- 2017-04-12 KR KR1020187015385A patent/KR20180127957A/ko unknown

- 2017-04-12 CN CN201780005127.4A patent/CN108432143B/zh active Active

- 2017-04-12 CN CN201780005275.6A patent/CN108432144B/zh active Active

- 2017-04-12 WO PCT/US2017/027243 patent/WO2017180765A1/en active Application Filing

- 2017-04-12 WO PCT/US2017/027262 patent/WO2017180778A1/en active Application Filing

- 2017-04-12 JP JP2018523754A patent/JP2019514230A/ja active Pending

- 2017-04-12 EP EP17719135.0A patent/EP3443671A1/en not_active Ceased

- 2017-04-12 JP JP2018523815A patent/JP6934866B2/ja active Active

- 2017-04-12 TW TW106112262A patent/TW201810957A/zh unknown

- 2017-04-12 CN CN201780005126.XA patent/CN108432142B/zh active Active

- 2017-04-12 CN CN201780005061.9A patent/CN108432141B/zh active Active

- 2017-04-12 JP JP2018523813A patent/JP6929282B2/ja active Active

- 2017-04-12 EP EP17733079.2A patent/EP3443673A1/en not_active Ceased

- 2017-04-12 TW TW106112233A patent/TW201810956A/zh unknown

- 2017-04-12 TW TW106112234A patent/TW201803277A/zh unknown

- 2017-04-12 KR KR1020187015388A patent/KR20180127960A/ko unknown

-

2018

- 2018-02-21 US US15/901,294 patent/US10355707B2/en active Active

- 2018-03-08 US US15/915,796 patent/US10122375B2/en active Active

- 2018-04-10 US US15/949,479 patent/US10171099B2/en active Active

Also Published As

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6929282B2 (ja) | 時間ベースの遅延ラインアナログ・デジタルコンバータ | |

| CN108702157B (zh) | 基于时间的延迟线模拟比较器 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200318 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200318 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210315 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210614 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210713 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210810 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6929282 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |