JP6898570B2 - 半導体集積回路装置 - Google Patents

半導体集積回路装置 Download PDFInfo

- Publication number

- JP6898570B2 JP6898570B2 JP2018520810A JP2018520810A JP6898570B2 JP 6898570 B2 JP6898570 B2 JP 6898570B2 JP 2018520810 A JP2018520810 A JP 2018520810A JP 2018520810 A JP2018520810 A JP 2018520810A JP 6898570 B2 JP6898570 B2 JP 6898570B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- wiring

- strap

- switch

- supply wirings

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/10—Integrated device layouts

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/392—Floor-planning or layout, e.g. partitioning or placement

-

- G—PHYSICS

- G06—COMPUTING OR CALCULATING; COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F30/00—Computer-aided design [CAD]

- G06F30/30—Circuit design

- G06F30/39—Circuit design at the physical level

- G06F30/394—Routing

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/0008—Arrangements for reducing power consumption

- H03K19/0016—Arrangements for reducing power consumption by using a control or a clock signal, e.g. in order to apply power supply

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/90—Masterslice integrated circuits

- H10D84/903—Masterslice integrated circuits comprising field effect technology

- H10D84/907—CMOS gate arrays

-

- H10W20/427—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/90—Masterslice integrated circuits

- H10D84/903—Masterslice integrated circuits comprising field effect technology

- H10D84/907—CMOS gate arrays

- H10D84/968—Macro-architecture

- H10D84/974—Layout specifications, i.e. inner core regions

- H10D84/981—Power supply lines

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Theoretical Computer Science (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Geometry (AREA)

- Evolutionary Computation (AREA)

- Computing Systems (AREA)

- Mathematical Physics (AREA)

- Computer Networks & Wireless Communication (AREA)

- Architecture (AREA)

- Semiconductor Integrated Circuits (AREA)

- Design And Manufacture Of Integrated Circuits (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

Description

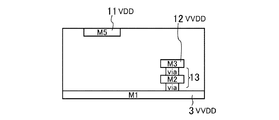

図1は第1実施形態に係る半導体集積回路装置の構成を示す平面図であり、電源遮断を行う回路ブロックにおけるレイアウトパターンを簡略化して図示している(以降の平面図も同様)。図1に示す半導体集積回路装置は、基板に、複数のスタンダードセル1が配置されている。X方向(図面横方向、第1方向に相当)に並べて配置された複数のスタンダードセル1を備えたスタンダードセル列2が、Y方向(図面縦方向、第1方向と垂直をなす方向である第2方向)に複数行配置されている。スタンダードセル1は、例えばインバータや論理回路等の機能を有する基本回路素子であり、スタンダードセル1を組み合わせて配置配線することによって、所定の機能を実現する半導体集積回路装置を設計・製造することができる。スタンダードセル1は、P型MOS(Metal Oxide Semiconductor)トランジスタ(PMOS)が形成されるN型領域とN型MOSトランジスタ(NMOS)が形成されるP型領域とをそれぞれ有している。本開示では、スタンダードセル1は、N型領域とP型領域とがY方向に並べて配置されており、かつ、スタンダードセル列2は、1行おきに、N型領域とP型領域との並びが反転しているものとする。なお、スタンダードセル1の内部構造については図示を省略している。

図1の構成では、4本のストラップ電源配線11(1)〜(4)について、スタンダードセル電源配線3(1),(3),(2),(4)の順で、その間にスイッチセル20が配置されているものとした。ただし、スイッチセル20の配置パターンは、図1に示したものに限られるものではない。

図6は本実施形態の変形例2に係る半導体集積回路装置の構成を示す平面図である。図6では、図の簡略化のために、スタンダードセル1の配置に関しては図示を省略している。また、スタンダードセル電源配線3、接地電源配線4、ストラップ電源配線11および副ストラップ電源配線12の配置に関しては、図1とほぼ同様であり、ここではその詳細な説明を省略する。

図7は本実施形態の変形例3に係る半導体集積回路装置の構成を示す平面図である。図7では、図の簡略化のために、スタンダードセル1の配置に関しては図示を省略している。また、スタンダードセル電源配線3、接地電源配線4、ストラップ電源配線11および副ストラップ電源配線12の配置に関しては、図1とほぼ同様であり、ここではその詳細な説明を省略する。

図8は第2実施形態に係る半導体集積回路装置の構成を示す平面図である。スタンダードセル1の配置や、スタンダードセル電源配線3、接地電源配線4、ストラップ電源配線11および副ストラップ電源配線12の配置に関しては、図1と同様であり、ここではその詳細な説明を省略する。

図9は第3実施形態に係る半導体集積回路装置の構成を示す平面図である。スタンダードセル1の配置や、スタンダードセル電源配線3、接地電源配線4およびストラップ電源配線11の配置に関しては、図1と同様であり、ここではその詳細な説明を省略する。

図10は第4実施形態に係る半導体集積回路装置の構成を示す平面図である。スタンダードセル1の配置や、スタンダードセル電源配線3、接地電源配線4、ストラップ電源配線11および副ストラップ電源配線12の配置に関しては、図1とほぼ同様であり、ここではその詳細な説明を省略する。

図11は図1の構成におけるスイッチセル20の配置パターンを概念的に示す図である。図11では、X軸方向に延びる各行がスタンダードセル電源配線3に対応し、Y軸方向に延びる各列がストラップ電源配線11に対応している。そして、各マスはそれぞれ、スタンダードセル電源配線3とストラップ電源配線11とが平面視で交差した箇所、言い換えると、スイッチセル20が配置される可能性がある箇所に対応している。そして、灰色のマスはスイッチセル20が配置された箇所を表しており、白いマスはスイッチセル20が配置されていない箇所を表している。なお、図6や図7の構成のように、スイッチセル20よりもセル高さが高いスイッチセル25,26が、複数のスタンダードセル電源配線3に対して配置されている場合は、図11のX軸方向に延びる各行は、複数のスタンダードセル電源配線3からなる「配線組」に対応することになる。

M=3:mx=2

M=4:mx=2,3,2の順

M=5:mx=2

M=6:mx=2,3,4,4,3,2の順

M=7:mx=3

M=8:mx=3

M=12:mx=5

M=16:mx=5

M=3:Dmax=1

M=4:Dmax=1

M=5:Dmax=1

M=6:Dmax=2

M=7:Dmax=2

M=8:Dmax=2

M=12:Dmax=3

M=16:Dmax=4

Dmax ≦ M/4

上の説明では、ストラップ電源配線11は第5配線層に設けられ、副ストラップ電源配線12,15は第3配線層および第5配線層に設けられるものとしたが、ストラップ電源配線や副ストラップ電源配線が形成される配線層はこれらに限られるものではない。ただし、副ストラップ電源配線は、スタンダードセル電源配線にできるだけ近い配線層に形成することが好ましい。これにより、副ストラップ電源配線とスタンダードセル電源配線との間の配線やビア等の経路における抵抗値が小さくなり、電源電位の低下を抑制することができる。また、上の説明では、スタンダードセル電源配線3は第1配線層に設けられるものとしたが、これに限られるものではなく、例えば複数の配線層に設けてもかまわない。

2 スタンダードセル列

3 スタンダードセル電源配線(電源配線)

11 ストラップ電源配線

12,15 副ストラップ電源配線

14 上層電源配線

20,20a,20b スイッチセル

25,26 スイッチセル

201 第1スイッチセル

202 第2スイッチセル

203 第3スイッチセル

Claims (12)

- 第1方向に並べて配置された複数のスタンダードセルをそれぞれ備え、前記第1方向と垂直をなす方向である第2方向に並べて配置された複数のスタンダードセル列と、

前記第1方向に延びるようにそれぞれ配置されており、前記複数のスタンダードセルに電源を供給する複数の電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置された、複数のストラップ電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置され、前記複数の電源配線とそれぞれ接続された、複数の副ストラップ電源配線と、

前記複数のストラップ電源配線のいずれかと、前記複数の電源配線の中のN本(Nは1以上の整数)からなる配線組との間に設けられており、制御信号に応じて、当該ストラップ電源配線と当該配線組に属する前記電源配線とを電気的に接続するか否かを切替可能に構成された、複数のスイッチセルとを備え、

前記複数のスイッチセルは、前記複数のストラップ電源配線に対してそれぞれ、M(Mは3以上の整数)個の前記配線組毎に1個ずつ、配置されており、

前記複数のスイッチセルの前記第2方向における配置位置は、隣り合う前記ストラップ電源配線において互いに異なっており、かつ、前記第1方向における前記ストラップ電源配線のM本ごとに、同一である

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記複数の副ストラップ電源配線の上層に、前記第1方向に延びるように配置されており、前記複数の副ストラップ電源配線とそれぞれ接続された、上層電源配線を備えた

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記副ストラップ電源配線は、前記ストラップ電源配線よりも下層に設けられている

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記ストラップ電源配線は、平面視において、前記スイッチセルと重なりを有している

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記副ストラップ電源配線は、平面視において、前記スイッチセルと重なりを有している

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記複数のストラップ電源配線は、間に前記副ストラップ電源配線が2本以上配置された、2本のストラップ電源配線を含む

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記複数の副ストラップ電源配線は、配置された層が互いに異なる、2本の副ストラップ電源配線を含む

ことを特徴とする半導体集積回路装置。 - 請求項1記載の半導体集積回路装置において、

前記スイッチセルは、トランジスタサイズが互いに異なる、2個のスイッチセルを含む

ことを特徴とする半導体集積回路装置。 - 第1方向に並べて配置された複数のスタンダードセルをそれぞれ備え、前記第1方向と垂直をなす方向である第2方向に並べて配置された複数のスタンダードセル列と、

前記第1方向に延びるようにそれぞれ配置されており、前記複数のスタンダードセルに電源を供給する複数の電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置された、複数のストラップ電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置され、前記複数の電源配線とそれぞれ接続された、複数の副ストラップ電源配線と、

前記複数のストラップ電源配線のいずれかと、前記複数の電源配線の中のN本(Nは1以上の整数)からなる配線組との間に設けられており、制御信号に応じて、当該ストラップ電源配線と当該配線組に属する前記電源配線とを電気的に接続するか否かを切替可能に構成された、複数のスイッチセルとを備え、

前記複数のスイッチセルは、前記複数のストラップ電源配線に対してそれぞれ、M(Mは3以上の整数)個の前記配線組毎に1個ずつ、配置されており、

前記複数のスイッチセルの前記第2方向における配置位置は、隣り合う前記ストラップ電源配線において互いに異なっており、かつ、前記第1方向における前記ストラップ電源配線のM本ごとに、同一であり、

前記複数のスイッチセルは、前記配線組の1つである第1配線組に対してそれぞれ設けられており、前記第1方向において隣り合う第1および第2スイッチセルと、前記第1配線組と前記第2方向において隣り合う前記配線組に対して設けられた第3スイッチセルとを含み、

前記第3スイッチセルは、前記第1スイッチセルが設けられた前記ストラップ電源配線と前記第2スイッチセルが設けられた前記ストラップ電源配線と間の中間位置にある、前記ストラップ電源配線に対して、設けられている

ことを特徴とする半導体集積回路装置。 - 請求項9記載の半導体集積回路装置において、

Mは4である

ことを特徴とする半導体集積回路装置。 - 第1方向に並べて配置された複数のスタンダードセルをそれぞれ備え、前記第1方向と垂直をなす方向である第2方向に並べて配置された複数のスタンダードセル列と、

前記第1方向に延びるようにそれぞれ配置されており、前記複数のスタンダードセルに電源を供給する複数の電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置された、複数のストラップ電源配線と、

前記複数の電源配線の上層において前記第2方向に延びるように配置され、前記複数の電源配線とそれぞれ接続された、複数の副ストラップ電源配線と、

前記複数のストラップ電源配線のいずれかと、前記複数の電源配線の中のN本(Nは1以上の整数)からなる配線組との間に設けられており、制御信号に応じて、当該ストラップ電源配線と当該配線組に属する前記電源配線とを電気的に接続するか否かを切替可能に構成された、複数のスイッチセルとを備え、

前記複数のスイッチセルは、前記複数のストラップ電源配線に対してそれぞれ、M(Mは3以上の整数)個の前記配線組毎に1個ずつ、配置されており、

前記複数のスイッチセルの前記第2方向における配置位置は、隣り合う前記ストラップ電源配線において互いに異なっており、かつ、前記第1方向における前記ストラップ電源配線のM本ごとに、同一であり、

前記複数のスイッチセルの配置を、X軸方向に延びる各行が前記配線組に対応し、Y軸方向に延びる各列が前記ストラップ電源配線に対応するマス目で表した場合において、

前記スイッチセルが配置されていない第1マスと、前記スイッチセルが配置されており当該第1マスから最も近い第2マスとの、X座標の差をX、Y座標の差をYとしたとき、

X+Y≦M/4

の関係を満たす

ことを特徴とする半導体集積回路装置。 - 請求項11記載の半導体集積回路装置において、

Mは4,8,12,16のうちのいずれかである

ことを特徴とする半導体集積回路装置。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016110402 | 2016-06-01 | ||

| JP2016110402 | 2016-06-01 | ||

| JP2017077462 | 2017-04-10 | ||

| JP2017077462 | 2017-04-10 | ||

| PCT/JP2017/019015 WO2017208887A1 (ja) | 2016-06-01 | 2017-05-22 | 半導体集積回路装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2017208887A1 JPWO2017208887A1 (ja) | 2019-03-28 |

| JP6898570B2 true JP6898570B2 (ja) | 2021-07-07 |

Family

ID=60477489

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018520810A Active JP6898570B2 (ja) | 2016-06-01 | 2017-05-22 | 半導体集積回路装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US10734373B2 (ja) |

| JP (1) | JP6898570B2 (ja) |

| CN (1) | CN109155284B (ja) |

| WO (1) | WO2017208887A1 (ja) |

Families Citing this family (17)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102018108836B4 (de) | 2017-11-14 | 2023-10-05 | Taiwan Semiconductor Manufacturing Co. Ltd. | Halbleitervorrichtungen mit standardzellen |

| US11011545B2 (en) * | 2017-11-14 | 2021-05-18 | Taiwan Semiconductor Manufacturing Co., Ltd. | Semiconductor device including standard cells |

| CN110531136B (zh) * | 2018-05-23 | 2021-11-12 | 中芯国际集成电路制造(上海)有限公司 | 标准单元漏电流的测试电路及测试方法 |

| US10784199B2 (en) * | 2019-02-20 | 2020-09-22 | Micron Technology, Inc. | Component inter-digitated VIAS and leads |

| JP7080845B2 (ja) * | 2019-03-20 | 2022-06-06 | 株式会社東芝 | 半導体装置 |

| JP7259944B2 (ja) | 2019-04-25 | 2023-04-18 | 株式会社ソシオネクスト | 半導体装置 |

| WO2020217396A1 (ja) | 2019-04-25 | 2020-10-29 | 株式会社ソシオネクスト | 半導体装置 |

| CN110752203B (zh) * | 2019-10-30 | 2021-03-23 | 珠海格力电器股份有限公司 | 一种低功耗芯片及其制备方法 |

| US12136595B2 (en) | 2019-12-10 | 2024-11-05 | Samsung Electronics Co., Ltd. | Semiconductor device including power gating switches |

| CN113688594B (zh) * | 2020-05-18 | 2024-06-21 | 元太科技工业股份有限公司 | 电子装置 |

| CN116472605B (zh) * | 2020-11-27 | 2025-06-24 | 株式会社索思未来 | 半导体集成电路装置的设计方法、半导体集成电路装置以及计算机可读记录介质 |

| JP7600701B2 (ja) | 2021-01-19 | 2024-12-17 | 株式会社ソシオネクスト | 半導体装置 |

| JP7635557B2 (ja) | 2021-01-19 | 2025-02-26 | 株式会社ソシオネクスト | 半導体装置 |

| CN115472195A (zh) * | 2021-07-27 | 2022-12-13 | 台湾积体电路制造股份有限公司 | 半导体器件及其操作方法 |

| DE102022100096A1 (de) * | 2021-07-27 | 2023-02-02 | Taiwan Semiconductor Manufacturing Co., Ltd. | Halbleitervorrichtung und verfahren zum betreiben davon |

| CN113935273A (zh) * | 2021-09-17 | 2022-01-14 | 东科半导体(安徽)股份有限公司 | 一种低功耗模块的控制信号连接方法 |

| CN119949047A (zh) * | 2022-09-27 | 2025-05-06 | 新唐科技日本株式会社 | 半导体集成电路装置 |

Family Cites Families (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3924471B2 (ja) * | 2002-01-30 | 2007-06-06 | 株式会社リコー | スタンダードセルまたはマクロセルを含む半導体集積回路、およびその配置配線方法 |

| JP4547939B2 (ja) * | 2004-03-02 | 2010-09-22 | ソニー株式会社 | 半導体集積回路およびそのレイアウト設計方法 |

| US7279926B2 (en) * | 2004-05-27 | 2007-10-09 | Qualcomm Incoporated | Headswitch and footswitch circuitry for power management |

| US7659746B2 (en) * | 2005-02-14 | 2010-02-09 | Qualcomm, Incorporated | Distributed supply current switch circuits for enabling individual power domains |

| JP2007095787A (ja) * | 2005-09-27 | 2007-04-12 | Nec Electronics Corp | 半導体集積回路 |

| JP5307427B2 (ja) | 2007-04-05 | 2013-10-02 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP5358913B2 (ja) * | 2007-09-07 | 2013-12-04 | 日本電気株式会社 | 半導体集積回路およびその設計方法 |

| JP5528662B2 (ja) | 2007-09-18 | 2014-06-25 | ソニー株式会社 | 半導体集積回路 |

| JP4636077B2 (ja) | 2007-11-07 | 2011-02-23 | ソニー株式会社 | 半導体集積回路 |

| JP5130904B2 (ja) * | 2007-12-21 | 2013-01-30 | 富士通セミコンダクター株式会社 | 電子回路装置及び電子回路装置の制御方法 |

| JP4535136B2 (ja) * | 2008-01-17 | 2010-09-01 | ソニー株式会社 | 半導体集積回路、および、スイッチの配置配線方法 |

| JP5398257B2 (ja) * | 2008-12-25 | 2014-01-29 | ルネサスエレクトロニクス株式会社 | 半導体装置及びそのスイッチトランジスタの制御方法 |

| US8368226B2 (en) * | 2009-12-23 | 2013-02-05 | Oracle International Corporation | Die power structure |

| JP2011159810A (ja) * | 2010-02-01 | 2011-08-18 | Renesas Electronics Corp | 半導体集積回路及びその制御方法 |

| JP5364023B2 (ja) * | 2010-03-29 | 2013-12-11 | パナソニック株式会社 | 半導体装置 |

| JP2011243794A (ja) * | 2010-05-19 | 2011-12-01 | Renesas Electronics Corp | 半導体装置、電源スイッチの制御方法及びその設計方法 |

| JP5404678B2 (ja) * | 2011-03-10 | 2014-02-05 | 株式会社東芝 | 電源制御装置 |

| JP5819218B2 (ja) * | 2012-02-23 | 2015-11-18 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP2016035995A (ja) * | 2014-08-04 | 2016-03-17 | 株式会社東芝 | 半導体集積回路装置 |

| US10394299B2 (en) * | 2016-05-23 | 2019-08-27 | Qualcomm Incorporated | Systems and methods to separate power domains in a processing device |

-

2017

- 2017-05-22 JP JP2018520810A patent/JP6898570B2/ja active Active

- 2017-05-22 WO PCT/JP2017/019015 patent/WO2017208887A1/ja not_active Ceased

- 2017-05-22 CN CN201780029899.1A patent/CN109155284B/zh active Active

-

2018

- 2018-11-13 US US16/189,900 patent/US10734373B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20190081029A1 (en) | 2019-03-14 |

| CN109155284B (zh) | 2022-09-23 |

| CN109155284A (zh) | 2019-01-04 |

| WO2017208887A1 (ja) | 2017-12-07 |

| US10734373B2 (en) | 2020-08-04 |

| JPWO2017208887A1 (ja) | 2019-03-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6898570B2 (ja) | 半導体集積回路装置 | |

| JP6826292B2 (ja) | 半導体集積回路装置 | |

| CN101471340B (zh) | 半导体集成电路 | |

| US12094882B2 (en) | Semiconductor integrated circuit device | |

| US12464819B2 (en) | Semiconductor integrated circuit device | |

| US20240072058A1 (en) | Output circuit | |

| US11824055B2 (en) | Semiconductor integrated circuit device | |

| JP5896682B2 (ja) | 半導体集積回路装置 | |

| US20080079026A1 (en) | Semiconductor integrated circuit | |

| JP2014131007A (ja) | 半導体集積回路 | |

| US10777579B2 (en) | Semiconductor integrated circuit device | |

| US20240363521A1 (en) | Semiconductor integrated circuit device | |

| US10417368B2 (en) | Semiconductor device and layout design method thereof | |

| JP7323847B2 (ja) | 半導体集積回路装置 | |

| WO2024214653A1 (ja) | 半導体集積回路装置 | |

| WO2024047820A1 (ja) | 半導体集積回路装置 | |

| JP6118923B2 (ja) | 半導体集積回路装置 | |

| WO2024241869A1 (ja) | 半導体集積回路装置 | |

| WO2022254676A1 (ja) | 半導体集積回路装置 | |

| JP2013140888A (ja) | 半導体装置及び半導体装置の製造方法 | |

| JP2011009388A (ja) | 半導体集積回路 | |

| JP2011222864A (ja) | 半導体装置 | |

| JP2015170607A (ja) | 横型mosfet |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20200409 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20210302 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210309 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210511 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210524 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6898570 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |