JP6861996B2 - 磁気抵抗効果素子及び磁気メモリ装置 - Google Patents

磁気抵抗効果素子及び磁気メモリ装置 Download PDFInfo

- Publication number

- JP6861996B2 JP6861996B2 JP2017518016A JP2017518016A JP6861996B2 JP 6861996 B2 JP6861996 B2 JP 6861996B2 JP 2017518016 A JP2017518016 A JP 2017518016A JP 2017518016 A JP2017518016 A JP 2017518016A JP 6861996 B2 JP6861996 B2 JP 6861996B2

- Authority

- JP

- Japan

- Prior art keywords

- magnetization

- region

- layer

- fixed

- recording layer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 230000005291 magnetic effect Effects 0.000 title claims description 88

- 230000005415 magnetization Effects 0.000 claims description 348

- 230000004888 barrier function Effects 0.000 claims description 39

- 230000000694 effects Effects 0.000 claims description 23

- 229910052742 iron Inorganic materials 0.000 claims description 8

- 229910052759 nickel Inorganic materials 0.000 claims description 7

- 230000002441 reversible effect Effects 0.000 claims description 5

- 230000000149 penetrating effect Effects 0.000 claims description 2

- 239000010408 film Substances 0.000 description 71

- 238000000034 method Methods 0.000 description 31

- 239000000463 material Substances 0.000 description 26

- 230000004048 modification Effects 0.000 description 24

- 238000012986 modification Methods 0.000 description 24

- 238000010586 diagram Methods 0.000 description 19

- 229910001030 Iron–nickel alloy Inorganic materials 0.000 description 13

- 238000004088 simulation Methods 0.000 description 12

- 230000005294 ferromagnetic effect Effects 0.000 description 11

- 230000005381 magnetic domain Effects 0.000 description 7

- 239000000758 substrate Substances 0.000 description 7

- 230000008878 coupling Effects 0.000 description 6

- 238000010168 coupling process Methods 0.000 description 6

- 238000005859 coupling reaction Methods 0.000 description 6

- 238000013461 design Methods 0.000 description 6

- 238000012546 transfer Methods 0.000 description 5

- 229910019236 CoFeB Inorganic materials 0.000 description 4

- 230000008569 process Effects 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 3

- 238000005516 engineering process Methods 0.000 description 3

- 230000005283 ground state Effects 0.000 description 3

- 230000020169 heat generation Effects 0.000 description 3

- 238000010438 heat treatment Methods 0.000 description 3

- 239000000696 magnetic material Substances 0.000 description 3

- 229910052748 manganese Inorganic materials 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 229910020630 Co Ni Inorganic materials 0.000 description 2

- 229910002440 Co–Ni Inorganic materials 0.000 description 2

- 229910045601 alloy Inorganic materials 0.000 description 2

- 239000000956 alloy Substances 0.000 description 2

- 229910052804 chromium Inorganic materials 0.000 description 2

- 229910052802 copper Inorganic materials 0.000 description 2

- 239000013078 crystal Substances 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000011156 evaluation Methods 0.000 description 2

- 239000003302 ferromagnetic material Substances 0.000 description 2

- 230000005307 ferromagnetism Effects 0.000 description 2

- 230000006870 function Effects 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000007246 mechanism Effects 0.000 description 2

- 229910052751 metal Inorganic materials 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 230000035699 permeability Effects 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 230000007704 transition Effects 0.000 description 2

- 229910052723 transition metal Inorganic materials 0.000 description 2

- 150000003624 transition metals Chemical class 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910003321 CoFe Inorganic materials 0.000 description 1

- 229910017061 Fe Co Inorganic materials 0.000 description 1

- 229910002551 Fe-Mn Inorganic materials 0.000 description 1

- 229910019041 PtMn Inorganic materials 0.000 description 1

- 229910052782 aluminium Inorganic materials 0.000 description 1

- 230000005290 antiferromagnetic effect Effects 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 238000004364 calculation method Methods 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000005260 corrosion Methods 0.000 description 1

- 230000007797 corrosion Effects 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 229910052732 germanium Inorganic materials 0.000 description 1

- 229910052737 gold Inorganic materials 0.000 description 1

- 230000005484 gravity Effects 0.000 description 1

- 229910052735 hafnium Inorganic materials 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000003993 interaction Effects 0.000 description 1

- 238000010884 ion-beam technique Methods 0.000 description 1

- 229910052741 iridium Inorganic materials 0.000 description 1

- 229910052750 molybdenum Inorganic materials 0.000 description 1

- 229910052758 niobium Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 229910052760 oxygen Inorganic materials 0.000 description 1

- 229910052763 palladium Inorganic materials 0.000 description 1

- 238000000059 patterning Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 238000005240 physical vapour deposition Methods 0.000 description 1

- 238000007747 plating Methods 0.000 description 1

- 229910052697 platinum Inorganic materials 0.000 description 1

- 230000010287 polarization Effects 0.000 description 1

- 238000011160 research Methods 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 238000012552 review Methods 0.000 description 1

- 229910052703 rhodium Inorganic materials 0.000 description 1

- 229910052707 ruthenium Inorganic materials 0.000 description 1

- 239000004065 semiconductor Substances 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 229910052709 silver Inorganic materials 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- -1 thickness 9 nm Inorganic materials 0.000 description 1

- 239000010409 thin film Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 229910052720 vanadium Inorganic materials 0.000 description 1

- 229910052726 zirconium Inorganic materials 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R33/00—Arrangements or instruments for measuring magnetic variables

- G01R33/02—Measuring direction or magnitude of magnetic fields or magnetic flux

- G01R33/06—Measuring direction or magnitude of magnetic fields or magnetic flux using galvano-magnetic devices

- G01R33/09—Magnetoresistive devices

- G01R33/093—Magnetoresistive devices using multilayer structures, e.g. giant magnetoresistance sensors

-

- G—PHYSICS

- G01—MEASURING; TESTING

- G01R—MEASURING ELECTRIC VARIABLES; MEASURING MAGNETIC VARIABLES

- G01R33/00—Arrangements or instruments for measuring magnetic variables

- G01R33/02—Measuring direction or magnitude of magnetic fields or magnetic flux

- G01R33/06—Measuring direction or magnitude of magnetic fields or magnetic flux using galvano-magnetic devices

- G01R33/09—Magnetoresistive devices

- G01R33/098—Magnetoresistive devices comprising tunnel junctions, e.g. tunnel magnetoresistance sensors

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/161—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect details concerning the memory cell structure, e.g. the layers of the ferromagnetic memory cell

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1673—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F1/00—Magnets or magnetic bodies characterised by the magnetic materials therefor; Selection of materials for their magnetic properties

- H01F1/0036—Magnets or magnetic bodies characterised by the magnetic materials therefor; Selection of materials for their magnetic properties showing low dimensional magnetism, i.e. spin rearrangements due to a restriction of dimensions, e.g. showing giant magnetoresistivity

- H01F1/0072—Magnets or magnetic bodies characterised by the magnetic materials therefor; Selection of materials for their magnetic properties showing low dimensional magnetism, i.e. spin rearrangements due to a restriction of dimensions, e.g. showing giant magnetoresistivity one dimensional, i.e. linear or dendritic nanostructures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01F—MAGNETS; INDUCTANCES; TRANSFORMERS; SELECTION OF MATERIALS FOR THEIR MAGNETIC PROPERTIES

- H01F10/00—Thin magnetic films, e.g. of one-domain structure

- H01F10/32—Spin-exchange-coupled multilayers, e.g. nanostructured superlattices

- H01F10/324—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer

- H01F10/3254—Exchange coupling of magnetic film pairs via a very thin non-magnetic spacer, e.g. by exchange with conduction electrons of the spacer the spacer being semiconducting or insulating, e.g. for spin tunnel junction [STJ]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y10/00—Nanotechnology for information processing, storage or transmission, e.g. quantum computing or single electron logic

-

- B—PERFORMING OPERATIONS; TRANSPORTING

- B82—NANOTECHNOLOGY

- B82Y—SPECIFIC USES OR APPLICATIONS OF NANOSTRUCTURES; MEASUREMENT OR ANALYSIS OF NANOSTRUCTURES; MANUFACTURE OR TREATMENT OF NANOSTRUCTURES

- B82Y25/00—Nanomagnetism, e.g. magnetoimpedance, anisotropic magnetoresistance, giant magnetoresistance or tunneling magnetoresistance

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Power Engineering (AREA)

- Inorganic Chemistry (AREA)

- Hall/Mr Elements (AREA)

- Mram Or Spin Memory Techniques (AREA)

Description

強磁性体を含む記録層と、

前記記録層の上に積層された絶縁層からなる障壁層と、

前記障壁層の上に積層され、強磁性体を含む参照層と、

を有し、

前記参照層は、略面内方向に実質固定された磁化成分を有し、

前記記録層は、略面内方向に実質固定された磁化成分を有する第1磁化固定領域と、前記第1磁化固定領域が有する磁化成分と反対の向きに実質固定された磁化成分を有する第2磁化固定領域と、前記第1磁化固定領域と前記第2磁化固定領域との間に位置し、略面内方向において反転可能な磁化成分を有する磁化自由領域とを含み、

前記第1磁化固定領域と前記第2磁化固定領域との間に磁壁が形成され、

前記磁壁は、前記磁化自由領域内において、前記第1磁化固定領域と前記第2磁化固定領域との間で行き来するように移動可能であり、

前記磁壁が前記第1磁化固定領域と前記磁化自由領域との間の第1の位置にあるときには、前記磁化自由領域の磁化は、前記第2磁化固定領域の磁化と同一方向の成分を有し、前記磁壁が前記第2磁化固定領域と前記磁化自由領域との間の第2の位置にあるときには、前記磁化自由領域の磁化は、前記第1磁化固定領域の磁化と同一方向の成分を有し、

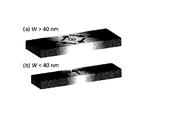

前記記録層を構成し、前記第1磁化固定領域と前記第2磁化固定領域とを結ぶ方向に延在する細線の線幅は40nm以下であり、

前記記録層の膜厚は、40nm以下であり、前記線幅の1/2以上、かつ、2倍以下である。

前記線幅は30nm以下であり、

前記膜厚は30nm以下であり、前記線幅の2/3以上、かつ、1.5倍以下であってもよい。

強磁性体を含む記録層と、

前記記録層の上に積層された障壁層と、

前記障壁層の上に積層され、強磁性体を含む参照層と、

を有し、

前記参照層は、略面内方向に実質固定された磁化成分を有し、

前記記録層は、略面内方向に実質固定された磁化成分を有する第1磁化固定領域と、前記第1磁化固定領域が有する磁化成分と反対の向きに実質固定された磁化成分を有する第2磁化固定領域と、前記第1磁化固定領域と前記第2磁化固定領域との間に位置し、略面内方向において反転可能な磁化成分を有する磁化自由領域とを含み、

前記第1磁化固定領域と前記第2磁化固定領域との間に磁壁が形成され、

前記磁壁は、前記磁化自由領域内において、前記第1磁化固定領域と前記第2磁化固定領域との間で行き来するように移動可能であり、

前記磁壁が前記第1磁化固定領域と前記磁化自由領域との間の第1の位置にあるときには、前記磁化自由領域の磁化は、前記第2磁化固定領域の磁化と同一方向の成分を有し、前記磁壁が前記第2磁化固定領域と前記磁化自由領域との間の第2の位置にあるときには、前記磁化自由領域の磁化は、前記第1磁化固定領域の磁化と同一方向の成分を有し、

前記磁壁はTransverse構造をとることができる。

上記のトンネル磁気抵抗効果素子と、

前記トンネル磁気抵抗効果素子の前記第1磁化固定領域と前記第2磁化固定領域との間に前記磁化自由領域を介して、書き込み対象のデータに応じた向きの書き込み電流を流すことにより、前記磁化自由領域内において、前記磁壁を移動させることにより、前記トンネル磁気抵抗効果素子にデータを書き込む書き込み手段と、

前記障壁層を貫通する方向に電流を流してトンネル抵抗を求めることにより、前記トンネル磁気抵抗効果素子に書き込まれているデータを読み出す読み出し手段と、

を備える。

以下、図1〜図4を参照して、実施の形態1に係る磁気抵抗効果素子を説明する。

また、垂直磁化を有する材料は少ないため、垂直磁化方式においては材料選択の幅が限定されるが、面内磁化方式を採用した場合、選択可能な材料が多岐にわたるという利点もある。

実施の形態1に係る磁気抵抗効果素子100において、記憶データを安定して書き込み且つ読み出すためには、参照層30の磁化M30の方向を安定的に固定する必要がある。参照層30の磁化M30を安定させるため、参照層30を積層フェリ結合層から構成することが有効である。

実施の形態2において、参照層30は、強磁性層31と結合層32と強磁性層33とが積層され、積層フェリ結合した積層構造を有する。強磁性層31と強磁性層33とは、結合層32により反強磁的に結合している。強磁性層31と強磁性層33は、Fe、Co、Niを含む強磁性材料を使用することが望ましい。また、結合層32は、Ru等を使用することが望ましい。その他の構成については、実施の形態1と同様である。

磁気抵抗効果素子の抵抗とデータの割り当ては任意であり、低抵抗状態にデータ“1”、高抵抗状態にデータ“0”を割り当てても良い。

磁気抵抗効果素子100は、記録層10の第1磁化固定領域11、第2磁化固定領域12の磁化をより強固に固定するための層をさらに有してもよい。図12(a)に示すように、変形例2では、第1磁化固定領域11の下に第1磁化固定層41が設けられており、その磁化M41は、第1磁化固定領域11の磁化M11と向きが揃っている。第2磁化固定領域12の下に第2磁化固定層42が設けられており、その磁化M42は、第2磁化固定領域12の磁化M12と向きが揃っている。

あるいは、図12(b)に示すように、第1磁化固定層41、第2磁化固定層42は、記録層10の上に設けられてもよい。ここでは、第1磁化固定層41は第1磁化固定領域11の上に、第2磁化固定層42は第2磁化固定領域12の上に設けられている。変形例2と同様に、第1磁化固定層41により、第1磁化固定領域11の磁化M11が、第2磁化固定層42により、第2磁化固定領域12の磁化M12が、それぞれより強固に固定される。

また、あるいは、第1磁化固定層41、第2磁化固定層42の一方のみを設けてもよい。図12(c)に示す例では、第1磁化固定領域11の上にだけ、第1磁化固定層41が設けられている。磁気抵抗効果素子100は、第2磁化固定領域12の磁化M12の固定のための第2磁化固定層42を有しない。第1磁化固定層41の配置位置は、第1磁化固定領域11の下であってもよい。あるいは、第2磁化固定領域12の上又は下に、第2磁化固定層42を設けて、第1磁化固定領域11の磁化M11の固定のための第1磁化固定層41を設けないようにしてもよい。

上記の実施の形態1では、図1(c)に示すように、記録層10は、上から見た場合の形状(X−Y平面における形状)が四角形であったが、記録層10の形状はこれに限られない。図12(d)に示す例では、記録層10は、X−Y平面における形状が凹型となるようパターニングされている。このように構成することにより、面内方向の外部磁場を用いて記録層10に単一の磁壁を導入することが可能である。

また、実施の形態1では、障壁層20、参照層30は、記録層10の磁化自由領域13の上面の領域に積層されていた。これは、参照層30は、少なくとも記録層10の磁化自由領域13をオーバーラップする必要があるからである。しかしながら、積層構造はこれに限られず、図13(a)に示すように、記録層10の上面全体に、障壁層20、参照層30を積層してもよい。この場合、積層体の製造が容易である。

また、必ずしも、記録層10を一番下に積層する必要はなく、図13(b)に示すように、下から、つまり、基板側から、参照層30、障壁層20、記録層10の順に積層してもよい。この場合には参照層30は記録層と同等か、それ以上の面積を有する形状にパターニングされる。

上述した例では、1つの磁気抵抗効果素子100は、1つの参照層30のみを有していたが、図14(a)に示すように、参照層を複数設けてもよい。この場合、各参照層30に隣接する記録層10の領域がそれぞれ磁化自由領域となる。このような構成により、磁気抵抗効果素子100を多値メモリとすることができる。あるいは、磁気抵抗効果素子をアナログメモリとすることができる。

図14(b)に示すように、記録層10が複数の磁化自由領域を含み、これら複数の磁化自由領域を覆うように、参照層30を長手方向に長く形成してもよい。この場合も、変形例8と同様に、磁気抵抗効果素子100を多値メモリ、あるいは、アナログメモリとすることができる。

図15(a)に、記録層10に磁壁のピンサイトを形成する例を示す。ここでは、記録層10の上面(XY面内)であって、第1磁化固定領域11と磁化自由領域13との間(14)、第2磁化固定領域12と磁化自由領域13との間(15)、それぞれに凹型の切り欠き(ピンサイト)を形成している。ピンサイトにより、磁壁DWの移動を止めることができる。なお、ピンサイトは、何れか一カ所のみに設けられてもよい。

ピンサイトの形成位置は,上述の例に限られない。図15(b)に示す例では、記録層10の前面(XZ面内)であって、第1磁化固定領域11と磁化自由領域13との間(14)、第2磁化固定領域12と磁化自由領域13との間(15)、それぞれに凹型の切り欠き(ピンサイト)を形成している。この場合も、ピンサイトの位置で磁壁DWの移動を止めることができる。なお、ピンサイトは、何れか一カ所のみに設けられてもよい。

あるいは、記録層10に切り欠きの形成することなく、第1磁化固定領域11と磁化自由領域13との間(14)、第2磁化固定領域12と磁化自由領域13との間(15)、それぞれに材料特性の異なる領域を設けることによっても、ピンサイトを形成することができる。図15(c)に変形例12に係る磁気抵抗記録素子100の形状の例を示す。ここでは、着色部が材料特性の異なる領域である。なお、ピンサイトは、何れか一カ所のみに設けられてもよい。

上述の実施の形態、変形例では、記録層10は長手方向に延伸した形状を有していたが、記録層10の形状はこれに限られない。図15(d)に示す例では、記録層10はアーチ状の形状を有する。記録層10の成膜前に、成膜面をアーチ状に形成することにより、記録層10をこのように形成することができる。あるいは、記録層10の形成工程の前に実施されるVia作製工程において、CMPプロセス等を調整して、磁性膜成膜面に凹凸が残るようすることで、記録層10をアーチ状に形成することができる。記録層10をアーチ状に形成することにより、基板垂直成分を有する外部磁場によって記録層10へ容易に磁壁を導入することができる。

上述の実施の形態、変形例においては、記録層10のY−Z断面は正方形あるいは長方形である例を説明したが、記録層10にテーパーを設けてもよい。変形例14に係る磁気抵抗効果素子100の形状の例を図16(a)に示す。記録層10をテーパー状に形成することで、磁壁の移動をスムーズにし、しきい電流密度をより低減することができる。このような形状は、記録層10のパターニングプロセスの調整(入射イオンビームの角度、ハードマスクの形状の調整等)により実現できる。

また、変形例2〜14のいずれにおいても、実施の形態2で説明した積層フェリ構造を参照層30に採用することができる。

101 磁気抵抗効果素子

10 記録層

11 第1磁化固定領域

12 第2磁化固定領域

13 磁化自由領域

14 第1磁化固定領域11と磁化自由領域13との間

15 第2磁化固定領域12と磁化自由領域13との間

20 障壁層

30 参照層

31 強磁性層

32 結合層

33 強磁性層

41 第1磁化固定層

42 第2磁化固定層

50 センサー層

60 絶縁層

200 磁気メモリセル回路

300 磁気メモリ装置

311 メモリセルアレイ

312 Xドライバ

313 Yドライバ

314 コントローラ

Claims (7)

- 強磁性体を含む記録層と、

前記記録層の上に積層された絶縁層からなる障壁層と、

前記障壁層の上に積層され、強磁性体を含む参照層と、

を有し、

前記参照層は、略面内方向に実質固定された磁化成分を有し、

前記記録層は、略面内方向に実質固定された磁化成分を有する第1磁化固定領域と、前記第1磁化固定領域が有する磁化成分と反対の向きに実質固定された磁化成分を有する第2磁化固定領域と、前記第1磁化固定領域と前記第2磁化固定領域との間に位置し、略面内方向において反転可能な磁化成分を有する磁化自由領域とを含み、

前記第1磁化固定領域と前記第2磁化固定領域との間に磁壁が形成され、

前記磁壁は、前記磁化自由領域内において、前記第1磁化固定領域と前記第2磁化固定領域との間で行き来するように移動可能であり、

前記磁壁が前記第1磁化固定領域と前記磁化自由領域との間の第1の位置にあるときには、前記磁化自由領域の磁化は、前記第2磁化固定領域の磁化と同一方向の成分を有し、前記磁壁が前記第2磁化固定領域と前記磁化自由領域との間の第2の位置にあるときには、前記磁化自由領域の磁化は、前記第1磁化固定領域の磁化と同一方向の成分を有し、

前記記録層を構成し、前記第1磁化固定領域と前記第2磁化固定領域とを結ぶ方向に延在する細線の線幅は40nm以下であり、

前記記録層の膜厚は、40nm以下であり、前記線幅の1/2以上、かつ、2倍以下である、

トンネル磁気抵抗効果素子。 - 前記記録層は、NiとFeとを含み、

前記線幅は30nm以下であり、

前記膜厚は30nm以下であり、前記線幅の2/3以上、かつ、1.5倍以下である、

請求項1に記載のトンネル磁気抵抗効果素子。 - 強磁性体を含む記録層と、

前記記録層の上に積層された障壁層と、

前記障壁層の上に積層され、強磁性体を含む参照層と、

を有し、

前記参照層は、略面内方向に実質固定された磁化成分を有し、

前記記録層は、略面内方向に実質固定された磁化成分を有する第1磁化固定領域と、前記第1磁化固定領域が有する磁化成分と反対の向きに実質固定された磁化成分を有する第2磁化固定領域と、前記第1磁化固定領域と前記第2磁化固定領域との間に位置し、略面内方向において反転可能な磁化成分を有する磁化自由領域とを含み、

前記第1磁化固定領域と前記第2磁化固定領域との間に磁壁が形成され、

前記磁壁は、前記磁化自由領域内において、前記第1磁化固定領域と前記第2磁化固定領域との間で行き来するように移動可能であり、

前記磁壁が前記第1磁化固定領域と前記磁化自由領域との間の第1の位置にあるときには、前記磁化自由領域の磁化は、前記第2磁化固定領域の磁化と同一方向の成分を有し、前記磁壁が前記第2磁化固定領域と前記磁化自由領域との間の第2の位置にあるときには、前記磁化自由領域の磁化は、前記第1磁化固定領域の磁化と同一方向の成分を有し、

前記磁壁はTransverse構造をとることができる、

トンネル磁気抵抗効果素子。 - 前記記録層の長手方向且つ前記磁化自由領域の長手方向に沿って電流を導入することで、前記磁化自由領域が有する磁化成分の向きが反転する、

請求項1から3の何れか1項に記載のトンネル磁気抵抗効果素子。 - 前記第1磁化固定領域の磁化成分、前記第2磁化固定領域の磁化成分のうち少なくともいずれかを固定するための磁化固定層を、さらに有する、

請求項1から4のいずれか1項に記載のトンネル磁気抵抗効果素子。 - 前記記録層の、前記第1磁化固定領域と前記磁化自由領域との間、前記第2磁化固定領域と前記磁化自由領域との間、のうち少なくともいずれかにピンサイトが設けられている、

請求項1から5のいずれか1項に記載のトンネル磁気抵抗効果素子。 - 請求項1から6のいずれか1項に記載のトンネル磁気抵抗効果素子と、

前記トンネル磁気抵抗効果素子の前記第1磁化固定領域と前記第2磁化固定領域との間に前記磁化自由領域を介して、書き込み対象のデータに応じた向きの書き込み電流を流すことにより、前記磁化自由領域内において、前記磁壁を移動させることにより、前記トンネル磁気抵抗効果素子にデータを書き込む書き込み手段と、

前記障壁層を貫通する方向に電流を流してトンネル抵抗を求めることにより、前記トンネル磁気抵抗効果素子に書き込まれているデータを読み出す読み出し手段と、

を備える、

磁気メモリ装置。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015098976 | 2015-05-14 | ||

| JP2015098976 | 2015-05-14 | ||

| PCT/JP2016/064530 WO2016182085A1 (ja) | 2015-05-14 | 2016-05-16 | 磁気抵抗効果素子及び磁気メモリ装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2016182085A1 JPWO2016182085A1 (ja) | 2018-04-12 |

| JP6861996B2 true JP6861996B2 (ja) | 2021-04-21 |

Family

ID=57249035

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017518016A Active JP6861996B2 (ja) | 2015-05-14 | 2016-05-16 | 磁気抵抗効果素子及び磁気メモリ装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US10410703B2 (ja) |

| JP (1) | JP6861996B2 (ja) |

| WO (1) | WO2016182085A1 (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN108666339B (zh) * | 2017-03-28 | 2020-11-13 | 中芯国际集成电路制造(上海)有限公司 | 磁性随机存储器及其存储单元的制造方法 |

| JP7013839B2 (ja) * | 2017-04-14 | 2022-02-01 | Tdk株式会社 | 磁壁利用型アナログメモリ、不揮発性ロジック回路及び磁気ニューロ素子 |

| CN111052349B (zh) * | 2017-10-26 | 2023-06-20 | Tdk株式会社 | 磁畴壁移动型磁记录元件和磁记录阵列 |

| JP7098914B2 (ja) * | 2017-11-14 | 2022-07-12 | Tdk株式会社 | スピン軌道トルク型磁化回転素子、スピン軌道トルク型磁気抵抗効果素子及び磁気メモリ |

| US11469370B2 (en) * | 2018-01-11 | 2022-10-11 | Tdk Corporation | Domain wall motion type magnetic recording element |

| US10490249B2 (en) * | 2018-02-01 | 2019-11-26 | Tdk Corporation | Data writing method, inspection method, spin device manufacturing method, and magnetoresistance effect element |

| US10468432B1 (en) * | 2018-05-30 | 2019-11-05 | International Business Machines Corporation | BEOL cross-bar array ferroelectric synapse units for domain wall movement |

| US10614902B1 (en) * | 2018-10-04 | 2020-04-07 | Universität Duisburg-Essen | Tubular nanosized magnetic wires with 360° magnetic domain walls |

| US10692927B1 (en) | 2019-02-15 | 2020-06-23 | International Business Machines Corporation | Double MTJ stack with synthetic anti-ferromagnetic free layer and AlN bottom barrier layer |

| JP7470599B2 (ja) | 2020-08-19 | 2024-04-18 | Tdk株式会社 | 配線層、磁壁移動素子および磁気アレイ |

| KR20220052392A (ko) * | 2020-10-20 | 2022-04-28 | 삼성전자주식회사 | 자기 메모리 장치 |

| US20240237547A9 (en) * | 2021-03-02 | 2024-07-11 | Tdk Corporation | Domain wall displacement element, magnetic array, and method of manufacturing domain wall displacement element |

Family Cites Families (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4413603B2 (ja) * | 2003-12-24 | 2010-02-10 | 株式会社東芝 | 磁気記憶装置及び磁気情報の書込み方法 |

| JP2006303159A (ja) * | 2005-04-20 | 2006-11-02 | Fuji Electric Holdings Co Ltd | スピン注入磁区移動素子およびこれを用いた装置 |

| JP2007273495A (ja) | 2006-03-30 | 2007-10-18 | Fujitsu Ltd | 磁気メモリ装置及びその駆動方法 |

| JP2008147488A (ja) * | 2006-12-12 | 2008-06-26 | Nec Corp | 磁気抵抗効果素子及びmram |

| WO2009001706A1 (ja) | 2007-06-25 | 2008-12-31 | Nec Corporation | 磁気抵抗効果素子、および磁気ランダムアクセスメモリ |

| US8120127B2 (en) * | 2007-08-03 | 2012-02-21 | Nec Corporation | Magnetic random access memory and method of manufacturing the same |

| JP5441005B2 (ja) * | 2008-02-13 | 2014-03-12 | 日本電気株式会社 | 磁壁移動素子及び磁気ランダムアクセスメモリ |

| JP5435412B2 (ja) * | 2008-04-28 | 2014-03-05 | 日本電気株式会社 | 磁気記憶素子、及び磁気メモリ |

| JP2010080496A (ja) * | 2008-09-24 | 2010-04-08 | Fujitsu Ltd | トンネル磁気抵抗素子、磁気メモリ装置及びその製造方法 |

| KR20100068791A (ko) * | 2008-12-15 | 2010-06-24 | 삼성전자주식회사 | 자성트랙, 자성트랙을 포함하는 정보저장장치 및 상기 정보저장장치의 동작방법 |

| JPWO2010095589A1 (ja) | 2009-02-17 | 2012-08-23 | 日本電気株式会社 | 磁気抵抗効果素子、及び磁気ランダムアクセスメモリ |

| JP5618103B2 (ja) * | 2010-06-03 | 2014-11-05 | 株式会社日立製作所 | 磁気抵抗効果素子及び磁気メモリ |

| JP2012028489A (ja) * | 2010-07-22 | 2012-02-09 | Nec Corp | 磁気記憶装置 |

| SG11201503626VA (en) * | 2013-01-02 | 2015-06-29 | Univ Nanyang Tech | A memory device |

-

2016

- 2016-05-16 WO PCT/JP2016/064530 patent/WO2016182085A1/ja active Application Filing

- 2016-05-16 JP JP2017518016A patent/JP6861996B2/ja active Active

-

2017

- 2017-11-13 US US15/810,896 patent/US10410703B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| WO2016182085A1 (ja) | 2016-11-17 |

| US10410703B2 (en) | 2019-09-10 |

| US20180108390A1 (en) | 2018-04-19 |

| JPWO2016182085A1 (ja) | 2018-04-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6861996B2 (ja) | 磁気抵抗効果素子及び磁気メモリ装置 | |

| CN106875969B (zh) | 磁存储器 | |

| US10622550B2 (en) | Magnetoresistance effect element including a recording layer with perpendicular anisotropy and a bias layer comprised of an antiferromagnetic material, magnetic memory device, manufacturing method, operation method, and integrated circuit | |

| KR102271208B1 (ko) | 개선된 스위칭 효율을 위한 스핀-궤도 토크 비트 설계 | |

| JP6304697B2 (ja) | 磁気メモリ素子および磁気メモリ | |

| US8711608B2 (en) | Memory with separate read and write paths | |

| US8514615B2 (en) | Structures and methods for a field-reset spin-torque MRAM | |

| JP5505312B2 (ja) | 磁気メモリ素子及び磁気ランダムアクセスメモリ | |

| US7613036B2 (en) | Memory element utilizing magnetization switching caused by spin accumulation and spin RAM device using the memory element | |

| JP5201539B2 (ja) | 磁気ランダムアクセスメモリ | |

| JP2007273495A (ja) | 磁気メモリ装置及びその駆動方法 | |

| JP5461683B2 (ja) | 磁気メモリセル及び磁気ランダムアクセスメモリ | |

| US20140301135A1 (en) | Mram having novelself-referenced read method | |

| JPWO2011078018A1 (ja) | 磁気抵抗効果素子及びそれを用いた磁気ランダムアクセスメモリ | |

| US20100091564A1 (en) | Magnetic stack having reduced switching current | |

| JP2007324172A (ja) | 磁気メモリ装置及びその製造方法 | |

| US8565011B2 (en) | Method of initializing magnetic memory element | |

| JP5754531B2 (ja) | 磁気抵抗効果素子及び磁気ランダムアクセスメモリの製造方法 | |

| US8519495B2 (en) | Single line MRAM |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171109 |

|

| A529 | Written submission of copy of amendment under article 34 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A5211 Effective date: 20171109 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20171129 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20190411 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20200602 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20200728 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201001 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20210323 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20210324 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6861996 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |