JP6726180B2 - 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 - Google Patents

高抵抗率半導体・オン・インシュレータウエハおよび製造方法 Download PDFInfo

- Publication number

- JP6726180B2 JP6726180B2 JP2017526096A JP2017526096A JP6726180B2 JP 6726180 B2 JP6726180 B2 JP 6726180B2 JP 2017526096 A JP2017526096 A JP 2017526096A JP 2017526096 A JP2017526096 A JP 2017526096A JP 6726180 B2 JP6726180 B2 JP 6726180B2

- Authority

- JP

- Japan

- Prior art keywords

- single crystal

- layer

- crystal semiconductor

- handle substrate

- silicon

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000004519 manufacturing process Methods 0.000 title claims description 15

- 239000012212 insulator Substances 0.000 title description 35

- 239000004065 semiconductor Substances 0.000 claims description 273

- 239000000758 substrate Substances 0.000 claims description 182

- 239000013078 crystal Substances 0.000 claims description 159

- 238000000034 method Methods 0.000 claims description 70

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 58

- 229910052732 germanium Inorganic materials 0.000 claims description 58

- 239000010703 silicon Substances 0.000 claims description 58

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 claims description 56

- 229910052710 silicon Inorganic materials 0.000 claims description 56

- 229910021420 polycrystalline silicon Inorganic materials 0.000 claims description 28

- 229910021421 monocrystalline silicon Inorganic materials 0.000 claims description 24

- 229910000577 Silicon-germanium Inorganic materials 0.000 claims description 22

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical group O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 18

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 claims description 17

- 238000005229 chemical vapour deposition Methods 0.000 claims description 16

- 238000000137 annealing Methods 0.000 claims description 14

- 238000005304 joining Methods 0.000 claims description 8

- 235000012239 silicon dioxide Nutrition 0.000 claims description 8

- 239000000377 silicon dioxide Substances 0.000 claims description 8

- 238000010438 heat treatment Methods 0.000 claims description 7

- 230000001590 oxidative effect Effects 0.000 claims description 7

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 claims description 6

- 229910052799 carbon Inorganic materials 0.000 claims description 6

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 2

- QVQLCTNNEUAWMS-UHFFFAOYSA-N barium oxide Chemical compound [Ba]=O QVQLCTNNEUAWMS-UHFFFAOYSA-N 0.000 claims 2

- MRELNEQAGSRDBK-UHFFFAOYSA-N lanthanum(3+);oxygen(2-) Chemical compound [O-2].[O-2].[O-2].[La+3].[La+3] MRELNEQAGSRDBK-UHFFFAOYSA-N 0.000 claims 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 claims 1

- 229910000449 hafnium oxide Inorganic materials 0.000 claims 1

- WIHZLLGSGQNAGK-UHFFFAOYSA-N hafnium(4+);oxygen(2-) Chemical compound [O-2].[O-2].[Hf+4] WIHZLLGSGQNAGK-UHFFFAOYSA-N 0.000 claims 1

- RVTZCBVAJQQJTK-UHFFFAOYSA-N oxygen(2-);zirconium(4+) Chemical compound [O-2].[O-2].[Zr+4] RVTZCBVAJQQJTK-UHFFFAOYSA-N 0.000 claims 1

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 claims 1

- 229910001928 zirconium oxide Inorganic materials 0.000 claims 1

- 239000010410 layer Substances 0.000 description 173

- 235000012431 wafers Nutrition 0.000 description 151

- 239000000463 material Substances 0.000 description 37

- 238000000151 deposition Methods 0.000 description 17

- 230000008021 deposition Effects 0.000 description 15

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 14

- 230000003647 oxidation Effects 0.000 description 14

- 238000007254 oxidation reaction Methods 0.000 description 14

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 13

- 229910052760 oxygen Inorganic materials 0.000 description 13

- 239000001301 oxygen Substances 0.000 description 13

- 230000008569 process Effects 0.000 description 13

- 229910052757 nitrogen Inorganic materials 0.000 description 9

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 9

- 238000003776 cleavage reaction Methods 0.000 description 7

- 230000007017 scission Effects 0.000 description 7

- 238000012546 transfer Methods 0.000 description 7

- 239000002131 composite material Substances 0.000 description 6

- 238000005530 etching Methods 0.000 description 6

- 150000002500 ions Chemical class 0.000 description 6

- VNWKTOKETHGBQD-UHFFFAOYSA-N methane Chemical compound C VNWKTOKETHGBQD-UHFFFAOYSA-N 0.000 description 6

- 239000002019 doping agent Substances 0.000 description 5

- 229910052739 hydrogen Inorganic materials 0.000 description 5

- 239000007943 implant Substances 0.000 description 5

- 239000000203 mixture Substances 0.000 description 5

- 239000002245 particle Substances 0.000 description 5

- 238000001994 activation Methods 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 238000004518 low pressure chemical vapour deposition Methods 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 239000002243 precursor Substances 0.000 description 4

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 3

- BLRPTPMANUNPDV-UHFFFAOYSA-N Silane Chemical compound [SiH4] BLRPTPMANUNPDV-UHFFFAOYSA-N 0.000 description 3

- 230000004913 activation Effects 0.000 description 3

- 230000015572 biosynthetic process Effects 0.000 description 3

- 229910052796 boron Inorganic materials 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 229910052734 helium Chemical group 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 238000002513 implantation Methods 0.000 description 3

- UIUXUFNYAYAMOE-UHFFFAOYSA-N methylsilane Chemical compound [SiH3]C UIUXUFNYAYAMOE-UHFFFAOYSA-N 0.000 description 3

- 229910000077 silane Inorganic materials 0.000 description 3

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 3

- 229910010271 silicon carbide Inorganic materials 0.000 description 3

- 229910052814 silicon oxide Inorganic materials 0.000 description 3

- VXEGSRKPIUDPQT-UHFFFAOYSA-N 4-[4-(4-methoxyphenyl)piperazin-1-yl]aniline Chemical compound C1=CC(OC)=CC=C1N1CCN(C=2C=CC(N)=CC=2)CC1 VXEGSRKPIUDPQT-UHFFFAOYSA-N 0.000 description 2

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical group N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 2

- JBRZTFJDHDCESZ-UHFFFAOYSA-N AsGa Chemical compound [As]#[Ga] JBRZTFJDHDCESZ-UHFFFAOYSA-N 0.000 description 2

- 229910001218 Gallium arsenide Inorganic materials 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 229910021417 amorphous silicon Inorganic materials 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 238000004140 cleaning Methods 0.000 description 2

- 230000002950 deficient Effects 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000001307 helium Chemical group 0.000 description 2

- -1 helium ions Chemical class 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 230000005527 interface trap Effects 0.000 description 2

- 238000005468 ion implantation Methods 0.000 description 2

- 238000001451 molecular beam epitaxy Methods 0.000 description 2

- 230000003071 parasitic effect Effects 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 238000001953 recrystallisation Methods 0.000 description 2

- 238000000926 separation method Methods 0.000 description 2

- 239000012686 silicon precursor Substances 0.000 description 2

- 239000005049 silicon tetrachloride Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 239000002344 surface layer Substances 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- QYKABQMBXCBINA-UHFFFAOYSA-N 4-(oxan-2-yloxy)benzaldehyde Chemical compound C1=CC(C=O)=CC=C1OC1OCCCC1 QYKABQMBXCBINA-UHFFFAOYSA-N 0.000 description 1

- 241000252506 Characiformes Species 0.000 description 1

- OTMSDBZUPAUEDD-UHFFFAOYSA-N Ethane Chemical compound CC OTMSDBZUPAUEDD-UHFFFAOYSA-N 0.000 description 1

- VGGSQFUCUMXWEO-UHFFFAOYSA-N Ethene Chemical compound C=C VGGSQFUCUMXWEO-UHFFFAOYSA-N 0.000 description 1

- 239000005977 Ethylene Substances 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 229910000530 Gallium indium arsenide Inorganic materials 0.000 description 1

- GPXJNWSHGFTCBW-UHFFFAOYSA-N Indium phosphide Chemical compound [In]#P GPXJNWSHGFTCBW-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910000676 Si alloy Inorganic materials 0.000 description 1

- 229910003902 SiCl 4 Inorganic materials 0.000 description 1

- 229910004298 SiO 2 Inorganic materials 0.000 description 1

- KXNLCSXBJCPWGL-UHFFFAOYSA-N [Ga].[As].[In] Chemical compound [Ga].[As].[In] KXNLCSXBJCPWGL-UHFFFAOYSA-N 0.000 description 1

- JFWWLEIVWNPOAL-UHFFFAOYSA-N [Ge].[Si].[Ge] Chemical compound [Ge].[Si].[Ge] JFWWLEIVWNPOAL-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 229910021529 ammonia Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 230000005540 biological transmission Effects 0.000 description 1

- LUXIMSHPDKSEDK-UHFFFAOYSA-N bis(disilanyl)silane Chemical compound [SiH3][SiH2][SiH2][SiH2][SiH3] LUXIMSHPDKSEDK-UHFFFAOYSA-N 0.000 description 1

- 239000007833 carbon precursor Substances 0.000 description 1

- 239000000969 carrier Substances 0.000 description 1

- 239000012159 carrier gas Substances 0.000 description 1

- VJTAZCKMHINUKO-UHFFFAOYSA-M chloro(2-methoxyethyl)mercury Chemical compound [Cl-].COCC[Hg+] VJTAZCKMHINUKO-UHFFFAOYSA-M 0.000 description 1

- 239000012141 concentrate Substances 0.000 description 1

- 238000002109 crystal growth method Methods 0.000 description 1

- 229910021419 crystalline silicon Inorganic materials 0.000 description 1

- BUMGIEFFCMBQDG-UHFFFAOYSA-N dichlorosilicon Chemical compound Cl[Si]Cl BUMGIEFFCMBQDG-UHFFFAOYSA-N 0.000 description 1

- PZPGRFITIJYNEJ-UHFFFAOYSA-N disilane Chemical compound [SiH3][SiH3] PZPGRFITIJYNEJ-UHFFFAOYSA-N 0.000 description 1

- 239000012776 electronic material Substances 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 1

- 230000005660 hydrophilic surface Effects 0.000 description 1

- 239000012535 impurity Substances 0.000 description 1

- 238000007689 inspection Methods 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 230000010354 integration Effects 0.000 description 1

- XCLKKWIIZMHQIV-UHFFFAOYSA-N isobutylgermane Chemical compound CC(C)C[Ge] XCLKKWIIZMHQIV-UHFFFAOYSA-N 0.000 description 1

- 238000002955 isolation Methods 0.000 description 1

- 229910052751 metal Inorganic materials 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 238000012986 modification Methods 0.000 description 1

- 230000004048 modification Effects 0.000 description 1

- APOOHHZPEUGNQX-UHFFFAOYSA-N n-methyl-n-trichlorogermylmethanamine Chemical compound CN(C)[Ge](Cl)(Cl)Cl APOOHHZPEUGNQX-UHFFFAOYSA-N 0.000 description 1

- 150000002894 organic compounds Chemical class 0.000 description 1

- 125000000082 organogermanium group Chemical group 0.000 description 1

- 238000002161 passivation Methods 0.000 description 1

- 239000012071 phase Substances 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 238000000678 plasma activation Methods 0.000 description 1

- 239000010453 quartz Substances 0.000 description 1

- 238000010791 quenching Methods 0.000 description 1

- 238000004064 recycling Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 238000005488 sandblasting Methods 0.000 description 1

- 229910052594 sapphire Inorganic materials 0.000 description 1

- 239000010980 sapphire Substances 0.000 description 1

- 229910021427 silicon allotrope Inorganic materials 0.000 description 1

- 239000002356 single layer Substances 0.000 description 1

- 238000010561 standard procedure Methods 0.000 description 1

- 238000005728 strengthening Methods 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000010301 surface-oxidation reaction Methods 0.000 description 1

- 230000000699 topical effect Effects 0.000 description 1

- VEDJZFSRVVQBIL-UHFFFAOYSA-N trisilane Chemical compound [SiH3][SiH2][SiH3] VEDJZFSRVVQBIL-UHFFFAOYSA-N 0.000 description 1

- 239000012808 vapor phase Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02002—Preparing wafers

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Recrystallisation Techniques (AREA)

- Crystals, And After-Treatments Of Crystals (AREA)

- Element Separation (AREA)

Description

であり、粗さプロファイルは、トレースに沿って規則的に等間隔に配置された点を含み、yiは、平均線からデータポイントまでの垂直距離である。

単結晶半導体ドナー基板、例えば単結晶半導体ドナーウエハに接合される。すなわち、単結晶半導体ドナーウエハは、酸化、注入、および注入後の洗浄を含む標準的なプロセスステップを受けてもよい。したがって、多層半導体構造の製造において従来から使用されている材料の単結晶半導体ウエハなどの単結晶半導体ドナー基板、例えば単結晶シリコンドナーウエハは、エッチングされ、研磨され、選択的に酸化されたものであるが、イオン注入されて、ドナー基板の中にダメージ層を形成する。

Claims (33)

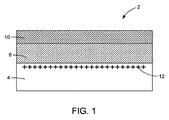

- その一方が単結晶半導体ハンドル基板の表面であり、他方が前記単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、前記単結晶半導体ハンドル基板の前記表面と前記裏面を接合する外縁と、前記単結晶半導体ハンドル基板の前記表面と前記裏面の間の中心平面と、および前記単結晶半導体ハンドル基板の前記表面と前記裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも3000Ω・cmの最小バルク領域抵抗率を有する単結晶半導体ハンドル基板と、

少なくとも20モル%のモルパーセントでゲルマニウムを含み、前記単結晶半導体ハンドル基板の前記表面に界面接触している緩和されたアモルファス半導体層と、

前記緩和されたアモルファス半導体層に界面接触している多結晶シリコン層を含み、少なくとも1000Ω・cmの抵抗率を有する電荷トラップ層と、

前記多結晶シリコン層を含む前記電荷トラップ層に界面接触している誘電体層と、

前記誘電体層に界面接触している単結晶半導体デバイス層と、

を含む多層構造。 - 前記単結晶半導体ハンドル基板は、3000Ω・cm〜100,000Ω・cmのバルク抵抗率を有する単結晶シリコンウエハを含む請求項1に記載の多層構造。

- 前記単結晶半導体ハンドル基板は、約3000Ω・cm〜約10,000Ω・cmのバルク抵抗率を有する請求項1に記載の多層構造。

- 前記単結晶半導体ハンドル基板は、約3000Ω・cm〜約5000Ω・cmのバルク抵抗率を有する請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも50モル%である請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも90モル%である請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも99.9モル%である請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、本質的にゲルマニウムから成る請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、臨界厚さより厚い請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層の平均厚さは、少なくとも約10ナノメートルである請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層の平均厚さは、約10ナノメートル〜約3000ナノメートルである請求項1に記載の多層構造。

- 前記誘電体層は、二酸化ケイ素、窒化ケイ素、酸化ハフニウム、酸化チタン、酸化ジルコニウム、酸化ランタン、酸化バリウム、およびそれらの組合せから成るグループから選択される請求項1に記載の多層構造。

- 前記誘電体層は、約10ナノメートル〜約10,000ナノメートル、約10ナノメートル〜約5000ナノメートル、または約100ナノメートル〜約400ナノメートルの厚さを有する埋め込み酸化物層を含む請求項1に記載の多層構造。

- 前記誘電体層は、二酸化シリコンを含む請求項1に記載の多層構造。

- 前記二酸化シリコンは、約10ナノメートル〜約10,000ナノメートル、約10ナノメートル〜約5000ナノメートル、または約100ナノメートル〜約400ナノメートルの厚さを有する請求項14に記載の多層構造。

- 75℃〜300℃の範囲の温度における化学気相堆積によって、単結晶半導体ハンドル基板の表面に界面接触するようにアモルファス半導体層を形成するステップであって、前記単結晶半導体ハンドル基板は、その一方が単結晶半導体ハンドル基板の表面であり、他方が前記単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、前記単結晶半導体ハンドル基板の前記表面と前記裏面を接合する外縁と、前記単結晶半導体ハンドル基板の前記表面と前記裏面の間の中心平面と、および前記単結晶半導体ハンドル基板の前記表面と前記裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも3000Ω・cmの最小バルク領域抵抗率を有し、更に、前記アモルファス半導体層は、少なくとも20モル%のゲルマニウムのモルパーセントでゲルマニウムを含むステップと、

前記アモルファス半導体層を少なくとも部分的に緩和するために、前記単結晶半導体ハンドル基板の前記表面に界面接触している前記アモルファス半導体層を有する前記単結晶半導体ハンドル基板を、600℃以上の温度で1秒〜1時間の期間アニールし、それによって緩和されたアモルファス半導体層を形成するステップと、

前記緩和されたアモルファス半導体層に界面接触している多結晶シリコン層を含み、少なくとも1000Ω・cmの抵抗率を有する電荷トラップ層を形成するステップと、

単結晶半導体ドナー基板の表面上の誘電体層を前記単結晶半導体ハンドル基板の前記多結晶シリコン層に接合させることによって接合構造を形成するステップであって、前記単結晶半導体ドナー基板は、その一方が前記半導体ドナー基板の表面であり、他方が前記半導体ドナー基板の裏面である2つの主要な、ほぼ平行な面と、前記半導体ドナー基板の前記表面と前記裏面を接合する外縁と、前記半導体ドナー基板の前記表面と前記裏面の間の中心平面と、を含み、更に、前記半導体ドナー基板の前記表面は、前記誘電体層を含むステップと、

を含む多層構造の製造方法。 - 前記単結晶半導体ハンドル基板は、3000Ω・cm〜100,000Ω・cmのバルク抵抗率を有する単結晶シリコンウエハを含む請求項16に記載の方法。

- 前記単結晶半導体ハンドル基板は、チョクラルスキー法またはフローティングゾーン法によって成長した単結晶シリコンインゴットからスライスされたシリコンウエハを含む請求項16に記載の方法。

- 前記単結晶半導体ハンドル基板は、約3000Ω・cm〜約10,000Ω・cmのバルク抵抗率を有する請求項16に記載の方法。

- 前記単結晶半導体ハンドル基板は、約3000Ω・cm〜約5000Ω・cmのバルク抵抗率を有する請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも50モル%である請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも90モル%である請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも99.9モル%である請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、ゲルマニウムを含む請求項16に記載の方法。

- 単結晶半導体ドナー基板の表面上の前記誘電体層に接合させるステップの前に前記多結晶シリコン層を含む電荷トラップ層を酸化させるステップを更に含む請求項16に記載の方法。

- 前記半導体ドナー基板の前記誘電体層と前記単結晶半導体ハンドル基板の前記表面上の前記多結晶シリコン層を含む電荷トラップ層との間の接合を強化するのに十分な温度で、および十分な期間、前記接合構造を加熱するステップを更に含む請求項16に記載の方法。

- 前記単結晶半導体ドナー基板は、イオン注入されたダメージ層を含み、

前記方法は、

前記単結晶半導体ドナー基板の前記イオン注入されたダメージ層で前記接合構造を機械的に劈開し、それによって前記単結晶半導体ハンドル基板と、前記緩和されたアモルファス半導体層と、前記緩和されたアモルファス半導体層に接触している前記多結晶シリコン層を含む電荷トラップ層と、前記誘電体層と、前記誘電体層に接触している単結晶半導体デバイス層と、を含む劈開構造を製造するステップと、

前記単結晶半導体デバイス層と前記単結晶半導体ハンドル基板との間の接合を強化するのに十分な温度で、および十分な期間、前記劈開構造を加熱するステップと、を含む請求項16に記載の方法。 - 前記緩和されたアモルファス半導体層は、ミスフィット転位、貫通転位、およびそれらの組合せから成るグループから選択される転位を含み、転位の密度は、1×105〜1×1010/cm2である請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、0.1モル%〜5モル%の濃度で炭素を含む請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、0.5モル%〜1モル%の濃度で炭素を含む請求項1に記載の多層構造。

- 前記緩和されたアモルファス半導体層は、ミスフィット転位、貫通転位、およびそれらの組合せから成るグループから選択される転位を含み、転位の密度は、1×105〜1×1010/cm2である請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、0.1モル%〜5モル%の濃度で炭素を含む請求項16に記載の方法。

- 前記緩和されたアモルファス半導体層は、0.5モル%〜1モル%の濃度で炭素を含む請求項16に記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201462081352P | 2014-11-18 | 2014-11-18 | |

| US62/081,352 | 2014-11-18 | ||

| PCT/US2015/060854 WO2016081356A1 (en) | 2014-11-18 | 2015-11-16 | High resistivity semiconductor-on-insulator wafer and a method of manufacturing |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020068195A Division JP7191886B2 (ja) | 2014-11-18 | 2020-04-06 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017538288A JP2017538288A (ja) | 2017-12-21 |

| JP2017538288A5 JP2017538288A5 (ja) | 2018-12-06 |

| JP6726180B2 true JP6726180B2 (ja) | 2020-07-22 |

Family

ID=54705879

Family Applications (4)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2017526096A Active JP6726180B2 (ja) | 2014-11-18 | 2015-11-16 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

| JP2020068195A Active JP7191886B2 (ja) | 2014-11-18 | 2020-04-06 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

| JP2021208175A Active JP7206366B2 (ja) | 2014-11-18 | 2021-12-22 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

| JP2023000068A Active JP7451777B2 (ja) | 2014-11-18 | 2023-01-04 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

Family Applications After (3)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2020068195A Active JP7191886B2 (ja) | 2014-11-18 | 2020-04-06 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

| JP2021208175A Active JP7206366B2 (ja) | 2014-11-18 | 2021-12-22 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

| JP2023000068A Active JP7451777B2 (ja) | 2014-11-18 | 2023-01-04 | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (3) | US10483152B2 (ja) |

| EP (3) | EP3573094B1 (ja) |

| JP (4) | JP6726180B2 (ja) |

| WO (1) | WO2016081356A1 (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6447439B2 (ja) * | 2015-09-28 | 2019-01-09 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

| US10622247B2 (en) * | 2016-02-19 | 2020-04-14 | Globalwafers Co., Ltd. | Semiconductor on insulator structure comprising a buried high resistivity layer |

| US10825681B2 (en) * | 2016-08-13 | 2020-11-03 | Applied Materials, Inc. | 3D CTF integration using hybrid charge trap layer of sin and self aligned SiGe nanodot |

| EP3533081B1 (en) * | 2016-10-26 | 2021-04-14 | GlobalWafers Co., Ltd. | High resistivity silicon-on-insulator substrate having enhanced charge trapping efficiency |

| EP3549162B1 (en) * | 2016-12-05 | 2022-02-02 | GlobalWafers Co., Ltd. | High resistivity silicon-on-insulator structure and method of manufacture thereof |

| US10943813B2 (en) | 2018-07-13 | 2021-03-09 | Globalwafers Co., Ltd. | Radio frequency silicon on insulator wafer platform with superior performance, stability, and manufacturability |

| CN110943066A (zh) * | 2018-09-21 | 2020-03-31 | 联华电子股份有限公司 | 具有高电阻晶片的半导体结构及高电阻晶片的接合方法 |

| FR3091618B1 (fr) * | 2019-01-09 | 2021-09-24 | Soitec Silicon On Insulator | Procédé de fabrication d’un substrat receveur pour une structure de type semi-conducteur sur isolant pour applications radiofrequences et procédé de fabrication d’une telle structure |

| US11296190B2 (en) * | 2020-01-15 | 2022-04-05 | Globalfoundries U.S. Inc. | Field effect transistors with back gate contact and buried high resistivity layer |

| US11715886B2 (en) * | 2020-05-08 | 2023-08-01 | Mobix Labs, Inc. | Low-cost, IPD and laminate based antenna array module |

| CN116487242A (zh) * | 2022-12-15 | 2023-07-25 | 苏州华太电子技术股份有限公司 | 抑制射频器件欧姆损耗的方法及射频器件 |

Family Cites Families (89)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4501060A (en) | 1983-01-24 | 1985-02-26 | At&T Bell Laboratories | Dielectrically isolated semiconductor devices |

| US4755865A (en) | 1986-01-21 | 1988-07-05 | Motorola Inc. | Means for stabilizing polycrystalline semiconductor layers |

| JPH0648686B2 (ja) | 1988-03-30 | 1994-06-22 | 新日本製鐵株式会社 | ゲッタリング能力の優れたシリコンウェーハおよびその製造方法 |

| JPH06105691B2 (ja) | 1988-09-29 | 1994-12-21 | 株式会社富士電機総合研究所 | 炭素添加非晶質シリコン薄膜の製造方法 |

| JP2617798B2 (ja) | 1989-09-22 | 1997-06-04 | 三菱電機株式会社 | 積層型半導体装置およびその製造方法 |

| US5461250A (en) * | 1992-08-10 | 1995-10-24 | International Business Machines Corporation | SiGe thin film or SOI MOSFET and method for making the same |

| US6043138A (en) | 1996-09-16 | 2000-03-28 | Advanced Micro Devices, Inc. | Multi-step polysilicon deposition process for boron penetration inhibition |

| US5783469A (en) | 1996-12-10 | 1998-07-21 | Advanced Micro Devices, Inc. | Method for making nitrogenated gate structure for improved transistor performance |

| FR2765393B1 (fr) * | 1997-06-25 | 2001-11-30 | France Telecom | Procede de gravure d'une couche de si1-xgex polycristallin ou d'un empilement d'une couche de si1-xgex polycristallin et d'une couche de si polycristallin, et son application a la microelectronique |

| US6068928A (en) | 1998-02-25 | 2000-05-30 | Siemens Aktiengesellschaft | Method for producing a polycrystalline silicon structure and polycrystalline silicon layer to be produced by the method |

| US6479166B1 (en) | 1998-10-06 | 2002-11-12 | Case Western Reserve University | Large area polysilicon films with predetermined stress characteristics and method for producing same |

| JP4313874B2 (ja) | 1999-02-02 | 2009-08-12 | キヤノン株式会社 | 基板の製造方法 |

| US6204205B1 (en) | 1999-07-06 | 2001-03-20 | Taiwan Semiconductor Manufacturing Company | Using H2anneal to improve the electrical characteristics of gate oxide |

| US6323108B1 (en) * | 1999-07-27 | 2001-11-27 | The United States Of America As Represented By The Secretary Of The Navy | Fabrication ultra-thin bonded semiconductor layers |

| US20020090758A1 (en) | 2000-09-19 | 2002-07-11 | Silicon Genesis Corporation | Method and resulting device for manufacturing for double gated transistors |

| JP4463957B2 (ja) | 2000-09-20 | 2010-05-19 | 信越半導体株式会社 | シリコンウエーハの製造方法およびシリコンウエーハ |

| US20050026432A1 (en) | 2001-04-17 | 2005-02-03 | Atwater Harry A. | Wafer bonded epitaxial templates for silicon heterostructures |

| US6562127B1 (en) | 2002-01-16 | 2003-05-13 | The United States Of America As Represented By The Secretary Of The Navy | Method of making mosaic array of thin semiconductor material of large substrates |

| US6562703B1 (en) * | 2002-03-13 | 2003-05-13 | Sharp Laboratories Of America, Inc. | Molecular hydrogen implantation method for forming a relaxed silicon germanium layer with high germanium content |

| US6995430B2 (en) | 2002-06-07 | 2006-02-07 | Amberwave Systems Corporation | Strained-semiconductor-on-insulator device structures |

| US7074623B2 (en) | 2002-06-07 | 2006-07-11 | Amberwave Systems Corporation | Methods of forming strained-semiconductor-on-insulator finFET device structures |

| US7057234B2 (en) | 2002-12-06 | 2006-06-06 | Cornell Research Foundation, Inc. | Scalable nano-transistor and memory using back-side trapping |

| JP4949014B2 (ja) | 2003-01-07 | 2012-06-06 | ソワテク | 薄層を除去した後の多層構造を備えるウェハのリサイクル |

| JP4853990B2 (ja) | 2003-01-29 | 2012-01-11 | ソイテック | 絶縁体上に歪み結晶層を製造する方法、前記方法による半導体構造及び製造された半導体構造 |

| US6995427B2 (en) | 2003-01-29 | 2006-02-07 | S.O.I.Tec Silicon On Insulator Technologies S.A. | Semiconductor structure for providing strained crystalline layer on insulator and method for fabricating same |

| US7005160B2 (en) | 2003-04-24 | 2006-02-28 | Asm America, Inc. | Methods for depositing polycrystalline films with engineered grain structures |

| WO2005013326A2 (en) * | 2003-07-30 | 2005-02-10 | Asm America, Inc. | Epitaxial growth of relaxed silicon germanium layers |

| JPWO2005022610A1 (ja) | 2003-09-01 | 2007-11-01 | 株式会社Sumco | 貼り合わせウェーハの製造方法 |

| US20070032040A1 (en) * | 2003-09-26 | 2007-02-08 | Dimitri Lederer | Method of manufacturing a multilayer semiconductor structure with reduced ohmic losses |

| US6992025B2 (en) * | 2004-01-12 | 2006-01-31 | Sharp Laboratories Of America, Inc. | Strained silicon on insulator from film transfer and relaxation by hydrogen implantation |

| US7018882B2 (en) * | 2004-03-23 | 2006-03-28 | Sharp Laboratories Of America, Inc. | Method to form local “silicon-on-nothing” or “silicon-on-insulator” wafers with tensile-strained silicon |

| US7279400B2 (en) * | 2004-08-05 | 2007-10-09 | Sharp Laboratories Of America, Inc. | Method of fabricating single-layer and multi-layer single crystalline silicon and silicon devices on plastic using sacrificial glass |

| US7312487B2 (en) | 2004-08-16 | 2007-12-25 | International Business Machines Corporation | Three dimensional integrated circuit |

| DE102004041378B4 (de) | 2004-08-26 | 2010-07-08 | Siltronic Ag | Halbleiterscheibe mit Schichtstruktur mit geringem Warp und Bow sowie Verfahren zu ihrer Herstellung |

| GB0424290D0 (en) * | 2004-11-02 | 2004-12-01 | Koninkl Philips Electronics Nv | Method of growing a strained layer |

| US7476594B2 (en) | 2005-03-30 | 2009-01-13 | Cree, Inc. | Methods of fabricating silicon nitride regions in silicon carbide and resulting structures |

| FR2890489B1 (fr) | 2005-09-08 | 2008-03-07 | Soitec Silicon On Insulator | Procede de fabrication d'une heterostructure de type semi-conducteur sur isolant |

| JP2007214199A (ja) | 2006-02-07 | 2007-08-23 | Canon Inc | 半導体基板及びその製造方法 |

| FR2897982B1 (fr) | 2006-02-27 | 2008-07-11 | Tracit Technologies Sa | Procede de fabrication des structures de type partiellement soi, comportant des zones reliant une couche superficielle et un substrat |

| US7936043B2 (en) * | 2006-03-17 | 2011-05-03 | Sychip Inc. | Integrated passive device substrates |

| FR2902233B1 (fr) | 2006-06-09 | 2008-10-17 | Soitec Silicon On Insulator | Procede de limitation de diffusion en mode lacunaire dans une heterostructure |

| FR2911430B1 (fr) | 2007-01-15 | 2009-04-17 | Soitec Silicon On Insulator | "procede de fabrication d'un substrat hybride" |

| KR101495153B1 (ko) | 2007-06-01 | 2015-02-24 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 기판의 제작 방법 및 반도체장치 |

| JP4445524B2 (ja) | 2007-06-26 | 2010-04-07 | 株式会社東芝 | 半導体記憶装置の製造方法 |

| JP2009016692A (ja) | 2007-07-06 | 2009-01-22 | Toshiba Corp | 半導体記憶装置の製造方法と半導体記憶装置 |

| US20090278233A1 (en) | 2007-07-26 | 2009-11-12 | Pinnington Thomas Henry | Bonded intermediate substrate and method of making same |

| US7915716B2 (en) | 2007-09-27 | 2011-03-29 | Stats Chippac Ltd. | Integrated circuit package system with leadframe array |

| US7879699B2 (en) | 2007-09-28 | 2011-02-01 | Infineon Technologies Ag | Wafer and a method for manufacturing a wafer |

| US8128749B2 (en) | 2007-10-04 | 2012-03-06 | International Business Machines Corporation | Fabrication of SOI with gettering layer |

| US7868419B1 (en) | 2007-10-18 | 2011-01-11 | Rf Micro Devices, Inc. | Linearity improvements of semiconductor substrate based radio frequency devices |

| JP2009135453A (ja) | 2007-10-30 | 2009-06-18 | Semiconductor Energy Lab Co Ltd | 半導体装置の作製方法、半導体装置及び電子機器 |

| US20090236689A1 (en) | 2008-03-24 | 2009-09-24 | Freescale Semiconductor, Inc. | Integrated passive device and method with low cost substrate |

| FR2933233B1 (fr) | 2008-06-30 | 2010-11-26 | Soitec Silicon On Insulator | Substrat de haute resistivite bon marche et procede de fabrication associe |

| FR2933234B1 (fr) | 2008-06-30 | 2016-09-23 | S O I Tec Silicon On Insulator Tech | Substrat bon marche a structure double et procede de fabrication associe |

| US8058137B1 (en) | 2009-04-14 | 2011-11-15 | Monolithic 3D Inc. | Method for fabrication of a semiconductor device and structure |

| JP2010258083A (ja) | 2009-04-22 | 2010-11-11 | Panasonic Corp | Soiウェーハ、その製造方法および半導体装置の製造方法 |

| KR101794182B1 (ko) | 2009-11-02 | 2017-11-06 | 후지 덴키 가부시키가이샤 | 반도체 장치 및 반도체 장치의 제조 방법 |

| JP5644096B2 (ja) | 2009-11-30 | 2014-12-24 | ソニー株式会社 | 接合基板の製造方法及び固体撮像装置の製造方法 |

| FR2953640B1 (fr) | 2009-12-04 | 2012-02-10 | S O I Tec Silicon On Insulator Tech | Procede de fabrication d'une structure de type semi-conducteur sur isolant, a pertes electriques diminuees et structure correspondante |

| US20110174362A1 (en) | 2010-01-18 | 2011-07-21 | Applied Materials, Inc. | Manufacture of thin film solar cells with high conversion efficiency |

| US9099526B2 (en) | 2010-02-16 | 2015-08-04 | Monolithic 3D Inc. | Integrated circuit device and structure |

| JP5836931B2 (ja) | 2010-03-26 | 2015-12-24 | テルモ株式会社 | 留置針組立体 |

| US8859393B2 (en) | 2010-06-30 | 2014-10-14 | Sunedison Semiconductor Limited | Methods for in-situ passivation of silicon-on-insulator wafers |

| US8642416B2 (en) | 2010-07-30 | 2014-02-04 | Monolithic 3D Inc. | Method of forming three dimensional integrated circuit devices using layer transfer technique |

| JP5117588B2 (ja) | 2010-09-07 | 2013-01-16 | 株式会社東芝 | 窒化物半導体結晶層の製造方法 |

| JP5627649B2 (ja) | 2010-09-07 | 2014-11-19 | 株式会社東芝 | 窒化物半導体結晶層の製造方法 |

| CN102465336B (zh) * | 2010-11-05 | 2014-07-09 | 上海华虹宏力半导体制造有限公司 | 一种高锗浓度的锗硅外延方法 |

| FR2967812B1 (fr) | 2010-11-19 | 2016-06-10 | S O I Tec Silicon On Insulator Tech | Dispositif electronique pour applications radiofrequence ou de puissance et procede de fabrication d'un tel dispositif |

| US9287353B2 (en) | 2010-11-30 | 2016-03-15 | Kyocera Corporation | Composite substrate and method of manufacturing the same |

| US8536021B2 (en) * | 2010-12-24 | 2013-09-17 | Io Semiconductor, Inc. | Trap rich layer formation techniques for semiconductor devices |

| EP2656388B1 (en) | 2010-12-24 | 2020-04-15 | QUALCOMM Incorporated | Trap rich layer for semiconductor devices |

| US8481405B2 (en) | 2010-12-24 | 2013-07-09 | Io Semiconductor, Inc. | Trap rich layer with through-silicon-vias in semiconductor devices |

| US8796116B2 (en) | 2011-01-31 | 2014-08-05 | Sunedison Semiconductor Limited | Methods for reducing the metal content in the device layer of SOI structures and SOI structures produced by such methods |

| JP6228462B2 (ja) * | 2011-03-16 | 2017-11-08 | エムイーエムシー・エレクトロニック・マテリアルズ・インコーポレイテッドMemc Electronic Materials,Incorporated | ハンドルウエハ内に高抵抗率領域を有するシリコン・オン・インシュレータ構造体およびそのような構造体の製法 |

| FR2973159B1 (fr) | 2011-03-22 | 2013-04-19 | Soitec Silicon On Insulator | Procede de fabrication d'un substrat de base |

| FR2973158B1 (fr) | 2011-03-22 | 2014-02-28 | Soitec Silicon On Insulator | Procédé de fabrication d'un substrat de type semi-conducteur sur isolant pour applications radiofréquences |

| FR2980916B1 (fr) | 2011-10-03 | 2014-03-28 | Soitec Silicon On Insulator | Procede de fabrication d'une structure de type silicium sur isolant |

| US9496255B2 (en) | 2011-11-16 | 2016-11-15 | Qualcomm Incorporated | Stacked CMOS chipset having an insulating layer and a secondary layer and method of forming same |

| US8741739B2 (en) | 2012-01-03 | 2014-06-03 | International Business Machines Corporation | High resistivity silicon-on-insulator substrate and method of forming |

| US20130193445A1 (en) | 2012-01-26 | 2013-08-01 | International Business Machines Corporation | Soi structures including a buried boron nitride dielectric |

| US8921209B2 (en) | 2012-09-12 | 2014-12-30 | International Business Machines Corporation | Defect free strained silicon on insulator (SSOI) substrates |

| US9202711B2 (en) | 2013-03-14 | 2015-12-01 | Sunedison Semiconductor Limited (Uen201334164H) | Semiconductor-on-insulator wafer manufacturing method for reducing light point defects and surface roughness |

| WO2014190165A2 (en) | 2013-05-24 | 2014-11-27 | Sunedison Semiconductor Limited | Methods for producing low oxygen silicon ingots |

| US8951896B2 (en) | 2013-06-28 | 2015-02-10 | International Business Machines Corporation | High linearity SOI wafer for low-distortion circuit applications |

| US9768056B2 (en) | 2013-10-31 | 2017-09-19 | Sunedison Semiconductor Limited (Uen201334164H) | Method of manufacturing high resistivity SOI wafers with charge trapping layers based on terminated Si deposition |

| US10079170B2 (en) | 2014-01-23 | 2018-09-18 | Globalwafers Co., Ltd. | High resistivity SOI wafers and a method of manufacturing thereof |

| WO2015119742A1 (en) | 2014-02-07 | 2015-08-13 | Sunedison Semiconductor Limited | Methods for preparing layered semiconductor structures |

| JP6118757B2 (ja) | 2014-04-24 | 2017-04-19 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

| JP6179530B2 (ja) | 2015-01-23 | 2017-08-16 | 信越半導体株式会社 | 貼り合わせsoiウェーハの製造方法 |

-

2015

- 2015-11-16 EP EP19185201.1A patent/EP3573094B1/en active Active

- 2015-11-16 EP EP15801615.4A patent/EP3221885B1/en active Active

- 2015-11-16 EP EP22213747.3A patent/EP4170705A3/en active Pending

- 2015-11-16 WO PCT/US2015/060854 patent/WO2016081356A1/en active Application Filing

- 2015-11-16 US US15/526,640 patent/US10483152B2/en active Active

- 2015-11-16 JP JP2017526096A patent/JP6726180B2/ja active Active

-

2018

- 2018-12-28 US US16/235,305 patent/US11139198B2/en active Active

-

2020

- 2020-04-06 JP JP2020068195A patent/JP7191886B2/ja active Active

-

2021

- 2021-08-25 US US17/445,840 patent/US11699615B2/en active Active

- 2021-12-22 JP JP2021208175A patent/JP7206366B2/ja active Active

-

2023

- 2023-01-04 JP JP2023000068A patent/JP7451777B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| EP3573094A1 (en) | 2019-11-27 |

| US20190139818A1 (en) | 2019-05-09 |

| EP3221885B1 (en) | 2019-10-23 |

| US11699615B2 (en) | 2023-07-11 |

| US11139198B2 (en) | 2021-10-05 |

| JP2023036918A (ja) | 2023-03-14 |

| WO2016081356A1 (en) | 2016-05-26 |

| JP2020113792A (ja) | 2020-07-27 |

| JP2017538288A (ja) | 2017-12-21 |

| JP7206366B2 (ja) | 2023-01-17 |

| EP4170705A3 (en) | 2023-10-18 |

| JP7191886B2 (ja) | 2022-12-19 |

| JP2022037175A (ja) | 2022-03-08 |

| JP7451777B2 (ja) | 2024-03-18 |

| EP3573094B1 (en) | 2023-01-04 |

| EP4170705A2 (en) | 2023-04-26 |

| US20210384070A1 (en) | 2021-12-09 |

| US10483152B2 (en) | 2019-11-19 |

| US20170316968A1 (en) | 2017-11-02 |

| EP3221885A1 (en) | 2017-09-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10784146B2 (en) | Method of depositing charge trapping polycrystalline silicon films on silicon substrates with controllable film stress | |

| US10381261B2 (en) | Method of manufacturing high resistivity semiconductor-on-insulator wafers with charge trapping layers | |

| US10672645B2 (en) | Method of manufacturing high resistivity SOI wafers with charge trapping layers based on terminated Si deposition | |

| JP7451777B2 (ja) | 高抵抗率半導体・オン・インシュレータウエハおよび製造方法 | |

| JP6730402B2 (ja) | 高抵抗率soiウエハおよびその製造方法 | |

| US10468294B2 (en) | High resistivity silicon-on-insulator substrate comprising a charge trapping layer formed on a substrate with a rough surface |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20181026 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20181026 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20190625 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20190702 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A711 Effective date: 20190926 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191001 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20191210 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20200406 |

|

| C60 | Trial request (containing other claim documents, opposition documents) |

Free format text: JAPANESE INTERMEDIATE CODE: C60 Effective date: 20200406 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20200415 |

|

| C21 | Notice of transfer of a case for reconsideration by examiners before appeal proceedings |

Free format text: JAPANESE INTERMEDIATE CODE: C21 Effective date: 20200421 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200602 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200626 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6726180 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |