JP6668897B2 - 給電制御装置 - Google Patents

給電制御装置 Download PDFInfo

- Publication number

- JP6668897B2 JP6668897B2 JP2016075885A JP2016075885A JP6668897B2 JP 6668897 B2 JP6668897 B2 JP 6668897B2 JP 2016075885 A JP2016075885 A JP 2016075885A JP 2016075885 A JP2016075885 A JP 2016075885A JP 6668897 B2 JP6668897 B2 JP 6668897B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor switch

- voltage

- power supply

- terminal

- control terminal

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J1/00—Circuit arrangements for dc mains or dc distribution networks

- H02J1/001—Hot plugging or unplugging of load or power modules to or from power distribution networks

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/51—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used

- H03K17/56—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices

- H03K17/687—Electronic switching or gating, i.e. not by contact-making and –breaking characterised by the components used by the use, as active elements, of semiconductor devices the devices being field-effect transistors

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J1/00—Circuit arrangements for dc mains or dc distribution networks

- H02J1/10—Parallel operation of dc sources

- H02J1/102—Parallel operation of dc sources being switching converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02J—CIRCUIT ARRANGEMENTS OR SYSTEMS FOR SUPPLYING OR DISTRIBUTING ELECTRIC POWER; SYSTEMS FOR STORING ELECTRIC ENERGY

- H02J7/00—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries

- H02J7/00032—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries characterised by data exchange

- H02J7/00038—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries characterised by data exchange using passive battery identification means, e.g. resistors or capacitors

- H02J7/00043—Circuit arrangements for charging or depolarising batteries or for supplying loads from batteries characterised by data exchange using passive battery identification means, e.g. resistors or capacitors using switches, contacts or markings, e.g. optical, magnetic or barcode

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M3/00—Conversion of dc power input into dc power output

- H02M3/02—Conversion of dc power input into dc power output without intermediate conversion into ac

- H02M3/04—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters

- H02M3/10—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M3/145—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M3/155—Conversion of dc power input into dc power output without intermediate conversion into ac by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/08—Modifications for protecting switching circuit against overcurrent or overvoltage

- H03K17/082—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit

- H03K17/0822—Modifications for protecting switching circuit against overcurrent or overvoltage by feedback from the output to the control circuit in field-effect transistor switches

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/161—Modifications for eliminating interference voltages or currents in field-effect transistor switches

Description

また、オン又はオフに切替え半導体スイッチは、第1半導体スイッチ及び第2半導体スイッチのみである。

バッテリの正極が第1半導体スイッチの電流入力端に接続され、負荷の一端が第2半導体スイッチの電流出力端に接続され、バッテリの負極が負荷の他端に接続されている場合において、第1半導体スイッチ及び第2半導体スイッチがオフであるとき、バッテリによってキャパシタは充電されている。切替え部が第2半導体スイッチの制御端の電圧を上昇させた場合、第2半導体スイッチを介して負荷に流れる電流が上昇し、第2半導体スイッチの電流出力端の電圧が上昇する。これにより、第2半導体スイッチの制御端の電圧がバッテリの出力電圧未満であっても、キャパシタのバッテリ側の一端における電圧がバッテリの出力電圧を超え、第1半導体スイッチの制御端に接続されている寄生容量が充電される。結果、第1半導体スイッチが、より速くオンに切替わる。

複数の第2半導体スイッチ夫々の電流入力端は、第1半導体スイッチの電流出力端に接続されている。第1半導体スイッチの制御端には、複数のダイオード夫々のカソードが接続されており、複数のダイオード夫々のアノードは、複数の第2半導体スイッチの制御端に接続されている。切替え部が、複数の第2半導体スイッチ中の少なくとも1つの制御端の電圧を上昇させた場合、第1半導体スイッチと、電圧を上昇させた一又は複数の制御端に対応する一又は複数の第2半導体スイッチとがオンに切替わる。複数の第2半導体スイッチを各別にオン又はオフに切替えることによって、複数の第2半導体スイッチを介した給電を制御する。

第1半導体スイッチ及び第2半導体スイッチ夫々は、例えば、Nチャネル型のFETであり、第1半導体スイッチのドレインが第2半導体スイッチのドレインに接続されている。

(実施の形態1)

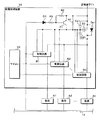

図1は、実施の形態1における電源システム1の要部構成を示すブロック図である。電源システム1は、車両に好適に搭載されており、給電制御装置10、バッテリ11、導体12及び負荷A1を備える。導体12は例えば、車両のボディである。

バッテリ11の接続を誤った場合、給電制御装置10は、負極端子T2から負荷A1に電流が流れることを防止する。

第1半導体スイッチ20はNチャネル型のFETである。従って、給電制御装置10は、更に、第1半導体スイッチ20の製造時に形成される寄生ダイオードDp1及び寄生容量Cs1,Cd1を有する。寄生ダイオードDp1は、第1半導体スイッチ20のドレイン及びソース間に接続され、寄生ダイオードDp1のカソード及びアノード夫々は第1半導体スイッチ20のドレイン及びソースに接続されている。寄生容量Cs1は第1半導体スイッチ20のゲート及びソース間に接続され、寄生容量Cd1は第1半導体スイッチ20のゲート及びドレイン間に接続されている。スイッチ21はNPN型のバイポーラトランジスタである。

第2半導体スイッチ30はNチャネル型のFETである。従って、制御回路B1は、更に、第2半導体スイッチ30の製造時に形成される寄生ダイオードDp2及び寄生容量Cs2,Cd2を有する。寄生ダイオードDp2は、第2半導体スイッチ30のドレイン及びソース間に接続され、寄生ダイオードDp2のカソード及びアノード夫々は第2半導体スイッチ30のドレイン及びソースに接続されている。寄生容量Cs2は第2半導体スイッチ30のゲート及びソース間に接続され、寄生容量Cd2は第2半導体スイッチ30のゲート及びドレイン間に接続されている。

抵抗R2の他端は、スイッチ21のベース、及び、抵抗R3の一端に接続されている。抵抗R3の他端はダイオードD1のカソードに接続されている。ダイオードD1のアノードは導体12に接続されている。

また、たとえ第1半導体スイッチ20及び第2半導体スイッチ30がオンであっても、バッテリ11の接続を誤った場合、第1半導体スイッチ20は強制的にオフに切替わるので、負荷A1に電流が流れることが確実に防止される。

第1半導体スイッチ20においては、ゲートから寄生容量Cs1,Cd1に電流を供給し、ソースの電位を基準としたゲートの電圧をオン閾値Vn1以上に上昇させる。これにより、第1半導体スイッチ20をオンに切替える。

また、寄生容量Cs1,Cd1に放電させることによって、ソースの電位を基準としたゲートの電圧を、オフ閾値Vf1未満に低下させる。これにより、第1半導体スイッチ20がオフに切替わる。

また、寄生容量Cs2,Cd2に放電させることによって、ソースの電位を基準としたゲートの電圧を、オフ閾値Vf2未満に低下させる。これにより、第2半導体スイッチ30がオフに切替わる。

駆動部31は、駆動信号が入力された場合、図示しない内部抵抗を介して、バッテリ11の出力電圧Vbよりも高い駆動電圧を、第2半導体スイッチ30のゲートと、第1半導体スイッチ20のゲートとに出力する。駆動部31は、内部抵抗及びダイオードD2を介して、第1半導体スイッチ20のゲートに駆動電圧を出力する。

このため、第1半導体スイッチ20のソースと、第2半導体スイッチ30のドレインとは電流入力端として機能し、第1半導体スイッチ20のドレインと、第2半導体スイッチ30のソースとは電流出力端として機能する。第1半導体スイッチ20及び第2半導体スイッチ30夫々のゲートは制御端として機能する。

第2半導体スイッチ30のゲートが駆動部31の内部抵抗を介して導体12に接続されている状態で寄生容量Cs1,Cd1の放電が終了した時点では、寄生容量Cs1,Cd1夫々の両端間の電圧は略ゼロVであり、寄生容量Cs1,Cd1夫々が蓄積している電力は略ゼロWである。

比較対象の給電制御装置は、抵抗R1が設けられておらず、かつ、第1半導体スイッチ20のゲートがダイオードD2を介さずに第2半導体スイッチ30のゲートに接続されている給電制御装置である。比較対象の給電制御装置でも、駆動部31が駆動電圧を出力することによって、第1半導体スイッチ20及び第2半導体スイッチ30をオフからオンに切替えることが可能である。

当然のことながら、給電制御装置10及び比較対象の給電制御装置夫々において、駆動部31が供給する電力は同じである。

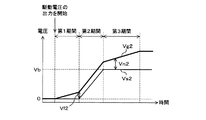

給電制御装置10、及び、比較対象の給電制御装置夫々について、ソース電圧Vs2及びゲート電圧Vg2夫々の推移の傾向は、変わらない。

なお、第1期間において、ゲート電圧Vg2の上昇によって、第1半導体スイッチ20のドレインの電圧が上昇する。一方で、第1半導体スイッチ20のゲートの電圧はバッテリ11の出力電圧Vbに維持されている。このため、寄生容量Cd1が充電される。しかしながら、寄生容量Cd1の静電容量は、例えば、寄生容量Cs1の静電容量の10分の1であり、十分に小さいので、第1期間に寄生容量Cd1に供給される電力は無視できる程度に小さい。

また、給電制御装置10では、駆動部31が第2半導体スイッチ30のゲートの電圧を調整することによって、第1半導体スイッチ20及び第2半導体スイッチ30をオン又はオフに切替えているので、製造費用が安価である。

図4は実施の形態2における給電制御装置10の回路図である。

以下では、実施の形態2について、実施の形態1と異なる点を説明する。後述する構成を除く他の構成については、実施の形態1と共通しているため、実施の形態1と共通する構成部には実施の形態1と同一の参照符号を付してその説明を省略する。

実施の形態2における給電制御装置10を実施の形態1における給電制御装置10と比較した場合、制御回路B1がキャパシタC1を更に有する点が異なる。キャパシタC1は、第1半導体スイッチ20のゲートと、第2半導体スイッチ30のソースとの間に接続されている。このため、駆動部31が駆動電圧を第2半導体スイッチ30のゲートに出力した場合に、第1半導体スイッチ20は、より速くオフからオンに切替わる。以下では、バッテリ11が正常に接続されている場合における給電制御装置10を説明する。

以上のように、実施の形態2における給電制御装置10においては、駆動部31が駆動電圧を出力してから第1半導体スイッチ20がオンに切替わるまでの期間が更に短い。このように、第1半導体スイッチ20は、より速くオンに切替わるため、第1半導体スイッチ20において、電流が寄生ダイオードDp1を流れている期間が更に短く、第1半導体スイッチ20で消費される電力が更に小さい。

実施の形態2においては、給電制御装置10が給電を制御する負荷の数は1つである。しかしながら、給電制御装置10が給電を制御する負荷の数は2以上であってもよい。

以下では、実施の形態3について、実施の形態2と異なる点を説明する。後述する構成を除く他の構成については、実施の形態2と共通しているため、実施の形態2と共通する構成部には実施の形態2と同一の参照符号を付してその説明を省略する。

バッテリ11の接続を誤った場合、給電制御装置10は、負極端子T2からn個の負荷A1,A2,・・・,Anに電流が流れることを防止する。

従って、制御回路Bkの第2半導体スイッチ30のドレインは、第1半導体スイッチ20のドレインに接続されている。更に、制御回路BkのダイオードD2のカソードは第1半導体スイッチ20のゲートに接続され、制御回路BkのダイオードD2のアノードは、制御回路Bkの第2半導体スイッチ30のゲートに接続されている。

制御回路Bkは、更に、ダイオードD3,D4を有する。制御回路Bkにおいて、ダイオードD3のカソードは第1半導体スイッチ20のゲートに接続されている。ダイオードD3のアノードは、ダイオードD4のカソードと、キャパシタC1の一端とに接続されている。ダイオードD4のアノードは、第1半導体スイッチ20のドレインに接続されている。キャパシタC1の他端は第2半導体スイッチ30のソースに接続されている。寄生ダイオードDp1,Dp2及びダイオードD2夫々の順方向の電圧降下の幅と同様に、ダイオードD3,D4夫々の順方向の電圧降下の幅も十分に小さいとみなす。

ダイオードD3は第2のダイオードとして機能し、ダイオードD4は第3のダイオードとして機能する。

制御回路Bkの駆動部31は、実施の形態2における駆動部31と同様に、駆動信号が入力された場合、図示しない内部抵抗を介して、駆動電圧を制御回路Bkの第2半導体スイッチ30のゲートと、第1半導体スイッチ20のゲートとに出力する。これにより、第1半導体スイッチ20、及び、制御回路Bkの第2半導体スイッチ30夫々のゲートの電圧が上昇し、第1半導体スイッチ20と、制御回路Bkの第2半導体スイッチ30とがオンに切替わる。

マイコン22は、n個の制御回路B1,B2,・・・,Bn夫々の駆動部31に駆動信号又は停止信号を出力することによって、n個の制御回路B1,B2,・・・,Bnの動作を各別に制御する。

20 第1半導体スイッチ

21 スイッチ

30 第2半導体スイッチ

31 駆動部(切替え部の一部)

C1 キャパシタ

Dp1 寄生ダイオード

D2 ダイオード

D3 ダイオード(第2のダイオード)

D4 ダイオード(第3のダイオード)

R1 抵抗

Claims (6)

- 第1半導体スイッチと、電流入力端が該第1半導体スイッチの電流出力端に接続されている第2半導体スイッチとをオン又はオフに切替える切替え部を備え、該切替え部の切替えにより、前記第2半導体スイッチを介した給電を制御する給電制御装置において、

前記第1半導体スイッチ及び第2半導体スイッチ夫々は、制御端の電圧がオン閾値以上である場合にオンに切替わり、該制御端の電圧がオフ閾値未満である場合にオフに切替わり、

前記第1半導体スイッチの前記電流入力端及び制御端間に接続される抵抗と、

カソードが前記第1半導体スイッチの前記制御端に接続され、アノードが前記第2半導体スイッチの前記制御端に接続されるダイオードと

を備え、

前記切替え部は、前記第2半導体スイッチの前記制御端の電圧を調整することによって前記切替えを行い、

前記切替え部がオン又はオフに切替える半導体スイッチは、前記第1半導体スイッチ及び第2半導体スイッチのみであること

を特徴とする給電制御装置。 - 第1半導体スイッチと、電流入力端が該第1半導体スイッチの電流出力端に接続されている第2半導体スイッチとをオン又はオフに切替える切替え部を備え、該切替え部の切替えにより、前記第2半導体スイッチを介した給電を制御する給電制御装置において、

前記第1半導体スイッチ及び第2半導体スイッチ夫々は、制御端の電圧がオン閾値以上である場合にオンに切替わり、該制御端の電圧がオフ閾値未満である場合にオフに切替わり、

前記第1半導体スイッチの前記電流入力端及び制御端間に接続される抵抗と、

カソードが前記第1半導体スイッチの前記制御端に接続され、アノードが前記第2半導体スイッチの前記制御端に接続されるダイオードと、

カソード及びアノードが前記第1半導体スイッチの前記電流出力端及び電流入力端に接続される寄生ダイオードと、

前記第1半導体スイッチの前記制御端、及び、前記第2半導体スイッチの前記電流出力端の間に接続されるキャパシタと

を備え、

前記切替え部は、前記第2半導体スイッチの前記制御端の電圧を調整することによって前記切替えを行うこと

を特徴とする給電制御装置。 - 第1半導体スイッチと、電流入力端が該第1半導体スイッチの電流出力端に接続されている第2半導体スイッチとをオン又はオフに切替える切替え部を備え、該切替え部の切替えにより、前記第2半導体スイッチを介した給電を制御する給電制御装置において、

前記第1半導体スイッチ及び第2半導体スイッチ夫々は、制御端の電圧がオン閾値以上である場合にオンに切替わり、該制御端の電圧がオフ閾値未満である場合にオフに切替わり、

前記第1半導体スイッチの前記電流入力端及び制御端間に接続される抵抗と、

カソードが前記第1半導体スイッチの前記制御端に接続され、アノードが前記第2半導体スイッチの前記制御端に接続されるダイオードと

を備え、

前記第2半導体スイッチ及びダイオード夫々の数は、2以上であって同じであり、

複数の前記第2半導体スイッチ夫々の前記電流入力端は、前記第1半導体スイッチの電流出力端に接続され、

複数の前記ダイオードのカソードは第1半導体スイッチの前記制御端に接続され、

前記複数のダイオード夫々のアノードは、前記複数の第2半導体スイッチの制御端に接続され、

前記切替え部は、前記複数の第2半導体スイッチの前記制御端の電圧を各別に調整すること

を特徴とする給電制御装置。 - カソード及びアノードが前記第1半導体スイッチの前記電流出力端及び電流入力端に接続される寄生ダイオードと、

カソードが前記第1半導体スイッチの前記制御端に接続される複数の第2のダイオードと、

カソードが前記複数の第2のダイオード夫々のアノードに接続され、アノードが前記第1半導体スイッチの前記電流出力端に接続される複数の第3のダイオードと、

一端が前記複数の第2のダイオード夫々のアノードに接続される複数のキャパシタと

を備え、

前記第2のダイオード、第3のダイオード及びキャパシタ夫々の数は前記第2半導体スイッチの数と同じであり、

前記複数のキャパシタ夫々の他端は、前記複数の第2半導体スイッチの前記電流出力端に接続されること

を特徴とする請求項3に記載に給電制御装置。 - 第1半導体スイッチと、電流入力端が該第1半導体スイッチの電流出力端に接続されている第2半導体スイッチとをオン又はオフに切替える切替え部を備え、該切替え部の切替えにより、前記第2半導体スイッチを介した給電を制御する給電制御装置において、

前記第1半導体スイッチ及び第2半導体スイッチ夫々は、制御端の電圧がオン閾値以上である場合にオンに切替わり、該制御端の電圧がオフ閾値未満である場合にオフに切替わり、

前記第1半導体スイッチの前記電流入力端及び制御端間に接続される抵抗と、

カソードが前記第1半導体スイッチの前記制御端に接続され、アノードが前記第2半導体スイッチの前記制御端に接続されるダイオードと

を備え、

前記切替え部は、前記第2半導体スイッチの前記制御端の電圧を調整することによって前記切替えを行い、

前記第1半導体スイッチは、電流入力端の電位を基準とした前記制御端の電圧に基づいてオン又はオフに切替わり、

前記第2半導体スイッチは、電流出力端の電位を基準とした前記制御端の電圧に基づいてオン又はオフに切替わること

を特徴とする給電制御装置。 - 前記第1半導体スイッチの電流入力端及び制御端間に接続され、前記第2半導体スイッチの電流出力端の電位を基準として、前記第1半導体スイッチの電流入力端に負の電圧が印加された場合にオンに切替わるスイッチを備え、

前記第1半導体スイッチは、電流入力端及び制御端間の電圧が略ゼロVである場合にオフであること

を特徴とする請求項5に記載の給電制御装置。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016075885A JP6668897B2 (ja) | 2016-04-05 | 2016-04-05 | 給電制御装置 |

| CN201780017479.1A CN108781078B (zh) | 2016-04-05 | 2017-03-22 | 供电控制装置 |

| US16/090,427 US10411696B2 (en) | 2016-04-05 | 2017-03-22 | Power supply control device |

| DE112017001921.4T DE112017001921T5 (de) | 2016-04-05 | 2017-03-22 | Energieversorgungs-Steuereinrichtung |

| PCT/JP2017/011413 WO2017175584A1 (ja) | 2016-04-05 | 2017-03-22 | 給電制御装置 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2016075885A JP6668897B2 (ja) | 2016-04-05 | 2016-04-05 | 給電制御装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2017188773A JP2017188773A (ja) | 2017-10-12 |

| JP2017188773A5 JP2017188773A5 (ja) | 2018-08-30 |

| JP6668897B2 true JP6668897B2 (ja) | 2020-03-18 |

Family

ID=60001139

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016075885A Active JP6668897B2 (ja) | 2016-04-05 | 2016-04-05 | 給電制御装置 |

Country Status (5)

| Country | Link |

|---|---|

| US (1) | US10411696B2 (ja) |

| JP (1) | JP6668897B2 (ja) |

| CN (1) | CN108781078B (ja) |

| DE (1) | DE112017001921T5 (ja) |

| WO (1) | WO2017175584A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP6668897B2 (ja) * | 2016-04-05 | 2020-03-18 | 株式会社オートネットワーク技術研究所 | 給電制御装置 |

| JP6740709B2 (ja) * | 2016-05-20 | 2020-08-19 | 株式会社オートネットワーク技術研究所 | 給電制御装置 |

| JP6891835B2 (ja) * | 2018-02-22 | 2021-06-18 | 株式会社オートネットワーク技術研究所 | 制御装置 |

| JP7026016B2 (ja) * | 2018-07-20 | 2022-02-25 | ルネサスエレクトロニクス株式会社 | 半導体装置および電子制御装置 |

| JP2022080104A (ja) * | 2020-11-17 | 2022-05-27 | 株式会社オートネットワーク技術研究所 | 給電制御装置、給電制御方法及びコンピュータプログラム |

| CN112994436B (zh) * | 2021-02-04 | 2022-06-03 | 重庆先进光电显示技术研究院 | 一种栅极开启电压产生电路、显示面板驱动装置及显示装置 |

| JP2022149753A (ja) * | 2021-03-25 | 2022-10-07 | 株式会社オートネットワーク技術研究所 | ラッチ回路及び給電制御装置 |

| CN113708467B (zh) * | 2021-10-29 | 2022-02-22 | 苏州浪潮智能科技有限公司 | 一种上电电路、电池备份单元及存储服务器系统 |

| US20230216402A1 (en) * | 2022-01-04 | 2023-07-06 | Nuvolta Technologies (Hefei) Co., Ltd. | Gate Drive Voltage Regulation Apparatus and Control Method |

Family Cites Families (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0998567A (ja) * | 1995-07-27 | 1997-04-08 | Toshiyasu Suzuki | 絶縁給電手段と変圧手段 |

| DE19848159A1 (de) * | 1998-10-20 | 2000-04-27 | Bosch Gmbh Robert | Schaltungsanordnung für eine elektronische Leistungsendstufe |

| JP4149778B2 (ja) * | 2002-10-28 | 2008-09-17 | 矢崎総業株式会社 | 車両用電力制御装置 |

| JP4150297B2 (ja) * | 2003-06-30 | 2008-09-17 | ソニー株式会社 | 電界効果トランジスタのドライブ回路 |

| JP2006108568A (ja) * | 2004-10-08 | 2006-04-20 | Sanyo Electric Co Ltd | スイッチング素子およびそれを用いた保護回路 |

| JP2006158185A (ja) * | 2004-10-25 | 2006-06-15 | Toshiba Corp | 電力用半導体装置 |

| CN1909325A (zh) * | 2005-08-01 | 2007-02-07 | 三洋电机株式会社 | 具有保护电路的电池组 |

| JP2008109349A (ja) * | 2006-10-25 | 2008-05-08 | Matsushita Electric Ind Co Ltd | 逆流電流防止回路 |

| KR101110102B1 (ko) | 2007-03-05 | 2012-03-13 | 봇슈 가부시키가이샤 | 글로우 플러그 구동 장치 |

| JP4536108B2 (ja) * | 2007-12-12 | 2010-09-01 | Okiセミコンダクタ株式会社 | 負荷駆動回路 |

| JP5217849B2 (ja) * | 2008-09-29 | 2013-06-19 | サンケン電気株式会社 | 電気回路のスイッチング装置 |

| JP2014003514A (ja) * | 2012-06-20 | 2014-01-09 | Renesas Electronics Corp | 半導体装置及び通信システム |

| JP5772776B2 (ja) | 2012-09-28 | 2015-09-02 | 株式会社オートネットワーク技術研究所 | 電力供給制御装置 |

| JP5502216B1 (ja) * | 2013-02-28 | 2014-05-28 | 三菱電機株式会社 | 電気負荷の分岐給電制御装置及び分岐給電制御方法 |

| JP6157752B2 (ja) * | 2014-09-09 | 2017-07-05 | 三菱電機株式会社 | 多相交流モータ駆動用インバータ装置 |

| WO2017009990A1 (ja) * | 2015-07-15 | 2017-01-19 | 株式会社 東芝 | 半導体装置 |

| JP6566355B2 (ja) * | 2015-09-11 | 2019-08-28 | パナソニックIpマネジメント株式会社 | 電力変換装置 |

| US10069439B2 (en) * | 2015-12-22 | 2018-09-04 | Renesas Electronics Corporation | Power conversion system, power module, and semiconductor device with diode coupling |

| CN114567192A (zh) * | 2016-03-04 | 2022-05-31 | 日本电产株式会社 | 电力转换装置、马达驱动单元和电动助力转向装置 |

| JP6668897B2 (ja) * | 2016-04-05 | 2020-03-18 | 株式会社オートネットワーク技術研究所 | 給電制御装置 |

| CN117175565A (zh) * | 2017-03-29 | 2023-12-05 | 太阳能安吉科技有限公司 | 旁路电路和在电力系统中旁通电力模块的方法 |

-

2016

- 2016-04-05 JP JP2016075885A patent/JP6668897B2/ja active Active

-

2017

- 2017-03-22 CN CN201780017479.1A patent/CN108781078B/zh active Active

- 2017-03-22 US US16/090,427 patent/US10411696B2/en active Active

- 2017-03-22 WO PCT/JP2017/011413 patent/WO2017175584A1/ja active Application Filing

- 2017-03-22 DE DE112017001921.4T patent/DE112017001921T5/de active Pending

Also Published As

| Publication number | Publication date |

|---|---|

| US10411696B2 (en) | 2019-09-10 |

| US20190123739A1 (en) | 2019-04-25 |

| DE112017001921T5 (de) | 2018-12-13 |

| CN108781078A (zh) | 2018-11-09 |

| WO2017175584A1 (ja) | 2017-10-12 |

| CN108781078B (zh) | 2021-11-16 |

| JP2017188773A (ja) | 2017-10-12 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6668897B2 (ja) | 給電制御装置 | |

| WO2017175578A1 (ja) | 給電制御装置 | |

| CN108701990B (zh) | 供电控制装置 | |

| WO2017122664A1 (ja) | 給電制御装置 | |

| US10396661B2 (en) | Power supply control apparatus | |

| JP6708003B2 (ja) | 給電制御装置 | |

| CN110190840B (zh) | 控制装置 | |

| WO2023231318A1 (zh) | 用于无人车的电压保持装置及无人车 | |

| WO2021033527A1 (ja) | 出力装置 | |

| CN111756085A (zh) | 供电控制装置 | |

| WO2021230051A1 (ja) | 給電制御装置 | |

| WO2018147102A1 (ja) | スイッチ制御装置 | |

| JP7413860B2 (ja) | 給電制御装置 | |

| WO2023079975A1 (ja) | 制御装置 | |

| JP4538990B2 (ja) | 電圧制御装置 | |

| CN108292851B (zh) | 供电控制装置 | |

| WO2021033630A1 (ja) | スイッチ装置 | |

| WO2021131698A1 (ja) | 給電制御装置 | |

| US11881850B2 (en) | Driving apparatus | |

| US20190363705A1 (en) | Switch circuit and power source apparatus |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180717 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20180727 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20191001 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20191031 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20200128 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20200210 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6668897 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |