JP6495272B2 - Mos−バイポーラ素子 - Google Patents

Mos−バイポーラ素子 Download PDFInfo

- Publication number

- JP6495272B2 JP6495272B2 JP2016528598A JP2016528598A JP6495272B2 JP 6495272 B2 JP6495272 B2 JP 6495272B2 JP 2016528598 A JP2016528598 A JP 2016528598A JP 2016528598 A JP2016528598 A JP 2016528598A JP 6495272 B2 JP6495272 B2 JP 6495272B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- well region

- trench

- semiconductor

- well

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 claims description 39

- 238000000034 method Methods 0.000 claims description 33

- 238000004519 manufacturing process Methods 0.000 claims description 12

- 239000000758 substrate Substances 0.000 claims description 9

- 230000015572 biosynthetic process Effects 0.000 claims description 5

- 238000003491 array Methods 0.000 claims 1

- 238000009792 diffusion process Methods 0.000 description 8

- 238000005530 etching Methods 0.000 description 3

- 238000005468 ion implantation Methods 0.000 description 3

- 238000000206 photolithography Methods 0.000 description 3

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 3

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 239000000463 material Substances 0.000 description 2

- 239000002184 metal Substances 0.000 description 2

- 238000003860 storage Methods 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 238000000407 epitaxy Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 238000002513 implantation Methods 0.000 description 1

- 229910044991 metal oxide Inorganic materials 0.000 description 1

- 150000004706 metal oxides Chemical class 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 230000000149 penetrating effect Effects 0.000 description 1

- 230000000630 rising effect Effects 0.000 description 1

- 238000000926 separation method Methods 0.000 description 1

- 229910052710 silicon Inorganic materials 0.000 description 1

- 239000010703 silicon Substances 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 229910010271 silicon carbide Inorganic materials 0.000 description 1

- 239000002210 silicon-based material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0603—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions

- H01L29/0607—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration

- H01L29/0611—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices

- H01L29/0615—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by particular constructional design considerations, e.g. for preventing surface leakage, for controlling electric field concentration or for internal isolations regions for preventing surface leakage or controlling electric field concentration for increasing or controlling the breakdown voltage of reverse biased devices by the doping profile or the shape or the arrangement of the PN junction, or with supplementary regions, e.g. junction termination extension [JTE]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/0684—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions characterised by the shape, relative sizes or dispositions of the semiconductor regions or junctions between the regions

- H01L29/0692—Surface layout

- H01L29/0696—Surface layout of cellular field-effect devices, e.g. multicellular DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/02—Semiconductor bodies ; Multistep manufacturing processes therefor

- H01L29/06—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions

- H01L29/10—Semiconductor bodies ; Multistep manufacturing processes therefor characterised by their shape; characterised by the shapes, relative sizes, or dispositions of the semiconductor regions ; characterised by the concentration or distribution of impurities within semiconductor regions with semiconductor regions connected to an electrode not carrying current to be rectified, amplified or switched and such electrode being part of a semiconductor device which comprises three or more electrodes

- H01L29/1095—Body region, i.e. base region, of DMOS transistors or IGBTs

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/66007—Multistep manufacturing processes

- H01L29/66075—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials

- H01L29/66227—Multistep manufacturing processes of devices having semiconductor bodies comprising group 14 or group 13/15 materials the devices being controllable only by the electric current supplied or the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched, e.g. three-terminal devices

- H01L29/66234—Bipolar junction transistors [BJT]

- H01L29/66325—Bipolar junction transistors [BJT] controlled by field-effect, e.g. insulated gate bipolar transistors [IGBT]

- H01L29/66333—Vertical insulated gate bipolar transistors

- H01L29/66348—Vertical insulated gate bipolar transistors with a recessed gate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/72—Transistor-type devices, i.e. able to continuously respond to applied control signals

- H01L29/739—Transistor-type devices, i.e. able to continuously respond to applied control signals controlled by field-effect, e.g. bipolar static induction transistors [BSIT]

- H01L29/7393—Insulated gate bipolar mode transistors, i.e. IGBT; IGT; COMFET

- H01L29/7395—Vertical transistors, e.g. vertical IGBT

- H01L29/7396—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions

- H01L29/7397—Vertical transistors, e.g. vertical IGBT with a non planar surface, e.g. with a non planar gate or with a trench or recess or pillar in the surface of the emitter, base or collector region for improving current density or short circuiting the emitter and base regions and a gate structure lying on a slanted or vertical surface or formed in a groove, e.g. trench gate IGBT

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/40—Electrodes ; Multistep manufacturing processes therefor

- H01L29/402—Field plates

- H01L29/407—Recessed field plates, e.g. trench field plates, buried field plates

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/70—Bipolar devices

- H01L29/74—Thyristor-type devices, e.g. having four-zone regenerative action

- H01L29/7404—Thyristor-type devices, e.g. having four-zone regenerative action structurally associated with at least one other device

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Physics & Mathematics (AREA)

- Ceramic Engineering (AREA)

- Computer Hardware Design (AREA)

- Manufacturing & Machinery (AREA)

- Thyristors (AREA)

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

第1及び第2の導電型の内の少なくとも1つのカソード領域がその中に配されていて、導電コンタクトによって相互に接続されている、第1の導電型のベース領域、

第2導電型の第1ウエル領域、

第1導電型の第2ウエル領域、

第2導電型のドリフト領域、

第1導電型のアノード領域、及び

アノードコンタクト、

を含む少なくとも1つのセルを有し、

それぞれのセルが第1ウエル領域内に配され、第1ウエル領域が第2ウエル領域内に配されている、

半導体素子が提供され、

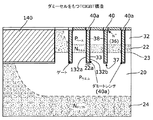

素子は、縦方向で第2ウエル領域及びドリフト領域と交差し、横方向でベース領域及び第1ウエル領域と交差する、細長トレンチを有し、

絶縁膜がトレンチの内表面を実質的に覆うように設けられ、

ゲートがトレンチを実質的に埋めるように絶縁膜上に設けられ、

素子は、素子の動作中に、ベース領域と第1ウエル領域の間の接合における空乏領域が第1ウエル領域と第2ウエル領域の間の接合まで延びることができ、よって第1ウエル領域の電位をアノードコンタクトの電位のいかなる上昇からも実質的に絶縁するように構成される。

第2導電型の半導体層内に第2ウエル領域を、残余半導体層がドリフト領域を形成するように、形成する工程、

第2ウエル領域内に第1ウエル領域を形成する工程、

第1ウエル領域内にベース領域を形成する工程、及び

カソード領域を形成する工程、

を含む方法も提供し、方法はさらに、

細長トレンチを、縦方向で第2ウエル領域及びドリフト領域と交差し、横方向でベース領域及び第1ウエル領域と交差するように、形成する工程、

を含む。

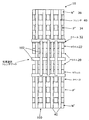

複数の、請求項1に記載の半導体素子を一枚の半導体基板上に形成する工程、素子は1つ以上の実質的に平行な列をなして配置される、及び

それぞれのトレンチが縦方向で第2ウエル領域及びドリフト領域と交差し、横方向で少なくとも1つの半導体素子のベース領域及び第1ウエル領域と交差するように、半導体素子の1つ以上の列に実質的に直交して通る、実質的に平行な列をなす、複数本の細長トレンチを形成する工程、

を含む。

20b P領域

22 Nウエル

23 Pウエル/Nウエル接合

24 Nドリフト領域

26 表面

32 Pベース

33 ゲート酸化物

34 P+領域

36 N+カソード領域

37 カソードコンタクト

38 多結晶シリコンゲート

40,40a,102 トレンチ

100 カソードセルブロック

132a,132b チャネル領域

140 MOSFETゲート

200 n型半導体基板

220 Pウエル層

222 Nウエル層

232 Pベース層

234 P+層

236 カソード層

240 トレンチ

242 ゲート酸化膜

244 ゲート電極

300 ダミー領域

Claims (14)

- 半導体素子であって、

第1導電型及び第2導電型の少なくとも1つのカソード領域が配された第1導電型のベース領域、

第2導電型の第1ウエル領域、

第1導電型の第2ウエル領域、

第2導電型のドリフト領域、

第1導電型のアノード領域、及び

アノードコンタクト、

を含む複数のセルであって、該複数のセルが導電コンタクトにより相互に接続されているもの、を有し、

前記セルのそれぞれが前記第1ウエル領域内に配され、前記第1ウエル領域が前記第2ウエル領域内に配されている、

半導体素子において、

前記素子が、縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域及び前記第1および第2ウエル領域と交差する、細長トレンチであって、前記第2ウエル領域の全厚の一部に亘って伸びている、細長トレンチを有し、

絶縁膜が前記トレンチの内表面を実質的に覆うように設けられ、

第1ゲートが前記トレンチを実質的に埋めるように前記絶縁膜上に形成され、

前記素子が、前記素子の動作中に、前記ベース領域と前記第1ウエル領域の間の接合における空乏領域が前記第1ウエル領域と前記第2ウエル領域の間の接合まで延びることができ、よって前記第1ウエル領域の電位を前記アノードコンタクトの電位のいかなる上昇からも実質的に絶縁するように構成され、

前記複数のセルの少なくとも一部のセルが作動し、前記複数のそれ以外のセルがダミーセルとして不作動であるように構成されている、

ことを特徴とする半導体素子。 - 請求項1に記載の半導体素子を作製する方法において、

第2導電型の半導体層内に前記第2ウエル領域を、残余半導体層が前記ドリフト領域を形成するように、形成する工程、

前記第2ウエル領域内に前記第1ウエル領域を形成する工程、

前記第1ウエル領域内に前記ベース領域を形成する工程、及び

前記カソード領域を形成する工程、

を含み、

前記方法がさらに、細長トレンチを、前記トレンチが縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域及び前記第1ウエル領域と交差するように、形成する工程を含み、

前記方法がさらに、半導体基板上に請求項1に記載の半導体素子を複数作製する工程であって、該半導体素子の一部は作動するように、それ以外の半導体素子はダミーセルとして作動しないように構成する工程を含む、

ことを特徴とする方法。 - 前記トレンチの各々が前記カソード領域の各々の形成に先立って形成されることを特徴とする請求項2に記載の方法。

- 半導体基板上に、複数の、請求項1に記載の半導体素子を形成する工程であって、その際、前記素子は1つ以上の実質的に平行な列をなして配置されるものである、工程、及び

1つまたは複数の前記半導体素子列に実質的に直交して通る、実質的に平行な列をなす、複数本の細長トレンチを、前記トレンチのそれぞれが縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で少なくとも1つの半導体素子の前記ベース領域及び前記第1ウエル領域と交差するように、形成する工程、

を含むことを特徴とする請求項2に記載の方法。 - 少なくとも1本のトレンチが、横方向で、前記半導体素子のそれぞれの前記第1ウエル領域及び前記第2ウエル領域と交差することを特徴とする請求項2に記載の方法。

- 前記少なくとも1本のトレンチが前記第2ウエル領域の全厚を貫通しないことを特徴とする請求項5に記載の方法。

- 前記少なくとも1本のトレンチが横方向で前記第2ウエル領域の全厚を貫通して前記ドリフト領域に延び込むことを特徴とする請求項5に記載の方法。

- 少なくとも1本のトレンチの前記内表面上に絶縁層を形成する工程及び前記トレンチのそれぞれを実質的に埋めるように構成されたゲートを形成する工程をさらに含むことを特徴とする請求項2に記載の方法。

- 少なくとも1つの前記素子列の前記素子のそれぞれが作動するように構成されることを特徴とする請求項4に記載の方法。

- 一つおきの前記素子列の前記素子のそれぞれが作動するように構成され、残余素子列の前記素子がダミーセルと指定されることを特徴とする請求項4に記載の方法。

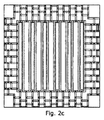

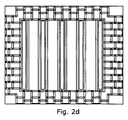

- 半導体構造において、実質的に平行な素子列をなして配置された、複数の、請求項1に記載の半導体素子を含み、前記半導体素子列に実質的に直交する、実質的に平行な列をなして配置された複数本のトレンチを有し、前記トレンチのそれぞれが、前記素子列のそれぞれの前記素子の、縦方向で前記第2ウエル領域及び前記ドリフト領域と交差し、横方向で前記ベース領域、前記第1ウエル領域及び前記第2領域と交差し、前記トレンチの少なくとも1本の前記内表面を実質的に覆うように絶縁膜が設けられ、前記少なくとも1本のトレンチを実質的に埋めるようにゲートが前記絶縁膜上に形成されており、前記素子の少なくとも一部が作動し、それ以外の前記素子がダミーセルとして作動しないように構成されていること、特徴とする半導体構造。

- 一つおきの前記素子列の前記素子のそれぞれが作動するように構成され、残余素子列の前記素子がダミーセルと指定されることを特徴とする請求項11に記載の半導体構造。

- 複数の前記セル及び/または前記素子が接続領域によって相互に接続されてクラスターをなしていることを特徴とする請求項11に記載の半導体構造。

- 前記接続領域が1本以上のトレンチを含むことを特徴とする請求項13に記載の半導体構造。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| GBGB1313126.3A GB201313126D0 (en) | 2013-07-23 | 2013-07-23 | MOS-Bipolar Device |

| GB1313126.3 | 2013-07-23 | ||

| GBGB1314474.6A GB201314474D0 (en) | 2013-07-23 | 2013-08-13 | MOS-Bipolar device |

| GB1314474.6 | 2013-08-13 | ||

| PCT/GB2014/052013 WO2015011440A1 (en) | 2013-07-23 | 2014-07-02 | Mos-bipolar device |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016527722A JP2016527722A (ja) | 2016-09-08 |

| JP2016527722A5 JP2016527722A5 (ja) | 2017-08-24 |

| JP6495272B2 true JP6495272B2 (ja) | 2019-04-03 |

Family

ID=49119141

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2016528598A Active JP6495272B2 (ja) | 2013-07-23 | 2014-07-02 | Mos−バイポーラ素子 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US10170605B2 (ja) |

| EP (1) | EP3025373B1 (ja) |

| JP (1) | JP6495272B2 (ja) |

| KR (1) | KR102173473B1 (ja) |

| CN (1) | CN105706241B (ja) |

| AU (1) | AU2014294820B2 (ja) |

| CA (1) | CA2918848A1 (ja) |

| ES (1) | ES2942334T3 (ja) |

| GB (3) | GB201313126D0 (ja) |

| WO (1) | WO2015011440A1 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102016112721B4 (de) * | 2016-07-12 | 2022-02-03 | Infineon Technologies Ag | n-Kanal-Leistungshalbleitervorrichtung mit p-Schicht im Driftvolumen |

| DE102016117264B4 (de) | 2016-09-14 | 2020-10-08 | Infineon Technologies Ag | Leistungshalbleiterbauelement mit Steuerbarkeit von dU/dt |

| DE102017107174B4 (de) | 2017-04-04 | 2020-10-08 | Infineon Technologies Ag | IGBT mit dV/dt-Steuerbarkeit und Verfahren zum Verarbeiten eines IGBT |

| DE102017124871B4 (de) | 2017-10-24 | 2021-06-17 | Infineon Technologies Ag | Leistungshalbleiter-Vorrichtung und Verfahren zum Herstellen einer Leistungshalbleiter-Vorrichtung |

| DE102017124872B4 (de) | 2017-10-24 | 2021-02-18 | Infineon Technologies Ag | Verfahren zur Herstellung eines IGBT mit dV/dt-Steuerbarkeit |

| GB2606383A (en) | 2021-05-06 | 2022-11-09 | Eco Semiconductors Ltd | A semiconductor device |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4761011B2 (ja) * | 1999-05-26 | 2011-08-31 | 株式会社豊田中央研究所 | サイリスタを有する半導体装置及びその製造方法 |

| GB9921068D0 (en) | 1999-09-08 | 1999-11-10 | Univ Montfort | Bipolar mosfet device |

| JP4028333B2 (ja) * | 2002-09-02 | 2007-12-26 | 株式会社東芝 | 半導体装置 |

| JP4130356B2 (ja) | 2002-12-20 | 2008-08-06 | 株式会社東芝 | 半導体装置 |

| JP5984282B2 (ja) | 2006-04-27 | 2016-09-06 | 富士電機株式会社 | 縦型トレンチ型絶縁ゲートmos半導体装置 |

| US7968940B2 (en) * | 2007-07-05 | 2011-06-28 | Anpec Electronics Corporation | Insulated gate bipolar transistor device comprising a depletion-mode MOSFET |

| US8716746B2 (en) * | 2010-08-17 | 2014-05-06 | Denso Corporation | Semiconductor device |

| JP5634318B2 (ja) * | 2011-04-19 | 2014-12-03 | 三菱電機株式会社 | 半導体装置 |

| US8564047B2 (en) | 2011-09-27 | 2013-10-22 | Force Mos Technology Co., Ltd. | Semiconductor power devices integrated with a trenched clamp diode |

-

2013

- 2013-07-23 GB GBGB1313126.3A patent/GB201313126D0/en not_active Ceased

- 2013-08-13 GB GBGB1314474.6A patent/GB201314474D0/en not_active Ceased

- 2013-08-13 GB GBGB1314475.3A patent/GB201314475D0/en active Pending

-

2014

- 2014-07-02 KR KR1020167004755A patent/KR102173473B1/ko active IP Right Grant

- 2014-07-02 CN CN201480042128.2A patent/CN105706241B/zh active Active

- 2014-07-02 WO PCT/GB2014/052013 patent/WO2015011440A1/en active Application Filing

- 2014-07-02 CA CA2918848A patent/CA2918848A1/en not_active Abandoned

- 2014-07-02 JP JP2016528598A patent/JP6495272B2/ja active Active

- 2014-07-02 AU AU2014294820A patent/AU2014294820B2/en active Active

- 2014-07-02 EP EP14749944.6A patent/EP3025373B1/en active Active

- 2014-07-02 US US14/906,654 patent/US10170605B2/en active Active

- 2014-07-02 ES ES14749944T patent/ES2942334T3/es active Active

Also Published As

| Publication number | Publication date |

|---|---|

| GB201314474D0 (en) | 2013-09-25 |

| EP3025373A1 (en) | 2016-06-01 |

| GB201314475D0 (en) | 2013-09-25 |

| WO2015011440A1 (en) | 2015-01-29 |

| US20160155831A1 (en) | 2016-06-02 |

| KR20160035029A (ko) | 2016-03-30 |

| AU2014294820A1 (en) | 2016-02-11 |

| JP2016527722A (ja) | 2016-09-08 |

| GB201313126D0 (en) | 2013-09-04 |

| AU2014294820B2 (en) | 2018-04-05 |

| ES2942334T3 (es) | 2023-05-31 |

| CN105706241B (zh) | 2019-12-31 |

| US10170605B2 (en) | 2019-01-01 |

| KR102173473B1 (ko) | 2020-11-03 |

| CN105706241A (zh) | 2016-06-22 |

| CA2918848A1 (en) | 2015-01-29 |

| EP3025373B1 (en) | 2022-12-21 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US9576841B2 (en) | Semiconductor device and manufacturing method | |

| JP6021908B2 (ja) | 絶縁ゲート型バイポーラトランジスタ | |

| JP6369173B2 (ja) | 縦型半導体装置およびその製造方法 | |

| JP6495272B2 (ja) | Mos−バイポーラ素子 | |

| US9023692B2 (en) | Semiconductor device and semiconductor device manufacturing method | |

| JP5787853B2 (ja) | 電力用半導体装置 | |

| KR101840903B1 (ko) | 절연 게이트 바이폴라 트랜지스터 | |

| US20130248882A1 (en) | Semiconductor device | |

| JP2009043966A (ja) | 半導体装置及びその製造方法 | |

| JP5833277B1 (ja) | 半導体装置 | |

| US6818940B2 (en) | Insulated gate bipolar transistor having trench gates of rectangular upper surfaces with different widths | |

| CN111886680B (zh) | 碳化硅半导体装置及其制造方法 | |

| JP7403401B2 (ja) | 半導体装置 | |

| KR101550798B1 (ko) | 래치업 억제구조를 가지는 전력용 반도체 장치 및 그 제조방법 | |

| JP2003258253A (ja) | 絶縁ゲート型バイポーラトランジスタ | |

| US9245986B2 (en) | Power semiconductor device and method of manufacturing the same | |

| CN116741828A (zh) | 沟渠式栅极晶体管组件 | |

| JP7486399B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| KR101949519B1 (ko) | 전력 반도체 소자 및 그 제조방법 | |

| KR102159418B1 (ko) | 슈퍼 정션 mosfet 및 그 제조 방법 | |

| GB2606383A (en) | A semiconductor device | |

| CN113140634A (zh) | 一种半导体器件及其制造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170629 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170629 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180320 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20180620 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20180820 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180920 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20190206 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20190306 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6495272 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |