JP6347744B2 - 積層半導体構造における縦方向の電気接続の形成方法 - Google Patents

積層半導体構造における縦方向の電気接続の形成方法 Download PDFInfo

- Publication number

- JP6347744B2 JP6347744B2 JP2014511848A JP2014511848A JP6347744B2 JP 6347744 B2 JP6347744 B2 JP 6347744B2 JP 2014511848 A JP2014511848 A JP 2014511848A JP 2014511848 A JP2014511848 A JP 2014511848A JP 6347744 B2 JP6347744 B2 JP 6347744B2

- Authority

- JP

- Japan

- Prior art keywords

- less

- copper

- insulating layer

- support substrate

- semiconductor structure

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 112

- 239000004065 semiconductor Substances 0.000 title claims description 72

- 239000000758 substrate Substances 0.000 claims description 66

- RYGMFSIKBFXOCR-UHFFFAOYSA-N Copper Chemical compound [Cu] RYGMFSIKBFXOCR-UHFFFAOYSA-N 0.000 claims description 64

- 239000010949 copper Substances 0.000 claims description 64

- 229910052802 copper Inorganic materials 0.000 claims description 63

- 239000000243 solution Substances 0.000 claims description 45

- 238000005530 etching Methods 0.000 claims description 42

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 claims description 33

- 238000001039 wet etching Methods 0.000 claims description 29

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 claims description 27

- 239000000463 material Substances 0.000 claims description 24

- PEDCQBHIVMGVHV-UHFFFAOYSA-N Glycerine Chemical compound OCC(O)CO PEDCQBHIVMGVHV-UHFFFAOYSA-N 0.000 claims description 22

- 229910052751 metal Inorganic materials 0.000 claims description 19

- 239000002184 metal Substances 0.000 claims description 19

- 238000009792 diffusion process Methods 0.000 claims description 18

- 238000000576 coating method Methods 0.000 claims description 17

- 230000015572 biosynthetic process Effects 0.000 claims description 16

- 239000011248 coating agent Substances 0.000 claims description 16

- 239000002904 solvent Substances 0.000 claims description 14

- KDLHZDBZIXYQEI-UHFFFAOYSA-N Palladium Chemical compound [Pd] KDLHZDBZIXYQEI-UHFFFAOYSA-N 0.000 claims description 12

- 239000012954 diazonium Substances 0.000 claims description 12

- 150000001989 diazonium salts Chemical class 0.000 claims description 12

- 239000003586 protic polar solvent Substances 0.000 claims description 12

- 239000008139 complexing agent Substances 0.000 claims description 11

- 229910001431 copper ion Inorganic materials 0.000 claims description 11

- 238000000151 deposition Methods 0.000 claims description 11

- 235000011187 glycerol Nutrition 0.000 claims description 11

- 239000000203 mixture Substances 0.000 claims description 11

- 238000005553 drilling Methods 0.000 claims description 9

- PIICEJLVQHRZGT-UHFFFAOYSA-N Ethylenediamine Chemical compound NCCN PIICEJLVQHRZGT-UHFFFAOYSA-N 0.000 claims description 8

- 239000011230 binding agent Substances 0.000 claims description 8

- 150000001450 anions Chemical class 0.000 claims description 7

- PXHVJJICTQNCMI-UHFFFAOYSA-N Nickel Chemical compound [Ni] PXHVJJICTQNCMI-UHFFFAOYSA-N 0.000 claims description 6

- 239000000178 monomer Substances 0.000 claims description 6

- 229910052763 palladium Inorganic materials 0.000 claims description 6

- JPVYNHNXODAKFH-UHFFFAOYSA-N Cu2+ Chemical compound [Cu+2] JPVYNHNXODAKFH-UHFFFAOYSA-N 0.000 claims description 5

- 239000012190 activator Substances 0.000 claims description 5

- 125000003118 aryl group Chemical group 0.000 claims description 5

- 238000001312 dry etching Methods 0.000 claims description 5

- 230000001588 bifunctional effect Effects 0.000 claims description 4

- 150000001282 organosilanes Chemical class 0.000 claims description 4

- 229910052760 oxygen Inorganic materials 0.000 claims description 4

- 150000002940 palladium Chemical class 0.000 claims description 4

- 150000003839 salts Chemical class 0.000 claims description 4

- 239000002253 acid Substances 0.000 claims description 3

- 150000007513 acids Chemical class 0.000 claims description 3

- 239000013543 active substance Substances 0.000 claims description 3

- 125000003277 amino group Chemical group 0.000 claims description 3

- BFNBIHQBYMNNAN-UHFFFAOYSA-N ammonium sulfate Chemical compound N.N.OS(O)(=O)=O BFNBIHQBYMNNAN-UHFFFAOYSA-N 0.000 claims description 3

- 229910052921 ammonium sulfate Inorganic materials 0.000 claims description 3

- 239000001166 ammonium sulphate Substances 0.000 claims description 3

- 235000011130 ammonium sulphate Nutrition 0.000 claims description 3

- 239000007853 buffer solution Substances 0.000 claims description 3

- 239000003638 chemical reducing agent Substances 0.000 claims description 3

- 229910017052 cobalt Inorganic materials 0.000 claims description 3

- 239000010941 cobalt Substances 0.000 claims description 3

- GUTLYIVDDKVIGB-UHFFFAOYSA-N cobalt atom Chemical compound [Co] GUTLYIVDDKVIGB-UHFFFAOYSA-N 0.000 claims description 3

- 239000003446 ligand Substances 0.000 claims description 3

- 229910001092 metal group alloy Inorganic materials 0.000 claims description 3

- 239000002105 nanoparticle Substances 0.000 claims description 3

- 229910052759 nickel Inorganic materials 0.000 claims description 3

- 239000002245 particle Substances 0.000 claims description 3

- 238000001020 plasma etching Methods 0.000 claims description 3

- 229920000768 polyamine Polymers 0.000 claims description 3

- 125000006850 spacer group Chemical group 0.000 claims description 3

- UVZICZIVKIMRNE-UHFFFAOYSA-N thiodiacetic acid Chemical compound OC(=O)CSCC(O)=O UVZICZIVKIMRNE-UHFFFAOYSA-N 0.000 claims description 3

- 238000009736 wetting Methods 0.000 claims description 3

- 239000012528 membrane Substances 0.000 claims description 2

- 239000003381 stabilizer Substances 0.000 claims description 2

- 230000008021 deposition Effects 0.000 claims 1

- 229910052710 silicon Inorganic materials 0.000 description 19

- 239000010703 silicon Substances 0.000 description 19

- 230000008569 process Effects 0.000 description 18

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 16

- 241000724291 Tobacco streak virus Species 0.000 description 16

- 235000012431 wafers Nutrition 0.000 description 13

- 239000004020 conductor Substances 0.000 description 11

- 239000008367 deionised water Substances 0.000 description 11

- ZMXDDKWLCZADIW-UHFFFAOYSA-N N,N-Dimethylformamide Chemical compound CN(C)C=O ZMXDDKWLCZADIW-UHFFFAOYSA-N 0.000 description 9

- 230000010354 integration Effects 0.000 description 8

- 229910021641 deionized water Inorganic materials 0.000 description 7

- 238000004519 manufacturing process Methods 0.000 description 7

- IAZDPXIOMUYVGZ-UHFFFAOYSA-N Dimethylsulphoxide Chemical compound CS(C)=O IAZDPXIOMUYVGZ-UHFFFAOYSA-N 0.000 description 6

- LYCAIKOWRPUZTN-UHFFFAOYSA-N Ethylene glycol Chemical compound OCCO LYCAIKOWRPUZTN-UHFFFAOYSA-N 0.000 description 6

- 229910004298 SiO 2 Inorganic materials 0.000 description 6

- 239000012153 distilled water Substances 0.000 description 6

- 238000013459 approach Methods 0.000 description 5

- 238000001465 metallisation Methods 0.000 description 5

- 239000000126 substance Substances 0.000 description 5

- SECXISVLQFMRJM-UHFFFAOYSA-N N-Methylpyrrolidone Chemical group CN1CCCC1=O SECXISVLQFMRJM-UHFFFAOYSA-N 0.000 description 4

- GLUUGHFHXGJENI-UHFFFAOYSA-N Piperazine Chemical compound C1CNCCN1 GLUUGHFHXGJENI-UHFFFAOYSA-N 0.000 description 4

- 230000006870 function Effects 0.000 description 4

- MUJIDPITZJWBSW-UHFFFAOYSA-N palladium(2+) Chemical compound [Pd+2] MUJIDPITZJWBSW-UHFFFAOYSA-N 0.000 description 4

- IMNIMPAHZVJRPE-UHFFFAOYSA-N triethylenediamine Chemical compound C1CN2CCN1CC2 IMNIMPAHZVJRPE-UHFFFAOYSA-N 0.000 description 4

- QTBSBXVTEAMEQO-UHFFFAOYSA-N Acetic acid Chemical compound CC(O)=O QTBSBXVTEAMEQO-UHFFFAOYSA-N 0.000 description 3

- CSCPPACGZOOCGX-UHFFFAOYSA-N Acetone Chemical compound CC(C)=O CSCPPACGZOOCGX-UHFFFAOYSA-N 0.000 description 3

- RPNUMPOLZDHAAY-UHFFFAOYSA-N Diethylenetriamine Chemical compound NCCNCCN RPNUMPOLZDHAAY-UHFFFAOYSA-N 0.000 description 3

- YXFVVABEGXRONW-UHFFFAOYSA-N Toluene Chemical compound CC1=CC=CC=C1 YXFVVABEGXRONW-UHFFFAOYSA-N 0.000 description 3

- 150000001875 compounds Chemical class 0.000 description 3

- 238000004070 electrodeposition Methods 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 150000005846 sugar alcohols Polymers 0.000 description 3

- WYTZZXDRDKSJID-UHFFFAOYSA-N (3-aminopropyl)triethoxysilane Chemical compound CCO[Si](OCC)(OCC)CCCN WYTZZXDRDKSJID-UHFFFAOYSA-N 0.000 description 2

- 125000003903 2-propenyl group Chemical group [H]C([*])([H])C([H])=C([H])[H] 0.000 description 2

- KFDVPJUYSDEJTH-UHFFFAOYSA-N 4-ethenylpyridine Chemical compound C=CC1=CC=NC=C1 KFDVPJUYSDEJTH-UHFFFAOYSA-N 0.000 description 2

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical group [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 2

- VEXZGXHMUGYJMC-UHFFFAOYSA-N Hydrochloric acid Chemical compound Cl VEXZGXHMUGYJMC-UHFFFAOYSA-N 0.000 description 2

- 229910052581 Si3N4 Inorganic materials 0.000 description 2

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- QAOWNCQODCNURD-UHFFFAOYSA-N Sulfuric acid Chemical compound OS(O)(=O)=O QAOWNCQODCNURD-UHFFFAOYSA-N 0.000 description 2

- 150000001298 alcohols Chemical class 0.000 description 2

- 229910052782 aluminium Inorganic materials 0.000 description 2

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 2

- 125000004432 carbon atom Chemical group C* 0.000 description 2

- YCIMNLLNPGFGHC-UHFFFAOYSA-N catechol Chemical compound OC1=CC=CC=C1O YCIMNLLNPGFGHC-UHFFFAOYSA-N 0.000 description 2

- 238000005229 chemical vapour deposition Methods 0.000 description 2

- 125000003963 dichloro group Chemical group Cl* 0.000 description 2

- 238000005516 engineering process Methods 0.000 description 2

- 125000001072 heteroaryl group Chemical group 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- GKQPCPXONLDCMU-CCEZHUSRSA-N lacidipine Chemical compound CCOC(=O)C1=C(C)NC(C)=C(C(=O)OCC)C1C1=CC=CC=C1\C=C\C(=O)OC(C)(C)C GKQPCPXONLDCMU-CCEZHUSRSA-N 0.000 description 2

- 239000007788 liquid Substances 0.000 description 2

- BDAGIHXWWSANSR-UHFFFAOYSA-N methanoic acid Natural products OC=O BDAGIHXWWSANSR-UHFFFAOYSA-N 0.000 description 2

- 238000004377 microelectronic Methods 0.000 description 2

- 230000005012 migration Effects 0.000 description 2

- 238000013508 migration Methods 0.000 description 2

- 238000012545 processing Methods 0.000 description 2

- 150000003254 radicals Chemical class 0.000 description 2

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 2

- 229910052814 silicon oxide Inorganic materials 0.000 description 2

- 238000012360 testing method Methods 0.000 description 2

- RYHBNJHYFVUHQT-UHFFFAOYSA-N 1,4-Dioxane Chemical compound C1COCCO1 RYHBNJHYFVUHQT-UHFFFAOYSA-N 0.000 description 1

- FXRJDJNKKJZYNN-UHFFFAOYSA-N 1-(2-hydroxyethoxy)butan-2-ol Chemical compound CCC(O)COCCO FXRJDJNKKJZYNN-UHFFFAOYSA-N 0.000 description 1

- JDSQBDGCMUXRBM-UHFFFAOYSA-N 2-[2-(2-butoxypropoxy)propoxy]propan-1-ol Chemical compound CCCCOC(C)COC(C)COC(C)CO JDSQBDGCMUXRBM-UHFFFAOYSA-N 0.000 description 1

- GFIWSSUBVYLTRF-UHFFFAOYSA-N 2-[2-(2-hydroxyethylamino)ethylamino]ethanol Chemical compound OCCNCCNCCO GFIWSSUBVYLTRF-UHFFFAOYSA-N 0.000 description 1

- SJECZPVISLOESU-UHFFFAOYSA-N 3-trimethoxysilylpropan-1-amine Chemical compound CO[Si](OC)(OC)CCCN SJECZPVISLOESU-UHFFFAOYSA-N 0.000 description 1

- OSWFIVFLDKOXQC-UHFFFAOYSA-N 4-(3-methoxyphenyl)aniline Chemical compound COC1=CC=CC(C=2C=CC(N)=CC=2)=C1 OSWFIVFLDKOXQC-UHFFFAOYSA-N 0.000 description 1

- ICMFHHGKLRTCBM-UHFFFAOYSA-N 4-nitrobenzenediazonium Chemical class [O-][N+](=O)C1=CC=C([N+]#N)C=C1 ICMFHHGKLRTCBM-UHFFFAOYSA-N 0.000 description 1

- DDFHBQSCUXNBSA-UHFFFAOYSA-N 5-(5-carboxythiophen-2-yl)thiophene-2-carboxylic acid Chemical compound S1C(C(=O)O)=CC=C1C1=CC=C(C(O)=O)S1 DDFHBQSCUXNBSA-UHFFFAOYSA-N 0.000 description 1

- 241000252506 Characiformes Species 0.000 description 1

- KRHYYFGTRYWZRS-UHFFFAOYSA-M Fluoride anion Chemical compound [F-] KRHYYFGTRYWZRS-UHFFFAOYSA-M 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 239000002202 Polyethylene glycol Substances 0.000 description 1

- 239000004372 Polyvinyl alcohol Substances 0.000 description 1

- BQCADISMDOOEFD-UHFFFAOYSA-N Silver Chemical compound [Ag] BQCADISMDOOEFD-UHFFFAOYSA-N 0.000 description 1

- 239000004809 Teflon Substances 0.000 description 1

- 229920006362 Teflon® Polymers 0.000 description 1

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 1

- NJSVDVPGINTNGX-UHFFFAOYSA-N [dimethoxy(propyl)silyl]oxymethanamine Chemical compound CCC[Si](OC)(OC)OCN NJSVDVPGINTNGX-UHFFFAOYSA-N 0.000 description 1

- 229910045601 alloy Inorganic materials 0.000 description 1

- 239000000956 alloy Substances 0.000 description 1

- 239000000010 aprotic solvent Substances 0.000 description 1

- 239000007864 aqueous solution Substances 0.000 description 1

- 238000000429 assembly Methods 0.000 description 1

- 230000000712 assembly Effects 0.000 description 1

- 239000012298 atmosphere Substances 0.000 description 1

- 125000004429 atom Chemical group 0.000 description 1

- 230000004888 barrier function Effects 0.000 description 1

- 239000002585 base Substances 0.000 description 1

- 239000003990 capacitor Substances 0.000 description 1

- 229910052799 carbon Inorganic materials 0.000 description 1

- 229910002091 carbon monoxide Inorganic materials 0.000 description 1

- 150000001735 carboxylic acids Chemical class 0.000 description 1

- 230000008859 change Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 238000004891 communication Methods 0.000 description 1

- 239000002131 composite material Substances 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- ARUVKPQLZAKDPS-UHFFFAOYSA-L copper(II) sulfate Chemical compound [Cu+2].[O-][S+2]([O-])([O-])[O-] ARUVKPQLZAKDPS-UHFFFAOYSA-L 0.000 description 1

- 229910000366 copper(II) sulfate Inorganic materials 0.000 description 1

- 230000008878 coupling Effects 0.000 description 1

- 238000010168 coupling process Methods 0.000 description 1

- 238000005859 coupling reaction Methods 0.000 description 1

- 238000002484 cyclic voltammetry Methods 0.000 description 1

- 230000007547 defect Effects 0.000 description 1

- 239000012895 dilution Substances 0.000 description 1

- 238000010790 dilution Methods 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000004870 electrical engineering Methods 0.000 description 1

- 238000010292 electrical insulation Methods 0.000 description 1

- 125000006575 electron-withdrawing group Chemical group 0.000 description 1

- 238000009713 electroplating Methods 0.000 description 1

- 150000002148 esters Chemical group 0.000 description 1

- RTZKZFJDLAIYFH-UHFFFAOYSA-N ether Substances CCOCC RTZKZFJDLAIYFH-UHFFFAOYSA-N 0.000 description 1

- 235000019253 formic acid Nutrition 0.000 description 1

- 229910052733 gallium Inorganic materials 0.000 description 1

- 238000000227 grinding Methods 0.000 description 1

- 229910052736 halogen Chemical group 0.000 description 1

- 150000002367 halogens Chemical group 0.000 description 1

- 125000005842 heteroatom Chemical group 0.000 description 1

- 229910052739 hydrogen Inorganic materials 0.000 description 1

- 229910000040 hydrogen fluoride Inorganic materials 0.000 description 1

- 230000002209 hydrophobic effect Effects 0.000 description 1

- 150000004679 hydroxides Chemical class 0.000 description 1

- 230000036039 immunity Effects 0.000 description 1

- 230000006698 induction Effects 0.000 description 1

- 239000003999 initiator Substances 0.000 description 1

- 239000011810 insulating material Substances 0.000 description 1

- 238000009413 insulation Methods 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 150000002576 ketones Chemical class 0.000 description 1

- 238000010297 mechanical methods and process Methods 0.000 description 1

- 230000005226 mechanical processes and functions Effects 0.000 description 1

- 238000000465 moulding Methods 0.000 description 1

- PHQOGHDTIVQXHL-UHFFFAOYSA-N n'-(3-trimethoxysilylpropyl)ethane-1,2-diamine Chemical compound CO[Si](OC)(OC)CCCNCCN PHQOGHDTIVQXHL-UHFFFAOYSA-N 0.000 description 1

- 230000035515 penetration Effects 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 229920001223 polyethylene glycol Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 229920001451 polypropylene glycol Polymers 0.000 description 1

- 229920002451 polyvinyl alcohol Polymers 0.000 description 1

- -1 resistors Substances 0.000 description 1

- 230000000284 resting effect Effects 0.000 description 1

- 150000003376 silicon Chemical class 0.000 description 1

- HBMJWWWQQXIZIP-UHFFFAOYSA-N silicon carbide Chemical compound [Si+]#[C-] HBMJWWWQQXIZIP-UHFFFAOYSA-N 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 125000001424 substituent group Chemical group 0.000 description 1

- 229910052717 sulfur Inorganic materials 0.000 description 1

- 229910052715 tantalum Inorganic materials 0.000 description 1

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 description 1

- MZLGASXMSKOWSE-UHFFFAOYSA-N tantalum nitride Chemical compound [Ta]#N MZLGASXMSKOWSE-UHFFFAOYSA-N 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76802—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing by forming openings in dielectrics

- H01L21/76816—Aspects relating to the layout of the pattern or to the size of vias or trenches

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02041—Cleaning

- H01L21/02057—Cleaning during device manufacture

- H01L21/0206—Cleaning during device manufacture during, before or after processing of insulating layers

- H01L21/02063—Cleaning during device manufacture during, before or after processing of insulating layers the processing being the formation of vias or contact holes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/28—Manufacture of electrodes on semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/268

- H01L21/283—Deposition of conductive or insulating materials for electrodes conducting electric current

- H01L21/288—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition

- H01L21/2885—Deposition of conductive or insulating materials for electrodes conducting electric current from a liquid, e.g. electrolytic deposition using an external electrical current, i.e. electro-deposition

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/31—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26 to form insulating layers thereon, e.g. for masking or by using photolithographic techniques; After treatment of these layers; Selection of materials for these layers

- H01L21/3105—After-treatment

- H01L21/311—Etching the insulating layers by chemical or physical means

- H01L21/31105—Etching inorganic layers

- H01L21/31111—Etching inorganic layers by chemical means

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76822—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc.

- H01L21/76823—Modification of the material of dielectric layers, e.g. grading, after-treatment to improve the stability of the layers, to increase their density etc. transforming an insulating layer into a conductive layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76831—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches, e.g. non-conductive sidewall liners

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76871—Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers

- H01L21/76874—Layers specifically deposited to enhance or enable the nucleation of further layers, i.e. seed layers for electroless plating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

- H01L21/76879—Filling of holes, grooves or trenches, e.g. vias, with conductive material by selective deposition of conductive material in the vias, e.g. selective C.V.D. on semiconductor material, plating

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76898—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics formed through a semiconductor substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/48—Arrangements for conducting electric current to or from the solid state body in operation, e.g. leads, terminal arrangements ; Selection of materials therefor

- H01L23/481—Internal lead connections, e.g. via connections, feedthrough structures

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/5226—Via connections in a multilevel interconnection structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/528—Geometry or layout of the interconnection structure

- H01L23/5283—Cross-sectional geometry

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L23/00—Details of semiconductor or other solid state devices

- H01L23/52—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames

- H01L23/522—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body

- H01L23/532—Arrangements for conducting electric current within the device in operation from one component to another, i.e. interconnections, e.g. wires, lead frames including external interconnections consisting of a multilayer structure of conductive and insulating layers inseparably formed on the semiconductor body characterised by the materials

- H01L23/53204—Conductive materials

- H01L23/53209—Conductive materials based on metals, e.g. alloys, metal silicides

- H01L23/53228—Conductive materials based on metals, e.g. alloys, metal silicides the principal metal being copper

- H01L23/53238—Additional layers associated with copper layers, e.g. adhesion, barrier, cladding layers

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/0001—Technical content checked by a classifier

- H01L2924/0002—Not covered by any one of groups H01L24/00, H01L24/00 and H01L2224/00

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/12—Passive devices, e.g. 2 terminal devices

- H01L2924/1204—Optical Diode

- H01L2924/12044—OLED

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Manufacturing & Machinery (AREA)

- Chemical & Material Sciences (AREA)

- Chemical Kinetics & Catalysis (AREA)

- General Chemical & Material Sciences (AREA)

- Inorganic Chemistry (AREA)

- Geometry (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Weting (AREA)

- Chemically Coating (AREA)

- Electroplating Methods And Accessories (AREA)

- Electrodes Of Semiconductors (AREA)

Description

。

− 絶縁誘電層又はライナーの成膜;

− 銅の移動又は拡散を防ぐための隔膜層の成膜;

− 用いた隔膜材料の導電性が非常に低い場合は、銅の電着の促進のため必要に応じてシード層の成膜;

− 銅の電着によるビアの充填;及び

− 化学機械研磨によるウェーハー表面からの余分な銅及び隔膜の除去

− 積層された半導体構造を得る、かかる積層半導体構造は

・第一表面及び背面を有する支持基板

・支持基板の第一表面上に積層された少なくとも一層の絶縁層;主に異なる材料が積み重なった絶縁層が用いられる;及び

・絶縁層内に形成される少なくとも一個の導電パッド;並びに

− 支持基板の背面側からビアを穿孔する。

− 第一表面及び第二表面(24)を含む支持基板、

− 前記支持基板の前記第一表面上に被覆される絶縁層、及び

− 前記絶縁層内に形成される一以上のデバイス構造;並びに

− 前記支持基板(20)の第二表面から前記デバイス構造までビアを穿孔し、デバイス構造を露出する工程;

*湿式エッチングはフッ化水素酸及び任意でグリセリンを含有する溶液で行い;

*前記エッチング液は0.5体積%以上、50体積%以下の、好ましくは1.35体積%のフッ化水素酸を含有し;

*前記エッチング液はさらに0.5体積%以上、50体積%以下の、好ましくは1.35体積%のグリセリンを含有し;

*上記方法はさらに湿式エッチング工程(320)の前に、前記積層半導体構造を水中に入れる予備湿潤化工程を備え;

*湿式エッチング工程の後に、前記積層半導体構造を水ですすぐ、すすぎ工程;

*上記方法はさらに湿式エッチング工程の後に、前記積層半導体構造を吸引下に置く吸引工程を備え;

*前記積層半導体構造を前記吸引工程において水中に入れる;

*上記方法はさらに湿式エッチング工程の前に、支持基板を薄くする除去工程を備え;

*上記方法はさらに湿式エッチング工程の前に、第二表面から少なくとも絶縁層まで予備ビアを形成する予備穿孔工程を備え;かつ

*前記予備ビアはドライエッチング、湿式エッチング又は反応性イオンエッチングで形成する。

− 前記縦方向の接続の表面を溶液に接触させることで、前記縦方向の接続を絶縁膜で湿式被覆(wet coating)する工程。

− プロトン性溶媒;

− 一以上のジアゾニウム塩;

− 一以上の、鎖状に重合可能な単量体であって前記プロトン性溶媒に溶解するもの;

− 一以上の、上記溶液のpHを7、好ましくは2.5より小さく調整することで前記ジアゾニウム塩を安定化させるのに十分な量の酸;及び

− R1及びR2は同一で、かつH;CH2CH2NH2;若しくはCH2CH2OHを表すものであり;若しくは

− R1はHを表し、かつR2はCH2CH2NH2を表すものであり;若しくは

− R2はCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;又は

− R2はCH2CH2NHCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;

− XはCl-;Br-;I-;H2O, NO3 -;CH3SO3 -;CF3SO3 -;CH3-Ph-SO3 -;CH3COO-からなる群から選ばれるリガンドを表す;

− R1及びR2は上記のとおり定義され、かつ

− Yは下記からなり、二価の負電荷を備える対イオンを表す:

・いずれもCl-;PF6 -;BF4 -;NO3 -;CH3SO3 -;CF3SO3 -;CH3C6H4SO3 -;CH3COO-からなる群から選ばれる2個の一価陰イオン;又は

・二価の陰イオン、好ましくはSO4 2-;

{NH2-(L)}3-n-Si(OR)n (V)

− LはCH2;CH2CH2;CH2CH2CH2-及びCH2CH2NHCH2CH2からなる群から選ばれるスペーサーであり;

− RはCH3,CH3CH2,CH3CH2CH2,(CH3)2CHからなる群から選ばれる基であり;かつ

− nは1,2又は3に等しい整数である。

− 一以上の溶媒;

− 濃度約14mM以上、約120mM以下の銅イオン;

− エチレンジアミン;

− 銅に対するエチレンジアミンのモル比は1.80以上、2.03以下;

− 上記組成のpHは6.6以上、7.5以下。

− 銅イオン、濃度45mM以上、1500mM以下の、好ましくは45mM以上、500mM以下の、より好ましくは100mM以上、300mM以下の銅イオン;

− 銅の錯化剤、2以上、4以下のアミノ基を有する芳香族ポリアミンを含む群の内の一以上の構成要素を備え、45mM以上、3000mM以下の、好ましくは45mM以上、1500mM以下の、より好ましくは300mM以上、900mM以下の濃度の銅の錯化剤;

− チオジグリコール酸、濃度1mg/L以上、500mg/L以下のチオジグリコール酸;

− 任意に、緩衝系、特に濃度0.1M以上、3M以下の硫酸アンモニウムを加えてもよい。

− 第一表面及び第二表面を有する支持基板、

− 前記支持基板の前記第一表面上に被覆される絶縁層、

− 前記絶縁層内に形成される一以上のデバイス構造;及び

− 前記支持基板の前記第二表面から前記デバイス構造まで達する、一以上の縦方向の接続、

*上記方式はさらに少なくとも、前記支持基板(30)の近傍にて縦方向の接続の壁を被覆する絶縁膜を備え、かかる絶縁層の厚みは均一であり、また、かかる絶縁層は特に上述の方法によって得られるものであり;

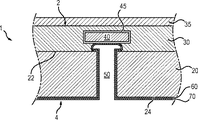

− 第一表面22及び第二表面24を有する支持基板20、

− 前記支持基板の前記第一表面上を被覆する絶縁層30、及び

− 前記絶縁層内に形成される一以上のデバイス構造40。

上記の場合、いかなる場合でもエッチング液が絶縁層30のみをエッチングするためマスクを必要としない。

− プロトン性溶媒;

− 一以上のジアゾニウム塩;

− 一以上の、鎖状に重合可能な単量体であって前記プロトン性溶媒に溶解するもの;

− 一以上の、上記溶液のpHを7、好ましくは2.5より小さく調整することで前記ジアゾニウム塩を安定化させるのに十分な量の酸;

R-N2 +,A- (I)

− Aは一価の陰イオンを表す。

− Rはアリル基を表す。

− 一以上のジアゾニウム塩;

− 一以上の、鎖状に重合可能な単量体であってプロトン性溶媒に溶解するもの;

− 一以上の、上記ジアゾニウム塩から遊離基の実体の生成を可能にする化学的な開始剤。

− R1及びR2は同一で、かつH;CH2CH2NH2;CH2CH2OHを表すものであり;若しくは

− R1はHを表し、かつR2はCH2CH2NH2を表すものであり;若しくは

− R2はCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;又は

− R2はCH2CH2NHCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;

− XはCl-;Br-;I-;H2O, NO3 -;CH3SO3 -;CF3SO3 -;CH3-Ph-SO3 -;CH3COO-からなる群から選ばれるリガンドを表す;

− R1及びR2は上記のとおり定義され、かつ

− Yは下記からなり、二価の負電荷を備える対イオンを表す:

・いずれもCl-;PF6 -;BF4 -;NO3 -;CH3SO3 -;CF3SO3 -;CH3C6H4SO3 -;CH3COO-からなる群から選ばれる2個の一価陰イオン;又は

・二価の陰イオン、好ましくはSO4 2-;

iii)

{NH2-(L)}3-n-Si(OR)n (V)

− LはCH2;CH2CH2;CH2CH2CH2-及びCH2CH2NHCH2CH2からなる群から選ばれるスペーサーであり;

− RはCH3,CH3CH2,CH3CH2CH2,(CH3)2CHからなる群から選ばれる基であり;かつ

− nは1,2又は3に等しい整数である。

− LはCH2CH2CH2-であり、RはCH3である(APTMS、(3−アミノプロピル)トリメトキシシラン);

− 若しくはLはCH2CH2CH2-であり、RはCH3である(APTES、(3−アミノプロピル)トリエトキシシラン);

− 又はLはCH2CH2NHCH2CH2であり、RはCH3である(DATMS又はDAMO、(3−(2−アミノエチルアミノ)プロピルトリメトキシシラン)である。

− R1及びR2は同一でかつCH2CH2OHであり、かつXはClであり、(N,N’−ビス(2−ヒドロキシエチル)エチレンジアミン)−(ジクロロ)パラジウム(II)と呼ばれる錯体;

− R1はHであり、R2はCH2CH2NH2であり、Yは2個のClであり、トランス−ビス(ジエチレントリアミン)パラジウム(II)と呼ばれる錯体;

− R1はHであり、R2はCH2CH2NH2であり、Yは2個のClであり、シス−ビス(ジエチレントリアミン)パラジウム(II)と呼ばれる錯体;

− 濃度約14mM以上、約120mM以下の銅イオン;

− エチレンジアミン;

− 銅に対するエチレンジアミンのモル比は1.80以上、2.03以下;

− 上記組成のpHは6.6以上、7.5以下。

− 銅イオン、濃度45mM以上、1500mM以下の、好ましくは45mM以上、500mM以下の、より好ましくは100mM以上、300mM以下の銅イオン;

− 銅の錯化剤、2以上、4以下のアミノ基を有する芳香族ポリアミンを含む群の内の一以上の構成要素を備え、45mM以上、3000mM以下の、好ましくは45mM以上、1500mM以下の、より好ましくは300mM以上、900mM以下の濃度の銅の錯化剤;

− チオジグリコール酸、濃度1mg/L以上、500mg/L以下のチオジグリコール酸;

− 任意に、緩衝系、特に濃度0.1M以上、3M以下の硫酸アンモニウムを加えてもよい。

シリコン基板上でエレクトログラフティングを実施するために以下からなるシステムを用いる:

○ 対になる電極として用いる炭素シート;

○ 安定した電源及び電気接続装置。

○ 0.01秒以上、1秒以下(例えば0.36秒)の、極性を有する時間T、この間、5V以上、20V以下の電位差を基板の表面に持たせる(例えば陰極の電位が−17V);及び

○ Tオフと呼ばれる、電位0の休止期間、0.01秒以上、1秒以下(例えば0.24秒)の持続時間。

Claims (20)

- 積層半導体構造において縦方向の電気接続を形成する方法であって、下記の工程を含み:

− 下記を備える積層半導体構造(1)を得る工程(100):

− 第一表面(22)及び第二表面(24)を含む支持基板(20)、

− 前記支持基板(20)の前記第一表面上(22)に被覆される絶縁層(30)、及び

− 前記絶縁層(30)内に形成される一以上のデバイス構造(40);並びに

− 前記支持基板(20)の第二表面から前記デバイス構造(40)までビア(50)を穿孔し(300)、デバイス構造(40)を露出するところ、前記絶縁層への穿孔(300)は少なくとも一部において湿式エッチング(320)によって行われる工程、

前記方法は、さらに前記縦方向のビア(50)の表面を溶液に接触させることで、前記縦方向のビア(50)を絶縁膜(60)で湿式被覆する工程(400)を含むことにより均一な絶縁膜(60)を得るところ、前記ビア(50)の湿式被覆は、選択的に前記支持基板(20)の近傍にある前記ビア(50)を被覆するのみであることを特徴とする方法。 - 湿式エッチング(320)は所定の時間行われ、

前記所定の時間は絶縁層(30)の材料、エッチング液及び穿孔すべき絶縁層(30)の厚さによって定まる、

請求項1に記載の方法。 - 湿式エッチング(320)はフッ化水素酸及び任意でグリセリンを含有する溶液で行う、

請求項1又は2に記載の方法。 - 前記エッチング液は0.5体積%以上、50体積%以下の、好ましくは1.35体積%のフッ化水素酸を含有する、

請求項3に記載の方法。 - 前記エッチング液はさらに0.5体積%以上、50体積%以下の、好ましくは1.35体積%のグリセリンを含有する、

請求項3又は4に記載の方法。 - さらに前記湿式エッチング工程(320)の前に、前記積層半導体構造(1)を水中に入れる予備湿潤化工程(322)をさらに備える、

請求項1〜5のいずれかに記載の方法。 - 前記湿式エッチング工程(320)の後に、前記積層半導体構造(1)を水ですすぐ、すすぎ工程(324)をさらに備える、

請求項1〜6のいずれかに記載の方法。 - 前記湿式エッチング工程(320)の後に、前記積層半導体構造(1)を吸引下に置く(328)吸引工程(326、328)を備える、

請求項1〜7のいずれかに記載の方法。 - 前記積層半導体構造(1)を前記吸引工程(326、328)において水中に入れる(326)、

請求項8に記載の方法。 - 前記湿式エッチング工程(320)の前に、前記支持基板(20)を薄くする除去工程(310)をさらに備える、

請求項1〜9のいずれかに記載の方法。 - 前記湿式エッチング工程(320)の前に、前記第二表面(24)から少なくとも絶縁層(30)まで予備ビア(52)を形成する予備穿孔工程(310)をさらに備える、

請求項1〜10のいずれかに記載の方法。 - 前記予備ビアはドライエッチング、湿式エッチング又は反応性イオンエッチングで形成する、

請求項11に記載の方法。 - 前記溶液は以下のものを含み:

− プロトン性溶媒;

− 一以上のジアゾニウム塩;

− 一以上の、鎖状に重合可能な単量体であって前記プロトン性溶媒に溶解するもの;

− 一以上の、上記溶液のpHを7、好ましくは2.5より小さく調整することで前記ジアゾニウム塩を安定化させるのに十分な量の酸;かつ

ポテンショパルスモード又はガルバノパルスモードにより、前記縦方向の接続の表面に、60ナノメートル以上の、好ましくは80ナノメートル以上、500ナノメートル以下の厚みを有する膜を形成するのに十分な持続時間の間、極性を持たせる、

請求項1に記載の方法。 - 以下の、銅の拡散に対する隔膜(70)を作成する工程(500)をさらに含む:

a)粒子、特に金属又は金属合金、具体的にはニッケル又はコバルトのナノ粒子を含有する有機膜を、前記絶縁膜(60)の表面に湿式法により形成する工程;

b)上記のとおり形成した膜を、100nm以上の厚さを有する金属膜を形成可能な条件下で、好ましくは有機膜に取り込まれる前記金属と同じ性質を有する一以上の金属塩、安定化剤及び一以上の還元剤を含有する溶液と接触させる工程;

請求項1に記載の方法。 - 以下の、銅の拡散に対する隔膜(70)を作成する工程(500)をさらに含む:

1.下記を含む溶液により絶縁層の表面を活性化する:

i) 下記の群から選ばれる一又は複数のパラジウム錯体を含有する活性剤:

・下記式(I)を有するパラジウム錯体:

− R1及びR2は同一で、かつH;CH2CH2NH2;若しくはCH2CH2OHを表すものであり;若しくは

− R1はHを表し、かつR2はCH2CH2NH2を表すものであり;若しくは

− R2はCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;又は

− R2はCH2CH2NHCH2CH2NHCH2CH2NH2を表し、かつR1はHを表すものであり;

− XはCl-;Br-;I-;H2O, NO3 -;CH3SO3 -;CF3SO3 -;CH3-Ph-SO3 -;CH3COO-からなる群から選ばれるリガンドを表す;

・下記式(IIa)又は(IIb)を有するパラジウム錯体:

− R1及びR2は上記のとおり定義され、かつ

− Yは下記からなり、二価の負電荷を備える対イオンを表す:

・いずれもCl-;PF6 -;BF4 -;NO3 -;CH3SO3 -;CF3SO3 -;CH3C6H4SO3 -;CH3COO-からなる群から選ばれる2個の一価陰イオン;又は

・二価の陰イオン、好ましくはSO4 2-;

ii) 下記一般式を有する一又は複数のオルガノシランからなる二官能の有機結合剤:

{NH2-(L)}3-n-Si(OR)n (V)

ここで:

− LはCH2;CH2CH2;CH2CH2CH2-及びCH2CH2NHCH2CH2からなる群から選ばれるスペーサーであり;

− RはCH3,CH3CH2,CH3CH2CH2及び(CH3)2CHからなる群から選ばれる基であり;かつ

− nは1,2又は3に等しい整数である。

iii)上記活性剤及び結合剤を溶解するのに適した一又は複数の溶媒からなる溶媒系;

2.前記活性化された表面に導電層を無電解沈着させる;

請求項1に記載の方法。 - 以下により銅シード層(80)を形成する工程(600)をさらに備える:

a)前記銅の拡散に対する隔膜層の、開放された表面に以下のものを含む溶液を接触させる:

− 一以上の溶媒;

− 濃度約14mM以上、約120mM以下の銅イオン;

− エチレンジアミン;

− 銅に対するエチレンジアミンのモル比は1.80以上、2.03以下;

− 上記組成のpHは6.6以上、7.5以下;

b)前記隔膜層の開放された前記表面を前記銅シード層の形成に充分な持続時間をもって極性を有するようにする;

請求項14又は15に記載の方法。 - 以下の組成を有する組成物を用いた、銅の導電沈着により縦方向の電気的接続を金属被覆する工程をさらに備える:

− 銅イオン、濃度45mM以上、1500mM以下の、好ましくは45mM以上、500mM以下の、より好ましくは100mM以上、300mM以下の前記銅イオン;

− 銅の錯化剤、2以上、4以下のアミノ基を有する芳香族ポリアミンを含む群の内の一以上の構成要素を備え、濃度45mM以上、3000mM以下の、好ましくは45mM以上、1500mM以下の、より好ましくは300mM以上、900mM以下の前記銅の錯化剤;

− 銅及び前記銅の錯化剤のモル比は0.1以上、5以下、好ましくは0.1以上、1以下、より好ましくは0.2以上、0.4以下である;

− チオジグリコール酸、濃度1mg/L以上、500mg/L以下の前記チオジグリコール酸;

− 任意に加えてもよい、緩衝系、特に濃度0.1M以上、3M以下の硫酸アンモニウム;

請求項15又は16に記載の方法。 - − 第一表面(22)及び第二表面(24)を有する支持基板(20)、

− 前記支持基板(20)の前記第一表面(22)上に被覆される絶縁層(30)、

− 前記絶縁層(30)内に形成される一以上のデバイス構造(40);

− 前記支持基板(20)の前記第二表面(24)から前記デバイス構造(40)まで達する、一以上の縦方向の接続であって、前記縦方向の接続は、前記支持基板(20)の第一表面(22)の近傍の絶縁層(30)に、アンダーカット(U)を有するもの、及び

前記支持基板(20)の近傍のみにて前記縦方向の接続の壁に設けられる一以上の絶縁膜(60)であって、前記絶縁膜(60)の厚みは均一であるものを備える、

積層半導体構造(1)。 - 前記絶縁膜(60)及び前記縦方向の接続の前記壁を覆う、銅の拡散に対する隔膜(70)をさらに備え、

前記銅の拡散に対する隔膜(70)の厚みは均一である、

請求項18に記載の積層半導体構造(1)。 - 銅の拡散に対する隔膜(70)を覆う、銅シード層(80)をさらに備え、

前記銅シード層(80)の厚みは均一である、

請求項19に記載の積層半導体構造(1)。

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US201161489015P | 2011-05-23 | 2011-05-23 | |

| US61/489,015 | 2011-05-23 | ||

| EP11305632.9 | 2011-05-23 | ||

| EP11305632.9A EP2528089B1 (en) | 2011-05-23 | 2011-05-23 | Method for forming a vertical electrical connection in a layered semiconductor structure |

| PCT/EP2012/059503 WO2012160063A1 (en) | 2011-05-23 | 2012-05-22 | Method for forming a vertical electrical connection in a layered semiconductor structure |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2014519201A JP2014519201A (ja) | 2014-08-07 |

| JP2014519201A5 JP2014519201A5 (ja) | 2017-02-02 |

| JP6347744B2 true JP6347744B2 (ja) | 2018-06-27 |

Family

ID=44789383

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2014511848A Active JP6347744B2 (ja) | 2011-05-23 | 2012-05-22 | 積層半導体構造における縦方向の電気接続の形成方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US9368397B2 (ja) |

| EP (1) | EP2528089B1 (ja) |

| JP (1) | JP6347744B2 (ja) |

| KR (1) | KR102014891B1 (ja) |

| CN (1) | CN103582942B (ja) |

| CA (1) | CA2836845C (ja) |

| IL (1) | IL229519B (ja) |

| SG (1) | SG194863A1 (ja) |

| TW (1) | TWI594387B (ja) |

| WO (1) | WO2012160063A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103367139B (zh) * | 2013-07-11 | 2016-08-24 | 华进半导体封装先导技术研发中心有限公司 | 一种tsv孔底部介质层刻蚀方法 |

| JP2015041691A (ja) * | 2013-08-21 | 2015-03-02 | 株式会社東芝 | 半導体装置および半導体装置の製造方法 |

| US9321635B2 (en) * | 2013-11-28 | 2016-04-26 | Solid State System Co., Ltd. | Method to release diaphragm in MEMS device |

| TWI698963B (zh) * | 2016-06-03 | 2020-07-11 | 日商大日本印刷股份有限公司 | 貫通電極基板及其製造方法、以及安裝基板 |

| CN109835867B (zh) * | 2017-11-24 | 2023-07-14 | 中芯国际集成电路制造(上海)有限公司 | 刻蚀溶液和刻蚀方法 |

| CN109082216B (zh) * | 2018-05-23 | 2019-12-27 | 同济大学 | 一种弹性导电膜及其制备方法 |

| CN110634837A (zh) * | 2019-09-27 | 2019-12-31 | 哈尔滨理工大学 | 一种用于铜互联电路中的扩散阻挡层 |

| US11276650B2 (en) * | 2019-10-31 | 2022-03-15 | Avago Technologies International Sales Pte. Limited | Stress mitigation structure |

| JP7419877B2 (ja) * | 2020-02-28 | 2024-01-23 | セイコーエプソン株式会社 | 振動デバイス、電子機器および移動体 |

Family Cites Families (29)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| BE510776A (ja) | 1951-04-20 | |||

| US3642549A (en) * | 1969-01-15 | 1972-02-15 | Ibm | Etching composition indication |

| US4230523A (en) * | 1978-12-29 | 1980-10-28 | International Business Machines Corporation | Etchant for silicon dioxide films disposed atop silicon or metallic silicides |

| US4442421A (en) * | 1981-07-31 | 1984-04-10 | Jacobus Otha J | Semiconducting coordination polymers and electrical applications thereof |

| JP2678701B2 (ja) * | 1992-02-19 | 1997-11-17 | 石原薬品 株式会社 | 電気銅めっき液 |

| JP4189141B2 (ja) * | 2000-12-21 | 2008-12-03 | 株式会社東芝 | 基板処理装置及びこれを用いた基板処理方法 |

| US6645832B2 (en) | 2002-02-20 | 2003-11-11 | Intel Corporation | Etch stop layer for silicon (Si) via etch in three-dimensional (3-D) wafer-to-wafer vertical stack |

| EP1245697A3 (de) * | 2002-07-17 | 2003-02-19 | ATOTECH Deutschland GmbH | Verfahren zum aussenstromlosen Abscheiden von Silber |

| US7297190B1 (en) * | 2006-06-28 | 2007-11-20 | Lam Research Corporation | Plating solutions for electroless deposition of copper |

| US7060624B2 (en) | 2003-08-13 | 2006-06-13 | International Business Machines Corporation | Deep filled vias |

| US7101792B2 (en) | 2003-10-09 | 2006-09-05 | Micron Technology, Inc. | Methods of plating via interconnects |

| US8158532B2 (en) * | 2003-10-20 | 2012-04-17 | Novellus Systems, Inc. | Topography reduction and control by selective accelerator removal |

| US7598167B2 (en) * | 2004-08-24 | 2009-10-06 | Micron Technology, Inc. | Method of forming vias in semiconductor substrates without damaging active regions thereof and resulting structures |

| JP2006093227A (ja) * | 2004-09-21 | 2006-04-06 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| FR2890984B1 (fr) * | 2005-09-20 | 2009-03-27 | Alchimer Sa | Procede d'electrodeposition destine au revetement d'une surface d'un substrat par un metal. |

| US7579274B2 (en) * | 2006-02-21 | 2009-08-25 | Alchimer | Method and compositions for direct copper plating and filing to form interconnects in the fabrication of semiconductor devices |

| JP5236503B2 (ja) | 2006-02-28 | 2013-07-17 | コミサリア ア レネルジィ アトミーク エ オ ゼネ ルジイ アルテアナティーフ | 水溶液から導電性または半導電性表面上に有機フィルムを形成する方法 |

| US7285477B1 (en) * | 2006-05-16 | 2007-10-23 | International Business Machines Corporation | Dual wired integrated circuit chips |

| JP5245135B2 (ja) * | 2007-06-30 | 2013-07-24 | 株式会社ザイキューブ | 貫通導電体を有する半導体装置およびその製造方法 |

| EP3032578B1 (en) * | 2008-03-19 | 2021-01-13 | IMEC vzw | Method for fabricating through-substrate vias and corresponding semiconductor device |

| FR2933425B1 (fr) * | 2008-07-01 | 2010-09-10 | Alchimer | Procede de preparation d'un film isolant electrique et application pour la metallisation de vias traversants |

| WO2010044741A1 (en) * | 2008-10-15 | 2010-04-22 | ÅAC Microtec AB | Method for making via interconnection |

| CN102132409A (zh) * | 2008-11-21 | 2011-07-20 | 松下电器产业株式会社 | 半导体装置及其制造方法 |

| JP2010129952A (ja) * | 2008-12-01 | 2010-06-10 | Nippon Telegr & Teleph Corp <Ntt> | 貫通電極配線の製造方法 |

| US8043965B2 (en) * | 2009-02-11 | 2011-10-25 | Northrop Grumann Systems Corporation | Method of forming a through substrate via in a compound semiconductor |

| JP2010205921A (ja) * | 2009-03-03 | 2010-09-16 | Olympus Corp | 半導体装置および半導体装置の製造方法 |

| FR2943688B1 (fr) * | 2009-03-27 | 2012-07-20 | Alchimer | Dispositif et procede pour realiser une reaction electrochimique sur une surface d'un substrat semi-conducteur |

| FR2950633B1 (fr) | 2009-09-30 | 2011-11-25 | Alchimer | Solution et procede d'activation de la surface oxydee d'un substrat semi-conducteur. |

| FR2961220B1 (fr) | 2010-06-11 | 2012-08-17 | Alchimer | Composition d'electrodeposition de cuivre et procede de remplissage d'une cavite d'un substrat semi-conducteur utilisant cette composition |

-

2011

- 2011-05-23 EP EP11305632.9A patent/EP2528089B1/en active Active

-

2012

- 2012-05-22 JP JP2014511848A patent/JP6347744B2/ja active Active

- 2012-05-22 CA CA2836845A patent/CA2836845C/en active Active

- 2012-05-22 TW TW101118163A patent/TWI594387B/zh active

- 2012-05-22 CN CN201280025014.8A patent/CN103582942B/zh active Active

- 2012-05-22 WO PCT/EP2012/059503 patent/WO2012160063A1/en active Application Filing

- 2012-05-22 KR KR1020137034071A patent/KR102014891B1/ko active IP Right Grant

- 2012-05-22 US US14/119,184 patent/US9368397B2/en active Active

- 2012-05-22 SG SG2013082995A patent/SG194863A1/en unknown

-

2013

- 2013-11-20 IL IL229519A patent/IL229519B/en active IP Right Grant

Also Published As

| Publication number | Publication date |

|---|---|

| EP2528089B1 (en) | 2014-03-05 |

| IL229519B (en) | 2018-01-31 |

| KR20140053912A (ko) | 2014-05-08 |

| WO2012160063A1 (en) | 2012-11-29 |

| US9368397B2 (en) | 2016-06-14 |

| CA2836845C (en) | 2020-06-30 |

| TW201304105A (zh) | 2013-01-16 |

| JP2014519201A (ja) | 2014-08-07 |

| CN103582942A (zh) | 2014-02-12 |

| IL229519A0 (en) | 2014-01-30 |

| CA2836845A1 (en) | 2012-11-29 |

| KR102014891B1 (ko) | 2019-10-21 |

| SG194863A1 (en) | 2013-12-30 |

| CN103582942B (zh) | 2017-05-24 |

| TWI594387B (zh) | 2017-08-01 |

| EP2528089A1 (en) | 2012-11-28 |

| US20140084474A1 (en) | 2014-03-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6347744B2 (ja) | 積層半導体構造における縦方向の電気接続の形成方法 | |

| KR101679434B1 (ko) | 전기적 절연 필름을 제조하는 방법 및 스루 비아의 금속화반응에 대한 적용 | |

| CN105845558B (zh) | 穿硅通孔填充工艺 | |

| JP5743907B2 (ja) | スルーシリコンビア(tsv)内にチップ−チップ間、チップ−ウェハー間及びウェハー−ウェハー間の銅インターコネクトを電着するプロセス | |

| KR101807313B1 (ko) | 듀얼 스테이트 저해제를 지닌 전해질을 이용한 관통형 실리콘 비아 충진 | |

| US9133560B2 (en) | Electroplating composition for coating a substrate surface with a metal | |

| CN113260739A (zh) | 纳米孪晶铜结构的电沉积 | |

| JP5689411B2 (ja) | 電着組成物、及び、該組成物を用いた半導体基板のコーティング方法 | |

| CN106463361A (zh) | 超共形电镀 | |

| TWI513863B (zh) | 銅電鍍組合物及使用此組合物填充半導體基板中之凹洞之方法 | |

| TWI673394B (zh) | 在微電子件中的銅的電沉積 | |

| TWI572750B (zh) | 直通矽穿孔之銅充填 | |

| TW202114128A (zh) | 封裝結構和其製造方法 | |

| WO2013142863A1 (en) | Through-silicon via filling | |

| KR101713686B1 (ko) | 실리콘 관통 비아의 무결함 필링용 평탄제 및 필링방법 | |

| WO2011018478A1 (en) | Electrolyte and method for the electroplating of copper on a barrier layer, and semiconductor substrate obtained with said method | |

| KR101436553B1 (ko) | 실리콘 관통 비아 구조를 가진 반도체 장치 및 그 제조 방법 | |

| WO2010133550A1 (en) | Method for coating a semiconductor substrate by electrodeposition | |

| US20110017703A1 (en) | Selective planarization method and devices fabricated on planarized structures | |

| KR102445575B1 (ko) | 도금용 평활제, 이를 포함하는 도금용 조성물 및 구리 배선의 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20150508 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20151112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20151124 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160208 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160322 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160422 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160531 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20160822 |

|

| A524 | Written submission of copy of amendment under article 19 pct |

Free format text: JAPANESE INTERMEDIATE CODE: A524 Effective date: 20161130 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20170314 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180323 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180529 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6347744 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |