JP6330705B2 - 半導体装置およびその製造方法ならびに電力変換装置 - Google Patents

半導体装置およびその製造方法ならびに電力変換装置 Download PDFInfo

- Publication number

- JP6330705B2 JP6330705B2 JP2015060424A JP2015060424A JP6330705B2 JP 6330705 B2 JP6330705 B2 JP 6330705B2 JP 2015060424 A JP2015060424 A JP 2015060424A JP 2015060424 A JP2015060424 A JP 2015060424A JP 6330705 B2 JP6330705 B2 JP 6330705B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- semiconductor device

- type

- ion implantation

- type semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H10P95/904—

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

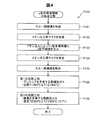

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

- H01L21/3245—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering of AIIIBV compounds

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/02104—Forming layers

- H01L21/02107—Forming insulating materials on a substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/2654—Bombardment with radiation with high-energy radiation producing ion implantation in AIIIBV compounds

- H01L21/26546—Bombardment with radiation with high-energy radiation producing ion implantation in AIIIBV compounds of electrically active species

- H01L21/26553—Through-implantation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

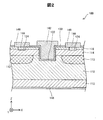

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0297—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the gate electrodes, e.g. to form trench gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/64—Double-diffused metal-oxide semiconductor [DMOS] FETs

- H10D30/66—Vertical DMOS [VDMOS] FETs

- H10D30/668—Vertical DMOS [VDMOS] FETs having trench gate electrodes, e.g. UMOS transistors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

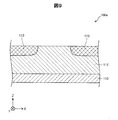

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/17—Semiconductor regions connected to electrodes not carrying current to be rectified, amplified or switched, e.g. channel regions

- H10D62/393—Body regions of DMOS transistors or IGBTs

-

- H10P30/206—

-

- H10P30/212—

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/01—Manufacture or treatment

- H10D30/021—Manufacture or treatment of FETs having insulated gates [IGFET]

- H10D30/028—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs

- H10D30/0291—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs

- H10D30/0295—Manufacture or treatment of FETs having insulated gates [IGFET] of double-diffused metal oxide semiconductor [DMOS] FETs of vertical DMOS [VDMOS] FETs using recessing of the source electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

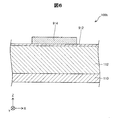

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

- H10D62/8503—Nitride Group III-V materials, e.g. AlN or GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/23—Electrodes carrying the current to be rectified, amplified, oscillated or switched, e.g. sources, drains, anodes or cathodes

- H10D64/251—Source or drain electrodes for field-effect devices

- H10D64/256—Source or drain electrodes for field-effect devices for lateral devices wherein the source or drain electrodes are recessed in semiconductor bodies

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Microelectronics & Electronic Packaging (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- Power Engineering (AREA)

- High Energy & Nuclear Physics (AREA)

- Health & Medical Sciences (AREA)

- Toxicology (AREA)

- Electrodes Of Semiconductors (AREA)

- Recrystallisation Techniques (AREA)

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015060424A JP6330705B2 (ja) | 2015-03-24 | 2015-03-24 | 半導体装置およびその製造方法ならびに電力変換装置 |

| US15/060,473 US9905432B2 (en) | 2015-03-24 | 2016-03-03 | Semiconductor device, method for manufacturing the same and power converter |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015060424A JP6330705B2 (ja) | 2015-03-24 | 2015-03-24 | 半導体装置およびその製造方法ならびに電力変換装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016181580A JP2016181580A (ja) | 2016-10-13 |

| JP2016181580A5 JP2016181580A5 (enExample) | 2017-08-03 |

| JP6330705B2 true JP6330705B2 (ja) | 2018-05-30 |

Family

ID=56976201

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015060424A Active JP6330705B2 (ja) | 2015-03-24 | 2015-03-24 | 半導体装置およびその製造方法ならびに電力変換装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9905432B2 (enExample) |

| JP (1) | JP6330705B2 (enExample) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12527023B2 (en) | 2021-02-24 | 2026-01-13 | Panasonic Holdings Corporation | Nitride semiconductor device |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10636663B2 (en) | 2017-03-29 | 2020-04-28 | Toyoda Gosei Co., Ltd. | Method of manufacturing semiconductor device including implanting impurities into an implanted region of a semiconductor layer and annealing the implanted region |

| JP6801555B2 (ja) * | 2017-03-29 | 2020-12-16 | 豊田合成株式会社 | 半導体装置の製造方法 |

| JP6791083B2 (ja) * | 2017-09-28 | 2020-11-25 | 豊田合成株式会社 | 半導体装置の製造方法 |

| JP7024319B2 (ja) * | 2017-10-24 | 2022-02-24 | 富士電機株式会社 | GaN系半導体装置の製造方法およびGaN系半導体装置 |

| JP6828697B2 (ja) * | 2018-02-06 | 2021-02-10 | 株式会社豊田中央研究所 | Iii族窒化物半導体装置およびiii族窒化物半導体基板の製造方法 |

| JP6927112B2 (ja) * | 2018-03-27 | 2021-08-25 | 豊田合成株式会社 | 半導体装置の製造方法 |

| JP6927116B2 (ja) * | 2018-03-28 | 2021-08-25 | 豊田合成株式会社 | 半導体装置 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4581198B2 (ja) * | 2000-08-10 | 2010-11-17 | ソニー株式会社 | 窒化物化合物半導体層の熱処理方法及び半導体素子の製造方法 |

| JP2003051613A (ja) * | 2002-05-20 | 2003-02-21 | Toyoda Gosei Co Ltd | 窒化ガリウム系化合物半導体及び素子の製造方法 |

| JP2004128189A (ja) | 2002-10-02 | 2004-04-22 | Sanyo Electric Co Ltd | 窒化ガリウム系化合物半導体の製造方法 |

| JP2004356257A (ja) | 2003-05-28 | 2004-12-16 | Toyota Central Res & Dev Lab Inc | p型III族窒化物半導体の製造方法 |

| JP2008135700A (ja) | 2006-11-01 | 2008-06-12 | Furukawa Electric Co Ltd:The | Iii族窒化物膜の製造方法及びiii族窒化物半導体素子 |

| JP5141037B2 (ja) | 2007-02-21 | 2013-02-13 | 株式会社豊田中央研究所 | 半導体装置の製造方法 |

| JP5358955B2 (ja) * | 2008-01-15 | 2013-12-04 | 住友電気工業株式会社 | p型窒化ガリウム系半導体領域を形成する方法 |

| JP5432480B2 (ja) * | 2008-07-02 | 2014-03-05 | ルネサスエレクトロニクス株式会社 | Si基板上のGaN系デバイスの熱処理方法 |

| JP5845714B2 (ja) | 2011-08-19 | 2016-01-20 | 住友電気工業株式会社 | 炭化珪素半導体装置の製造方法 |

| JP5763514B2 (ja) | 2011-12-13 | 2015-08-12 | トヨタ自動車株式会社 | スイッチング素子の製造方法 |

| JP6047995B2 (ja) * | 2012-08-22 | 2016-12-21 | 住友電気工業株式会社 | Iii族窒化物半導体を作製する方法、半導体素子を作製する方法、iii族窒化物半導体装置、熱処理を行う方法 |

| JP6098259B2 (ja) * | 2013-03-19 | 2017-03-22 | 豊田合成株式会社 | 半導体装置の製造方法 |

| JP2014225506A (ja) * | 2013-05-15 | 2014-12-04 | 住友電気工業株式会社 | 窒化ガリウム系半導体層の製造方法、窒化ガリウム系半導体層、および窒化ガリウム系半導体基板 |

-

2015

- 2015-03-24 JP JP2015060424A patent/JP6330705B2/ja active Active

-

2016

- 2016-03-03 US US15/060,473 patent/US9905432B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12527023B2 (en) | 2021-02-24 | 2026-01-13 | Panasonic Holdings Corporation | Nitride semiconductor device |

Also Published As

| Publication number | Publication date |

|---|---|

| US9905432B2 (en) | 2018-02-27 |

| US20160284563A1 (en) | 2016-09-29 |

| JP2016181580A (ja) | 2016-10-13 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6330705B2 (ja) | 半導体装置およびその製造方法ならびに電力変換装置 | |

| US10332966B2 (en) | Semiconductor device, method of manufacturing the same and power converter | |

| JP6627408B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| KR101473534B1 (ko) | 화합물 반도체 장치 및 그 제조 방법 | |

| CN103765592B (zh) | 用于生长iii‑v外延层的方法 | |

| Lee et al. | Wafer-level heterogeneous integration of GaN HEMTs and Si (100) MOSFETs | |

| TW200950081A (en) | Semiconductor device and method for manufacturing semiconductor device | |

| TW201242016A (en) | Method of producing semiconductor device and semiconductor device | |

| CN105304712A (zh) | 半导体装置及其制造方法 | |

| US20170278952A1 (en) | Method of manufacturing semiconductor device, and semiconductor device | |

| JP6791083B2 (ja) | 半導体装置の製造方法 | |

| WO2013145022A1 (ja) | 炭化珪素半導体装置の製造方法 | |

| US20160104791A1 (en) | Method for forming an implanted area for a heterojunction transistor that is normally blocked | |

| JP2018170334A (ja) | 半導体装置の製造方法 | |

| US10497572B2 (en) | Method for manufacturing semiconductor device | |

| JP6927112B2 (ja) | 半導体装置の製造方法 | |

| JP6485299B2 (ja) | 半導体装置およびその製造方法ならびに電力変換装置 | |

| JP6406080B2 (ja) | 半導体装置の製造方法 | |

| US9852925B2 (en) | Method of manufacturing semiconductor device | |

| CN108574001B (zh) | 半导体装置 | |

| JP2017079282A (ja) | 半導体装置の製造方法 | |

| JP2016009843A (ja) | 半導体装置およびその製造方法 | |

| JP5540685B2 (ja) | 化合物半導体装置の製造方法 | |

| KR101375685B1 (ko) | 질화물 반도체 소자 및 그 제조 방법 | |

| JP5275773B2 (ja) | 電界効果トランジスタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170419 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170620 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20180109 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180327 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180409 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6330705 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |