JP6319151B2 - 半導体装置および半導体装置の製造方法 - Google Patents

半導体装置および半導体装置の製造方法 Download PDFInfo

- Publication number

- JP6319151B2 JP6319151B2 JP2015059436A JP2015059436A JP6319151B2 JP 6319151 B2 JP6319151 B2 JP 6319151B2 JP 2015059436 A JP2015059436 A JP 2015059436A JP 2015059436 A JP2015059436 A JP 2015059436A JP 6319151 B2 JP6319151 B2 JP 6319151B2

- Authority

- JP

- Japan

- Prior art keywords

- semiconductor layer

- nitride semiconductor

- semiconductor device

- nitride

- electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/117—Shapes of semiconductor bodies

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/124—Shapes, relative sizes or dispositions of the regions of semiconductor bodies or of junctions between the regions

- H10D62/125—Shapes of junctions between the regions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/10—Shapes, relative sizes or dispositions of the regions of the semiconductor bodies; Shapes of the semiconductor bodies

- H10D62/129—Cathode regions of diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D62/00—Semiconductor bodies, or regions thereof, of devices having potential barriers

- H10D62/80—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials

- H10D62/85—Semiconductor bodies, or regions thereof, of devices having potential barriers characterised by the materials being Group III-V materials, e.g. GaAs

- H10D62/8503—Nitride Group III-V materials, e.g. AlN or GaN

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D64/00—Electrodes of devices having potential barriers

- H10D64/20—Electrodes characterised by their shapes, relative sizes or dispositions

- H10D64/27—Electrodes not carrying the current to be rectified, amplified, oscillated or switched, e.g. gates

- H10D64/311—Gate electrodes for field-effect devices

- H10D64/411—Gate electrodes for field-effect devices for FETs

- H10D64/511—Gate electrodes for field-effect devices for FETs for IGFETs

- H10D64/512—Disposition of the gate electrodes, e.g. buried gates

- H10D64/513—Disposition of the gate electrodes, e.g. buried gates within recesses in the substrate, e.g. trench gates, groove gates or buried gates

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

- H10D8/01—Manufacture or treatment

- H10D8/045—Manufacture or treatment of PN junction diodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D8/00—Diodes

- H10D8/422—PN diodes having the PN junctions in mesas

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D89/00—Aspects of integrated devices not covered by groups H10D84/00 - H10D88/00

- H10D89/60—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD]

- H10D89/601—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs

- H10D89/611—Integrated devices comprising arrangements for electrical or thermal protection, e.g. protection circuits against electrostatic discharge [ESD] for devices having insulated gate electrodes, e.g. for IGFETs or IGBTs using diodes as protective elements

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/24—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials using chemical vapour deposition [CVD]

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/32—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials characterised by intermediate layers between substrates and deposited layers

- H10P14/3202—Materials thereof

- H10P14/3214—Materials thereof being Group IIIA-VA semiconductors

- H10P14/3216—Nitrides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3402—Deposited materials, e.g. layers characterised by the chemical composition

- H10P14/3414—Deposited materials, e.g. layers characterised by the chemical composition being group IIIA-VIA materials

- H10P14/3416—Nitrides

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3438—Doping during depositing

- H10P14/3441—Conductivity type

- H10P14/3442—N-type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10P—GENERIC PROCESSES OR APPARATUS FOR THE MANUFACTURE OR TREATMENT OF DEVICES COVERED BY CLASS H10

- H10P14/00—Formation of materials, e.g. in the shape of layers or pillars

- H10P14/20—Formation of materials, e.g. in the shape of layers or pillars of semiconductor materials

- H10P14/34—Deposited materials, e.g. layers

- H10P14/3438—Doping during depositing

- H10P14/3441—Conductivity type

- H10P14/3444—P-type

Landscapes

- Electrodes Of Semiconductors (AREA)

- Semiconductor Integrated Circuits (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Physics & Mathematics (AREA)

- Geometry (AREA)

Description

本発明の第1の形態は、

第1導電型の第1窒化物半導体層と、前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、前記第1導電型の第4窒化物半導体層と、がこの順に積層された積層体と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する第1の電極と、を有し、

前記第3窒化物半導体層と、前記第4窒化物半導体層とを貫通し、前記第2窒化物半導体層に達するトレンチが形成され、

前記トレンチに絶縁膜を介して設けられたゲート電極を備える、

縦型MOSトランジスタと、

前記第1の電極と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する前記第2導電型のオーミック電極と、を有する、

保護素子と、を備える、半導体装置であって、

前記第1導電型の不純物濃度は、前記第1窒化物半導体層に比べて前記第2窒化物半導体層のほうが低く、

前記第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、

前記積層体の積層方向から見たときに、前記凸部の上面は、前記第2導電型のオーミック電極と少なくとも一部が重なる位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置である。

本発明の第2の形態は、

半導体装置の製造方法であって、

第1導電型の第1窒化物半導体層の面に突出する凸部を形成する工程と、

前記第1窒化物半導体層の面であって、前記凸部を備える面に、前記第1窒化物半導体層よりも不純物濃度が小さい前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、をこの順に積層する工程と、

前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達するトレンチを形成する工程と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、第1の電極を形成する工程と、

積層方向において、前記凸部の上面と少なくとも一部が重なる位置であって、前記第3窒化物半導体層の面であり、前記第2窒化物半導体層と接する面とは反対側の面に、前記第2導電型のオーミック電極を形成する工程と、

前記トレンチに絶縁膜を介してゲート電極を形成する工程と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、前記第1導電型の第4窒化物半導体層を形成する工程と、

前記第4窒化物半導体層にソース電極を形成する工程と、

を有し、

前記第4窒化物半導体層は、前記積層方向において、前記凸部の上面と重ならない位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、

前記第1窒化物半導体層から前記第4窒化物半導体層までの窒化物半導体層と前記ゲート電極と前記第1の電極と前記ソース電極とから形成される縦型MOSトランジスタと、前記第1窒化物半導体層から前記第3窒化物半導体層までの窒化物半導体層と前記第1電極と前記第2導電型のオーミック電極から形成されるPN接合ダイオードである保護素子と、を備える半導体装置の製造方法である。また、本発明は以下の形態として実現することもできる。

A1.半導体装置10の構成:

図1は、第1実施形態における半導体装置10の構成を模式的に示す断面図である。半導体装置10は、縦型MOS(Metal-Oxide-Semiconductor)トランジスタ300と保護素子200とを備える。縦型MOSトランジスタ300は、窒化物半導体を用いて形成されたGaN系の半導体装置である。本実施形態では、縦型MOSトランジスタ300は、トレンチゲート型MOSFET(Metal-Oxide-Semiconductor Field Effect Transistor)であり、例えば、電力制御に用いられ、パワーデバイスとも呼ばれる。保護素子200は、PN接合ダイオードである。本実施形態においては、窒化物半導体として窒化ガリウム(GaN)を用いる。

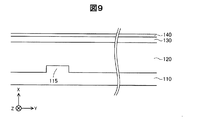

図7は、半導体装置10の製造方法を示す工程図である。まず、工程P105において、基板110の面に突出する凸部115を形成する。

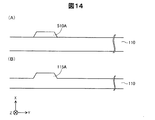

図13は、第2実施形態における半導体装置10Aの構成を模式的に示す図である。半導体装置10Aは、半導体装置10と比較して、凸部の形状が異なるが、それ以外は同じである。半導体装置10Aの凸部115Aの側面(Y軸方向側の面)は、凸部115Aの上面(+X軸方向側の面)に対して傾斜している。本実施形態において、半導体装置10Aの凸部115Aの側面(Y軸方向側の面)は、テーパー形状である。半導体装置10Aの製造方法は、半導体装置10の製造方法と比較して、凸部115Aを形成する工程(工程P105)において異なるが、それ以外は同じである。

この発明は上記の実施形態に限られるものではなく、その要旨を逸脱しない範囲において種々の形態において実施することが可能であり、例えば次のような変形も可能である。

本実施形態において、凸部115はエッチングにより形成したが、本発明はこれに限られない。凸部115の形成方法を、再成長を用いる方法としてもよい。

本実施形態において、積層体100の積層方向(X軸方向)において、N型半導体層140は、凸部115の上面と重ならない位置に配されている。しかし、本発明はこれに限らない。

本実施形態において、凸部115Dは、段差部186の下方(−X軸方向側)には配置されていない。しかし、本発明はこれに限らない。

本実施形態において、基板とN型半導体層との少なくとも一方に含まれるドナーとして、ケイ素(Si)を用いているが、本発明はこれに限られない。ドナーとして、ゲルマニウム(Ge)や、酸素(O)を用いてもよい。

本実施形態において、P型半導体層に含まれるアクセプタとして、マグネシウム(Mg)を用いているが、本発明はこれに限られない。アクセプタとして、亜鉛(Zn)や、炭素(C)を用いてもよい。

本実施形態において、電極230は、パラジウム(Pd)から形成される。しかし、本発明はこれに限られない。電極230は、他の材料により形成されていてもよく、複数層の構成であってもよい。例えば、電極230は、ニッケル(Ni)、白金(Pt)、コバルト(Co)等の導電性材料の少なくとも1つを含む電極であってもよく、ニッケル(Ni)/パラジウム(Pd)構成や、白金(Pt)/パラジウム(Pd)構成(パラジウムが半導体基板側)のような2層構成であってもよい。

本実施形態において、ゲート電極である電極250は、アルミニウム(Al)から形成される。しかし、本発明はこれに限られない。電極250は、ポリシリコンを用いてもよい。また、電極250は、他の材料により形成されていてもよく、複数層の構成であってもよい。例えば、電極250は、金(Au)/ニッケル(Ni)構成や、アルミニウム(Al)/チタン(Ti)構成、アルミニウム(Al)/窒化チタン(TiN)構成(それぞれ、ニッケル、チタン、窒化チタンがゲート絶縁膜側)のような2層構成であってもよいし、窒化チタン(TiN)/アルミニウム(Al)/窒化チタン(TiN)構成のような3層構成であってもよい。

10A…半導体装置

10C…半導体装置

100…積層体

110…基板

115…凸部

115A…凸部

115B…凸部

115D…凸部

120…N型半導体層

130…P型半導体層

140…N型半導体層

140C…N型半導体層

182…凹部

184…トレンチ

186…段差部

200…保護素子

210…電極

230…電極

240…電極

250…電極

270…配線

280…配線

285…開口部

300…縦型MOSトランジスタ

340…絶縁膜

510…絶縁膜

510A…絶縁膜

510B…絶縁膜

Id…電流

Vds…電圧

Vgs…電圧

d1…距離

d3…距離

l1…実線

l2…一点鎖線

l3…二点鎖線

l4…破線

Claims (15)

- 第1導電型の第1窒化物半導体層と、前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、前記第1導電型の第4窒化物半導体層と、がこの順に積層された積層体と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する第1の電極と、を有し、

前記第3窒化物半導体層と、前記第4窒化物半導体層とを貫通し、前記第2窒化物半導体層に達するトレンチが形成され、

前記トレンチに絶縁膜を介して設けられたゲート電極を備える、

縦型MOSトランジスタと、

前記第1の電極と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面と接する前記第2導電型のオーミック電極と、を有する、

保護素子と、を備える、半導体装置であって、

前記第1導電型の不純物濃度は、前記第1窒化物半導体層に比べて前記第2窒化物半導体層のほうが低く、

前記第1窒化物半導体層は、前記第2窒化物半導体層へ突出する凸部を備え、

前記積層体の積層方向から見たときに、前記凸部の上面は、前記第2導電型のオーミック電極と少なくとも一部が重なる位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置。 - 請求項1に記載の半導体装置であって、

前記積層方向から見たときに、前記第4窒化物半導体層は、前記凸部の上面と重ならない位置に配されている、半導体装置。 - 請求項1または請求項2に記載の半導体装置であって、さらに、

前記積層方向から見たときに、前記凸部に対して、前記トレンチが配されている側とは反対側に、前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達する段差部が形成されており、

前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みは、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚み以下である、半導体装置。 - 請求項3に記載の半導体装置であって、

前記段差部の底面と前記凸部との距離は、前記段差部の底面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置。 - 請求項1から請求項4までのいずれか一項に記載の半導体装置であって、さらに、

前記第4窒化物半導体層の面であって、前記第3窒化物半導体層と接する面とは反対側の面と接する前記第1導電型のオーミック電極を備える、半導体装置。 - 請求項3又は請求項4に従属する請求項5に記載の半導体装置であって、さらに、

前記第1導電型のオーミック電極と前記第2導電型のオーミック電極とを電気的に接続する第1配線を備え、

前記第1配線は、絶縁膜を介して前記段差部の側面を覆っている、半導体装置。 - 請求項1から請求項6までのいずれか一項に記載の半導体装置であって、

前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されている、半導体装置。 - 請求項1から請求項7までのいずれか一項に記載の半導体装置であって、

前記第1窒化物半導体層は、窒化ガリウムにより形成されている、半導体装置。 - 請求項8に記載の半導体装置であって、

前記第1窒化物半導体層は、窒化ガリウム基板である、半導体装置。 - 請求項9に記載の半導体装置であって、

前記凸部の側面は、前記凸部の上面に対して傾斜している、半導体装置。 - 請求項1から請求項9までのいずれか一項に記載の半導体装置であって、

前記凸部の側面は、a面またはm面で構成され、前記凸部の上面は、c面で構成されている、半導体装置。 - 半導体装置の製造方法であって、

第1導電型の第1窒化物半導体層の面に突出する凸部を形成する工程と、

前記第1窒化物半導体層の面であって、前記凸部を備える面に、前記第1窒化物半導体層よりも不純物濃度が小さい前記第1導電型の第2窒化物半導体層と、第2導電型の第3窒化物半導体層と、をこの順に積層する工程と、

前記第3窒化物半導体層を貫通し、前記第2窒化物半導体層に達するトレンチを形成する工程と、

前記第1窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、第1の電極を形成する工程と、

積層方向において、前記凸部の上面と少なくとも一部が重なる位置であって、前記第3窒化物半導体層の面であり、前記第2窒化物半導体層と接する面とは反対側の面に、前記第2導電型のオーミック電極を形成する工程と、

前記トレンチに絶縁膜を介してゲート電極を形成する工程と、

前記第3窒化物半導体層の面であって、前記第2窒化物半導体層と接する面とは反対側の面に、前記第1導電型の第4窒化物半導体層を形成する工程と、

前記第4窒化物半導体層にソース電極を形成する工程と、

を有し、

前記第4窒化物半導体層は、前記積層方向において、前記凸部の上面と重ならない位置に配されており、

前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みは、前記凸部の上面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、

前記第1窒化物半導体層から前記第4窒化物半導体層までの窒化物半導体層と前記ゲート電極と前記第1の電極と前記ソース電極とから形成される縦型MOSトランジスタと、前記第1窒化物半導体層から前記第3窒化物半導体層までの窒化物半導体層と前記第1電極と前記第2導電型のオーミック電極から形成されるPN接合ダイオードである保護素子と、を備える半導体装置の製造方法。 - 請求項12に記載の半導体装置の製造方法であって、さらに、

前記凸部の上面と前記トレンチの底面との距離が、前記トレンチの底面が接する部分における前記第2窒化物半導体層の厚みよりも大きい、半導体装置の製造方法。 - 請求項12または請求項13に記載の半導体装置の製造方法であって、

前記第1窒化物半導体層から前記第4窒化物半導体層は、ガリウムを含む窒化物半導体により形成されている、半導体装置の製造方法。 - 請求項12から請求項14までのいずれか一項に記載の半導体装置の製造方法であって、

前記第1窒化物半導体層は、窒化ガリウム基板である、半導体装置の製造方法。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015059436A JP6319151B2 (ja) | 2015-03-23 | 2015-03-23 | 半導体装置および半導体装置の製造方法 |

| US15/065,708 US9704952B2 (en) | 2015-03-23 | 2016-03-09 | Semiconductor device and method for manufacturing semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2015059436A JP6319151B2 (ja) | 2015-03-23 | 2015-03-23 | 半導体装置および半導体装置の製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2016181534A JP2016181534A (ja) | 2016-10-13 |

| JP2016181534A5 JP2016181534A5 (ja) | 2017-07-27 |

| JP6319151B2 true JP6319151B2 (ja) | 2018-05-09 |

Family

ID=56975895

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2015059436A Active JP6319151B2 (ja) | 2015-03-23 | 2015-03-23 | 半導体装置および半導体装置の製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US9704952B2 (ja) |

| JP (1) | JP6319151B2 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| WO2016143265A1 (ja) * | 2015-03-11 | 2016-09-15 | パナソニック株式会社 | 窒化物半導体装置 |

| JP6581614B2 (ja) | 2017-03-14 | 2019-09-25 | 株式会社サイオクス | 半導体構造体の製造方法、検査方法、およびプログラム |

| TWI791871B (zh) | 2019-07-19 | 2023-02-11 | 力晶積成電子製造股份有限公司 | 通道全環繞半導體裝置及其製造方法 |

| TWI707438B (zh) * | 2019-07-19 | 2020-10-11 | 力晶積成電子製造股份有限公司 | 電路架構 |

| JP7337739B2 (ja) * | 2020-03-19 | 2023-09-04 | 株式会社東芝 | 半導体装置 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH025482A (ja) * | 1988-06-24 | 1990-01-10 | Hitachi Ltd | 縦形mosfet |

| JP4167313B2 (ja) * | 1997-03-18 | 2008-10-15 | 株式会社東芝 | 高耐圧電力用半導体装置 |

| JP4234016B2 (ja) * | 2001-07-12 | 2009-03-04 | ミシシッピ・ステイト・ユニバーシティ | 選択的エピタキシの使用による、炭化ケイ素におけるセルフアライントランジスタ |

| GB0312512D0 (en) * | 2003-05-31 | 2003-07-09 | Koninkl Philips Electronics Nv | Termination structures for semiconductor devices and the manufacture thereof |

| JP4561247B2 (ja) | 2004-08-31 | 2010-10-13 | 株式会社デンソー | 半導体装置およびその製造方法 |

| DE102006025958B3 (de) | 2006-06-02 | 2007-10-11 | Infineon Technologies Ag | Sanft schaltendes Halbleiterbauelement mit hoher Robustheit und geringen Schaltverlusten |

| JP2010114248A (ja) * | 2008-11-06 | 2010-05-20 | Toyota Central R&D Labs Inc | 半導体装置 |

| JP5582102B2 (ja) | 2010-07-01 | 2014-09-03 | 株式会社デンソー | 半導体装置 |

| CN104221151B (zh) * | 2012-03-16 | 2017-02-22 | 三菱电机株式会社 | 半导体装置及其制造方法 |

| JP6107597B2 (ja) * | 2013-03-26 | 2017-04-05 | 豊田合成株式会社 | 半導体装置およびその製造方法 |

| JP6092680B2 (ja) * | 2013-03-26 | 2017-03-08 | 新電元工業株式会社 | 半導体装置及び半導体装置の製造方法 |

-

2015

- 2015-03-23 JP JP2015059436A patent/JP6319151B2/ja active Active

-

2016

- 2016-03-09 US US15/065,708 patent/US9704952B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2016181534A (ja) | 2016-10-13 |

| US20160284843A1 (en) | 2016-09-29 |

| US9704952B2 (en) | 2017-07-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI770134B (zh) | 半導體裝置及半導體裝置之製造方法 | |

| JP5564791B2 (ja) | 化合物半導体装置及びその製造方法 | |

| JP6251071B2 (ja) | 半導体装置 | |

| US8963203B2 (en) | Nitride semiconductor device and method for manufacturing same | |

| US8530937B2 (en) | Compound semiconductor device having insulation film with different film thicknesses beneath electrodes | |

| JP7082508B2 (ja) | 窒化物半導体装置 | |

| US9583608B2 (en) | Nitride semiconductor device and method for manufacturing nitride semiconductor device | |

| JP2020184609A (ja) | 半導体デバイス及びその製造方法 | |

| JP6319151B2 (ja) | 半導体装置および半導体装置の製造方法 | |

| JP2010103425A (ja) | 窒化物半導体装置 | |

| KR20150093117A (ko) | 반도체 장치 | |

| JP6627441B2 (ja) | 半導体装置 | |

| JP2015099903A (ja) | 窒化物半導体装置およびその製造方法 | |

| CN112531025A (zh) | 高电子迁移率晶体管 | |

| CN103296077A (zh) | 半导体结构及其形成方法 | |

| JP2020061414A (ja) | 窒化物半導体装置および窒化物半導体装置の製造方法 | |

| CN112928161A (zh) | 高电子迁移率晶体管及其制作方法 | |

| CN112750700B (zh) | 高电子迁移率晶体管及其制作方法 | |

| CN112652659B (zh) | 高电子迁移率晶体管及其制作方法 | |

| JP2018157100A (ja) | 窒化物半導体装置 | |

| JP2021052025A (ja) | 半導体装置、半導体装置の製造方法及び電子装置 | |

| JP2017168583A (ja) | 半導体装置 | |

| JP6406080B2 (ja) | 半導体装置の製造方法 | |

| JP6176131B2 (ja) | 半導体装置の製造方法 | |

| JP6319141B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20170419 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20170615 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20171130 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20171226 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20180221 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20180306 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20180319 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6319151 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |