JP6122533B2 - 表示装置の駆動方法 - Google Patents

表示装置の駆動方法 Download PDFInfo

- Publication number

- JP6122533B2 JP6122533B2 JP2016113721A JP2016113721A JP6122533B2 JP 6122533 B2 JP6122533 B2 JP 6122533B2 JP 2016113721 A JP2016113721 A JP 2016113721A JP 2016113721 A JP2016113721 A JP 2016113721A JP 6122533 B2 JP6122533 B2 JP 6122533B2

- Authority

- JP

- Japan

- Prior art keywords

- period

- transistor

- selection period

- scanning line

- oxide semiconductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 238000000034 method Methods 0.000 title claims description 31

- 239000004065 semiconductor Substances 0.000 claims description 104

- 239000000758 substrate Substances 0.000 claims description 58

- 238000003079 width control Methods 0.000 claims description 5

- 239000010410 layer Substances 0.000 description 113

- 239000010408 film Substances 0.000 description 107

- 239000004973 liquid crystal related substance Substances 0.000 description 34

- 238000010586 diagram Methods 0.000 description 25

- 238000010438 heat treatment Methods 0.000 description 21

- 239000012535 impurity Substances 0.000 description 15

- 230000015572 biosynthetic process Effects 0.000 description 13

- XKRFYHLGVUSROY-UHFFFAOYSA-N Argon Chemical compound [Ar] XKRFYHLGVUSROY-UHFFFAOYSA-N 0.000 description 12

- 229910007541 Zn O Inorganic materials 0.000 description 12

- 239000001257 hydrogen Substances 0.000 description 12

- 229910052739 hydrogen Inorganic materials 0.000 description 12

- 238000004544 sputter deposition Methods 0.000 description 11

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 10

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 10

- 238000005259 measurement Methods 0.000 description 9

- 239000012298 atmosphere Substances 0.000 description 8

- 239000003990 capacitor Substances 0.000 description 8

- 230000006866 deterioration Effects 0.000 description 8

- 150000002431 hydrogen Chemical class 0.000 description 8

- 239000000126 substance Substances 0.000 description 8

- 239000013078 crystal Substances 0.000 description 7

- 239000007789 gas Substances 0.000 description 7

- XLOMVQKBTHCTTD-UHFFFAOYSA-N Zinc monoxide Chemical compound [Zn]=O XLOMVQKBTHCTTD-UHFFFAOYSA-N 0.000 description 6

- 229910052786 argon Inorganic materials 0.000 description 6

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 5

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 5

- 239000002585 base Substances 0.000 description 5

- 230000008859 change Effects 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 239000001307 helium Substances 0.000 description 5

- 229910052734 helium Inorganic materials 0.000 description 5

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 5

- 150000004678 hydrides Chemical class 0.000 description 5

- 125000002887 hydroxy group Chemical group [H]O* 0.000 description 5

- 229910052757 nitrogen Inorganic materials 0.000 description 5

- 230000001681 protective effect Effects 0.000 description 5

- 229910052710 silicon Inorganic materials 0.000 description 5

- 239000010703 silicon Substances 0.000 description 5

- 229910052814 silicon oxide Inorganic materials 0.000 description 5

- 239000011734 sodium Substances 0.000 description 5

- 229910052782 aluminium Inorganic materials 0.000 description 4

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 4

- 238000000151 deposition Methods 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 238000012538 light obscuration Methods 0.000 description 4

- 239000000463 material Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 229910052754 neon Inorganic materials 0.000 description 4

- GKAOGPIIYCISHV-UHFFFAOYSA-N neon atom Chemical compound [Ne] GKAOGPIIYCISHV-UHFFFAOYSA-N 0.000 description 4

- 239000012299 nitrogen atmosphere Substances 0.000 description 4

- 239000001301 oxygen Substances 0.000 description 4

- 229910052760 oxygen Inorganic materials 0.000 description 4

- 239000000565 sealant Substances 0.000 description 4

- 125000006850 spacer group Chemical group 0.000 description 4

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 3

- 229910052581 Si3N4 Inorganic materials 0.000 description 3

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 3

- 229910052783 alkali metal Inorganic materials 0.000 description 3

- 150000001340 alkali metals Chemical class 0.000 description 3

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 description 3

- 229910021417 amorphous silicon Inorganic materials 0.000 description 3

- 239000003086 colorant Substances 0.000 description 3

- 230000007547 defect Effects 0.000 description 3

- 238000005530 etching Methods 0.000 description 3

- 125000004435 hydrogen atom Chemical group [H]* 0.000 description 3

- AMGQUBHHOARCQH-UHFFFAOYSA-N indium;oxotin Chemical compound [In].[Sn]=O AMGQUBHHOARCQH-UHFFFAOYSA-N 0.000 description 3

- 239000011229 interlayer Substances 0.000 description 3

- 238000004519 manufacturing process Methods 0.000 description 3

- 239000011159 matrix material Substances 0.000 description 3

- 239000002184 metal Substances 0.000 description 3

- 229910044991 metal oxide Inorganic materials 0.000 description 3

- 150000004706 metal oxides Chemical group 0.000 description 3

- 239000000203 mixture Substances 0.000 description 3

- 229920002620 polyvinyl fluoride Polymers 0.000 description 3

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 3

- 239000010936 titanium Substances 0.000 description 3

- 229910052719 titanium Inorganic materials 0.000 description 3

- 239000011787 zinc oxide Substances 0.000 description 3

- VUFNLQXQSDUXKB-DOFZRALJSA-N 2-[4-[4-[bis(2-chloroethyl)amino]phenyl]butanoyloxy]ethyl (5z,8z,11z,14z)-icosa-5,8,11,14-tetraenoate Chemical compound CCCCC\C=C/C\C=C/C\C=C/C\C=C/CCCC(=O)OCCOC(=O)CCCC1=CC=C(N(CCCl)CCCl)C=C1 VUFNLQXQSDUXKB-DOFZRALJSA-N 0.000 description 2

- 208000005156 Dehydration Diseases 0.000 description 2

- 229910019092 Mg-O Inorganic materials 0.000 description 2

- 229910019395 Mg—O Inorganic materials 0.000 description 2

- GWEVSGVZZGPLCZ-UHFFFAOYSA-N Titan oxide Chemical compound O=[Ti]=O GWEVSGVZZGPLCZ-UHFFFAOYSA-N 0.000 description 2

- 238000009825 accumulation Methods 0.000 description 2

- 230000005540 biological transmission Effects 0.000 description 2

- PMHQVHHXPFUNSP-UHFFFAOYSA-M copper(1+);methylsulfanylmethane;bromide Chemical compound Br[Cu].CSC PMHQVHHXPFUNSP-UHFFFAOYSA-M 0.000 description 2

- 230000018044 dehydration Effects 0.000 description 2

- 238000006297 dehydration reaction Methods 0.000 description 2

- 238000006356 dehydrogenation reaction Methods 0.000 description 2

- 238000011161 development Methods 0.000 description 2

- 239000000428 dust Substances 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 230000001747 exhibiting effect Effects 0.000 description 2

- 229910052733 gallium Inorganic materials 0.000 description 2

- 229910003437 indium oxide Inorganic materials 0.000 description 2

- PJXISJQVUVHSOJ-UHFFFAOYSA-N indium(iii) oxide Chemical compound [O-2].[O-2].[O-2].[In+3].[In+3] PJXISJQVUVHSOJ-UHFFFAOYSA-N 0.000 description 2

- 239000011261 inert gas Substances 0.000 description 2

- 230000004298 light response Effects 0.000 description 2

- QGLKJKCYBOYXKC-UHFFFAOYSA-N nonaoxidotritungsten Chemical compound O=[W]1(=O)O[W](=O)(=O)O[W](=O)(=O)O1 QGLKJKCYBOYXKC-UHFFFAOYSA-N 0.000 description 2

- 239000002245 particle Substances 0.000 description 2

- 229920003023 plastic Polymers 0.000 description 2

- 239000004033 plastic Substances 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920006267 polyester film Polymers 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000008569 process Effects 0.000 description 2

- 239000002356 single layer Substances 0.000 description 2

- 239000010409 thin film Substances 0.000 description 2

- OGIDPMRJRNCKJF-UHFFFAOYSA-N titanium oxide Inorganic materials [Ti]=O OGIDPMRJRNCKJF-UHFFFAOYSA-N 0.000 description 2

- 229910001930 tungsten oxide Inorganic materials 0.000 description 2

- YVTHLONGBIQYBO-UHFFFAOYSA-N zinc indium(3+) oxygen(2-) Chemical compound [O--].[Zn++].[In+3] YVTHLONGBIQYBO-UHFFFAOYSA-N 0.000 description 2

- 239000004925 Acrylic resin Substances 0.000 description 1

- 229920000178 Acrylic resin Polymers 0.000 description 1

- 108091006149 Electron carriers Proteins 0.000 description 1

- 229910005191 Ga 2 O 3 Inorganic materials 0.000 description 1

- GYHNNYVSQQEPJS-UHFFFAOYSA-N Gallium Chemical compound [Ga] GYHNNYVSQQEPJS-UHFFFAOYSA-N 0.000 description 1

- 201000005569 Gout Diseases 0.000 description 1

- 244000126211 Hericium coralloides Species 0.000 description 1

- DGAQECJNVWCQMB-PUAWFVPOSA-M Ilexoside XXIX Chemical compound C[C@@H]1CC[C@@]2(CC[C@@]3(C(=CC[C@H]4[C@]3(CC[C@@H]5[C@@]4(CC[C@@H](C5(C)C)OS(=O)(=O)[O-])C)C)[C@@H]2[C@]1(C)O)C)C(=O)O[C@H]6[C@@H]([C@H]([C@@H]([C@H](O6)CO)O)O)O.[Na+] DGAQECJNVWCQMB-PUAWFVPOSA-M 0.000 description 1

- 108010083687 Ion Pumps Proteins 0.000 description 1

- 229920012266 Poly(ether sulfone) PES Polymers 0.000 description 1

- 239000004642 Polyimide Substances 0.000 description 1

- 241000270295 Serpentes Species 0.000 description 1

- 229910020944 Sn-Mg Inorganic materials 0.000 description 1

- 229910020923 Sn-O Inorganic materials 0.000 description 1

- ATJFFYVFTNAWJD-UHFFFAOYSA-N Tin Chemical compound [Sn] ATJFFYVFTNAWJD-UHFFFAOYSA-N 0.000 description 1

- 229910052784 alkaline earth metal Inorganic materials 0.000 description 1

- 150000001342 alkaline earth metals Chemical class 0.000 description 1

- 125000004432 carbon atom Chemical group C* 0.000 description 1

- 150000001875 compounds Chemical class 0.000 description 1

- 229920001940 conductive polymer Polymers 0.000 description 1

- 239000004020 conductor Substances 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 238000002425 crystallisation Methods 0.000 description 1

- 230000008025 crystallization Effects 0.000 description 1

- 230000001186 cumulative effect Effects 0.000 description 1

- 230000009977 dual effect Effects 0.000 description 1

- 230000005684 electric field Effects 0.000 description 1

- 230000005611 electricity Effects 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000002474 experimental method Methods 0.000 description 1

- 238000007667 floating Methods 0.000 description 1

- 239000011888 foil Substances 0.000 description 1

- 229910052738 indium Inorganic materials 0.000 description 1

- APFVFJFRJDLVQX-UHFFFAOYSA-N indium atom Chemical compound [In] APFVFJFRJDLVQX-UHFFFAOYSA-N 0.000 description 1

- 230000001678 irradiating effect Effects 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 229910052748 manganese Inorganic materials 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 230000000704 physical effect Effects 0.000 description 1

- 229920001721 polyimide Polymers 0.000 description 1

- 239000000843 powder Substances 0.000 description 1

- 238000012545 processing Methods 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 230000008439 repair process Effects 0.000 description 1

- 230000004044 response Effects 0.000 description 1

- 239000003566 sealing material Substances 0.000 description 1

- 238000001004 secondary ion mass spectrometry Methods 0.000 description 1

- 239000005361 soda-lime glass Substances 0.000 description 1

- 229910052708 sodium Inorganic materials 0.000 description 1

- 239000007787 solid Substances 0.000 description 1

- 230000003068 static effect Effects 0.000 description 1

- 238000003860 storage Methods 0.000 description 1

- 238000000859 sublimation Methods 0.000 description 1

- 230000008022 sublimation Effects 0.000 description 1

- JBQYATWDVHIOAR-UHFFFAOYSA-N tellanylidenegermanium Chemical compound [Te]=[Ge] JBQYATWDVHIOAR-UHFFFAOYSA-N 0.000 description 1

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 description 1

- 229910052721 tungsten Inorganic materials 0.000 description 1

- 239000010937 tungsten Substances 0.000 description 1

- 229910052724 xenon Inorganic materials 0.000 description 1

- FHNFHKCVQCLJFQ-UHFFFAOYSA-N xenon atom Chemical compound [Xe] FHNFHKCVQCLJFQ-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/36—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using liquid crystals

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2077—Display of intermediate tones by a combination of two or more gradation control methods

- G09G3/2081—Display of intermediate tones by a combination of two or more gradation control methods with combination of amplitude modulation and time modulation

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/2007—Display of intermediate tones

- G09G3/2018—Display of intermediate tones by time modulation using two or more time intervals

- G09G3/2022—Display of intermediate tones by time modulation using two or more time intervals using sub-frames

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/22—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources

- G09G3/30—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels

- G09G3/32—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED]

- G09G3/3208—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED]

- G09G3/3225—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters using controlled light sources using electroluminescent panels semiconductive, e.g. using light-emitting diodes [LED] organic, e.g. using organic light-emitting diodes [OLED] using an active matrix

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Computer Hardware Design (AREA)

- General Physics & Mathematics (AREA)

- Theoretical Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Control Of Indicators Other Than Cathode Ray Tubes (AREA)

- Liquid Crystal Display Device Control (AREA)

- Liquid Crystal (AREA)

- Thin Film Transistor (AREA)

Description

、各画素に設けられるトランジスタの半導体層に酸化物半導体を用いる構成における、表

示装置の駆動方法に関する。

用素子として用いる表示装置は、コンピュータのモニタやテレビジョン装置などの市販製

品で広く用いられている。アモルファスシリコンを用いたトランジスタの製造技術はすで

に確立され、60インチを超える液晶パネルも生産されている。

能化が望めないことから、ポリシリコンを用いた薄膜トランジスタの開発も進められてき

ている。しかし、ポリシリコンを作製するには結晶化工程が必要となり、これがトランジ

スタの特性バラツキの要因や、パネルサイズの大面積化に対する阻害要因となっていた。

っている。酸化物半導体の材料としては、酸化亜鉛を成分とするものが知られている。例

えば特許文献1には、電子キャリア濃度が1018/cm3未満である非晶質酸化物(酸

化物半導体)なるもので形成されたトランジスタを表示装置の駆動用素子として用いる構

成について開示している。

、外部環境に応じて諸特性が変化してしまう問題がある。具体的には、酸化物半導体を用

いて作製されるトランジスタに400nm以下の波長の光を照射しつつ、ゲートに負バイ

アスを印加すると、しきい値電圧が変動するといった特性の劣化を生じてしまう。

するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表示装

置の駆動方法を提供することを課題の一とする。

加されることでしきい値電圧が変動したトランジスタに対し、ゲートに20V以上の電圧

を1m秒以上印加することで、当該トランジスタのしきい値電圧の変動を変動前と同程度

の状態まで回復させる表示装置の駆動方法を提供するものである。具体的には、複数のフ

レーム期間により画像表示を行う表示装置の駆動方法において、各フレーム期間における

複数の走査線のうち、いずれか一の走査線を選択する期間で駆動用素子であるトランジス

タに対し、ゲートに20V以上の電圧を1m秒以上印加できるよう駆動する。そして複数

のフレーム期間にわたって、各行を選択していくことで全ての駆動用素子であるトランジ

スタに対し、ゲートに20V以上の電圧を1m秒以上印加できるようにし、トランジスタ

の特性劣化を回復するものである。

画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、第1の

フレーム期間では、第1の走査線を第1の選択期間で選択し、第1の走査線以外の第2の

走査線を含む走査線を第2の選択期間で選択し、第2のフレーム期間では、第2の走査線

を第1の選択期間で選択し、第2の走査線以外の第1の走査線を含む走査線を第2の選択

期間で選択し、第1の選択期間及び第2の選択期間は、画素に設けられる酸化物半導体を

有するトランジスタのゲートにハイレベルの電位を印加する期間であり、第1の選択期間

は、第2の選択期間より長い期間である表示装置の駆動方法である。

画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、第1の

フレーム期間では、第1の走査線を第1の選択期間で選択し、第1の走査線以外の第2の

走査線を含む走査線を第2の選択期間で選択し、第2のフレーム期間では、第2の走査線

を第1の選択期間で選択し、第2の走査線以外の第1の走査線を含む走査線を第2の選択

期間で選択し、第1の選択期間及び第2の選択期間は、画素に設けられる酸化物半導体を

有するトランジスタのゲートにハイレベルの電位を印加する期間であり、第1の選択期間

において、トランジスタに電気的に接続される信号線には、ローレベルの電位の画像信号

が供給され、第1の選択期間は、第2の選択期間より長い期間である表示装置の駆動方法

である。

る表示装置の駆動方法でもよい。

動方法でもよい。

具備するトランジスタにおいて、当該トランジスタの特性劣化を回復することの出来る表

示装置の駆動方法を提供することができる。

の形態は多くの異なる態様で実施することが可能であり、趣旨及びその範囲から逸脱する

ことなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。

従って本実施の形態及び実施例の記載内容に限定して解釈されるものではない。なお、以

下に説明する構成において、同様のものを指す符号は異なる図面間で共通の符号を用いて

示し、同一部分又は同様な機能を有する部分の詳細な説明は省略する。

り、又は領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしも

そのスケールに限定されない。

同を避けるために付したものであり、数的に限定するものではないことを付記する。

まず、表示装置における表示部(または画素部ともいう)の簡単な回路構成について図1

(A)に示す。

、表示部100における、走査線101(ゲート線)、信号線102(データ線)、画素

103、トランジスタ104、表示素子105を示している。なお表示部100には、n

本(nは2以上の自然数)の走査線、m本(mは2以上の自然数)の信号線が設けられ、

複数の画素103におけるトランジスタ104の導通状態を制御するものとして、以下説

明する。

選択するための配線である。具体的には、走査線101は、トランジスタ104のゲート

に接続されており、ゲートに印加する電位に応じて、トランジスタのソースとドレインと

の間の導通状態を制御する。なお図1(A)において、1行目の走査線はGOUT_1、

2行目の走査線はGOUT_2、i行目(iはn以下の自然数)の走査線はGOUT_i

、n行目の走査線はGOUT_nとして示している。

に画像信号を供給するための配線である。具体的には、信号線102は、トランジスタ1

04のソースまたはドレインの一方にあたる第1端子に接続されており、トランジスタの

導通状態に応じて画像信号をソースまたはドレインの他方にあたる第2端子に供給する。

そして表示素子105では、階調の制御が行われる。

102に接続されている。一例としては、画素103は、走査線101及び信号線102

の交差部に応じて設けられる構成となる。なお画素103は表示部100において、必ず

しも縦横に並べて配置する構成でなくてもよい。例えば画素103は、走査線101及び

/または信号線102を蛇行させた上で画素103をジグザグに配置する構成としてもよ

い。

るさを制御できる表示単位に相当するものとする。従って、カラー表示装置の場合には、

カラー画像の最小表示単位は、Rの画素とGの画素とBの画素との三画素から構成される

ものとする。ただし、カラー画像を表示するための色要素は、三色に限定されず、三色以

上を用いても良いし、RGB以外の色を用いても良い。

。トランジスタ104のゲートは走査線101に接続され、第1端子は信号線102に接

続され、第2端子は表示素子105に接続される。

ide Semiconductor)を用いたトランジスタであることを示している。

導体や、三元系金属酸化物であるIn−Ga−Zn−O系酸化物半導体、In−Sn−Z

n−O系酸化物半導体、In−Al−Zn−O系酸化物半導体、Sn−Ga−Zn−O系

酸化物半導体、Al−Ga−Zn−O系酸化物半導体、Sn−Al−Zn−O系酸化物半

導体や、二元系金属酸化物であるIn−Zn−O系酸化物半導体、Sn−Zn−O系酸化

物半導体、Al−Zn−O系酸化物半導体、Zn−Mg−O系酸化物半導体、Sn−Mg

−O系酸化物半導体、In−Mg−O系酸化物半導体、In−Ga−O系酸化物半導体や

、In−O系酸化物半導体、Sn−O系酸化物半導体、Zn−O系酸化物半導体などを用

いることができる。なお、本明細書においては、例えば、In−Sn−Ga−Zn−O系

酸化物半導体とは、インジウム(In)、錫(Sn)、ガリウム(Ga)、亜鉛(Zn)

を有する金属酸化物、という意味であり、その化学量論的組成比は特に問わない。また、

上記酸化物半導体は、珪素を含んでいてもよい。

きる。ここで、Mは、Ga、Al、Mn及びCoから選ばれた一又は複数の金属元素を示

す。

製するのが望ましい。酸化物半導体膜は、例えば、スパッタリング法などを用いて作製す

ることができる。

有する素子であり、ドレイン領域とソース領域の間にチャネル領域を有しており、ドレイ

ン領域とチャネル領域とソース領域とを介して電流を流すことができる。ここで、ソース

とドレインとは、トランジスタの構造や動作条件等によって変わるため、いずれがソース

またはドレインであるかを限定することが困難である。そこで、本明細書においては、ソ

ース及びドレインとして機能する領域を、ソースもしくはドレインと呼ばない場合がある

。その場合、一例としては、それぞれを一方の端子、他方の端子と表記する場合がある。

型の構造でもよい。または、チャネル領域が複数の領域に分かれて直列に接続された、ダ

ブルゲート型の構造でもよい。または、ゲート電極がチャネル領域の上下に設けられたデ

ュアルゲート型の構造でもよい。また、トランジスタを構成する半導体層を複数の島状の

半導体層にわけて形成し、スイッチング動作を実現しうるトランジスタ素子としてもよい

。

ば液晶素子を用いればよい。なお表示素子105としては、液晶素子の他にも例えばME

MS(Micro Electro Mechanical System)素子を用い

てもよい。なお表示素子105には液晶素子の他に保持容量を併設する構成もある。また

表示素子105としてEL素子等の自発光素子を用いる構成でもよい。

nによる画素の選択期間について模式的に示したものである。また図1(B)では、画像

表示を行うための複数のフレーム期間の一部について示している。そして図1(B)では

第1のフレーム期間乃至第nのフレーム期間にわたって順に示している。例えば第1のフ

レーム期間におけるGOUT_1が第1の選択期間T1で画素を選択し、次いでGOUT

_2が第2の選択期間T2で画素を選択していき、そして最終行であるGOUT_nが第

2の選択期間T2で画素を選択するものである。第1のフレーム期間乃至第nのフレーム

期間では、1行目からn行目までの走査線101の選択期間の累計によって、おおよその

1フレーム期間の長さが決まってくる。

ルの電位を走査線101に供給することで、トランジスタ104のソースとドレインとの

間を導通状態とする期間のことをいう。逆に、選択期間以外の期間となる非選択期間では

、ローレベルの電位を走査線101に供給し、トランジスタ104のソースとドレインと

の間が非導通状態となる。

1(第1の走査線ともいう)に接続された画素を第1の選択期間T1で選択し、1行目以

外の走査線に接続された画素を第2の選択期間T2で選択する。同様に第2のフレーム期

間において2行目の走査線GOUT_2(第2の走査線ともいう)に接続された画素を第

1の選択期間T1で選択し、2行目以外の走査線に接続された画素を第2の選択期間T2

で画素を選択する。同様に第iのフレーム期間においてi行目の走査線GOUT_iをに

接続された画素第1の選択期間T1で選択し、i行目以外の走査線に接続された画素を第

2の選択期間T2で選択する。同様に第nのフレーム期間においてn行目の走査線GOU

T_nに接続された画素を第1の選択期間T1で選択し、n行目以外の走査線に接続され

た画素を第2の選択期間T2で画素を選択する。

の行での走査線による選択期間を第2の選択期間T2としている。従って1行目からn行

目までの走査線101の選択期間の累計による1フレーム期間の長さは、第1のフレーム

期間乃至第nのフレーム期間で同じ長さとなる。

ートにハイレベルの電位を印加する期間であり、当該期間の長さを1m秒以上とするもの

である。そして第1の選択期間T1では、信号線より画像信号dataが表示素子側に供

給されることとなる。また図2(B)に示すように、第2の選択期間T2はトランジスタ

のゲートにハイレベルの電位を印加する期間であり、当該期間の長さを数μ秒程度とする

ものである。そして第2の選択期間T2では、信号線より画像信号dataが表示素子側

に供給されることとなる。また図2(C)に示すように1フレーム期間は、走査線101

のGOUT_1乃至GOUT_nによる第1の選択期間T1及び第2の選択期間T2の累

積期間により、1フレーム期間の長さが定まることとなる。

第1の選択期間T1を挿入するよう走査する。そして、ゲートに負バイアスを印加される

ことでしきい値電圧が変動した各行のトランジスタに対し、ゲートに20V以上の電圧を

1m秒以上印加することで、前述のしきい値電圧の変動を回復させることができるもので

ある。その結果、酸化物半導体を半導体層として具備するトランジスタにおいて、当該ト

ランジスタの特性劣化を回復することが出来る。

UT_1乃至GOUT_nによる第1の選択期間T1のみによる走査、及び第2の選択期

間T2のみによる走査について示している。

UT_nによる第1の選択期間T1の累積期間により、1フレーム期間の長さが定まるこ

ととなる。そのため、1m秒以上の期間を要する第1の選択期間T1が累積すると、1フ

レーム期間の長さが長くなり、複数のフレーム期間による動画表示等が困難になってしま

う。

GOUT_nによる第2の選択期間T2の累積期間により、1フレーム期間の長さが定ま

ることとなる。そのため、1秒間を60フレームで表示を行う場合1フレーム期間は16

.6m秒となり、数μ秒程度の期間を要する第2の選択期間T2が累積しても1フレーム

期間内に収めることができる。しかしながら当該駆動ではゲートに20V以上の電圧を1

m秒以上印加するといった駆動が困難となる。

駆動を複数のフレーム期間にわたって第1の選択期間T1を挿入するよう走査することで

、動画表示等が困難になることなく、ゲートに負バイアスを印加されることでしきい値電

圧が変動した各行のトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加す

ることで、前述のしきい値電圧の変動を回復させることができるものである。その結果、

酸化物半導体を半導体層として具備するトランジスタにおいて、当該トランジスタの特性

劣化を回復することが出来る。

わたって第1の選択期間T1を挿入する走査は、走査線101のGOUT_1乃至GOU

T_nのいずれか一に限らず、2行以上の走査線で行う構成としてもよい。具体的には、

図4(A)に示すように1フレーム期間において、走査線101のGOUT_i及びGO

UT_i+1を第1の選択期間T1とする構成であってもよい。また図4(A)に示した

ように連続する走査線に限らず、図4(B)に示すように離間した走査線である走査線1

01のGOUT_2及びGOUT_iを第1の選択期間T1とする構成であってもよい。

図4(B)は図4(A)に比べ、第1の選択期間T1で選択することによるちらつきを小

さくすることができる。

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

本実施の形態では上記実施の形態1で説明した表示素子として液晶素子を具備する液晶表

示装置の構成例を示し、液晶表示装置における反転駆動を行う際の駆動方法について説明

する。

複数の画素103を有する表示部100と、走査線駆動回路301と、信号線駆動回路3

02と、走査線駆動回路301によって電位が制御されるn本の走査線101と、信号線

駆動回路302によって電位が制御されるm本の信号線102と、を有する。

図である。図5(B)に示す画素103は、ゲートが走査線101に接続され、ソース及

びドレインの一方が信号線102に接続されたトランジスタ104と、一方の電極がトラ

ンジスタ104のソース及びドレインの他方に接続され、他方の電極が容量電位を供給す

る配線314(容量配線ともいう)に接続された容量素子312と、一方の電極(画素電

極ともいう)がトランジスタ104のソース及びドレインの他方及び容量素子312の一

方の電極に接続され、他方の電極(対向電極ともいう)が対向電位を供給する配線313

に接続された液晶素子311と、を有する。

向電位を同一の電位とすることが可能である。

て表したものである。図6においては、走査線101_j(jはn以下の自然数)、走査

線101_j+1、及び走査線101_j+2、並びに信号線102_k(kはm以下の

自然数)を示している。また図6では走査線101_j(jはn以下の自然数)及び信号

線102_kに接続される画素として画素103_j、走査線101_j+1(jはn以

下の自然数)及び信号線102_kに接続される画素として画素103_j+1、走査線

101_j+2(jはn以下の自然数)及び信号線102_kに接続される画素として画

素103_j+2を示している。なお各画素における表示素子としては、液晶素子を示し

ている。

イミングチャートについて示したものである。図7(A)ではiフレーム目において走査

線101_jにおける選択信号を第1の選択信号T1とし、i+1フレーム目において走

査線101_j+1における選択信号を第1の選択信号T1としている。なおiフレーム

目およびi+1フレーム目では、第1の選択期間T1以外の期間を第2の選択期間T2と

して走査線を走査している。

反転駆動のために、iフレーム目とi+1フレーム目において信号線102_kに供給す

る画像信号を反転する極性(図中、+記号、−記号で表記)となるよう、交互に切り替わ

る様子を示している。なお図7(A)では対向電位が供給される配線の電位を併せて示し

ており、ここでは一定の電位が供給される様子を表しているが、反転駆動の方式に応じて

適宜変動するよう動作させることも可能である。

ム期間にわたって第1の選択期間T1を挿入するよう走査することで、動画表示等が困難

になることなく、ゲートに負バイアスを印加されることでしきい値電圧が変動した各行の

トランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加することで、前述のし

きい値電圧の変動を回復させることができるものである。その結果、酸化物半導体を半導

体層として具備するトランジスタにおいて、当該トランジスタの特性劣化を回復すること

が出来る。

を行う際の画像信号の極性に関わらず、ローレベルの電位となるようにすることも可能で

ある。具体的なタイミングチャートについて図7(B)に示す。図7(B)に示すように

i+1フレーム目でハイレベルの電位となる画像信号の極性の場合に走査線101_j+

1が第1の選択信号T1によるハイレベルの電位の際に、ローレベルの電位となる画像信

号の極性とするものである。当該構成とすることにより、ゲートに負バイアスを印加する

際の負バイアスの大きさを大きくすることが出来るため、しきい値電圧が変動した各行の

トランジスタに対し、前述のしきい値電圧の変動を回復させる効果を高めることができる

。

動や、ソースライン反転駆動とすることもできる。またドット反転駆動とすることもでき

る。

である。

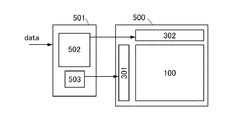

本実施の形態では、上記実施の形態で説明した駆動方法を実現しうる表示装置のブロック

図について説明する。

02と、表示部100と、を有する。

り入力される。また表示制御回路501は、走査線駆動回路301及び信号線駆動回路3

02を駆動するためのクロック信号を生成するクロック生成回路502と、走査線駆動回

路301に出力するクロック信号のパルス幅を制御するためのパルス幅制御回路503と

、を有する。

子基板500上に設けられる構成でなくてもよい。

1及び信号線駆動回路302を駆動するための回路である。またパルス幅制御回路503

は、走査線駆動回路301でのフレーム毎に第1の選択信号が各行に出力されるようクロ

ック信号のパルス幅を制御するための回路である。具体的には、第1の選択信号T1を出

力する期間ではクロック信号がハイレベルの電位を保持するように走査線駆動回路301

に出力するクロック信号のパルス幅を制御する。

ーム期間毎に切り替えて出力できる回路であれば、本実施の形態以外の構成であってもよ

い。

である。

本実施の形態では、液晶素子を有する素子基板について説明する。なお本実施の形態で説

明する液晶素子を有する素子基板を液晶表示装置という。

(A2)は、第1の基板4001上に形成されたトランジスタ4010、4011及び液

晶素子4013を、第2の基板4006との間にシール材4005によって封止したパネ

ルの上面図であり、図9(B)は、図9(A1)(A2)のM−Nにおける断面図に相当

する。

ようにして、シール材4005が設けられている。また、画素部4002と、走査線駆動

回路4004の上に第2の基板4006が設けられている。画素部4002と、走査線駆

動回路4004とは、第1の基板4001とシール材4005と第2の基板4006とに

よって、液晶層4008と共に封止されている。

域とは異なる領域に、別途用意された基板上に単結晶半導体膜又は多結晶半導体膜で形成

された信号線駆動回路4003が実装されている。なお、図9(A2)は信号線駆動回路

の一部を第1の基板4001上に酸化物半導体を用いたトランジスタで形成する例であり

、第1の基板4001上に信号線駆動回路4003bが形成され、かつ別途用意された基

板上に単結晶半導体膜又は多結晶半導体膜で形成された信号線駆動回路4003aが実装

されている。

ワイヤボンディング方法、またはTAB方法などを用いることができる。図9(A1)は

、COG方法により信号線駆動回路4003を実装する例であり、図9(A2)は、TA

B方法により信号線駆動回路4003を実装する例である。

、トランジスタを複数有しており、図9(B)では、画素部4002に含まれるトランジ

スタ4010と、走査線駆動回路4004に含まれるトランジスタ4011とを例示して

いる。トランジスタ4010、4011上には絶縁層4020、4021が設けられてい

る。

膜を用いて半導体層を作製するものである。

画素電極層4030は、トランジスタ4010と電気的に接続されている。液晶素子40

13は、画素電極層4030、共通電極層4031、及び液晶層4008を含む。

すなわち水平な方向)な電界を生じさせて、基板と平行な面内で液晶分子を動かして、階

調を制御する方式を用いることができる。このような方式として、本実施の形態では、図

9に示すようなIPS(In Plane Switching)モードで用いる電極構

成を適用する場合を示している。なお、IPSモードに限られず、FFS(Fringe

Field Switching)モードで用いる電極構成を適用することも可能であ

る。なお特にブルー相を示す液晶層を用いる構成は、高い印加電圧により配向を制御する

必要があり、上記実施の形態1で説明した、ゲートに負バイアスを印加されることでしき

い値電圧が変動したトランジスタに対し、ゲートに20V以上の電圧を1m秒以上印加す

ることで、当該トランジスタのしきい値電圧の変動を変動前と同程度の状態まで回復させ

る表示装置の駆動方法を行うのに好適である。

スチックなどを用いることができる。プラスチックとしては、ポリエーテルサルフォン(

PES)、ポリイミド、FRP(Fiberglass−Reinforced Pla

stics)板、PVF(ポリビニルフルオライド)フィルム、ポリエステルフィルムま

たはアクリル樹脂フィルムを用いることができる。また、アルミニウムホイルをPVFフ

ィルムやポリエステルフィルムで挟んだ構造のシートを用いることもできる。

ペーサ4035は、絶縁膜を選択的にエッチングすることにより設けることができる。な

お、柱状のスペーサ4035の代わりに、球状のスペーサを用いていてもよい。

てもよいが、特に限定されない。

ぐためのものであり、緻密な膜が好ましい。保護膜は、スパッタ法を用いて、酸化珪素膜

、窒化珪素膜、酸化窒化珪素膜、窒化酸化珪素膜、酸化アルミニウム膜、窒化アルミニウ

ム膜、酸化窒化アルミニウム膜、又は窒化酸化アルミニウム膜の単層、又は積層で形成す

ればよい。

い。

、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、

酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(ITO)、インジウム亜鉛

酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用

いることができる。

ともいう)を含む導電性組成物を用いて形成することができる。

4002に与えられる各種信号及び電位は、FPC4018から供給されている。

対して、駆動回路保護用の保護回路を同一基板上に設けることが好ましい。保護回路は、

酸化物半導体を用いた非線形素子を用いて構成することが好ましい。

子電極4016は、トランジスタ4010、4011のソース電極層及びドレイン電極層

と同じ導電膜で形成されている。

て電気的に接続されている。

装している例を示しているが、この構成に限定されない。走査線駆動回路を別途形成して

実装してもよいし、信号線駆動回路の一部または走査線駆動回路の一部のみを別途形成し

て実装してもよい。

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

本実施の形態では実施の形態4でも説明したトランジスタの半導体層に用いる酸化物半導

体膜の作製方法の具体例について説明する。

℃以下、好ましくは300℃以上500℃以下となるように加熱する。

分に除去された高純度ガスを導入し、上記ターゲットを用いて基板上に酸化物半導体膜を

成膜する。成膜室内の残留水分を除去するためには、排気手段として、クライオポンプ、

イオンポンプ、チタンサブリメーションポンプなどの吸着型の真空ポンプを用いることが

望ましい。また、排気手段は、ターボポンプにコールドトラップを加えたものであっても

よい。クライオポンプを用いて排気した成膜室は、例えば、水素、水、水酸基または水素

化物などの不純物(より好ましくは炭素原子を含む化合物も)などが除去されているため

、当該成膜室で成膜した酸化物半導体膜に含まれる水素、水、水酸基または水素化物など

の不純物の濃度を低減することができる。

む物質が混入するおそれがあるため、基板を上述の温度で加熱することが好ましい。基板

を上述の温度で加熱して、酸化物半導体膜の成膜を行うことにより、基板温度は高温とな

るため、水素結合は熱により切断され、水素原子を含む物質が酸化物半導体膜に取り込ま

れにくい。したがって、基板が上述の温度で加熱された状態で、酸化物半導体膜の成膜を

行うことにより、酸化物半導体膜に含まれる水素、水、水酸基または水素化物などの不純

物の濃度を十分に低減することができる。また、スパッタリングによる損傷を軽減するこ

とができる。

直流(DC)電源を0.5kW、基板温度を400℃、成膜雰囲気を酸素(酸素流量比率

100%)雰囲気とする。なお、パルス直流電源を用いると、成膜時に発生する粉状物質

(パーティクル、ごみともいう)が軽減でき、膜厚分布も均一となるため好ましい。

プラズマを発生させる逆スパッタを行い、酸化物半導体膜の被形成表面に付着している粉

状物質(パーティクル、ごみともいう)を除去することが好ましい。逆スパッタとは、基

板に電圧を印加し、基板近傍にプラズマを形成して、基板側の表面を改質する方法である

。なお、アルゴンに代えて、窒素、ヘリウム、酸素などのガスを用いてもよい。

物半導体膜の加工は、所望の形状のマスクを酸化物半導体膜上に形成した後、当該酸化物

半導体膜をエッチングすることによって行うことができる。

うことによって、酸化物半導体膜中に含まれる水素原子を含む物質をさらに除去し、酸化

物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。熱

処理の温度は、不活性ガス雰囲気下、250℃以上700℃以下、好ましくは450℃以

上600℃以下、または基板の歪み点未満とする。不活性ガス雰囲気としては、窒素、ま

たは希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素

などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や

、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好

ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ま

しくは0.1ppm以下)とする。

450℃、1時間の条件で行うことができる。この間、酸化物半導体膜は大気に触れさせ

ず、水や水素の混入が生じないようにする。

い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することが

できる。

水化処理や、脱水素化処理などと呼ぶこともできる。当該熱処理は、例えば、酸化物半導

体膜を島状に加工する前、ゲート絶縁膜の形成後などのタイミングにおいて行うことも可

能である。また、このような脱水化処理、脱水素化処理は、一回に限らず複数回行っても

良い。

ていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石

灰ガラスも使えると指摘されている(神谷、野村、細野、「アモルファス酸化物半導体の

物性とデバイス開発の現状」、固体物理、2009年9月号、Vol.44、p.621

−633)。しかし、このような指摘は適切でない。アルカリ金属は酸化物半導体を構成

する元素ではないため、不純物である。アルカリ土類金属も、酸化物半導体を構成する元

素ではない場合において、不純物となる。特に、アルカリ金属のうちNaは、酸化物半導

体膜に接する絶縁膜が酸化物である場合、当該絶縁膜中に拡散してNa+となる。また、

Naは、酸化物半導体膜内において、酸化物半導体を構成する金属と酸素の結合を分断す

る、或いは、その結合中に割り込む。その結果、例えば、閾値電圧がマイナス方向にシフ

トすることによるノーマリオン化、移動度の低下等の、トランジスタの特性の劣化が起こ

り、加えて、特性のばらつきも生じる。この不純物によりもたらされるトランジスタの特

性の劣化と、特性のばらつきは、酸化物半導体膜中の水素の濃度が十分に低い場合におい

て顕著に現れる。従って、酸化物半導体膜中の水素の濃度が5×1019/cm3以下、

特に5×1018/cm3以下である場合には、上記不純物の濃度を低減することが望ま

しい。具体的に、二次イオン質量分析法によるNa濃度の測定値は、5×1016/cm

3以下、好ましくは1×1016/cm3以下、更に好ましくは1×1015/cm3以

下とするとよい。同様に、Li濃度の測定値は、5×1015/cm3以下、好ましくは

1×1015/cm3以下とするとよい。同様に、K濃度の測定値は、5×1015/c

m3以下、好ましくは1×1015/cm3以下とするとよい。

て結晶性を有する酸化物半導体膜を用いることが好ましい。結晶性を有する酸化物半導体

膜を用いることで、トランジスタの信頼性(ゲート・バイアス・ストレス耐性)を高める

ことができるからである。

軸配向を有した結晶(C Axis Aligned Crystalline:CAA

Cとも呼ぶ)を含む酸化物を用いることが好ましい。

よってCAAC膜を得るには酸化物半導体膜の堆積初期段階において六方晶の結晶が形成

されるようにすることと、当該結晶を種として結晶が成長されるようにすることが肝要で

ある。そのためには、ターゲットと基板の距離を広くとり(例えば、150mm〜200

mm程度)、基板加熱温度を100℃〜500℃、好適には200℃〜400℃、さらに

好適には250℃〜300℃にすると好ましい。また、これに加えて、成膜時の基板加熱

温度よりも高い温度で、堆積された酸化物半導体膜を熱処理することで膜中に含まれるミ

クロな欠陥や、積層界面の欠陥を修復することができる。

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

本実施の形態では、液晶表示装置の画素の平面図及び断面図の一例について図面を用いて

説明する。

)は図10(A)の一点鎖線A−Bにおける断面図である。

層1201を含む)は、図中上下方向(列方向)に延伸するように配置されている。走査

線となる配線層(ゲート電極層1202を含む)は、図中左右方向(行方向)に延伸する

ように配置されている。コモン線となる配線層(ゲート電極層1203を含む)は、ソー

ス電極層1201aに概略直交する方向(図中左右方向(行方向))に延伸するように配

置されている。容量配線層1204は、ゲート電極層1202及びゲート電極層1203

に概略平行な方向であって、且つ、ソース電極層1201aに概略直交する方向(図中左

右方向(行方向))に延伸するように配置されている。

スタ1205が設けられている。トランジスタ1205上には、絶縁膜1207、絶縁膜

1208、及び層間膜1209が設けられている。

れる第1の電極層として透明電極層1210、ゲート電極層1203に接続される第2の

電極層として透明電極層1211を有する。透明電極層1210及び透明電極層1211

は、互いの櫛歯状の形状が噛み合うように、且つ離間して設けられている。トランジスタ

1205上の絶縁膜1207、絶縁膜1208、及び層間膜1209には、開口(コンタ

クトホール)が形成されている。開口(コンタクトホール)において、透明電極層121

0とトランジスタ1205とが接続されている。

してゲート電極層1202上に配置された半導体層1213を有し、半導体層1213に

接してソース電極層1201a及びドレイン電極層1201bを有する。また、容量配線

層1204、ゲート絶縁層1212、及びドレイン電極層1201bが積層して、容量素

子1215を形成している。

2の基板1219とが重畳ように配置されている。

ンジスタを用いる例を示したが、本明細書に開示する表示装置に適用できるトランジスタ

の構造は特に限定されない。例えば、ゲート絶縁層を介してゲート電極層が半導体層の上

側に配置されるトップゲート構造のトランジスタ、及び、ゲート絶縁層を介してゲート電

極層が半導体層の下側に配置されるボトムゲート構造のスタガ型トランジスタ及びプレー

ナ型トランジスタなどを用いることができる。

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

本実施の形態においては、電子機器の例について説明する。

ができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン

受信機ともいう)、コンピュータ用のモニタ、電子ペーパー、デジタルカメラ、デジタル

ビデオカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう

)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機等の大型ゲーム機等が挙

げられる。

に用いることが可能である。例えば、電子ペーパーを用いて、電子書籍(電子ブック)、

ポスター、電車等の乗り物の車内広告、クレジットカード等の各種カードにおける表示等

に適用することができる。電子機器の一例を図11に示す。

700及び筐体1701の2つの筐体で構成されている。筐体1700及び筐体1701

は、蝶番1704により一体になっており、開閉動作を行うことができる。このような構

成により、書籍のような動作を行うことが可能となる。

込まれている。表示部1702及び表示部1703は、続き画面を表示する構成としても

よいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすること

で、例えば右側の表示部(図11(A)では表示部1702)に文章を表示し、左側の表

示部(図11(A)では表示部1703)に画像を表示することができる。

、図11(B)に示すデジタルフォトフレームは、筐体1711に表示部1712が組み

込まれている。表示部1712は、各種画像を表示することが可能であり、例えば、デジ

タルカメラ等で撮影した画像データを表示させることで、通常の写真立てと同様に機能さ

せることができる。

に示すテレビジョン装置は、筐体1721に表示部1722が組み込まれている。表示部

1722により、映像を表示することが可能である。また、ここでは、スタンド1723

により筐体1721を支持した構成を示している。表示部1722は、上記実施の形態に

示した表示装置を適用することができる。

携帯電話機は、筐体1731に組み込まれた表示部1732の他、操作ボタン1733、

操作ボタン1737、外部接続ポート1734、スピーカ1735、及びマイク1736

等を備えている。

接触により、表示部1732の表示内容を操作することができる。また、電話の発信、或

いはメールの作成等は、表示部1732を指等で接触することにより行うことができる。

対して、適宜、組み合わせ、又は置き換えなどを自由に行うことができる。

ことでトランジスタのしきい値電圧の変動を回復させることに関して、トランジスタのゲ

ートに対して印加する正の電圧の印加条件を変化させる実験に基づいた測定結果の説明を

行う。

性を測定した。具体的には、正の電圧の印加時間を変化させることで、光照射前後の光応

答特性の測定結果はどのように変化するのか、について測定した。

ネルエッチ型と呼ばれる逆スタガ型薄膜トランジスタである。トランジスタ810は、ガ

ラス基板800上に、下地膜811、ゲート電極層801、ゲート絶縁層802、酸化物

半導体層803、ソース電極層805a、ドレイン電極層805b、絶縁層807を含ん

で構成されている。

805a及びドレイン電極層805bはヘビのように曲がりくねった形状を有する。また

ソース電極層805aとゲート電極層801とが重畳する長さ、及びドレイン電極層80

5bとゲート電極層801とが重畳する長さは、特に限定していない。

下地膜811は、膜厚100nmの窒化シリコン膜、膜厚150nmの酸化窒化シリコン

膜を、順に積層して形成した。

厚100nmのタングステン膜を単層で形成した。なお、ゲート電極層801の端部はテ

ーパー形状とした。ここで、テーパー角は、例えば、30°以上60°以下とした。テー

パー角とは、テーパー形状を有する層(例えば、ゲート電極層801)を、その断面(基

板の表面と直交する面)に垂直な方向から観察した際に、当該層の側面と底面がなす傾斜

角を示す。更に、ゲート電極層801を覆うように、ゲート絶縁層802を形成した。ゲ

ート絶縁層802は、膜厚100nmの酸化窒化シリコン膜を、単層で形成した。

する酸化物ターゲットを用いたスパッタ法により、ガラス基板(126.6mm×126

.6mm)上に膜厚35nmのIn−Ga−Zn−O膜を成膜した。なお、In−Ga−

Zn−O膜の成膜条件は、成膜温度200℃、圧力0.6Pa、電力5kWとした。

またはヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれない雰囲気、例

えば雰囲気の露点が−40℃以下、好ましくは−60℃以下であることが好ましい。また

は、加熱処理装置に導入する窒素、またはヘリウム、ネオン、アルゴン等の希ガスの純度

を、6N(99.9999%)以上好ましくは7N(99.99999%)以上(即ち不

純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

ム膜、膜厚100nmのチタン膜の順に積層して導電膜の積層を形成した。フォトリソグ

ラフィ工程により導電膜の積層上にレジストマスクを形成し、選択的にエッチングを行っ

てソース電極層805a及びドレイン電極層805bを形成した後、レジストマスクを除

去した。その後、窒素雰囲気下で300℃、1時間の加熱処理を行った。

ドレイン電極層805b上に膜厚400nmの酸化シリコン膜を成膜した。なお、酸化シ

リコン膜の成膜条件は、成膜温度200℃、時間2分、電力6kWとした。その後、窒素

雰囲気で300℃、1時間の加熱処理を行った。上述のように作製されたトランジスタ8

10を図12に示す。

3に、光照射前後の光応答特性(光電流−時間特性)の測定結果を示す。図13に示す各

図において、縦軸を光電流値、横軸を時刻としている。なお、図13に示すように光応答

特性を、第1の期間51、第2の期間52、第3の期間53、第4の期間54に分割して

説明する。第1の期間51は、光照射期間でありゲートに電圧を印加していない期間であ

る。第2の期間52は、光消灯期間でありゲートに電圧を印加していない期間である。第

3の期間53は、光消灯期間でありゲートに正の電圧を印加している期間である。第4の

期間54は、光消灯期間でありゲートに電圧を印加していない期間である。

光消灯中)、dは正の電圧印加終了時間(光消灯中)、eは測定終了時間をそれぞれ示す

ものとする。

なわち光照射開始時間aから、測定終了時間eまでの時間は1620秒であった。第1の

期間51では、測定対象のトランジスタ810の遮光されていない側から、すなわち当該

トランジスタ810の基板表面に対して垂直な方向から光照射を行った。なお、照射強度

は、3.5mW/cm2であり、光源は波長400nm以下の光として、分光した光を照

射することのできる波長400nmのキセノン光源を利用した。また第3の期間53では

、正の電圧を印加した。本実施例において正の電圧を印加するとは、測定対象のトランジ

スタ810のゲートに20V以上の電圧として、ここでは20Vの電圧をそれぞれ印加す

ることを意味する。なお測定対象のトランジスタ810のゲートに正の電圧を印加する際

、トランジスタのソースを0V、ドレインを0Vとしている。

53である正の電圧の印加時間を、500m秒、100m秒、10m秒、1m秒、100

μ秒、10μ秒、の6段階で変化させて測定を行った。図14(A)は、印加時間500

m秒、図14(B)は、印加時間100m秒、図14(C)は、印加時間10m秒、図1

4(D)は、印加時間1m秒、図14(E)は、印加時間100μ秒、図14(F)は、

印加時間10μ秒における、光照射前後の光応答特性の測定結果をそれぞれ示している。

、正の電圧印加後の光電流の値が低減できることがわかった。すなわち、トランジスタの

ゲートに正の電圧を印加することで光照射による光電流が上昇してしまう特性劣化の回復

を確認できた。特にゲートに負バイアスを印加されることでしきい値電圧が変動したトラ

ンジスタに対してゲートに20V以上の電圧を1m秒以上印加する場合には、光照射によ

る光電流が上昇してしまう特性劣化の回復を顕著に確認できた。

T2 期間

51 期間

52 期間

53 期間

54 期間

100 表示部

101 走査線

101_j 走査線

102 信号線

102_k 信号線

103 画素

103_j 画素

104 トランジスタ

105 表示素子

301 走査線駆動回路

302 信号線駆動回路

311 液晶素子

312 容量素子

313 配線

314 配線

500 素子基板

501 表示制御回路

502 クロック生成回路

503 パルス幅制御回路

800 ガラス基板

801 ゲート電極層

802 ゲート絶縁層

803 酸化物半導体層

805a ソース電極層

805b ドレイン電極層

807 絶縁層

810 トランジスタ

811 下地膜

1201a ソース電極層

1201b ドレイン電極層

1202 ゲート電極層

1203 ゲート電極層

1204 容量配線層

1206 トランジスタ

1207 絶縁膜

1208 絶縁膜

1209 層間膜

1210 透明電極層

1211 透明電極層

1212 ゲート絶縁層

1213 半導体層

1215 容量素子

1217 液晶層

1218 基板

1219 基板

1700 筐体

1701 筐体

1702 表示部

1703 表示部

1704 蝶番

1711 筐体

1712 表示部

1721 筐体

1722 表示部

1723 スタンド

1731 筐体

1732 表示部

1733 操作ボタン

1734 外部接続ポート

1735 スピーカ

1736 マイク

1737 操作ボタン

4001 基板

4002 画素部

4003 信号線駆動回路

4003a 信号線駆動回路

4003b 信号線駆動回路

4004 走査線駆動回路

4005 シール材

4006 基板

4008 液晶層

4010 トランジスタ

4011 トランジスタ

4013 液晶素子

4015 接続端子電極

4016 端子電極

4018 FPC

4019 異方性導電膜

4020 絶縁層

4030 画素電極層

4031 共通電極層

4035 スペーサ

Claims (1)

- 複数のフレーム期間において複数の走査線及び信号線により、複数の画素に供給する画像信号を制御して画像表示を行う表示装置の駆動方法において、

前記表示装置は、素子基板および表示制御回路を有し、

前記素子基板は、表示部と、走査線駆動回路と、信号線駆動回路と、を有し、

前記表示制御回路は、クロック生成回路と、パルス幅制御回路と、を有し、

前記表示部は、前記複数の走査線と、前記複数の信号線と、前記複数の画素と、を有し、

前記複数の走査線の各々は、酸化物半導体を有するトランジスタのゲートに電気的に接続されており、

前記表示装置において、第1のフレーム期間では、第1の走査線を第1の選択期間で選択し、前記第1の走査線以外の第2の走査線を第2の選択期間で選択し、

前記表示装置において、第2のフレーム期間では、前記第2の走査線を前記第1の選択期間で選択し、前記第2の走査線以外の前記第1の走査線を前記第2の選択期間で選択し、

前記第1のフレーム期間における前記第1の選択期間は、前記第1の走査線にハイレベルの20V以上の電圧を印加する期間であり、

前記第1のフレーム期間における前記第2の選択期間は、前記第2の走査線にハイレベルの電位を印加する期間であり、

前記第1の選択期間は、1ms以上の期間であり、

前記第1の選択期間は、前記第2の選択期間より長い期間であり、

前記第1の選択期間及び前記第2の選択期間の長さは、前記パルス幅制御回路により制御されることを特徴とする表示装置の駆動方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010248017 | 2010-11-05 | ||

| JP2010248017 | 2010-11-05 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011238196A Division JP6010291B2 (ja) | 2010-11-05 | 2011-10-31 | 表示装置の駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2016167096A JP2016167096A (ja) | 2016-09-15 |

| JP6122533B2 true JP6122533B2 (ja) | 2017-04-26 |

Family

ID=46019186

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011238196A Active JP6010291B2 (ja) | 2010-11-05 | 2011-10-31 | 表示装置の駆動方法 |

| JP2016113721A Active JP6122533B2 (ja) | 2010-11-05 | 2016-06-07 | 表示装置の駆動方法 |

Family Applications Before (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011238196A Active JP6010291B2 (ja) | 2010-11-05 | 2011-10-31 | 表示装置の駆動方法 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US8754839B2 (ja) |

| JP (2) | JP6010291B2 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR102279459B1 (ko) | 2012-10-24 | 2021-07-19 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| CN103793089B (zh) * | 2012-10-30 | 2017-05-17 | 宸鸿科技(厦门)有限公司 | 触控面板 |

| TWI636309B (zh) | 2013-07-25 | 2018-09-21 | 日商半導體能源研究所股份有限公司 | 液晶顯示裝置及電子裝置 |

| US9360564B2 (en) * | 2013-08-30 | 2016-06-07 | Semiconductor Energy Laboratory Co., Ltd. | Imaging device |

| US9590110B2 (en) * | 2013-09-10 | 2017-03-07 | Semiconductor Energy Laboratory Co., Ltd. | Ultraviolet light sensor circuit |

| JP2015072310A (ja) * | 2013-10-01 | 2015-04-16 | 株式会社ジャパンディスプレイ | 液晶表示装置 |

| US10699634B2 (en) | 2014-04-21 | 2020-06-30 | Joled Inc. | Display device and method for driving display device |

| JP6383573B2 (ja) * | 2014-06-05 | 2018-08-29 | 株式会社ジャパンディスプレイ | 表示装置 |

| TWI792916B (zh) | 2016-06-24 | 2023-02-11 | 日商半導體能源研究所股份有限公司 | 顯示裝置、電子裝置 |

Family Cites Families (114)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS60198861A (ja) | 1984-03-23 | 1985-10-08 | Fujitsu Ltd | 薄膜トランジスタ |

| JPH0244256B2 (ja) | 1987-01-28 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn2o5deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244258B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn3o6deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPS63210023A (ja) | 1987-02-24 | 1988-08-31 | Natl Inst For Res In Inorg Mater | InGaZn↓4O↓7で示される六方晶系の層状構造を有する化合物およびその製造法 |

| JPH0244260B2 (ja) | 1987-02-24 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn5o8deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244262B2 (ja) | 1987-02-27 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn6o9deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH0244263B2 (ja) | 1987-04-22 | 1990-10-03 | Kagaku Gijutsucho Mukizaishitsu Kenkyushocho | Ingazn7o10deshimesarerurotsuhoshokeinosojokozoojusurukagobutsuoyobisonoseizoho |

| JPH022511A (ja) * | 1988-06-15 | 1990-01-08 | Fujitsu Ltd | アクティブマトリクス型液晶表示装置の駆動装置 |

| JPH05251705A (ja) | 1992-03-04 | 1993-09-28 | Fuji Xerox Co Ltd | 薄膜トランジスタ |

| JPH0667154A (ja) * | 1992-08-14 | 1994-03-11 | Semiconductor Energy Lab Co Ltd | 液晶電気光学装置の駆動方法 |

| JP3479375B2 (ja) | 1995-03-27 | 2003-12-15 | 科学技術振興事業団 | 亜酸化銅等の金属酸化物半導体による薄膜トランジスタとpn接合を形成した金属酸化物半導体装置およびそれらの製造方法 |

| JPH11505377A (ja) | 1995-08-03 | 1999-05-18 | フィリップス エレクトロニクス ネムローゼ フェンノートシャップ | 半導体装置 |

| JP3625598B2 (ja) | 1995-12-30 | 2005-03-02 | 三星電子株式会社 | 液晶表示装置の製造方法 |

| JP3305990B2 (ja) * | 1996-09-05 | 2002-07-24 | 株式会社東芝 | 液晶表示装置およびその駆動方法 |

| JP2000019484A (ja) * | 1998-06-30 | 2000-01-21 | Toshiba Corp | 液晶表示装置及びその駆動方法 |

| JP4170454B2 (ja) | 1998-07-24 | 2008-10-22 | Hoya株式会社 | 透明導電性酸化物薄膜を有する物品及びその製造方法 |

| JP2000150861A (ja) | 1998-11-16 | 2000-05-30 | Tdk Corp | 酸化物薄膜 |

| JP3276930B2 (ja) | 1998-11-17 | 2002-04-22 | 科学技術振興事業団 | トランジスタ及び半導体装置 |

| KR20000074515A (ko) * | 1999-05-21 | 2000-12-15 | 윤종용 | 액정표시장치 및 그의 화상 신호 전송 배선 형성 방법 |

| TW460731B (en) | 1999-09-03 | 2001-10-21 | Ind Tech Res Inst | Electrode structure and production method of wide viewing angle LCD |

| JP3622592B2 (ja) * | 1999-10-13 | 2005-02-23 | 株式会社日立製作所 | 液晶表示装置 |

| JP4089858B2 (ja) | 2000-09-01 | 2008-05-28 | 国立大学法人東北大学 | 半導体デバイス |

| KR20020038482A (ko) | 2000-11-15 | 2002-05-23 | 모리시타 요이찌 | 박막 트랜지스터 어레이, 그 제조방법 및 그것을 이용한표시패널 |

| JP3997731B2 (ja) | 2001-03-19 | 2007-10-24 | 富士ゼロックス株式会社 | 基材上に結晶性半導体薄膜を形成する方法 |

| JP2002289859A (ja) | 2001-03-23 | 2002-10-04 | Minolta Co Ltd | 薄膜トランジスタ |

| JP3925839B2 (ja) | 2001-09-10 | 2007-06-06 | シャープ株式会社 | 半導体記憶装置およびその試験方法 |

| JP4090716B2 (ja) | 2001-09-10 | 2008-05-28 | 雅司 川崎 | 薄膜トランジスタおよびマトリクス表示装置 |

| JP4164562B2 (ja) | 2002-09-11 | 2008-10-15 | 独立行政法人科学技術振興機構 | ホモロガス薄膜を活性層として用いる透明薄膜電界効果型トランジスタ |

| EP1443130B1 (en) | 2001-11-05 | 2011-09-28 | Japan Science and Technology Agency | Natural superlattice homologous single crystal thin film, method for preparation thereof, and device using said single crystal thin film |

| JP4083486B2 (ja) | 2002-02-21 | 2008-04-30 | 独立行政法人科学技術振興機構 | LnCuO(S,Se,Te)単結晶薄膜の製造方法 |

| JP3671012B2 (ja) * | 2002-03-07 | 2005-07-13 | 三洋電機株式会社 | 表示装置 |

| US7049190B2 (en) | 2002-03-15 | 2006-05-23 | Sanyo Electric Co., Ltd. | Method for forming ZnO film, method for forming ZnO semiconductor layer, method for fabricating semiconductor device, and semiconductor device |

| JP3933591B2 (ja) | 2002-03-26 | 2007-06-20 | 淳二 城戸 | 有機エレクトロルミネッセント素子 |

| US7339187B2 (en) | 2002-05-21 | 2008-03-04 | State Of Oregon Acting By And Through The Oregon State Board Of Higher Education On Behalf Of Oregon State University | Transistor structures |

| JP2004022625A (ja) | 2002-06-13 | 2004-01-22 | Murata Mfg Co Ltd | 半導体デバイス及び該半導体デバイスの製造方法 |

| US7105868B2 (en) | 2002-06-24 | 2006-09-12 | Cermet, Inc. | High-electron mobility transistor with zinc oxide |

| US7067843B2 (en) | 2002-10-11 | 2006-06-27 | E. I. Du Pont De Nemours And Company | Transparent oxide semiconductor thin film transistors |

| JP4166105B2 (ja) | 2003-03-06 | 2008-10-15 | シャープ株式会社 | 半導体装置およびその製造方法 |

| JP2004273732A (ja) | 2003-03-07 | 2004-09-30 | Sharp Corp | アクティブマトリクス基板およびその製造方法 |

| JP4108633B2 (ja) | 2003-06-20 | 2008-06-25 | シャープ株式会社 | 薄膜トランジスタおよびその製造方法ならびに電子デバイス |

| US7262463B2 (en) | 2003-07-25 | 2007-08-28 | Hewlett-Packard Development Company, L.P. | Transistor including a deposited channel region having a doped portion |

| JP4163081B2 (ja) * | 2003-09-22 | 2008-10-08 | アルプス電気株式会社 | 液晶表示装置の駆動方法及び液晶表示装置 |

| KR20070116889A (ko) | 2004-03-12 | 2007-12-11 | 도꾸리쯔교세이호징 가가꾸 기쥬쯔 신꼬 기꼬 | 아몰퍼스 산화물 박막의 기상성막방법 |

| US7297977B2 (en) | 2004-03-12 | 2007-11-20 | Hewlett-Packard Development Company, L.P. | Semiconductor device |

| US7282782B2 (en) | 2004-03-12 | 2007-10-16 | Hewlett-Packard Development Company, L.P. | Combined binary oxide semiconductor device |

| US7145174B2 (en) | 2004-03-12 | 2006-12-05 | Hewlett-Packard Development Company, Lp. | Semiconductor device |

| US7211825B2 (en) | 2004-06-14 | 2007-05-01 | Yi-Chi Shih | Indium oxide-based thin film transistors and circuits |

| JP4572095B2 (ja) * | 2004-07-15 | 2010-10-27 | Nec液晶テクノロジー株式会社 | 液晶表示装置、携帯機器及び液晶表示装置の駆動方法 |

| JP2006100760A (ja) | 2004-09-02 | 2006-04-13 | Casio Comput Co Ltd | 薄膜トランジスタおよびその製造方法 |

| US7285501B2 (en) | 2004-09-17 | 2007-10-23 | Hewlett-Packard Development Company, L.P. | Method of forming a solution processed device |

| US7298084B2 (en) | 2004-11-02 | 2007-11-20 | 3M Innovative Properties Company | Methods and displays utilizing integrated zinc oxide row and column drivers in conjunction with organic light emitting diodes |

| KR100939998B1 (ko) | 2004-11-10 | 2010-02-03 | 캐논 가부시끼가이샤 | 비정질 산화물 및 전계 효과 트랜지스터 |

| JP5126729B2 (ja) | 2004-11-10 | 2013-01-23 | キヤノン株式会社 | 画像表示装置 |

| US7791072B2 (en) | 2004-11-10 | 2010-09-07 | Canon Kabushiki Kaisha | Display |

| AU2005302964B2 (en) | 2004-11-10 | 2010-11-04 | Canon Kabushiki Kaisha | Field effect transistor employing an amorphous oxide |

| US7829444B2 (en) | 2004-11-10 | 2010-11-09 | Canon Kabushiki Kaisha | Field effect transistor manufacturing method |

| US7863611B2 (en) | 2004-11-10 | 2011-01-04 | Canon Kabushiki Kaisha | Integrated circuits utilizing amorphous oxides |

| US7453065B2 (en) | 2004-11-10 | 2008-11-18 | Canon Kabushiki Kaisha | Sensor and image pickup device |

| EP1810335B1 (en) | 2004-11-10 | 2020-05-27 | Canon Kabushiki Kaisha | Light-emitting device |

| US7579224B2 (en) | 2005-01-21 | 2009-08-25 | Semiconductor Energy Laboratory Co., Ltd. | Method for manufacturing a thin film semiconductor device |

| TWI562380B (en) | 2005-01-28 | 2016-12-11 | Semiconductor Energy Lab Co Ltd | Semiconductor device, electronic device, and method of manufacturing semiconductor device |

| TWI481024B (zh) | 2005-01-28 | 2015-04-11 | 半導體能源研究所股份有限公司 | 半導體裝置,電子裝置,和半導體裝置的製造方法 |

| JP4850422B2 (ja) * | 2005-01-31 | 2012-01-11 | パイオニア株式会社 | 表示装置およびその駆動方法 |

| US7858451B2 (en) | 2005-02-03 | 2010-12-28 | Semiconductor Energy Laboratory Co., Ltd. | Electronic device, semiconductor device and manufacturing method thereof |

| US7948171B2 (en) | 2005-02-18 | 2011-05-24 | Semiconductor Energy Laboratory Co., Ltd. | Light emitting device |

| US20060197092A1 (en) | 2005-03-03 | 2006-09-07 | Randy Hoffman | System and method for forming conductive material on a substrate |

| US8681077B2 (en) | 2005-03-18 | 2014-03-25 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, and display device, driving method and electronic apparatus thereof |

| WO2006105077A2 (en) | 2005-03-28 | 2006-10-05 | Massachusetts Institute Of Technology | Low voltage thin film transistor with high-k dielectric material |

| US7645478B2 (en) | 2005-03-31 | 2010-01-12 | 3M Innovative Properties Company | Methods of making displays |

| US8300031B2 (en) | 2005-04-20 | 2012-10-30 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device comprising transistor having gate and drain connected through a current-voltage conversion element |

| JP2006344849A (ja) | 2005-06-10 | 2006-12-21 | Casio Comput Co Ltd | 薄膜トランジスタ |

| US7402506B2 (en) | 2005-06-16 | 2008-07-22 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7691666B2 (en) | 2005-06-16 | 2010-04-06 | Eastman Kodak Company | Methods of making thin film transistors comprising zinc-oxide-based semiconductor materials and transistors made thereby |

| US7507618B2 (en) | 2005-06-27 | 2009-03-24 | 3M Innovative Properties Company | Method for making electronic devices using metal oxide nanoparticles |

| KR100711890B1 (ko) | 2005-07-28 | 2007-04-25 | 삼성에스디아이 주식회사 | 유기 발광표시장치 및 그의 제조방법 |

| JP2007059128A (ja) | 2005-08-23 | 2007-03-08 | Canon Inc | 有機el表示装置およびその製造方法 |

| JP4850457B2 (ja) | 2005-09-06 | 2012-01-11 | キヤノン株式会社 | 薄膜トランジスタ及び薄膜ダイオード |

| JP2007073705A (ja) | 2005-09-06 | 2007-03-22 | Canon Inc | 酸化物半導体チャネル薄膜トランジスタおよびその製造方法 |

| JP5116225B2 (ja) | 2005-09-06 | 2013-01-09 | キヤノン株式会社 | 酸化物半導体デバイスの製造方法 |

| JP4280736B2 (ja) | 2005-09-06 | 2009-06-17 | キヤノン株式会社 | 半導体素子 |

| EP1998374A3 (en) | 2005-09-29 | 2012-01-18 | Semiconductor Energy Laboratory Co, Ltd. | Semiconductor device having oxide semiconductor layer and manufacturing method thereof |

| JP2007108457A (ja) * | 2005-10-14 | 2007-04-26 | Nec Electronics Corp | 表示装置、データドライバic、ゲートドライバic、及び走査線駆動回路 |

| JP5037808B2 (ja) | 2005-10-20 | 2012-10-03 | キヤノン株式会社 | アモルファス酸化物を用いた電界効果型トランジスタ、及び該トランジスタを用いた表示装置 |

| KR101397571B1 (ko) | 2005-11-15 | 2014-05-22 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체장치 및 그의 제조방법 |

| TWI292281B (en) | 2005-12-29 | 2008-01-01 | Ind Tech Res Inst | Pixel structure of active organic light emitting diode and method of fabricating the same |

| US7867636B2 (en) | 2006-01-11 | 2011-01-11 | Murata Manufacturing Co., Ltd. | Transparent conductive film and method for manufacturing the same |

| JP4977478B2 (ja) | 2006-01-21 | 2012-07-18 | 三星電子株式会社 | ZnOフィルム及びこれを用いたTFTの製造方法 |

| US7576394B2 (en) | 2006-02-02 | 2009-08-18 | Kochi Industrial Promotion Center | Thin film transistor including low resistance conductive thin films and manufacturing method thereof |

| US7977169B2 (en) | 2006-02-15 | 2011-07-12 | Kochi Industrial Promotion Center | Semiconductor device including active layer made of zinc oxide with controlled orientations and manufacturing method thereof |

| KR20070101595A (ko) | 2006-04-11 | 2007-10-17 | 삼성전자주식회사 | ZnO TFT |

| US20070252928A1 (en) | 2006-04-28 | 2007-11-01 | Toppan Printing Co., Ltd. | Structure, transmission type liquid crystal display, reflection type display and manufacturing method thereof |

| JP5028033B2 (ja) | 2006-06-13 | 2012-09-19 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4999400B2 (ja) | 2006-08-09 | 2012-08-15 | キヤノン株式会社 | 酸化物半導体膜のドライエッチング方法 |

| JP4609797B2 (ja) | 2006-08-09 | 2011-01-12 | Nec液晶テクノロジー株式会社 | 薄膜デバイス及びその製造方法 |

| JP4332545B2 (ja) | 2006-09-15 | 2009-09-16 | キヤノン株式会社 | 電界効果型トランジスタ及びその製造方法 |

| JP5164357B2 (ja) | 2006-09-27 | 2013-03-21 | キヤノン株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP4274219B2 (ja) | 2006-09-27 | 2009-06-03 | セイコーエプソン株式会社 | 電子デバイス、有機エレクトロルミネッセンス装置、有機薄膜半導体装置 |

| US7622371B2 (en) | 2006-10-10 | 2009-11-24 | Hewlett-Packard Development Company, L.P. | Fused nanocrystal thin film semiconductor and method |

| US7772021B2 (en) | 2006-11-29 | 2010-08-10 | Samsung Electronics Co., Ltd. | Flat panel displays comprising a thin-film transistor having a semiconductive oxide in its channel and methods of fabricating the same for use in flat panel displays |

| JP2008140684A (ja) | 2006-12-04 | 2008-06-19 | Toppan Printing Co Ltd | カラーelディスプレイおよびその製造方法 |

| KR101303578B1 (ko) | 2007-01-05 | 2013-09-09 | 삼성전자주식회사 | 박막 식각 방법 |

| US8207063B2 (en) | 2007-01-26 | 2012-06-26 | Eastman Kodak Company | Process for atomic layer deposition |

| KR100851215B1 (ko) | 2007-03-14 | 2008-08-07 | 삼성에스디아이 주식회사 | 박막 트랜지스터 및 이를 이용한 유기 전계 발광표시장치 |

| JP2008242388A (ja) * | 2007-03-29 | 2008-10-09 | Seiko Epson Corp | 有機トランジスタの駆動方法及び電気泳動表示装置 |

| US7795613B2 (en) | 2007-04-17 | 2010-09-14 | Toppan Printing Co., Ltd. | Structure with transistor |

| KR101325053B1 (ko) | 2007-04-18 | 2013-11-05 | 삼성디스플레이 주식회사 | 박막 트랜지스터 기판 및 이의 제조 방법 |

| KR20080094300A (ko) | 2007-04-19 | 2008-10-23 | 삼성전자주식회사 | 박막 트랜지스터 및 그 제조 방법과 박막 트랜지스터를포함하는 평판 디스플레이 |

| KR101334181B1 (ko) | 2007-04-20 | 2013-11-28 | 삼성전자주식회사 | 선택적으로 결정화된 채널층을 갖는 박막 트랜지스터 및 그제조 방법 |

| US8274078B2 (en) | 2007-04-25 | 2012-09-25 | Canon Kabushiki Kaisha | Metal oxynitride semiconductor containing zinc |

| KR101345376B1 (ko) | 2007-05-29 | 2013-12-24 | 삼성전자주식회사 | ZnO 계 박막 트랜지스터 및 그 제조방법 |

| JP5160836B2 (ja) * | 2007-08-08 | 2013-03-13 | ルネサスエレクトロニクス株式会社 | テレビジョン受像機 |

| JP5215158B2 (ja) | 2007-12-17 | 2013-06-19 | 富士フイルム株式会社 | 無機結晶性配向膜及びその製造方法、半導体デバイス |

| JP4623179B2 (ja) | 2008-09-18 | 2011-02-02 | ソニー株式会社 | 薄膜トランジスタおよびその製造方法 |

| JP5451280B2 (ja) | 2008-10-09 | 2014-03-26 | キヤノン株式会社 | ウルツ鉱型結晶成長用基板およびその製造方法ならびに半導体装置 |

-

2011

- 2011-10-31 JP JP2011238196A patent/JP6010291B2/ja active Active

- 2011-11-01 US US13/286,289 patent/US8754839B2/en not_active Expired - Fee Related

-

2014

- 2014-06-03 US US14/294,204 patent/US9070329B2/en active Active

-

2016

- 2016-06-07 JP JP2016113721A patent/JP6122533B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| US20120113086A1 (en) | 2012-05-10 |

| JP2016167096A (ja) | 2016-09-15 |

| US9070329B2 (en) | 2015-06-30 |

| US8754839B2 (en) | 2014-06-17 |

| US20140285414A1 (en) | 2014-09-25 |

| JP2012113292A (ja) | 2012-06-14 |

| JP6010291B2 (ja) | 2016-10-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6122533B2 (ja) | 表示装置の駆動方法 | |

| JP7412500B2 (ja) | 半導体装置、表示装置 | |

| JP7578771B2 (ja) | 表示装置 | |

| JP7656687B2 (ja) | 表示装置 | |

| JP6778780B2 (ja) | 半導体装置の作製方法 | |

| JP6856795B2 (ja) | 半導体装置及び表示装置 | |

| JP5677671B2 (ja) | 表示装置及びその駆動方法 | |

| JP2025081400A (ja) | 表示装置 | |

| TWI720331B (zh) | 顯示裝置和其製造方法 | |

| TWI613825B (zh) | 具有層疊佈線的半導體裝置及其製造方法 | |

| KR102228220B1 (ko) | 반도체 장치의 제작 방법 | |

| JP6351947B2 (ja) | 液晶表示装置の作製方法 | |

| CN103728757A (zh) | 液晶显示装置、触摸屏 | |

| JP2011170328A (ja) | 表示装置の駆動方法、及び液晶表示装置 | |

| JP2012023359A (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20160608 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20170307 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20170331 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 6122533 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |