JP5975605B2 - 薄膜電池の製造方法および薄膜電池 - Google Patents

薄膜電池の製造方法および薄膜電池 Download PDFInfo

- Publication number

- JP5975605B2 JP5975605B2 JP2011111705A JP2011111705A JP5975605B2 JP 5975605 B2 JP5975605 B2 JP 5975605B2 JP 2011111705 A JP2011111705 A JP 2011111705A JP 2011111705 A JP2011111705 A JP 2011111705A JP 5975605 B2 JP5975605 B2 JP 5975605B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- thin film

- regions

- layers

- film battery

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000010409 thin film Substances 0.000 title claims description 59

- 238000004519 manufacturing process Methods 0.000 title claims description 24

- 239000000758 substrate Substances 0.000 claims description 67

- 238000000034 method Methods 0.000 claims description 16

- 238000000926 separation method Methods 0.000 claims description 15

- 238000007740 vapor deposition Methods 0.000 claims description 14

- 238000009413 insulation Methods 0.000 claims description 2

- 238000000059 patterning Methods 0.000 description 29

- 239000000463 material Substances 0.000 description 13

- 239000003792 electrolyte Substances 0.000 description 11

- 238000002161 passivation Methods 0.000 description 7

- 238000011065 in-situ storage Methods 0.000 description 6

- 239000004065 semiconductor Substances 0.000 description 6

- 238000005229 chemical vapour deposition Methods 0.000 description 5

- 238000000151 deposition Methods 0.000 description 5

- 238000000231 atomic layer deposition Methods 0.000 description 4

- 230000015572 biosynthetic process Effects 0.000 description 4

- 238000005520 cutting process Methods 0.000 description 4

- 230000008021 deposition Effects 0.000 description 4

- 239000010408 film Substances 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 238000005240 physical vapour deposition Methods 0.000 description 4

- 239000011521 glass Substances 0.000 description 3

- 238000003698 laser cutting Methods 0.000 description 3

- 229910001416 lithium ion Inorganic materials 0.000 description 3

- 230000000873 masking effect Effects 0.000 description 3

- 229910052710 silicon Inorganic materials 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000012876 topography Methods 0.000 description 3

- HBBGRARXTFLTSG-UHFFFAOYSA-N Lithium ion Chemical compound [Li+] HBBGRARXTFLTSG-UHFFFAOYSA-N 0.000 description 2

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 230000008901 benefit Effects 0.000 description 2

- 239000000919 ceramic Substances 0.000 description 2

- 238000002955 isolation Methods 0.000 description 2

- 238000001459 lithography Methods 0.000 description 2

- 230000003287 optical effect Effects 0.000 description 2

- 230000001681 protective effect Effects 0.000 description 2

- 229910018072 Al 2 O 3 Inorganic materials 0.000 description 1

- 229910018119 Li 3 PO 4 Inorganic materials 0.000 description 1

- WHXSMMKQMYFTQS-UHFFFAOYSA-N Lithium Chemical compound [Li] WHXSMMKQMYFTQS-UHFFFAOYSA-N 0.000 description 1

- 229910000676 Si alloy Inorganic materials 0.000 description 1

- ZVLDJSZFKQJMKD-UHFFFAOYSA-N [Li].[Si] Chemical compound [Li].[Si] ZVLDJSZFKQJMKD-UHFFFAOYSA-N 0.000 description 1

- 238000010521 absorption reaction Methods 0.000 description 1

- 239000010405 anode material Substances 0.000 description 1

- 238000000149 argon plasma sintering Methods 0.000 description 1

- 239000006182 cathode active material Substances 0.000 description 1

- 238000001311 chemical methods and process Methods 0.000 description 1

- 238000011109 contamination Methods 0.000 description 1

- 230000007423 decrease Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000005530 etching Methods 0.000 description 1

- 238000001704 evaporation Methods 0.000 description 1

- 238000010438 heat treatment Methods 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 230000000670 limiting effect Effects 0.000 description 1

- 229910052744 lithium Inorganic materials 0.000 description 1

- 238000006263 metalation reaction Methods 0.000 description 1

- 238000004377 microelectronic Methods 0.000 description 1

- 230000036961 partial effect Effects 0.000 description 1

- 239000002245 particle Substances 0.000 description 1

- 229920002120 photoresistant polymer Polymers 0.000 description 1

- 229920000642 polymer Polymers 0.000 description 1

- 230000002829 reductive effect Effects 0.000 description 1

- 238000001228 spectrum Methods 0.000 description 1

- 238000004544 sputter deposition Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01M—PROCESSES OR MEANS, e.g. BATTERIES, FOR THE DIRECT CONVERSION OF CHEMICAL ENERGY INTO ELECTRICAL ENERGY

- H01M10/00—Secondary cells; Manufacture thereof

- H01M10/04—Construction or manufacture in general

- H01M10/0436—Small-sized flat cells or batteries for portable equipment

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01M—PROCESSES OR MEANS, e.g. BATTERIES, FOR THE DIRECT CONVERSION OF CHEMICAL ENERGY INTO ELECTRICAL ENERGY

- H01M10/00—Secondary cells; Manufacture thereof

- H01M10/05—Accumulators with non-aqueous electrolyte

- H01M10/052—Li-accumulators

- H01M10/0525—Rocking-chair batteries, i.e. batteries with lithium insertion or intercalation in both electrodes; Lithium-ion batteries

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01M—PROCESSES OR MEANS, e.g. BATTERIES, FOR THE DIRECT CONVERSION OF CHEMICAL ENERGY INTO ELECTRICAL ENERGY

- H01M10/00—Secondary cells; Manufacture thereof

- H01M10/42—Methods or arrangements for servicing or maintenance of secondary cells or secondary half-cells

- H01M10/425—Structural combination with electronic components, e.g. electronic circuits integrated to the outside of the casing

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02E—REDUCTION OF GREENHOUSE GAS [GHG] EMISSIONS, RELATED TO ENERGY GENERATION, TRANSMISSION OR DISTRIBUTION

- Y02E60/00—Enabling technologies; Technologies with a potential or indirect contribution to GHG emissions mitigation

- Y02E60/10—Energy storage using batteries

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02P—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN THE PRODUCTION OR PROCESSING OF GOODS

- Y02P70/00—Climate change mitigation technologies in the production process for final industrial or consumer products

- Y02P70/50—Manufacturing or production processes characterised by the final manufactured product

Landscapes

- Engineering & Computer Science (AREA)

- Chemical & Material Sciences (AREA)

- Manufacturing & Machinery (AREA)

- Chemical Kinetics & Catalysis (AREA)

- Electrochemistry (AREA)

- General Chemical & Material Sciences (AREA)

- Materials Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Secondary Cells (AREA)

- Primary Cells (AREA)

- Connection Of Batteries Or Terminals (AREA)

Description

(a)基板の表面上または該基板の表面に設けられた絶縁層上に第1の層を設け、該第1の層上に第2の層を設けるステップ。

(b)前記第2の層の複数の領域を横方向に相互に分離し、かつ/または、前記第1の層の複数の領域を横方向に相互に分離し、該第2の層の複数の領域を横方向に相互に分離するステップ。

(c)前記第2の層上に第3の層を設け、該第3の層上に第4の層を設けるステップ。

(d)前記第4の層の複数の領域を横方向に相互に分離し、かつ/または、前記第3の層の複数の領域を横方向に相互に分離し、該第4の層の複数の領域を横方向に相互に分離するステップ。

・シリコン基板。場合によっては、集積回路または集積マイクロメカニカル素子が集積されたシリコン基板、または、スルーコンタクトが設けられたシリコン基板。

・ガラス基板。場合によっては、スルーコンタクトが集積されたガラス基板。

・セラミック

・温度安定性のポリマー。

・とりわけ遮蔽マスクと比較して、層のパターニングを格段に良好に行えるようになること。基板上(とりわけウェハ上)におけるスペースを格段に効率的に利用し、切断くずを低減することができる。

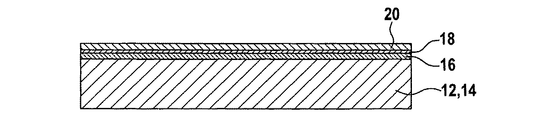

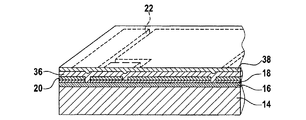

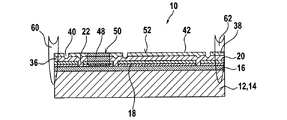

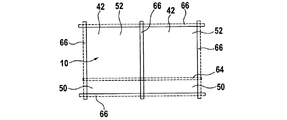

16 絶縁層

18 第1の層

20 第2の層

22,40 切り込み

24,26,28 分離によって形成された領域

30,32,34 分離によって形成された領域

36 第3の層

38 第4の層

42,44,46 分離によって形成された領域

48 スルーコンタクト

50 カソードのコンタクト面

52 アノードのコンタクト面

56 3次元パターニングされた基板

58 トレンチ

60 アノードの切断線

62 カソードの切断線

Claims (7)

- 薄膜電池(10)の製造方法であって、

前記薄膜電池(10)の積層体を形成するために、基板(14)の基板表面に複数の層(16,18,20,36,38)を連続的に設け、

設けた前記層のうち少なくとも1つの層(18,20,38)の複数の異なる領域(24,26,28;30,32,34;42,44,46)を横方向に相互に分離する製造方法において、

前記複数の異なる領域をレーザビームによって分離し、

前記複数の層のうち1つの層(20,38)はカソード層であり、該複数の層のうち1つの層(38,20)はアノード層であり、

前記カソード層および/または前記アノード層は、前記積層体の埋め込み層(18,20,36)として設け、該カソード層および/または該アノード層と外部とのコンタクトのためにスルーコンタクト(48)を作製することを特徴とする、製造方法。 - ・第1の層(18)を前記基板表面上に設けるか、または、該基板表面上に設けられた絶縁層(16)上に設け、第2の層(20)を該第1の層(18)に設けるステップと、

・前記第2の層(20)の複数の領域(24,26,28)を横方向に相互に分離するか、または、前記第1の層(18)の複数の領域(30,32,34)を横方向に相互に分離しかつ該第2の層(20)の複数の領域(24,26,28)を横方向に相互に分離するステップと、

・前記第2の層(20)に第3の層(36)を設け、該第3の層(36)に第4の層(38)を設けるステップと、

・前記第4の層(38)の複数の領域(42,44,46)を横方向に相互に分離するか、または、前記第3の層(36)の複数の領域を横方向に分離しかつ該第4の層(38)の複数の領域を横方向に相互に分離するステップ

とを有する、請求項1記載の製造方法。 - さらに、前記複数の層(16,18,20,36,38)を完全または部分的にカバーするカバー層を設ける、請求項1または2記載の製造方法。

- 前記複数の層のうち少なくとも1つの層の複数の領域(24,26,28;30,32,34;42,44,46)の分離は、該少なくとも1つの層(18,20,38)の分離すべき領域(24,24,28;30,32,34;42,44,46)を相互に電気的に分離する絶縁分離である、請求項1から3までのいずれか1項記載の製造方法。

- 前記複数の層(16,18,20,36,38)のうち少なくとも1つの層を気相成膜設備で設け、前記複数の層のうち少なくとも1つの層(18,20,38)の複数の領域(18,20,38)の分離も該気相成膜設備で行う、請求項1から4までのいずれか1項記載の製造方法。

- 3次元パターニングされた基板表面を設け、該基板表面に前記複数の層(16,18,20,36,38)を設ける、請求項1から5までのいずれか1項記載の製造方法。

- 設けられた層(16,18,20,36,38)のうち少なくとも1つの層をレーザビームによって、少なくとも局所的に除去する、請求項1から6までのいずれか1項記載の製造方法。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| DE102010029060A DE102010029060A1 (de) | 2010-05-18 | 2010-05-18 | Verfahren zur Herstellung einer Dünnschichtbatterie und entsprechende Dünnschichtbatterie |

| DE102010029060.2 | 2010-05-18 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011243577A JP2011243577A (ja) | 2011-12-01 |

| JP2011243577A5 JP2011243577A5 (ja) | 2014-07-24 |

| JP5975605B2 true JP5975605B2 (ja) | 2016-08-23 |

Family

ID=44898714

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2011111705A Expired - Fee Related JP5975605B2 (ja) | 2010-05-18 | 2011-05-18 | 薄膜電池の製造方法および薄膜電池 |

Country Status (5)

| Country | Link |

|---|---|

| JP (1) | JP5975605B2 (ja) |

| CN (1) | CN102255102B (ja) |

| DE (1) | DE102010029060A1 (ja) |

| FR (1) | FR2960346B1 (ja) |

| IT (1) | ITMI20110836A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE102014209263A1 (de) * | 2014-05-15 | 2015-11-19 | Fraunhofer-Gesellschaft zur Förderung der angewandten Forschung e.V. | Mikrobatterie und Verfahren zum Herstellen einer Mikrobatterie |

| TW201622228A (zh) * | 2014-08-27 | 2016-06-16 | 應用材料股份有限公司 | 三維薄膜電池 |

| DE102015204844A1 (de) * | 2015-03-18 | 2016-09-22 | Robert Bosch Gmbh | Verfahren und Vorrichtung zum Verbinden von Batteriezellen sowie Batteriepack, Batteriemodul, Batterie sowie Fahrzeug |

| JP6287946B2 (ja) * | 2015-05-08 | 2018-03-07 | トヨタ自動車株式会社 | 電池用積層体の製造方法 |

| FR3039005A1 (fr) * | 2015-07-13 | 2017-01-20 | St Microelectronics Tours Sas | Batterie en couches minces autosupportee et procede de fabrication d'une telle batterie |

| DE102016118755B4 (de) | 2015-10-05 | 2019-08-14 | Lpkf Laser & Electronics Ag | 3D-Dünnschichtbatterie und ein Verfahren und Substrat zu deren Herstellung |

| JP6683001B2 (ja) * | 2016-05-10 | 2020-04-15 | トヨタ自動車株式会社 | 固体電池の製造方法 |

| US10833296B2 (en) | 2017-09-26 | 2020-11-10 | International Business Machines Corporation | Thin film solid-state microbattery packaging |

| US10658702B2 (en) * | 2017-10-02 | 2020-05-19 | International Business Machines Corporation | High-performance thin-film battery with an interfacial layer |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3612018B2 (ja) * | 1992-12-04 | 2005-01-19 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| FR2862437B1 (fr) * | 2003-11-14 | 2006-02-10 | Commissariat Energie Atomique | Procede de fabrication d'une micro-batterie au lithium |

| SE0402471D0 (sv) * | 2004-10-12 | 2004-10-12 | Anders Lundblad | Electrochemical device |

| CA2658092A1 (en) * | 2006-07-18 | 2008-01-24 | Cymbet Corporation | Method and apparatus for solid-state microbattery photolithographic manufacture, singulation and passivation |

| CN101496218A (zh) * | 2006-07-25 | 2009-07-29 | 皇家飞利浦电子股份有限公司 | 三维基板上薄层电池堆叠体的制造方法 |

| KR101773498B1 (ko) * | 2007-10-25 | 2017-09-01 | 어플라이드 머티어리얼스, 인코포레이티드 | 박막 배터리들의 대량 생산을 위한 방법 |

| FR2952477B1 (fr) * | 2009-11-06 | 2011-12-09 | St Microelectronics Tours Sas | Procede de formation d'une batterie de type lithium-ion en couches minces |

-

2010

- 2010-05-18 DE DE102010029060A patent/DE102010029060A1/de not_active Ceased

-

2011

- 2011-05-13 IT IT000836A patent/ITMI20110836A1/it unknown

- 2011-05-17 CN CN201110127423.6A patent/CN102255102B/zh active Active

- 2011-05-17 FR FR1154261A patent/FR2960346B1/fr not_active Expired - Fee Related

- 2011-05-18 JP JP2011111705A patent/JP5975605B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| CN102255102A (zh) | 2011-11-23 |

| JP2011243577A (ja) | 2011-12-01 |

| ITMI20110836A1 (it) | 2011-11-19 |

| FR2960346B1 (fr) | 2019-08-23 |

| CN102255102B (zh) | 2016-03-23 |

| FR2960346A1 (fr) | 2011-11-25 |

| DE102010029060A1 (de) | 2011-11-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5975605B2 (ja) | 薄膜電池の製造方法および薄膜電池 | |

| CN102263293B (zh) | 用于制造薄层电池组的方法和装置 | |

| KR102413942B1 (ko) | 그래핀 시트 상의 패시베이션 층의 침착 | |

| CN110088904A (zh) | 三维存储器件及其制造方法 | |

| US10903525B2 (en) | Self-supporting thin-film battery and method of manufacturing such a battery | |

| US10373766B2 (en) | Method of producing a super-capacitor | |

| JP2009152186A (ja) | 封入されたリチウム電気化学的装置 | |

| JP2017526143A (ja) | レーザパターニングされた薄膜バッテリ | |

| JP6328131B2 (ja) | 容量性マイクロマシントランスデューサ及びその製造方法 | |

| TW201532298A (zh) | 使用自對準植入體及覆蓋體之太陽能電池射極區之製備 | |

| JP6888985B2 (ja) | 積層型ミニチュアライズ薄膜電池及びその製造方法 | |

| JP2004146297A (ja) | 固体電池 | |

| CN103732528B (zh) | 从mems空腔底部消除硅残留物 | |

| TWI708388B (zh) | 半導體結構及其製備方法 | |

| US10109887B1 (en) | 3D-structured solid state battery | |

| CN113795960B (zh) | 处理层状结构的方法 | |

| CN114420634A (zh) | 一种半导体器件的制备方法 | |

| TWI227527B (en) | Method of manufacturing a semiconductor device | |

| US11522243B2 (en) | Hermetic packaging of a micro-battery device | |

| KR102388206B1 (ko) | 트렌치 커패시터의 제조 방법 | |

| TWI798910B (zh) | 製作電容的方法 | |

| US20240046966A1 (en) | Wordline sidewall contacts in 3d nand structures | |

| JP4741549B2 (ja) | 半導体装置の製造方法 | |

| CN114242655A (zh) | 一种半导体器件的制备方法 | |

| JP2023115493A (ja) | コンデンサ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20140519 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20140611 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20150218 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150223 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20150525 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20150824 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20151119 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20160229 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20160524 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20160620 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20160719 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5975605 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |