JP5435720B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5435720B2 JP5435720B2 JP2009289041A JP2009289041A JP5435720B2 JP 5435720 B2 JP5435720 B2 JP 5435720B2 JP 2009289041 A JP2009289041 A JP 2009289041A JP 2009289041 A JP2009289041 A JP 2009289041A JP 5435720 B2 JP5435720 B2 JP 5435720B2

- Authority

- JP

- Japan

- Prior art keywords

- gate electrode

- region

- semiconductor device

- gate

- transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823468—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the gate sidewall spacers, e.g. double spacers, particular spacer material or shape

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/823412—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

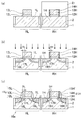

以下、本発明の第1の実施形態の半導体装置とその製造方法について、図面を参照しながら説明する。

次に、本発明の第2の実施形態の半導体装置とその製造方法について、図面を参照しながら説明する。

2 素子分離領域

10 半導体装置

10a 半導体装置

11H ゲート構造

11L ゲート構造

12H ゲート絶縁膜

12L ゲート絶縁膜

13H ゲート電極

13L ゲート電極

14A 絶縁膜

14B 絶縁膜

14H オフセットスペーサー

14HA 第一層

14HB 第二層

14L オフセットスペーサー

15H サイドウォールスペーサー

15L サイドウォールスペーサー

16H ソース/ドレイン領域

16L ソース/ドレイン領域

17H エクステンション領域

17L エクステンション領域

18H ハロー領域

18L ハロー領域

20 レジスト

21 レジスト

Claims (9)

- 基板上に、同一の導電型である第1電界効果型トランジスタ及び第2電界効果型トランジスタが形成され、

前記第1電界効果型トランジスタは、

前記基板における第1活性領域上に形成された第1ゲート電極と、

前記第1ゲート電極の側方に形成された堆積絶縁膜からなる第1サイドウォールスペーサーと、

前記第1活性領域における前記第1ゲート電極下方を挟む両側に形成された第1導電型の第1エクステンション領域とを備え、

前記第2電界効果型トランジスタは、

前記基板における第2活性領域上に形成された第2ゲート電極と、

前記第2ゲート電極の側方に形成された堆積絶縁膜からなる第2サイドウォールスペーサーと、

前記第2活性領域における前記第2ゲート電極下方を挟む両側に形成された第1導電型の第2エクステンション領域とを備え、

前記第1サイドウォールスペーサーと、前記第1ゲート電極との間に、堆積絶縁膜からなる第1オフセットスペーサーが設けられ、

前記第2サイドウォールスペーサーと、前記第2ゲート電極との間に、前記第1オフセットスペーサーよりも厚い、堆積絶縁膜からなる第2オフセットスペーサーが設けられ、

前記第1ゲート電極のゲート長方向の寸法と、前記第2ゲート電極のゲート長方向の寸法とは同一寸法に形成されており、

前記第1電界効果型トランジスタと前記第2電界効果型トランジスタとは、同一不純物濃度のチャネル拡散層を有し、

前記第2電界効果型トランジスタは、前記第1電界効果型トランジスタよりも閾値電圧が高く設定され、

前記第1エクステンション領域と前記第1ゲート電極とが重なるゲート長方向の長さは、前記第2エクステンション領域と前記第2ゲート電極とが重なるゲート長方向の長さよりも長く、

前記第1ゲート電極と前記第1サイドウォールスペーサーとの間の距離は、前記第2ゲート電極と前記第2サイドウォールスペーサーとの間の距離よりも短いことを特徴とする半導体装置。 - 請求項1の半導体装置において、

前記第1オフセットスペーサー及び前記第2オフセットスペーサーのうちの少なくとも前記第2オフセットスペーサーは、2層以上の積層構造であり、

前記第2オフセットスペーサーの積層数は、前記第1オフセットスペーサーの積層数よりも多いことを特徴とする半導体装置。 - 請求項1又は2のいずれか1つの半導体装置において、

前記第1エクステンション領域と前記第1ゲート電極とが重なるゲート長方向の長さは、前記第2エクステンション領域と前記第2ゲート電極とが重なるゲート長方向の長さよりも所定の距離だけ長いことを特徴とする半導体装置。 - 請求項1〜3のいずれか1つの半導体装置において、

前記第1ゲート電極と前記第1サイドウォールスペーサーとの間の距離は、前記第2ゲート電極と前記第2サイドウォールスペーサーとの間の距離よりも所定の距離だけ短いことを特徴とする半導体装置。 - 請求項3又は4の半導体装置において、

前記所定の距離は、前記第1電界効果型トランジスタの閾値電圧と前記第2電界効果型トランジスタの閾値電圧との違いによって設定されていることを特徴とする半導体装置。 - 請求項3〜5のいずれか1つの半導体装置において、

前記所定の距離は、2nm以上で且つ4nm以下であることを特徴とする半導体装置。 - 請求項1〜6のいずれか1つの半導体装置において、

前記第1ゲート電極の下方における前記第1エクステンション領域間の距離は、前記第2ゲート電極の下方における前記第2エクステンション領域間の距離よりも短いことを特徴とする半導体装置。 - 請求項1〜7のいずれか1つの半導体装置において、

前記第1エクステンション領域と前記基板との間に設けられた第2導電型の第1ハロー領域と、

前記第2エクステンション領域と前記基板との間に設けられた第2導電型の第2ハロー領域とを更に備えることを特徴とする半導体装置。 - 請求項1〜8のいずれか1つの半導体装置において、

前記第1活性領域における前記第1ゲート電極から見て前記第1エクステンション領域の外側に形成された第1導電型の第1ソース/ドレイン領域と、

前記第2活性領域における前記第2ゲート電極から見て前記第2エクステンション領域の外側に形成された第1導電型の第2ソース/ドレイン領域とを備えることを特徴とする半導体装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009289041A JP5435720B2 (ja) | 2009-12-21 | 2009-12-21 | 半導体装置 |

| PCT/JP2010/004887 WO2011077606A1 (ja) | 2009-12-21 | 2010-08-03 | 半導体装置とその製造方法 |

| US13/399,004 US20120161245A1 (en) | 2009-12-21 | 2012-02-17 | Semiconductor device and method for fabricating the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2009289041A JP5435720B2 (ja) | 2009-12-21 | 2009-12-21 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2011129811A JP2011129811A (ja) | 2011-06-30 |

| JP2011129811A5 JP2011129811A5 (ja) | 2011-12-01 |

| JP5435720B2 true JP5435720B2 (ja) | 2014-03-05 |

Family

ID=44195160

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2009289041A Expired - Fee Related JP5435720B2 (ja) | 2009-12-21 | 2009-12-21 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US20120161245A1 (ja) |

| JP (1) | JP5435720B2 (ja) |

| WO (1) | WO2011077606A1 (ja) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5847537B2 (ja) * | 2011-10-28 | 2016-01-27 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法および半導体装置 |

| US8822295B2 (en) | 2012-04-03 | 2014-09-02 | International Business Machines Corporation | Low extension dose implants in SRAM fabrication |

| JP5927017B2 (ja) * | 2012-04-20 | 2016-05-25 | ルネサスエレクトロニクス株式会社 | 半導体装置及び半導体装置の製造方法 |

| JP6275559B2 (ja) * | 2014-06-13 | 2018-02-07 | ルネサスエレクトロニクス株式会社 | 半導体装置およびその製造方法 |

| WO2017171881A1 (en) * | 2016-04-01 | 2017-10-05 | Intel Corporation | Semiconductor device having sub regions to define threshold voltages |

Family Cites Families (35)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3532625B2 (ja) * | 1994-10-06 | 2004-05-31 | 東芝マイクロエレクトロニクス株式会社 | 半導体装置の製造方法 |

| KR100214468B1 (ko) * | 1995-12-29 | 1999-08-02 | 구본준 | 씨모스 소자 제조방법 |

| JPH1167927A (ja) * | 1997-06-09 | 1999-03-09 | Mitsubishi Electric Corp | 半導体装置およびその製造方法 |

| KR19990030993A (ko) * | 1997-10-08 | 1999-05-06 | 윤종용 | 고속동작을 위한 모스트랜지스터구조 |

| US5989966A (en) * | 1997-12-15 | 1999-11-23 | Taiwan Semiconductor Manufacturing Company, Ltd. | Method and a deep sub-micron field effect transistor structure for suppressing short channel effects |

| US6124610A (en) * | 1998-06-26 | 2000-09-26 | Advanced Micro Devices, Inc. | Isotropically etching sidewall spacers to be used for both an NMOS source/drain implant and a PMOS LDD implant |

| JP2000150885A (ja) * | 1998-09-07 | 2000-05-30 | Seiko Epson Corp | Mosトランジスタの閾値電圧設定方法および半導体装置 |

| JP4481388B2 (ja) * | 1999-06-25 | 2010-06-16 | 独立行政法人情報通信研究機構 | 絶縁ゲート型電界効果トランジスタおよびその製造方法 |

| JP2001015704A (ja) | 1999-06-29 | 2001-01-19 | Hitachi Ltd | 半導体集積回路 |

| JP3275896B2 (ja) * | 1999-10-06 | 2002-04-22 | 日本電気株式会社 | 半導体装置の製造方法 |

| JP2001196475A (ja) * | 2000-01-12 | 2001-07-19 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP2002026139A (ja) * | 2000-06-30 | 2002-01-25 | Toshiba Corp | 半導体装置及び半導体装置の製造方法 |

| JP4635333B2 (ja) * | 2000-12-14 | 2011-02-23 | ソニー株式会社 | 半導体装置の製造方法 |

| JP2002231821A (ja) * | 2001-01-31 | 2002-08-16 | Mitsubishi Electric Corp | 半導体装置の製造方法及び半導体装置 |

| JP2003197765A (ja) * | 2001-12-28 | 2003-07-11 | Texas Instr Japan Ltd | 半導体装置およびその製造方法 |

| US6849492B2 (en) * | 2002-07-08 | 2005-02-01 | Micron Technology, Inc. | Method for forming standard voltage threshold and low voltage threshold MOSFET devices |

| JP2003249568A (ja) * | 2003-01-31 | 2003-09-05 | Oki Electric Ind Co Ltd | 半導体装置の製造方法 |

| JP4393109B2 (ja) * | 2003-05-21 | 2010-01-06 | 株式会社ルネサステクノロジ | 半導体装置の製造方法 |

| US7064396B2 (en) * | 2004-03-01 | 2006-06-20 | Freescale Semiconductor, Inc. | Integrated circuit with multiple spacer insulating region widths |

| JP2005303087A (ja) * | 2004-04-13 | 2005-10-27 | Matsushita Electric Ind Co Ltd | 半導体装置およびその製造方法 |

| KR100827443B1 (ko) * | 2006-10-11 | 2008-05-06 | 삼성전자주식회사 | 손상되지 않은 액티브 영역을 가진 반도체 소자 및 그 제조방법 |

| US7456066B2 (en) * | 2006-11-03 | 2008-11-25 | Taiwan Semiconductor Manufacturing Co., Ltd. | Variable width offset spacers for mixed signal and system on chip devices |

| JP4320405B2 (ja) * | 2007-03-27 | 2009-08-26 | Okiセミコンダクタ株式会社 | 半導体装置及びその製造方法 |

| US7718496B2 (en) * | 2007-10-30 | 2010-05-18 | International Business Machines Corporation | Techniques for enabling multiple Vt devices using high-K metal gate stacks |

| JP2009141168A (ja) * | 2007-12-07 | 2009-06-25 | Panasonic Corp | 半導体装置及びその製造方法 |

| JP2009277771A (ja) * | 2008-05-13 | 2009-11-26 | Panasonic Corp | 半導体装置とその製造方法 |

| US7951678B2 (en) * | 2008-08-12 | 2011-05-31 | International Business Machines Corporation | Metal-gate high-k reference structure |

| JP2010123669A (ja) * | 2008-11-18 | 2010-06-03 | Nec Electronics Corp | 半導体装置およびその製造方法 |

| JP2010153683A (ja) * | 2008-12-26 | 2010-07-08 | Hitachi Ltd | 半導体装置 |

| US8106455B2 (en) * | 2009-04-30 | 2012-01-31 | International Business Machines Corporation | Threshold voltage adjustment through gate dielectric stack modification |

| DE102009021486B4 (de) * | 2009-05-15 | 2013-07-04 | Globalfoundries Dresden Module One Llc & Co. Kg | Verfahren zur Feldeffekttransistor-Herstellung |

| US20100308418A1 (en) * | 2009-06-09 | 2010-12-09 | Knut Stahrenberg | Semiconductor Devices and Methods of Manufacture Thereof |

| US8105892B2 (en) * | 2009-08-18 | 2012-01-31 | International Business Machines Corporation | Thermal dual gate oxide device integration |

| US8283734B2 (en) * | 2010-04-09 | 2012-10-09 | Taiwan Semiconductor Manufacturing Company, Ltd. | Multi-threshold voltage device and method of making same |

| DE102010063781B4 (de) * | 2010-12-21 | 2016-08-11 | Globalfoundries Dresden Module One Limited Liability Company & Co. Kg | Unterschiedliche Schwellwertspannungseinstellung in PMOS-Transistoren durch unterschiedliche Herstellung eines Kanalhalbleitermaterials |

-

2009

- 2009-12-21 JP JP2009289041A patent/JP5435720B2/ja not_active Expired - Fee Related

-

2010

- 2010-08-03 WO PCT/JP2010/004887 patent/WO2011077606A1/ja active Application Filing

-

2012

- 2012-02-17 US US13/399,004 patent/US20120161245A1/en not_active Abandoned

Also Published As

| Publication number | Publication date |

|---|---|

| WO2011077606A1 (ja) | 2011-06-30 |

| JP2011129811A (ja) | 2011-06-30 |

| US20120161245A1 (en) | 2012-06-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4850174B2 (ja) | 半導体装置及びその製造方法 | |

| US7732839B2 (en) | Semiconductor device and method for fabricating the same | |

| US9245975B2 (en) | Recessed channel insulated-gate field effect transistor with self-aligned gate and increased channel length | |

| TWI485854B (zh) | 於三維電晶體中基於應變隔離材料之應變工程 | |

| KR102008738B1 (ko) | 반도체 장치 및 그 제조 방법 | |

| CN103165674B (zh) | 具有多阈值电压的FinFET | |

| US9966456B1 (en) | Methods of forming gate electrodes on a vertical transistor device | |

| US8258577B2 (en) | CMOS inverter device with fin structures | |

| US8409942B2 (en) | Replacement gate approach based on a reverse offset spacer applied prior to work function metal deposition | |

| JP2008244009A (ja) | 半導体装置およびその製造方法 | |

| US20120223388A1 (en) | Superior fill conditions in a replacement gate approach by using a tensile stressed overlayer | |

| US9337045B2 (en) | Methods of forming a semiconductor circuit element and semiconductor circuit element | |

| TWI714583B (zh) | 半導體裝置及其形成方法 | |

| JP2012164699A (ja) | 半導体装置 | |

| JP5435720B2 (ja) | 半導体装置 | |

| JP5627165B2 (ja) | 半導体装置及び半導体装置の製造方法 | |

| TW202129964A (zh) | 先進邏輯操作的電荷捕捉tfet半導體元件製作方法 | |

| KR20100138973A (ko) | 높이가 감소된 금속 게이트 스택을 포함하는 반도체 디바이스 및 상기 반도체 디바이스를 제조하는 방법 | |

| JP2008103579A (ja) | 半導体装置及びその製造方法 | |

| US7723777B2 (en) | Semiconductor device and method for making same | |

| JP2014123668A (ja) | Mos型半導体装置及びその製造方法 | |

| JP2000200836A (ja) | 半導体装置およびその製造方法 | |

| US8329526B2 (en) | Cap removal in a high-k metal gate electrode structure by using a sacrificial fill material | |

| JP4630235B2 (ja) | 半導体装置及びその製造方法 | |

| JP5073158B2 (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111019 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20120215 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20130108 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130307 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130409 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130613 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130620 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20130705 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20131025 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131206 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |