JP5401774B2 - 半導体素子のゲート駆動回路 - Google Patents

半導体素子のゲート駆動回路 Download PDFInfo

- Publication number

- JP5401774B2 JP5401774B2 JP2007219244A JP2007219244A JP5401774B2 JP 5401774 B2 JP5401774 B2 JP 5401774B2 JP 2007219244 A JP2007219244 A JP 2007219244A JP 2007219244 A JP2007219244 A JP 2007219244A JP 5401774 B2 JP5401774 B2 JP 5401774B2

- Authority

- JP

- Japan

- Prior art keywords

- mosfet

- gate

- drive circuit

- semiconductor element

- turned

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K3/00—Circuits for generating electric pulses; Monostable, bistable or multistable circuits

- H03K3/01—Details

- H03K3/012—Modifications of generator to improve response time or to decrease power consumption

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/168—Modifications for eliminating interference voltages or currents in composite switches

Landscapes

- Power Conversion In General (AREA)

- Electronic Switches (AREA)

Description

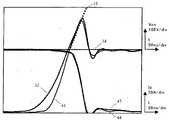

図3より、ターンオフ初期には、サーチコイル波形33の振動は殆ど見られず、コレクタ・エミッタ間電圧Vce31が直流電圧Vdc34に達した"*"のタイミングと同期して、急激にサーチコイル波形33が振動することが分かる。

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第2MOSFETのオン抵抗を、第3、第4MOSFETのオン抵抗よりも大きくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンさせることを特徴とする。

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第4MOSFETのオン抵抗を、第2,第3MOSFETのオン抵抗よりも小さくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンし、前記半導体素子がオフへ移行したとき、前記第4MOSFETをオンさせることを特徴とするものである。

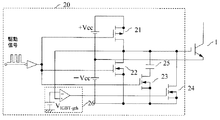

対象とする半導体素子はIGBT1であり、その駆動回路が符号20で示されている。この駆動回路20は、第1MOSFETとしてのPチャネル MOSFET21と、第2MOSFETとしてのNチャネル MOSFET22と、第3MOSFETとしてのNチャネル MOSFET23と、第4MOSFETとしてのNチャネル MOSFET24と、MOSFET23に直列に接続されたコンデンサ25と、MOSFET24の制御回路26などから構成される。制御回路26は、IGBT1のターンオフ保持用の制御回路である。また、Vccは、IGBT1のゲート端子に、ゲート電圧を印加するための直流電源であり、第1MOSFET21と第2MOSFET22との直列回路の両端に接続されている。

第4MOSFETがオンすることで、IGBT1のオフ状態を保持し安定電位を確保するものである。このため、第4MOSFET24のオン抵抗はできるだけ小さい方が望ましく、第2,第3MOSFET22,23のオン抵抗より小さいことが要求される。この第4MOSFET24は短絡を目的とするもので、特にMOSFETである必要はなく、バイポーラトランジスタでも良く、場合によっては機械的スイッチを用いても良い。

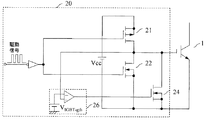

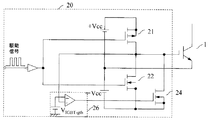

図5は、ゲートの電位を基準とした場合に正の電源のみで、ゲートへ逆バイアスを供給しない場合の例である。これに対し、図6はゲートの電位を基準とした場合に正負の電源を備え、ゲートへ逆バイアスを供給できる場合の例である。なお、図5,図6とも、図1または図2に示すコンデンサ25と第3MOSFET23を有していない点を除けば、図1または図2と同じなので説明は省略する。

すなわち、この発明のゲート駆動回路を用いることで、従来に比べてトレードオフ特性を改善できる。また、正負電源の有無により動作原理は変わらないが、負の電源がある場合の方が、トレードオフ特性の改善効果はやや高いということができる。

Claims (4)

- 半導体素子のゲートに少なくとも正の電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第2MOSFETのオン抵抗を、第3、第4MOSFETのオン抵抗よりも大きくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンさせることを特徴とする半導体素子のゲート駆動回路。 - 前記第4MOSFETは、前記半導体素子がオフ状態へ移行したとき、オンさせることを特徴とする請求項1に記載の半導体素子のゲート駆動回路。

- 半導体素子のゲートに少なくとも正の電圧を供給してオン・オフ制御する半導体素子のゲート駆動回路において、

直流電源間に第1MOSFETと第2MOSFETとを直列に接続し、前記半導体素子のゲート端子を前記第1MOSFETの負電位側端子および前記第2MOSFETの正電位側端子に接続し、半導体素子のエミッタ端子を第2MOSFETの負電位側端子に接続するとともに、第2MOSFETと並列に、コンデンサと第3MOSFETとの直列回路および第4MOSFETを接続し、

前記第4MOSFETのオン抵抗を、第2,第3MOSFETのオン抵抗よりも小さくし、

半導体素子をターンオフさせるときは、第1MOSFETをオフさせた状態で前記第2MOSFETと同時もしくは前記第2MOSFETより先に前記第3MOSFETをオンし、前記半導体素子がオフへ移行したとき、前記第4MOSFETをオンさせることを特徴とする半導体素子のゲート駆動回路。 - 前記第4MOSFETのオン抵抗を、第2,第3MOSFETのオン抵抗よりも小さくすることを特徴とする請求項2に記載の半導体素子のゲート駆動回路。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007219244A JP5401774B2 (ja) | 2007-08-27 | 2007-08-27 | 半導体素子のゲート駆動回路 |

| US12/189,319 US9543928B2 (en) | 2007-08-27 | 2008-08-11 | Gate driving circuit and method for driving semiconductor device |

| US14/106,205 US20140097876A1 (en) | 2007-08-27 | 2013-12-13 | Gate driving circuit and method for driving semiconductor device |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007219244A JP5401774B2 (ja) | 2007-08-27 | 2007-08-27 | 半導体素子のゲート駆動回路 |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012257649A Division JP5516705B2 (ja) | 2012-11-26 | 2012-11-26 | 半導体素子のゲート駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009055696A JP2009055696A (ja) | 2009-03-12 |

| JP5401774B2 true JP5401774B2 (ja) | 2014-01-29 |

Family

ID=40406485

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007219244A Active JP5401774B2 (ja) | 2007-08-27 | 2007-08-27 | 半導体素子のゲート駆動回路 |

Country Status (2)

| Country | Link |

|---|---|

| US (2) | US9543928B2 (ja) |

| JP (1) | JP5401774B2 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10523192B2 (en) | 2017-06-07 | 2019-12-31 | Fuji Electric Co., Ltd. | Gate drive apparatus for driving a plurality of switching elements connected in parallel to each other |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP2548417A1 (en) * | 2010-03-19 | 2013-01-23 | Koninklijke Philips Electronics N.V. | Electronic ballast for parallel lamp operation with program start |

| CN102844973B (zh) | 2010-04-01 | 2016-01-06 | 日立汽车系统株式会社 | 电力转换装置 |

| WO2012153458A1 (ja) | 2011-05-11 | 2012-11-15 | 富士電機株式会社 | 制御装置 |

| JP5932269B2 (ja) * | 2011-09-08 | 2016-06-08 | 株式会社東芝 | パワー半導体モジュール及びパワー半導体モジュールの駆動方法 |

| CN103843251B (zh) * | 2011-09-30 | 2016-08-24 | 夏普株式会社 | 电平移位电路 |

| KR20150071339A (ko) | 2013-12-18 | 2015-06-26 | 삼성전기주식회사 | 게이트 구동 회로 |

| EP2911298A1 (en) | 2014-02-25 | 2015-08-26 | ABB Oy | Gate drive circuit with a voltage stabilizer and a method |

| JP6497070B2 (ja) | 2014-12-26 | 2019-04-10 | 富士電機株式会社 | 半導体装置およびその制御方法 |

| CN107534383B (zh) * | 2015-05-13 | 2020-09-01 | 松下半导体解决方案株式会社 | 驱动电路、开关控制电路以及开关装置 |

| KR20160143909A (ko) * | 2015-06-04 | 2016-12-15 | 엘에스산전 주식회사 | Igbt 구동 장치 |

| JP6698313B2 (ja) * | 2015-10-27 | 2020-05-27 | ローム株式会社 | スイッチ駆動回路、スイッチ回路、および電源装置 |

| CN108702150B (zh) * | 2016-09-09 | 2021-12-21 | 富士电机株式会社 | 功率元件的驱动电路 |

| CN110352548B (zh) | 2017-09-15 | 2021-03-02 | 富士电机株式会社 | 功率模块、反向导通igbt及驱动电路 |

| JP2019193406A (ja) * | 2018-04-24 | 2019-10-31 | 株式会社日立製作所 | ゲート駆動回路およびゲート駆動方法 |

| JP7140015B2 (ja) * | 2019-03-18 | 2022-09-21 | 株式会社デンソー | スイッチの駆動回路 |

| WO2021117661A1 (ja) * | 2019-12-12 | 2021-06-17 | パナソニックIpマネジメント株式会社 | ゲート駆動回路、絶縁型ゲートドライバおよびゲート駆動方法 |

| CN111181128A (zh) * | 2020-02-16 | 2020-05-19 | 苏州浪潮智能科技有限公司 | 一种基于e-fuse芯片的保护电路 |

| JP7396250B2 (ja) * | 2020-11-05 | 2023-12-12 | 株式会社明電舎 | 交直変換装置および交直変換装置の制御方法 |

| CN115549441A (zh) | 2021-06-30 | 2022-12-30 | 纳维达斯半导体有限公司 | 关断电路和功率转换器 |

| US11855635B2 (en) | 2021-06-30 | 2023-12-26 | Navitas Semiconductor Limited | Transistor DV/DT control circuit |

| JP7757668B2 (ja) * | 2021-09-13 | 2025-10-22 | オムロン株式会社 | スイッチング回路および電力変換器 |

| CN114825879B (zh) * | 2022-06-06 | 2026-03-06 | 重庆平创半导体研究院有限责任公司 | 一种半导体开关组件及其控制方法 |

| WO2025181929A1 (ja) * | 2024-02-28 | 2025-09-04 | ファナック株式会社 | 半導体素子の駆動回路 |

| CN121530144A (zh) * | 2026-01-14 | 2026-02-13 | 深圳砺芯半导体有限责任公司 | 抑制串扰的冲击负电荷驱动电路及开关电源变换器 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5296064A (en) * | 1976-02-09 | 1977-08-12 | Seiko Epson Corp | Electronic timepiece |

| US5548237A (en) * | 1995-03-10 | 1996-08-20 | International Business Machines Corporation | Process tolerant delay circuit |

| JP3067687B2 (ja) * | 1997-05-08 | 2000-07-17 | 富士電機株式会社 | Igbt駆動回路 |

| JP3430878B2 (ja) * | 1997-09-19 | 2003-07-28 | 富士電機株式会社 | Mosゲート形素子の駆動回路 |

| JP3692740B2 (ja) | 1997-11-19 | 2005-09-07 | 株式会社明電舎 | スイッチング制御回路 |

| JP3383570B2 (ja) * | 1998-03-10 | 2003-03-04 | 株式会社東芝 | 電圧駆動型電力素子の駆動装置 |

| JP3432425B2 (ja) * | 1998-08-05 | 2003-08-04 | 株式会社東芝 | ゲート回路 |

| JP3666843B2 (ja) | 1999-02-26 | 2005-06-29 | 株式会社東芝 | 絶縁ゲート型半導体素子のゲート回路 |

| JP3568823B2 (ja) * | 1999-05-24 | 2004-09-22 | 東芝三菱電機産業システム株式会社 | 絶縁ゲート型半導体素子のゲート制御回路 |

| JP2001223571A (ja) * | 2000-02-10 | 2001-08-17 | Fuji Electric Co Ltd | 電圧駆動型半導体素子のゲート駆動装置 |

| JP3885563B2 (ja) * | 2001-11-16 | 2007-02-21 | 日産自動車株式会社 | パワー半導体駆動回路 |

| JP2003304678A (ja) * | 2002-04-10 | 2003-10-24 | Nissan Motor Co Ltd | 電圧駆動型素子の駆動装置 |

| US7602229B2 (en) * | 2003-09-08 | 2009-10-13 | Koninklijke Philips Electronics N.V. | High frequency control of a semiconductor switch |

| WO2005104743A2 (en) * | 2004-04-26 | 2005-11-10 | Rowan Electric, Inc. | Adaptive gate drive for switching devices of inverter |

| JP4755455B2 (ja) * | 2005-07-07 | 2011-08-24 | ローム株式会社 | パワートランジスタのオンオフを制御する制御回路およびそれを用いたスイッチングレギュレータならびに電子機器 |

| US7786779B2 (en) * | 2009-01-06 | 2010-08-31 | Himax Technologies Limited | Buffer for driving circuit and method thereof |

-

2007

- 2007-08-27 JP JP2007219244A patent/JP5401774B2/ja active Active

-

2008

- 2008-08-11 US US12/189,319 patent/US9543928B2/en active Active

-

2013

- 2013-12-13 US US14/106,205 patent/US20140097876A1/en not_active Abandoned

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10523192B2 (en) | 2017-06-07 | 2019-12-31 | Fuji Electric Co., Ltd. | Gate drive apparatus for driving a plurality of switching elements connected in parallel to each other |

Also Published As

| Publication number | Publication date |

|---|---|

| US20140097876A1 (en) | 2014-04-10 |

| JP2009055696A (ja) | 2009-03-12 |

| US9543928B2 (en) | 2017-01-10 |

| US20090058499A1 (en) | 2009-03-05 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5401774B2 (ja) | 半導体素子のゲート駆動回路 | |

| JP5516705B2 (ja) | 半導体素子のゲート駆動方法 | |

| US8847631B2 (en) | High speed low loss gate drive circuit | |

| Wang et al. | A novel RCD level shifter for elimination of spurious turn-on in the bridge-leg configuration | |

| JP5801001B2 (ja) | 駆動保護回路、半導体モジュール及び自動車 | |

| JP4880751B2 (ja) | パワーmosfetのための回生型ゲート駆動回路 | |

| JP6645924B2 (ja) | 半導体装置及び電力変換装置 | |

| US20150028923A1 (en) | High efficiency gate drive circuit for power transistors | |

| US20140103962A1 (en) | High-speed gate driver for power switches with reduced voltage ringing | |

| JP7151325B2 (ja) | ドライバ回路 | |

| JPWO2017141545A1 (ja) | 半導体素子の過電流保護装置 | |

| JP2018093681A (ja) | 駆動回路及び該回路を含んでなる半導体モジュール | |

| Wang et al. | Switching performance improvement of IGBT modules using an active gate driver | |

| JP6234131B2 (ja) | パワーモジュール | |

| JP2013005474A (ja) | 電源回路 | |

| JP6090007B2 (ja) | 駆動回路 | |

| JP5925434B2 (ja) | ゲート駆動回路 | |

| JP2018153006A (ja) | ゲート駆動装置 | |

| JP2018098849A (ja) | パワーモジュール | |

| EP2627001B1 (en) | External power transistor control | |

| Kuo et al. | Universal active gate driver IC with closed-loop timing control and gate-sensing technique for silicon carbide power devices | |

| JP6734007B2 (ja) | パワーモジュール | |

| JP5994697B2 (ja) | 半導体駆動装置 | |

| JP5369987B2 (ja) | ゲート駆動回路 | |

| Lemmon et al. | Gate-drive considerations for silicon carbide FET-based half-bridge circuits |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20091112 |

|

| RD03 | Notification of appointment of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7423 Effective date: 20091112 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20091112 |

|

| A625 | Written request for application examination (by other person) |

Free format text: JAPANESE INTERMEDIATE CODE: A625 Effective date: 20100615 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20110422 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120912 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121002 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121126 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20130528 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130826 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20130902 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20131001 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20131014 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5401774 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |