JP2019193406A - ゲート駆動回路およびゲート駆動方法 - Google Patents

ゲート駆動回路およびゲート駆動方法 Download PDFInfo

- Publication number

- JP2019193406A JP2019193406A JP2018082704A JP2018082704A JP2019193406A JP 2019193406 A JP2019193406 A JP 2019193406A JP 2018082704 A JP2018082704 A JP 2018082704A JP 2018082704 A JP2018082704 A JP 2018082704A JP 2019193406 A JP2019193406 A JP 2019193406A

- Authority

- JP

- Japan

- Prior art keywords

- gate

- semiconductor element

- mosfet

- drive circuit

- voltage

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K17/00—Electronic switching or gating, i.e. not by contact-making and –breaking

- H03K17/16—Modifications for eliminating interference voltages or currents

- H03K17/161—Modifications for eliminating interference voltages or currents in field-effect transistor switches

- H03K17/162—Modifications for eliminating interference voltages or currents in field-effect transistor switches without feedback from the output circuit to the control circuit

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/08—Circuits specially adapted for the generation of control voltages for semiconductor devices incorporated in static converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M1/00—Details of apparatus for conversion

- H02M1/0003—Details of control, feedback or regulation circuits

- H02M1/0006—Arrangements for supplying an adequate voltage to the control circuit of converters

-

- H—ELECTRICITY

- H02—GENERATION; CONVERSION OR DISTRIBUTION OF ELECTRIC POWER

- H02M—APPARATUS FOR CONVERSION BETWEEN AC AND AC, BETWEEN AC AND DC, OR BETWEEN DC AND DC, AND FOR USE WITH MAINS OR SIMILAR POWER SUPPLY SYSTEMS; CONVERSION OF DC OR AC INPUT POWER INTO SURGE OUTPUT POWER; CONTROL OR REGULATION THEREOF

- H02M7/00—Conversion of ac power input into dc power output; Conversion of dc power input into ac power output

- H02M7/42—Conversion of dc power input into ac power output without possibility of reversal

- H02M7/44—Conversion of dc power input into ac power output without possibility of reversal by static converters

- H02M7/48—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode

- H02M7/53—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal

- H02M7/537—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters

- H02M7/5387—Conversion of dc power input into ac power output without possibility of reversal by static converters using discharge tubes with control electrode or semiconductor devices with control electrode using devices of a triode or transistor type requiring continuous application of a control signal using semiconductor devices only, e.g. single switched pulse inverters in a bridge configuration

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02B—CLIMATE CHANGE MITIGATION TECHNOLOGIES RELATED TO BUILDINGS, e.g. HOUSING, HOUSE APPLIANCES OR RELATED END-USER APPLICATIONS

- Y02B70/00—Technologies for an efficient end-user side electric power management and consumption

- Y02B70/10—Technologies improving the efficiency by using switched-mode power supplies [SMPS], i.e. efficient power electronics conversion e.g. power factor correction or reduction of losses in power supplies or efficient standby modes

Abstract

Description

また、実施例では、電圧維持手段が、出力部と負側電源の間にN型MOSFETと並列に接続されたダイオードを含むことを開示する。また、ダイオードが、ショットキーバリアダイオード、ツェナーダイオード、またはPNダイオードであることを開示する。

Vgs=−Vm+(V1+V2) (式1)

Vgs=−Vm−(V1+V3) (式2)

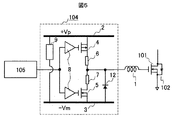

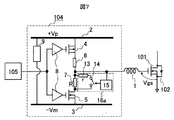

2:ゲート駆動回路の正側電源

3:ゲート駆動回路の負側電源

4:P型MOSFET

5:N型MOSFET

6:オン側ゲート抵抗

7:オフ側ゲート抵抗

8:駆動制御装置

9:電源生成部

10:NPNトランジスタ

11:PNPトランジスタ

12:ダイオード

13:並列化抵抗

14:アナログスイッチ

15:ゲートオフ判定部

16a:低インピーダンス化回路

16b:低インピーダンス化回路

17:電圧クランプ用MOSFET

91:定格電圧(上限値)

92:正側電圧電源

93:負側電圧電源

94:定格電圧(下限値)

100:パワーユニット

101:電圧駆動型の半導体素子(IGBT、MOSFETなど)

102:還流ダイオード

103:フィルタコンデンサ

104:ゲート駆動回路

105:指令論理部

106:モータ

107:架線

108:集電装置

109:遮断機

110:フィルタリアクトル

111:車輪

112:レール

Claims (17)

- SiCを適用した電圧駆動型の半導体素子を駆動するゲート駆動回路において、

前記ゲート駆動回路が、P型MOSFETおよびN側MOSFETが直列に接続され、且つ前記N側MOSFETが負側電源に直接接続されて構成され、前記P型MOSFETと前記N側MOSFETの中間にある出力段が、前記半導体素子のオフ中に負バイアスとなるように前記P型MOSFETおよび前記N型MOSFETを相補的にオンオフすることを特徴とするゲート駆動回路。 - 請求項1に記載のゲート駆動回路において、

前記半導体素子のオフ中に出力段を負バイアスに維持する電圧維持手段を有することを特徴とするゲート駆動回路。 - 請求項2に記載のゲート駆動回路において、

前記電圧維持手段が、前記出力部と前記負側電源の間に前記N型MOSFETと並列に接続されたダイオードを含むことを特徴とするゲート駆動回路。 - 請求項3に記載のゲート駆動回路において、

前記ダイオードが、ショットキーバリアダイオード、ツェナーダイオード、またはPNダイオードであることを特徴とするゲート駆動回路。 - 請求項2に記載のゲート駆動回路において、

前記電圧維持手段が、前記出力段とN側MOSFETの中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗と、前記並列化抵抗に直列接続されたスイッチと、前記半導体素子がオフ状態の場合に前記スイッチをオンとする判定部を含むことを特徴とするゲート駆動回路。 - 請求項2に記載のゲート駆動回路において、

前記電圧維持手段が、前記出力段と前記負側電源の間で前記N側MOSFETと並列に接続されたMOSFETと、前記半導体素子がオフ状態の場合に前記MOSFETを短絡させる判定部を含むことを特徴とするゲート駆動回路。 - 請求項1乃至6のいずれかに記載のゲート駆動回路において、

前記半導体素子が、ノーマリオフの半導体素子であることを特徴とするゲート駆動回路。 - 請求項1乃至7のいずれかに記載のゲート駆動回路において、

前記負側電源の電圧生成に、絶縁型電源トランス、または絶縁側DCDCコンバータが用いられることを特徴とするゲート駆動回路 - 請求項1乃至8のいずれかに記載のゲート駆動回路を搭載した3相交流インバータ。

- SiCを適用した電圧駆動型の半導体素子のゲート駆動方法において、

P側MOSFET、および負極電源に直接接続されたN側MOSFETを相補的にオンオフして、直列に接続されている前記P型MOSFETと前記N側MOSFETの中間にある出力段を、前記半導体素子のオフ中に負バイアスとすることを特徴とするゲート駆動方法。 - 請求項10記載のゲート駆動方法において、

電圧維持手段により、前記半導体素子のオフ中に出力段を負バイアスに維持することを特徴とするゲート駆動方法。 - 請求項11に記載のゲート駆動方法において、

前記電圧維持手段が、前記出力部と前記負側電源の間に前記N型MOSFETと並列に接続されたダイオードを含むことを特徴とするゲート駆動方法。 - 請求項12に記載のゲート駆動方法において、

前記ダイオードが、ショットキーバリアダイオード、ツェナーダイオード、またはPNダイオードであることを特徴とするゲート駆動方法。 - 請求項11に記載のゲート駆動方法において、

前記半導体素子がオフ状態の場合に、前記出力段とN側MOSFETの中間にあるオフ側ゲート抵抗に並列接続された並列化抵抗に直列接続されたスイッチをオンとすることを特徴とするゲート駆動方法。 - 請求項11に記載のゲート駆動方法において、

前記半導体素子がオフ状態の場合に、前記出力段と前記負側電源の間で前記N側MOSFETと並列に接続されたMOSFETを短絡させることを特徴とするゲート駆動方法。 - 請求項11乃至15のいずれかに記載のゲート駆動方法において、

前記半導体素子が、ノーマリオフの半導体素子であることを特徴とするゲート駆動方法。 - 請求項11乃至16のいずれかに記載のゲート駆動方法において、

絶縁型電源トランス、または絶縁側DCDCコンバータにより、前記負側電源の電圧を生成することを特徴とするゲート駆動方法。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018082704A JP2019193406A (ja) | 2018-04-24 | 2018-04-24 | ゲート駆動回路およびゲート駆動方法 |

| PCT/JP2019/009651 WO2019207977A1 (ja) | 2018-04-24 | 2019-03-11 | ゲート駆動回路およびゲート駆動方法 |

| EP19792293.3A EP3787164A1 (en) | 2018-04-24 | 2019-03-11 | Gate drive circuit and gate drive method |

| CN201980025569.4A CN111971884A (zh) | 2018-04-24 | 2019-03-11 | 栅极驱动电路和栅极驱动方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2018082704A JP2019193406A (ja) | 2018-04-24 | 2018-04-24 | ゲート駆動回路およびゲート駆動方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2019193406A true JP2019193406A (ja) | 2019-10-31 |

| JP2019193406A5 JP2019193406A5 (ja) | 2021-01-28 |

Family

ID=68295092

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2018082704A Pending JP2019193406A (ja) | 2018-04-24 | 2018-04-24 | ゲート駆動回路およびゲート駆動方法 |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP3787164A1 (ja) |

| JP (1) | JP2019193406A (ja) |

| CN (1) | CN111971884A (ja) |

| WO (1) | WO2019207977A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114884320A (zh) * | 2022-07-07 | 2022-08-09 | 深圳平创半导体有限公司 | 一种用于减小栅极负压驱动电路功耗的装置 |

Families Citing this family (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US11791709B2 (en) | 2021-07-01 | 2023-10-17 | Navitas Semiconductor Limited | Integrated gallium nitride power device with protection circuits |

| EP4131779A1 (en) * | 2021-08-03 | 2023-02-08 | Infineon Technologies Austria AG | Gate driver device |

Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009055696A (ja) * | 2007-08-27 | 2009-03-12 | Fuji Electric Device Technology Co Ltd | 半導体素子のゲート駆動回路およびゲート駆動方法 |

| JP2012199763A (ja) * | 2011-03-22 | 2012-10-18 | Sanken Electric Co Ltd | ゲートドライブ回路 |

| JP2015023774A (ja) * | 2013-07-23 | 2015-02-02 | 日新電機株式会社 | ゲート駆動回路 |

| WO2015182658A1 (ja) * | 2014-05-30 | 2015-12-03 | 三菱電機株式会社 | 電力用半導体素子の駆動回路 |

| JP2016034178A (ja) * | 2014-07-31 | 2016-03-10 | 株式会社日立製作所 | 電力変換装置及びその制御方法 |

| JP2016123199A (ja) * | 2014-12-25 | 2016-07-07 | パナソニックIpマネジメント株式会社 | 駆動装置、電力変換装置 |

| WO2018008398A1 (ja) * | 2016-07-04 | 2018-01-11 | 三菱電機株式会社 | 駆動回路およびそれを用いたパワーモジュール |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009225506A (ja) * | 2008-03-13 | 2009-10-01 | Toshiba Corp | 電力変換器 |

| JP5130310B2 (ja) * | 2010-03-17 | 2013-01-30 | 日立アプライアンス株式会社 | 電圧駆動型半導体素子のゲート駆動回路及び電力変換装置 |

| JP5503427B2 (ja) | 2010-06-22 | 2014-05-28 | 本田技研工業株式会社 | ゲート駆動回路 |

| JP5975833B2 (ja) * | 2012-02-01 | 2016-08-23 | 三菱電機株式会社 | 電力変換装置 |

| JP2014057491A (ja) | 2012-09-14 | 2014-03-27 | Mitsubishi Electric Corp | 半導体スイッチング素子のゲート駆動回路 |

| JP6798179B2 (ja) * | 2016-07-29 | 2020-12-09 | 富士電機株式会社 | 3レベルチョッパ装置 |

-

2018

- 2018-04-24 JP JP2018082704A patent/JP2019193406A/ja active Pending

-

2019

- 2019-03-11 WO PCT/JP2019/009651 patent/WO2019207977A1/ja unknown

- 2019-03-11 EP EP19792293.3A patent/EP3787164A1/en not_active Withdrawn

- 2019-03-11 CN CN201980025569.4A patent/CN111971884A/zh active Pending

Patent Citations (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2009055696A (ja) * | 2007-08-27 | 2009-03-12 | Fuji Electric Device Technology Co Ltd | 半導体素子のゲート駆動回路およびゲート駆動方法 |

| JP2012199763A (ja) * | 2011-03-22 | 2012-10-18 | Sanken Electric Co Ltd | ゲートドライブ回路 |

| JP2015023774A (ja) * | 2013-07-23 | 2015-02-02 | 日新電機株式会社 | ゲート駆動回路 |

| WO2015182658A1 (ja) * | 2014-05-30 | 2015-12-03 | 三菱電機株式会社 | 電力用半導体素子の駆動回路 |

| JP2016034178A (ja) * | 2014-07-31 | 2016-03-10 | 株式会社日立製作所 | 電力変換装置及びその制御方法 |

| JP2016123199A (ja) * | 2014-12-25 | 2016-07-07 | パナソニックIpマネジメント株式会社 | 駆動装置、電力変換装置 |

| WO2018008398A1 (ja) * | 2016-07-04 | 2018-01-11 | 三菱電機株式会社 | 駆動回路およびそれを用いたパワーモジュール |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN114884320A (zh) * | 2022-07-07 | 2022-08-09 | 深圳平创半导体有限公司 | 一种用于减小栅极负压驱动电路功耗的装置 |

Also Published As

| Publication number | Publication date |

|---|---|

| CN111971884A (zh) | 2020-11-20 |

| EP3787164A1 (en) | 2021-03-03 |

| WO2019207977A1 (ja) | 2019-10-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6619381B2 (ja) | 回路を動作させる方法及び回路 | |

| EP3035532B1 (en) | Gate drive circuit and method of operating same | |

| US10320278B2 (en) | Semiconductor device having a decreased switching loss | |

| US9444448B2 (en) | High performance IGBT gate drive | |

| US9362903B2 (en) | Gate drivers for circuits based on semiconductor devices | |

| CN103986359B (zh) | 电力转换装置 | |

| US20110121884A1 (en) | Half-bridge circuits employing normally on switches and methods of preventing unintended current flow therein | |

| US20130271187A1 (en) | Driver for semiconductor switch element | |

| US20160285386A1 (en) | Rectifier | |

| WO2013115000A1 (ja) | 半導体スイッチング素子の駆動回路並びにそれを用いた電力変換回路 | |

| WO2019207977A1 (ja) | ゲート駆動回路およびゲート駆動方法 | |

| JP2009011013A (ja) | 電力変換装置 | |

| WO2016030954A1 (ja) | 駆動回路、電力変換装置、およびモータシステム | |

| JP5382535B2 (ja) | ゲート駆動回路の電源装置 | |

| JP6122542B1 (ja) | アクティブクランプ回路 | |

| JP2019041499A (ja) | 駆動回路および半導体モジュール | |

| JP6004988B2 (ja) | 電力用半導体素子のゲート制御装置 | |

| CN110741546B (zh) | 整流电路以及电源装置 | |

| JP2019041514A (ja) | 半導体素子の駆動回路 | |

| JPH10209832A (ja) | 半導体スイッチ回路 | |

| US11271547B2 (en) | Gate drive circuit, drive device, semiconductor device, and gate drive method | |

| WO2024057598A1 (ja) | 半導体スイッチング素子のゲート駆動回路、電動機制御システムおよび半導体装置 | |

| US11909384B2 (en) | Direct-drive D-mode GaN half-bridge power module | |

| JP6679967B2 (ja) | 半導体素子の駆動装置 | |

| JP2021185741A (ja) | 電力変換装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20201211 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20201211 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20201211 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20201221 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20201228 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20210226 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20210427 |