JP5259666B2 - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP5259666B2 JP5259666B2 JP2010212720A JP2010212720A JP5259666B2 JP 5259666 B2 JP5259666 B2 JP 5259666B2 JP 2010212720 A JP2010212720 A JP 2010212720A JP 2010212720 A JP2010212720 A JP 2010212720A JP 5259666 B2 JP5259666 B2 JP 5259666B2

- Authority

- JP

- Japan

- Prior art keywords

- memory cell

- voltage

- word line

- write

- nth

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3436—Arrangements for verifying correct programming or erasure

- G11C16/3454—Arrangements for verifying correct programming or for detecting overprogrammed cells

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Semiconductor Memories (AREA)

- Non-Volatile Memory (AREA)

Description

まず、第1の実施形態に係わる3次元積層型不揮発性半導体記憶装置を例として、図6のブロック図を用いて説明する。

本実施形態の3次元積層型不揮発性半導体記憶装置は、BiCSフラッシュメモリ10と、メモリコントローラ(外部コントローラともいう)20とを有する。ここで、BiCSフラッシュメモリ10は、メモリセルアレイ11、センスアンプ12、カラムアドレスバッファ/カラムデコーダ13、ロウデコーダ14、制御回路(内部コントローラともいう)15、電圧生成回路16、パワーオン検出回路17、ロウアドレスバッファ18、入出力バッファ19を備える。

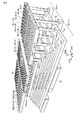

まず、本実施形態のメモリセルアレイ1について、図1乃至図3を用いて説明する。

半導体基板31内に形成されるソース拡散層32は、例えば、同一プレーン内の全ブロックBKに共通に1つ設けられる。ソース拡散層32は、コンタクトプラグPSLを介して、ソース線SL・M1に接続される。

本実施形態では、導電層は、層間絶縁膜を介して6層積層された構造となっている。図1では、導電膜は、ワード線WL<0> 乃至WL<3> と、ドレイン側セレクトゲート線(第1セレクトゲート線)SGDと、ソース側セレクトゲート線(第2セレクトゲート線)SGSである。

そして、NANDストリング(図3で後述する)を構成するための複数の活性層(アクティブエリア)AAは、z方向(半導体基板の表面に対して垂直方向)に柱状に形成されており、ソース拡散層32から複数の導電層を突き抜けてビット線BLに達するように形成される。

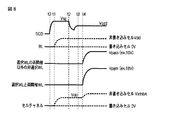

図6に示すように、センスアンプ12は、ビット線BLを介してメモリセルアレイ11と接続される。センスアンプ12は、読み出しの際にメモリセルアレイ11のデータをページ単位で読み出しを行い、書き込みの際にメモリセルアレイ11にデータをページ単位で書き込む。

ロウデコーダ14は、ロウアドレスバッファ18を介して入力されるロウアドレス信号をデコードして、ワード線WL及びセレクトゲート線SGD,SGSを選択し、駆動する。

制御回路15は、メモリコントローラ20を介して供給される各種外部制御信号(書き込みイネーブル信号WEn、読み出しイネーブル信号REn、コマンドラッチイネーブル信号CLE、アドレスラッチイネーブル信号ALE等)とコマンドCMDに基づいて、データ書き込み及び消去のシーケンス制御及び読み出しの動作・制御を行う。制御回路15は、パワーオン検出回路17から入力される検知信号を受けて、初期化動作を自動的に行う。

電圧発生回路16は、制御回路15により制御されて、書き込み、消去及び読み出しの動作に必要な各種内部電圧を発生するもので、電源電圧より高い内部電圧を発生するために昇圧回路が用いられる。

パワーオン検出回路17は、制御回路15に接続される。パワーオン検出回路17は、電源の投入を検出し、制御回路15に検知信号を出力する。

メモリコンロトーラ20は、BiCSフラッシュメモリ10に必要なコマンドなどを出力し、BiCSフラッシュメモリ10の動作モード(後述する、第1の書き込みモード、第2の書き込みモードを含む。)を設定し、読み出し及び書き込みを行う。

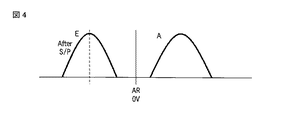

ここで、本実施形態の不揮発性半導体メモリは、図3(b)に示すように、隣接するメモリセル間で電荷蓄積層34がつながっている。このため、平面NANDタイプの不揮発性半導体メモリのようにメモリセルの消去レベルを負にしたVthバジェットを使用すると、本実施形態の不揮発性半導体メモリのデータリテンションが悪化する場合がある。その支配的要因はいわゆる電荷の横抜けである。これは、例えば同一チャネルのボディで正の閾値のメモリセルと負の閾値のメモリセルが隣接した場合に起こる。

次に、本実施形態の不揮発性半導体記憶装置の書き込み動作について、図7のフローチャート図を用いて説明する。

以上により、データ書き込みの高速化をはかり得る不揮発性半導体記憶装置を提供できる。以下、具体的に説明する。図11は、第1の実施形態における書き込みによるn番目及び(n±1)番目のワード線に接続されたメモリセルの閾値分布を示す図であり、図12は、複数ワード線群に接続されたメモリセルに書き込みを行った場合の各メモリセルの閾値分布の状態を示す図である。

次に、第2の実施形態に係わる不揮発性半導体記憶装置を説明する。MLCのチップを用いたSSD(Solid State Drive)においてSLCをバッファとして使用した例を用いて説明する。本実施形態にかかる不揮発性半導体記憶装置は、第1の実施形態に係わる不揮発性半導体記憶装置と構成は同一であるが、動作方法が異なる。したがって、本実施形態では、不揮発性半導体記憶装置の動作方法について詳細に説明する。

説明の便宜上、第1の実施形態におけるステップS1からステップS6までのいわゆるSLC書き込みを行い、SLCバッファにデータが書き込まれていることを前提として説明する。

本実施形態の不揮発性半導体記憶装置では、第1及び第2の実施形態に対して、メモリコントローラが、第1の実施形態のように3本のワード線に接続されたメモリセルにデータ書き込みを行う超高速SLCバッファーモード(第1の書き込みモード)と、1本のワード線に接続されたメモリセルの消去状態を、第1の消去状態から第2の消去状態に書き込み、データ書き込みを行う高速SLCバッファーモード(第2の書き込みモード)を選択する点で異なり、その他は同様である。

なお、本発明は上述した各実施形態に限定されるものではない。メモリセルアレイの構成は必ずしもBiCSに限るものではなく、電荷蓄積層と制御ゲートを有するメモリセルを基板上に積層した、積層型のメモリセル構造の不揮発性半導体記憶装置に適用することができる。さらに、BiCSの構造も前記図1に何ら限定されるものではなく、仕様に応じて適宜変更可能である。

11…メモリセルアレイ

12…センスアンプ

13…カラムアドレスバッファ/カラムデコーダ

14…ロウデコーダ

15…制御回路

16…電圧生成回路

17…パワーオン検出回路

18…ロウアドレスバッファ

19…入出力バッファ

20…メモリコントローラ

31…半導体基板

32…ソース拡散層

33…トンネル絶縁膜

34…電荷蓄積層

35…ブロック絶縁膜

36…制御ゲート

Claims (6)

- 半導体基板上に積層された複数のワード線に、電荷蓄積層を有する複数のメモリセルがそれぞれ接続され、且つ、隣接するメモリセル間で電荷蓄積層が連続しているメモリセルアレイと、

前記メモリセルアレイのn番目(nは自然数)のワード線と電気的に接続された第1メモリセル及び第2メモリセルにデータを書き込む際に、前記第1メモリセルと電気的に接続される第1ビット線に第1電圧を、前記第2メモリセルと電気的に接続される第2ビット線に前記第1電圧よりも高い第2電圧を印加したまま、(n−1)番目及び(n+1)番目のワード線にn番目のワード線と同一の書き込み電圧を一括して印加するよう制御する制御回路と、

を具備したことを特徴とする不揮発性半導体記憶装置。 - 前記制御回路は、前記n番目のワード線に接続された第1メモリセル及び第2メモリセルにベリファイを行い、

前記n番目のワード線に接続された第1メモリセルの閾値電圧が所望の正の電圧を超えるまで、前記n番目及び前記(n±1)番目のワード線に書き込み電圧を一括して印加することを特徴とする請求項1記載の不揮発性半導体記憶装置。 - 前記制御回路は、さらに、前記(n+1)番目のワード線と電気的に接続された第3メモリセル及び第4メモリセルのベリファイを行い、前記(n−1)番目のワード線と電気的に接続された第5メモリセル及び第6メモリセルのベリファイを行い、前記n番目のワード線と電気的に接続された第1メモリセルの閾値電圧が所望の正の電圧を超えるまで、前記n番目及び(n±1)番目のワード線に書き込み電圧を一括して印加することを特徴とする請求項2記載の不揮発性半導体記憶装置。

- 前記制御回路は、前記ベリファイの結果に応じて、ベリファイパスしたメモリセルと電気的に接続されたビット線に非書き込み電圧を印加し、

ベリファイフェイルしたメモリセルと電気的に接続されたビット線に書き込み電圧を印加することを特徴とする請求項2又は3記載の不揮発性半導体記憶装置。 - 前記メモリセルアレイは、

前記半導体基板上に柱状に形成された活性層と、

前記活性層の側壁面を囲むようにトンネル絶縁膜,電荷蓄積層,及びブロック絶縁膜が形成されたゲート絶縁膜部と、

前記ゲート絶縁膜部の側壁面を囲むように形成されて、且つ前記半導体基板上に複数の層間絶縁膜と複数の導電層が交互に積層された積層構造部と

を有し、

前記活性層,トンネル絶縁膜,電荷蓄積層,ブロック絶縁膜,及び導電層を含むトランジスタで前記メモリセルを構成したものであることを特徴とする請求項1乃至4の何れか1項に記載の不揮発性半導体記憶装置。 - 前記制御回路は、要求される書き込み速度に応じて、

前記第1メモリセル及び前記第2メモリセルにデータを書き込む際に、前記第1ビット線に前記第1電圧を、前記第2ビット線に前記第2電圧を印加したまま、(n−1)番目及び(n+1)番目のワード線にn番目のワード線と同一の書き込み電圧を一括して印加する第1の書き込みモードと、

前記第1メモリセル及び前記第2メモリセルにデータを書き込む際に、前記第1メモリセル及び第2メモリセルの閾値電圧を、負の閾値電圧を有する第1消去状態から正の閾値電圧を有する第2消去状態へと遷移させた後、前記第1ビット線に前記第1電圧を、前記第2ビット線に前記第2電圧を印加したまま、前記n番目のワード線に書き込み電圧を印加する第2の書き込みモードと

のいずれかを選択することを特徴とする請求項1乃至5の何れか1項に記載の不揮発性半導体記憶装置。

Priority Applications (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010212720A JP5259666B2 (ja) | 2010-09-22 | 2010-09-22 | 不揮発性半導体記憶装置 |

| KR1020110023771A KR20120031113A (ko) | 2010-09-22 | 2011-03-17 | 불휘발성 반도체 기억 장치 |

| US13/157,603 US8593872B2 (en) | 2010-09-22 | 2011-06-10 | Nonvolatile semiconductor memory device capable of speeding up data write |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2010212720A JP5259666B2 (ja) | 2010-09-22 | 2010-09-22 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2012069200A JP2012069200A (ja) | 2012-04-05 |

| JP5259666B2 true JP5259666B2 (ja) | 2013-08-07 |

Family

ID=45817666

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010212720A Active JP5259666B2 (ja) | 2010-09-22 | 2010-09-22 | 不揮発性半導体記憶装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (1) | US8593872B2 (ja) |

| JP (1) | JP5259666B2 (ja) |

| KR (1) | KR20120031113A (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10049760B2 (en) | 2016-09-06 | 2018-08-14 | Toshiba Memory Corporation | Programming and verification methods for three-dimensional memory device |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103119656A (zh) * | 2010-09-24 | 2013-05-22 | 株式会社东芝 | 非易失性半导体存储器件 |

| KR101893562B1 (ko) * | 2012-01-09 | 2018-10-04 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그것의 프로그램 방법 |

| KR101913331B1 (ko) * | 2012-01-19 | 2018-10-30 | 삼성전자주식회사 | 비휘발성 메모리 장치, 그것을 포함하는 비휘발성 메모리 시스템, 그것의 프로그램 방법, 그리고 그것을 제어하는 컨트롤러 동작 방법 |

| US9099202B2 (en) | 2012-11-06 | 2015-08-04 | Sandisk Technologies Inc. | 3D stacked non-volatile storage programming to conductive state |

| US9466382B2 (en) | 2012-11-14 | 2016-10-11 | Sandisk Technologies Llc | Compensation for sub-block erase |

| US8830717B2 (en) | 2012-11-29 | 2014-09-09 | Sandisk Technologies Inc. | Optimized configurable NAND parameters |

| US8988941B2 (en) | 2012-12-18 | 2015-03-24 | SanDisk Tehcnologies Inc. | Select transistor tuning |

| KR102090589B1 (ko) * | 2013-01-14 | 2020-03-18 | 삼성전자주식회사 | 비휘발성 메모리 장치의 데이터 저장 방법 및 비휘발성 메모리 장치의 테스트 방법 |

| US9218890B2 (en) | 2013-06-03 | 2015-12-22 | Sandisk Technologies Inc. | Adaptive operation of three dimensional memory |

| KR102175039B1 (ko) | 2013-06-25 | 2020-11-05 | 삼성전자주식회사 | 불휘발성 메모리 장치의 데이터 기입 방법 |

| TWI573148B (zh) | 2013-08-02 | 2017-03-01 | 東芝股份有限公司 | A controller, a memory system, and a memory device |

| US9324438B2 (en) | 2013-08-05 | 2016-04-26 | Jonker Llc | Method of operating incrementally programmable non-volatile memory |

| CN104425020A (zh) * | 2013-08-23 | 2015-03-18 | 慧荣科技股份有限公司 | 存取快闪存储器中储存单元的方法以及使用该方法的装置 |

| US9142324B2 (en) | 2013-09-03 | 2015-09-22 | Sandisk Technologies Inc. | Bad block reconfiguration in nonvolatile memory |

| KR20150060144A (ko) * | 2013-11-26 | 2015-06-03 | 삼성전자주식회사 | 비휘발성 메모리 장치의 동작 방법 |

| US9218886B2 (en) | 2013-12-10 | 2015-12-22 | SanDisk Technologies, Inc. | String dependent parameter setup |

| KR102128466B1 (ko) | 2014-04-14 | 2020-06-30 | 삼성전자주식회사 | 메모리 시스템, 상기 메모리 시스템의 프로그램 방법 및 상기 메모리 시스템의 테스트 방법 |

| US9613713B2 (en) * | 2014-09-16 | 2017-04-04 | Kabushiki Kaisha Toshiba | Semiconductor memory device |

| JP2016062623A (ja) * | 2014-09-16 | 2016-04-25 | 株式会社東芝 | 半導体記憶装置 |

| US9691473B2 (en) | 2015-09-22 | 2017-06-27 | Sandisk Technologies Llc | Adaptive operation of 3D memory |

| US9401216B1 (en) | 2015-09-22 | 2016-07-26 | Sandisk Technologies Llc | Adaptive operation of 3D NAND memory |

| JP2017162526A (ja) | 2016-03-07 | 2017-09-14 | 東芝メモリ株式会社 | 記憶装置 |

| US9916901B1 (en) | 2017-01-26 | 2018-03-13 | Micron Technology, Inc. | Memory device including multiple gate-induced drain leakage current generator circuits |

| JP2018147535A (ja) * | 2017-03-07 | 2018-09-20 | 東芝メモリ株式会社 | 半導体記憶装置及びメモリシステム |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3576763B2 (ja) * | 1997-08-21 | 2004-10-13 | 株式会社東芝 | 半導体記憶装置 |

| JPH11162199A (ja) * | 1997-11-25 | 1999-06-18 | Hitachi Ltd | 半導体記憶装置 |

| JP2000236031A (ja) * | 1999-02-16 | 2000-08-29 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP3983969B2 (ja) * | 2000-03-08 | 2007-09-26 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP3709126B2 (ja) * | 2000-07-05 | 2005-10-19 | シャープ株式会社 | 不揮発性半導体メモリ装置の消去方法 |

| JP3702229B2 (ja) * | 2002-01-16 | 2005-10-05 | 株式会社東芝 | 半導体記憶装置 |

| JP4796126B2 (ja) * | 2005-03-31 | 2011-10-19 | サンディスク コーポレイション | メモリセルの部分集合を個別に検証してさらにソフトプログラミングすることによる不揮発性メモリのソフトプログラミング |

| EP1864293B1 (en) * | 2005-03-31 | 2010-08-04 | SanDisk Corporation | Erasing non-volatile memory using individual verification and additional erasing of subsets of memory cells |

| JP2007257739A (ja) * | 2006-03-23 | 2007-10-04 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5019198B2 (ja) * | 2006-06-29 | 2012-09-05 | 株式会社東芝 | 半導体記憶装置 |

| JP5142692B2 (ja) * | 2007-12-11 | 2013-02-13 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| US7633804B2 (en) * | 2008-03-20 | 2009-12-15 | Micron Technology, Inc. | Adjusting programming or erase voltage pulses in response to the number of programming or erase failures |

| JP2009230818A (ja) * | 2008-03-24 | 2009-10-08 | Toshiba Corp | 半導体記憶装置 |

| JP2009266946A (ja) * | 2008-04-23 | 2009-11-12 | Toshiba Corp | 三次元積層不揮発性半導体メモリ |

| JP2009301607A (ja) * | 2008-06-10 | 2009-12-24 | Toshiba Corp | 不揮発性半導体記憶装置およびその制御方法 |

| KR101468099B1 (ko) * | 2008-07-24 | 2014-12-03 | 삼성전자주식회사 | 불휘발성 메모리 장치의 프로그램 방법 |

| JP2010118580A (ja) * | 2008-11-14 | 2010-05-27 | Toshiba Corp | 不揮発性半導体記憶装置 |

| JP5275052B2 (ja) * | 2009-01-08 | 2013-08-28 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| JP2010199235A (ja) * | 2009-02-24 | 2010-09-09 | Toshiba Corp | 不揮発性半導体記憶装置 |

-

2010

- 2010-09-22 JP JP2010212720A patent/JP5259666B2/ja active Active

-

2011

- 2011-03-17 KR KR1020110023771A patent/KR20120031113A/ko not_active Ceased

- 2011-06-10 US US13/157,603 patent/US8593872B2/en active Active

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US10049760B2 (en) | 2016-09-06 | 2018-08-14 | Toshiba Memory Corporation | Programming and verification methods for three-dimensional memory device |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2012069200A (ja) | 2012-04-05 |

| US8593872B2 (en) | 2013-11-26 |

| KR20120031113A (ko) | 2012-03-30 |

| US20120069667A1 (en) | 2012-03-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5259666B2 (ja) | 不揮発性半導体記憶装置 | |

| US8570802B2 (en) | Nonvolatile semiconductor memory device capable of speeding up write operation | |

| US9799406B2 (en) | Memory system | |

| TWI656534B (zh) | Memory device | |

| US7539061B2 (en) | Method of programming flash memory device | |

| CN110085272B (zh) | 半导体存储装置 | |

| CN109817266B (zh) | 非易失性存储设备及其擦除方法 | |

| JP2010009733A (ja) | 不揮発性半導体記憶装置 | |

| CN111725211B (zh) | 半导体存储装置 | |

| JP2015176623A (ja) | 半導体記憶装置及びメモリコントローラ | |

| JP2011198419A (ja) | 不揮発性半導体記憶装置およびその書き込み方法 | |

| US20140063972A1 (en) | Semiconductor storage device | |

| CN112530486B (zh) | 半导体存储装置 | |

| US11709629B2 (en) | Nonvolatile memory device | |

| JP2014063552A (ja) | 半導体記憶装置 | |

| JP2012160222A (ja) | 不揮発性半導体記憶装置 | |

| JP2020047321A (ja) | 半導体記憶装置 | |

| US8867273B2 (en) | Non-volatile semiconductor memory device and method of writing data therein | |

| JP2010040125A (ja) | 不揮発性半導体記憶装置の消去方法 | |

| US8929144B2 (en) | Nonvolatile semiconductor memory device | |

| TWI858355B (zh) | 半導體記憶裝置 | |

| US20130163329A1 (en) | Memory system | |

| TWI894766B (zh) | 半導體記憶裝置 | |

| US20250157542A1 (en) | Non-volatile memory device and programming method | |

| JP2013200924A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20120809 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121212 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121218 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130218 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130402 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130424 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160502 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5259666 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |