JP5219609B2 - フレームレート変換装置、方法及びプログラム - Google Patents

フレームレート変換装置、方法及びプログラム Download PDFInfo

- Publication number

- JP5219609B2 JP5219609B2 JP2008119988A JP2008119988A JP5219609B2 JP 5219609 B2 JP5219609 B2 JP 5219609B2 JP 2008119988 A JP2008119988 A JP 2008119988A JP 2008119988 A JP2008119988 A JP 2008119988A JP 5219609 B2 JP5219609 B2 JP 5219609B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- motion

- frame

- luminance

- degree

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/14—Picture signal circuitry for video frequency region

- H04N5/144—Movement detection

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F3/00—Input arrangements for transferring data to be processed into a form capable of being handled by the computer; Output arrangements for transferring data from processing unit to output unit, e.g. interface arrangements

- G06F3/14—Digital output to display device ; Cooperation and interconnection of the display device with other functional units

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N5/00—Details of television systems

- H04N5/14—Picture signal circuitry for video frequency region

- H04N5/21—Circuitry for suppressing or minimising disturbance, e.g. moiré or halo

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N7/00—Television systems

- H04N7/01—Conversion of standards, e.g. involving analogue television standards or digital television standards processed at pixel level

- H04N7/0127—Conversion of standards, e.g. involving analogue television standards or digital television standards processed at pixel level by changing the field or frame frequency of the incoming video signal, e.g. frame rate converter

- H04N7/0132—Conversion of standards, e.g. involving analogue television standards or digital television standards processed at pixel level by changing the field or frame frequency of the incoming video signal, e.g. frame rate converter the field or frame frequency of the incoming video signal being multiplied by a positive integer, e.g. for flicker reduction

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/10—Special adaptations of display systems for operation with variable images

- G09G2320/106—Determination of movement vectors or equivalent parameters within the image

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2340/00—Aspects of display data processing

- G09G2340/04—Changes in size, position or resolution of an image

- G09G2340/0407—Resolution change, inclusive of the use of different resolutions for different screen areas

- G09G2340/0435—Change or adaptation of the frame rate of the video stream

Landscapes

- Engineering & Computer Science (AREA)

- Multimedia (AREA)

- Signal Processing (AREA)

- Theoretical Computer Science (AREA)

- Human Computer Interaction (AREA)

- Physics & Mathematics (AREA)

- General Engineering & Computer Science (AREA)

- General Physics & Mathematics (AREA)

- Television Systems (AREA)

Description

前記入力フレームにおける画像の1又は複数の画素からなる各領域の動き度を検出する検出手段と、

前記検出手段により検出された各領域の動き度に応じて前記複数のサブフレームにおける各領域での輝度分配量を決定する決定手段と、

前記決定手段により決定された輝度分配量で前記入力フレームの各領域の輝度を分配して前記複数のサブフレームを出力する出力手段と、を具備し、

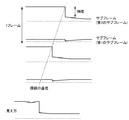

前記決定手段は、前記領域において、前記動き検出手段により検出された動き度が予め定められた値より小さければ、該動き度が予め定められた値よりも大きい場合よりも、前記出力手段により出力される前記複数のサブフレーム間の当該領域の輝度差を小さくすることを特徴とする。

図1は、本発明の一実施の形態に係わるフレームレート変換装置の概略構成の一例を示すブロック図である。

103 動き検出部

104 分配補正係数生成部

105 LPF

106 分配処理部

107 差分処理部

108 切替器

Claims (11)

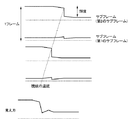

- 入力フレームの輝度を複数のサブフレームに分配してフレームレート変換を行なうフレームレート変換装置であって、

前記入力フレームにおける画像の1又は複数の画素からなる各領域の動き度を検出する検出手段と、

前記検出手段により検出された各領域の動き度に応じて前記複数のサブフレームにおける各領域での輝度分配量を決定する決定手段と、

前記決定手段により決定された輝度分配量で前記入力フレームの各領域の輝度を分配して前記複数のサブフレームを出力する出力手段と、を具備し、

前記決定手段は、前記領域において、前記動き検出手段により検出された動き度が予め定められた値より小さければ、該動き度が予め定められた値よりも大きい場合よりも、前記出力手段により出力される前記複数のサブフレーム間の当該領域の輝度差を小さくすることを特徴とするフレームレート変換装置。 - 前記決定手段は、

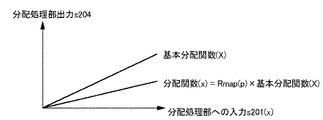

前記各領域の動き度に応じて前記複数のサブフレームの各領域における輝度分配量を補正する分配補正係数を生成することにより前記輝度分配量を決定し、

前記出力手段は、

前記決定手段により生成された分配補正係数で補正された輝度分配量にしたがって前記入力フレームの各領域の輝度を第1のサブフレームに分配する分配処理手段と、

前記第1のサブフレームと前記入力フレームとの輝度の差分から第2のサブフレームを生成する差分処理手段と、

前記第1のサブフレームと前記第2のサブフレームとを切り替えて1フレーム期間中に出力する切替手段と

を具備することを特徴とする請求項1記載のフレームレート変換装置。 - 前記検出手段は、

前記入力フレームと該入力フレームよりも前に入力されたフレームとからフレーム間差分を算出し、該算出した差分値と閾値との関係から該入力フレームよりも前に入力されたフレームにおける画像の各領域の動き度を検出する

ことを特徴とする請求項1記載のフレームレート変換装置。 - 前記検出手段は、

前記入力フレームと該入力フレームよりも前に入力されたフレームとから各領域のフレーム間の動きベクトルを算出し、該算出した動きベクトルから該入力フレームよりも前に入力されたフレームにおける画像の各領域の動き度を検出する

ことを特徴とする請求項1記載のフレームレート変換装置。 - 前記検出手段は、

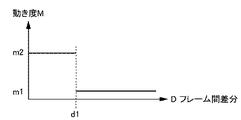

前記入力フレームよりも前に入力されたフレームにおける画像の各領域の動きと予め定められた値との関係から動きの大きい領域と動きの小さい領域とに対応する動き度をそれぞれ検出し、

前記決定手段は、

前記動きの大きい領域であれば、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、前記動きの小さい領域である場合に該サブフレームの対応する領域に分配する輝度分配量よりも低くすることで、前記複数のサブフレーム間の当該領域の輝度差を大きくする

ことを特徴とする請求項1記載のフレームレート変換装置。 - 前記検出手段は、

前記入力フレームよりも前に入力されたフレームにおける画像の各領域の動きと予め定められた値との関係から動きの大きい領域と動きの小さい領域とに対応する動き度をそれぞれ検出し、

前記決定手段は、

前記動きの小さい領域であれば、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、前記動きの大きい領域である場合に該サブフレームの対応する領域に分配する輝度分配量よりも高くすることで、前記複数のサブフレーム間の当該領域の輝度差を小さくする

ことを特徴とする請求項1又は5記載のフレームレート変換装置。 - 第1の値と該第1の値よりも大きい第2の値とが予め定められており、

前記検出手段は、

前記入力フレームよりも前に入力されたフレームにおける画像の各領域の動きと前記第1の値又は前記第2の値との関係から動きの大きい領域と動きの小さい領域とを含む領域に対応する動き度をそれぞれ検出し、

前記決定手段は、

前記動きの大きい領域であれば、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、前記動きの小さい領域である場合に該サブフレームの対応する領域に分配する輝度分配量よりも低くすることで、前記複数のサブフレーム間の当該領域の輝度差を大きくし、前記動きの小さい領域であれば、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、前記動きの大きい領域である場合に該サブフレームの対応する領域に分配する輝度分配量よりも高くすることで、前記複数のサブフレーム間の当該領域の輝度差を小さくする

ことを特徴とする請求項1記載のフレームレート変換装置。 - 前記検出手段は、

前記入力フレームよりも前に入力されたフレームにおける画像の領域の動きが前記第1の値から前記第2の値の間であれば、該第1の値から該第2の値の間で動きが大きくなるにつれて、動き度を単調に変化させて検出し、

前記決定手段は、

前記領域の動きが前記第1の値から前記第2の値の間であれば、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、前記動きの小さい領域である場合に該サブフレームの対応する領域に分配する輝度分配量よりも低くし、かつ動きが大きくなるにつれて、前記検出された動き度に応じて該輝度分配量を低くすることで、前記複数のサブフレーム間の当該領域の輝度差を大きくする

ことを特徴とする請求項7記載のフレームレート変換装置。 - 前記決定手段は、

前記動きの小さい領域であり、かつ該領域が動きの大きい領域と隣接する場合には、前記出力手段により時間的に後方に出力されるサブフレームの対応する領域への輝度分配量を、該動きが小さい領域において該隣接する位置までの所定範囲の輝度分配量を連続的に減衰させることで、前記複数のサブフレーム間の該所定範囲の輝度差を大きくする

ことを特徴とする請求項6又は7記載のフレームレート変換装置。 - 入力フレームの輝度を複数のサブフレームに分配してフレームレート変換を行なうフレームレート変換装置におけるフレームレート変換方法であって、

検出手段が、前記入力フレームにおける画像の1又は複数の画素からなる各領域の動き度を検出する検出工程と、

決定手段が、前記検出工程により検出された各領域の動き度に応じて前記複数のサブフレームにおける各領域での輝度分配量を決定する決定工程と、

出力手段が、前記決定工程により決定された輝度分配量で前記入力フレームの各領域の輝度を分配して前記複数のサブフレームを出力する出力工程と、を含み、

前記決定工程では、前記領域において、前記動き検出工程において検出された動き度が予め定められた値より小さければ、該動き度が予め定められた値よりも大きい場合よりも、前記出力工程において出力される前記複数のサブフレーム間の当該領域の輝度差を小さくすることを特徴とするフレームレート変換方法。 - 入力フレームの輝度を複数のサブフレームに分配してフレームレート変換を行なうフレームレート変換装置に内蔵されたコンピュータを、

前記入力フレームにおける画像の1又は複数の画素からなる各領域の動き度を検出する検出手段、

前記検出手段により検出された各領域の動き度に応じて前記複数のサブフレームにおける各領域での輝度分配量を決定する決定手段、

前記決定手段により決定された輝度分配量で前記入力フレームの各領域の輝度を分配して前記複数のサブフレームを出力する出力手段

として機能させるためのプログラムであって、

前記決定手段は、前記領域において、前記動き検出手段により検出された動き度が予め定められた値より小さければ、該動き度が予め定められた値よりも大きい場合よりも、前記出力手段により出力される前記複数のサブフレーム間の当該領域の輝度差を小さくすることを特徴とするプログラム。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008119988A JP5219609B2 (ja) | 2008-05-01 | 2008-05-01 | フレームレート変換装置、方法及びプログラム |

| US12/423,342 US20090273707A1 (en) | 2008-05-01 | 2009-04-14 | Frame rate conversion apparatus, frame rate conversion method, and computer-readable storage medium |

| EP09158048.0A EP2124430B1 (en) | 2008-05-01 | 2009-04-16 | Frame rate conversion apparatus, frame rate conversion method, and computer-readable storage medium |

| CN2009101376641A CN101572076B (zh) | 2008-05-01 | 2009-05-04 | 帧速率变换设备和帧速率变换方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008119988A JP5219609B2 (ja) | 2008-05-01 | 2008-05-01 | フレームレート変換装置、方法及びプログラム |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009272781A JP2009272781A (ja) | 2009-11-19 |

| JP2009272781A5 JP2009272781A5 (ja) | 2011-06-16 |

| JP5219609B2 true JP5219609B2 (ja) | 2013-06-26 |

Family

ID=40868954

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008119988A Expired - Fee Related JP5219609B2 (ja) | 2008-05-01 | 2008-05-01 | フレームレート変換装置、方法及びプログラム |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US20090273707A1 (ja) |

| EP (1) | EP2124430B1 (ja) |

| JP (1) | JP5219609B2 (ja) |

| CN (1) | CN101572076B (ja) |

Families Citing this family (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4813517B2 (ja) * | 2008-05-29 | 2011-11-09 | オリンパス株式会社 | 画像処理装置、画像処理プログラム、画像処理方法、および電子機器 |

| JP5676874B2 (ja) * | 2009-10-30 | 2015-02-25 | キヤノン株式会社 | 画像処理装置およびその制御方法、プログラム |

| WO2011061957A1 (ja) | 2009-11-17 | 2011-05-26 | シャープ株式会社 | 符号化装置、復号化装置、符号化装置の制御方法、復号化装置の制御方法、伝送システム、および制御プログラムを記録したコンピュータ読み取り可能な記録媒体 |

| US8824825B2 (en) | 2009-11-17 | 2014-09-02 | Sharp Kabushiki Kaisha | Decoding device with nonlinear process section, control method for the decoding device, transmission system, and computer-readable recording medium having a control program recorded thereon |

| US8643776B2 (en) * | 2009-11-30 | 2014-02-04 | Mediatek Inc. | Video processing method capable of performing predetermined data processing operation upon output of frame rate conversion with reduced storage device bandwidth usage and related video processing apparatus thereof |

| EP2538658A4 (en) * | 2010-02-15 | 2013-07-24 | Sharp Kk | SIGNAL PROCESSING DEVICE, CONTROL PROGRAM AND INTEGRATED CIRCUIT |

| CN102131058B (zh) * | 2011-04-12 | 2013-04-17 | 上海理滋芯片设计有限公司 | 高清数字视频帧速率变换处理模块及其方法 |

| KR102143618B1 (ko) * | 2014-01-17 | 2020-08-11 | 삼성전자주식회사 | 프레임률 제어 방법 및 그 전자 장치 |

| JP2016012068A (ja) * | 2014-06-30 | 2016-01-21 | 日本放送協会 | 画像表示装置 |

| US11443715B2 (en) | 2019-01-04 | 2022-09-13 | Ati Technologies Ulc | Strobe configuration for illumination of frame at display device |

| US11503248B1 (en) * | 2022-01-04 | 2022-11-15 | Novatek Microelectronics Corp. | Method of MEMC and related video processor |

Family Cites Families (41)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB2031686B (en) * | 1978-09-14 | 1983-02-02 | Micro Consultants Ltd | Movement detection |

| NL8100603A (nl) * | 1981-02-09 | 1982-09-01 | Philips Nv | Rasterfrequentieverdubbelingsschakeling voor een televisiesignaal. |

| DE3814570A1 (de) * | 1988-04-29 | 1989-11-09 | Grundig Emv | Verfahren und schaltungsanordnung zur flimmerreduktion bei einem fernsehempfaenger |

| DE59008311D1 (de) * | 1990-03-09 | 1995-03-02 | Itt Ind Gmbh Deutsche | Verfahren und Vorrichtung zur Reduktion des Kantenflackerns eines Fernsehbildes. |

| DE4327733C1 (de) * | 1993-08-18 | 1994-06-01 | Grundig Emv | Bewegungsdetektor |

| JP3758294B2 (ja) * | 1997-04-10 | 2006-03-22 | 株式会社富士通ゼネラル | ディスプレイ装置の動画補正方法及び動画補正回路 |

| US6909466B1 (en) * | 1998-09-30 | 2005-06-21 | Micronas Gmbh | Circuit for frame rate conversion using a motion-adaptive method |

| CN1160681C (zh) * | 1999-04-12 | 2004-08-04 | 松下电器产业株式会社 | 图象显示装置 |

| JP2001296841A (ja) * | 1999-04-28 | 2001-10-26 | Matsushita Electric Ind Co Ltd | 表示装置 |

| US7085318B2 (en) * | 2000-06-15 | 2006-08-01 | Sony Corporation | Image processing system, image processing method, program, and recording medium |

| US7116372B2 (en) * | 2000-10-20 | 2006-10-03 | Matsushita Electric Industrial Co., Ltd. | Method and apparatus for deinterlacing |

| JP2002351382A (ja) * | 2001-03-22 | 2002-12-06 | Victor Co Of Japan Ltd | ディスプレイ装置 |

| JP3660610B2 (ja) * | 2001-07-10 | 2005-06-15 | 株式会社東芝 | 画像表示方法 |

| US6784942B2 (en) * | 2001-10-05 | 2004-08-31 | Genesis Microchip, Inc. | Motion adaptive de-interlacing method and apparatus |

| US7050501B2 (en) * | 2002-07-16 | 2006-05-23 | Broadcom Corporation | Digital noise reduction techniques |

| KR100486715B1 (ko) * | 2002-10-09 | 2005-05-03 | 삼성전자주식회사 | 펄스수 변조방식 디지털 디스플레이 패널에서 의사 윤곽감소를 위한 방법 및 장치 |

| JP4080951B2 (ja) * | 2003-05-30 | 2008-04-23 | 株式会社東芝 | フレーム補間方法及び装置並びに画像表示システム |

| JP4817000B2 (ja) * | 2003-07-04 | 2011-11-16 | ソニー株式会社 | 画像処理装置および方法、並びにプログラム |

| JP4003713B2 (ja) * | 2003-08-06 | 2007-11-07 | ソニー株式会社 | 画像処理装置および画像処理方法 |

| US20050047504A1 (en) * | 2003-09-03 | 2005-03-03 | Sung Chih-Ta Star | Data stream encoding method and apparatus for digital video compression |

| US7153268B2 (en) * | 2003-09-09 | 2006-12-26 | General Electric Company | Motion adaptive frame averaging for ultrasound doppler color flow imaging |

| JP2005173387A (ja) * | 2003-12-12 | 2005-06-30 | Nec Corp | 画像処理方法、表示装置の駆動方法及び表示装置 |

| KR100989314B1 (ko) * | 2004-04-09 | 2010-10-25 | 삼성전자주식회사 | 디스플레이장치 |

| JP4086030B2 (ja) * | 2004-10-15 | 2008-05-14 | 松下電器産業株式会社 | 画像表示装置 |

| JP3841105B1 (ja) | 2005-08-17 | 2006-11-01 | セイコーエプソン株式会社 | 動画ボケ改善のための信号処理 |

| TW200627362A (en) * | 2004-11-01 | 2006-08-01 | Seiko Epson Corp | Signal processing for reducing blur of moving image |

| KR100691324B1 (ko) * | 2005-07-22 | 2007-03-12 | 삼성전자주식회사 | 액정 디스플레이장치 |

| JP4306671B2 (ja) * | 2005-11-04 | 2009-08-05 | セイコーエプソン株式会社 | 動画像表示装置および動画像表示方法 |

| KR100766085B1 (ko) * | 2006-02-28 | 2007-10-11 | 삼성전자주식회사 | 프레임레이트 변환기능을 구비한 영상표시장치 및프레임레이트 변환방법 |

| TWI323605B (en) * | 2006-05-12 | 2010-04-11 | Realtek Semiconductor Corp | Apparatus and method for reducing temporal noise |

| JP4462234B2 (ja) * | 2006-05-26 | 2010-05-12 | セイコーエプソン株式会社 | 電気光学装置及び電子機器 |

| JP2008011251A (ja) * | 2006-06-29 | 2008-01-17 | Toshiba Corp | 液晶表示装置 |

| TWI338276B (en) * | 2006-11-13 | 2011-03-01 | Novatek Microelectronics Corp | Method and apparatus for driving an lcd monitor |

| US8144778B2 (en) * | 2007-02-22 | 2012-03-27 | Sigma Designs, Inc. | Motion compensated frame rate conversion system and method |

| WO2008114658A1 (ja) * | 2007-03-16 | 2008-09-25 | Sony Corporation | 画像処理装置、画像表示装置および画像処理方法 |

| JP2008261984A (ja) * | 2007-04-11 | 2008-10-30 | Hitachi Ltd | 画像処理方法及びこれを用いた画像表示装置 |

| US8098333B2 (en) * | 2007-06-29 | 2012-01-17 | Seiko Epson Corporation | Phase shift insertion method for reducing motion artifacts on hold-type displays |

| JP4525946B2 (ja) * | 2007-10-19 | 2010-08-18 | ソニー株式会社 | 画像処理装置、画像表示装置および画像処理方法 |

| KR20090127690A (ko) * | 2008-06-09 | 2009-12-14 | 삼성전자주식회사 | 디스플레이장치 및 그 제어방법 |

| JP5202246B2 (ja) * | 2008-11-20 | 2013-06-05 | キヤノン株式会社 | 動画像処理装置、及び方法、プログラム |

| JP2010197785A (ja) * | 2009-02-26 | 2010-09-09 | Seiko Epson Corp | 画像表示装置、電子機器および画像表示方法 |

-

2008

- 2008-05-01 JP JP2008119988A patent/JP5219609B2/ja not_active Expired - Fee Related

-

2009

- 2009-04-14 US US12/423,342 patent/US20090273707A1/en not_active Abandoned

- 2009-04-16 EP EP09158048.0A patent/EP2124430B1/en not_active Not-in-force

- 2009-05-04 CN CN2009101376641A patent/CN101572076B/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009272781A (ja) | 2009-11-19 |

| EP2124430B1 (en) | 2013-11-06 |

| CN101572076A (zh) | 2009-11-04 |

| EP2124430A1 (en) | 2009-11-25 |

| US20090273707A1 (en) | 2009-11-05 |

| CN101572076B (zh) | 2011-11-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5219609B2 (ja) | フレームレート変換装置、方法及びプログラム | |

| JP4586052B2 (ja) | 画像処理装置及びその制御方法 | |

| US8576925B2 (en) | Image processing apparatus and image processing method, and program | |

| JP4231071B2 (ja) | 画像表示装置、画像表示方法および画像表示プログラム | |

| JP5398365B2 (ja) | 画像処理装置、画像処理方法 | |

| US8643677B2 (en) | Image processing apparatus and image processing method, and program therefor | |

| KR101258473B1 (ko) | 프레임 레이트 변환 장치 및 프레임 레이트 변환 방법 | |

| US9830880B1 (en) | Method and system for adjusting the refresh rate of a display device based on a video content rate | |

| JP2010278995A (ja) | 画像処理装置、画像処理方法、プログラム及び記憶媒体 | |

| JP5141043B2 (ja) | 画像表示装置および画像表示方法 | |

| JP2009098574A (ja) | 画像処理装置、画像表示装置および画像処理方法 | |

| JP2011097375A (ja) | 画像処理装置、画像処理方法、プログラム及び記憶媒体 | |

| US9159287B2 (en) | Image display apparatus and image display method | |

| JP5219608B2 (ja) | フレームレート変換装置、方法及びプログラム | |

| JP2011059312A (ja) | 画像表示装置およびその制御方法 | |

| JP5558766B2 (ja) | 画像処理装置及びその制御方法 | |

| JP2011033707A (ja) | 画像処理装置及びその制御方法 | |

| JP2005151135A (ja) | 画像境界の判定装置および判定方法、並びにそれを用いた画像信号の処理装置および処理方法 | |

| JP6320022B2 (ja) | 映像表示装置、映像表示装置の制御方法及びプログラム | |

| JP5340104B2 (ja) | 画像処理装置、画像処理方法 | |

| JP2011139124A (ja) | 動きベクトル生成装置、表示装置、集積回路、動きベクトル生成プログラムおよび動きベクトル生成方法 | |

| JP2010283695A (ja) | 画像処理装置、画像処理方法 | |

| JP2010028576A (ja) | 画像処理装置及びその制御方法 | |

| JP2008263256A (ja) | 補間信号生成回路、補間信号生成方法、プログラムおよびビデオ信号処理装置 | |

| JPH10294883A (ja) | 画像処理装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110425 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110425 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20121108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20121116 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20130115 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20130204 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20130305 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160315 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20160315 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |