JP5154951B2 - 半導体装置及び表示装置 - Google Patents

半導体装置及び表示装置 Download PDFInfo

- Publication number

- JP5154951B2 JP5154951B2 JP2007553828A JP2007553828A JP5154951B2 JP 5154951 B2 JP5154951 B2 JP 5154951B2 JP 2007553828 A JP2007553828 A JP 2007553828A JP 2007553828 A JP2007553828 A JP 2007553828A JP 5154951 B2 JP5154951 B2 JP 5154951B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- layer

- circuit element

- semiconductor device

- film

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/673—Thin-film transistors [TFT] characterised by the electrodes characterised by the shapes, relative sizes or dispositions of the gate electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6729—Thin-film transistors [TFT] characterised by the electrodes

- H10D30/6737—Thin-film transistors [TFT] characterised by the electrodes characterised by the electrode materials

- H10D30/6739—Conductor-insulator-semiconductor electrodes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/431—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs having different compositions, shapes, layouts or thicknesses of gate insulators in different TFTs

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/40—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs

- H10D86/60—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates characterised by multiple TFTs wherein the TFTs are in active matrices

-

- H10P95/94—

-

- G—PHYSICS

- G02—OPTICS

- G02F—OPTICAL DEVICES OR ARRANGEMENTS FOR THE CONTROL OF LIGHT BY MODIFICATION OF THE OPTICAL PROPERTIES OF THE MEDIA OF THE ELEMENTS INVOLVED THEREIN; NON-LINEAR OPTICS; FREQUENCY-CHANGING OF LIGHT; OPTICAL LOGIC ELEMENTS; OPTICAL ANALOGUE/DIGITAL CONVERTERS

- G02F1/00—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics

- G02F1/01—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour

- G02F1/13—Devices or arrangements for the control of the intensity, colour, phase, polarisation or direction of light arriving from an independent light source, e.g. switching, gating or modulating; Non-linear optics for the control of the intensity, phase, polarisation or colour based on liquid crystals, e.g. single liquid crystal display cells

- G02F1/133—Constructional arrangements; Operation of liquid crystal cells; Circuit arrangements

- G02F1/136—Liquid crystal cells structurally associated with a semi-conducting layer or substrate, e.g. cells forming part of an integrated circuit

- G02F1/1362—Active matrix addressed cells

- G02F1/136286—Wiring, e.g. gate line, drain line

- G02F1/136295—Materials; Compositions; Manufacture processes

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D30/00—Field-effect transistors [FET]

- H10D30/60—Insulated-gate field-effect transistors [IGFET]

- H10D30/67—Thin-film transistors [TFT]

- H10D30/6704—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device

- H10D30/6713—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes

- H10D30/6715—Thin-film transistors [TFT] having supplementary regions or layers in the thin films or in the insulated bulk substrates for controlling properties of the device characterised by the properties of the source or drain regions, e.g. compositions or sectional shapes characterised by the doping profiles, e.g. having lightly-doped source or drain extensions

Landscapes

- Thin Film Transistor (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

Description

本発明の第1半導体装置は、第1半導体層、第1絶縁膜、第1導電層及び第3絶縁膜がこの順に積層された構造を有する第1回路素子と、第2半導体層、第1絶縁膜よりも膜厚が大きい第2絶縁膜及び第2導電層がこの順に積層された構造を有する第2回路素子とを基板上に有するものである。上記第1半導体装置の好適な形態としては、例えば、(1)第1回路素子及び第2回路素子が薄膜トランジスタ(TFT)である形態、(2)第1回路素子がTFTであり、第2回路素子が保持容量素子である形態が挙げられる。(1)の場合、第1回路素子を第1TFTとし、第2回路素子を第2TFTとすると、第1TFTのゲート絶縁膜(第1絶縁膜)は、第2TFTのゲート絶縁膜(第2絶縁膜)よりも膜厚が小さいことから、第1回路素子は、第2回路素子よりも高速な動作を実現することができる高性能なTFTとして機能することができ、第2回路素子は、第1回路素子よりも絶縁破壊電圧が大きい高耐圧なTFTとして機能することができる。また、(2)の場合、第1回路素子を第3TFTとし、第2回路素子を保持容量素子とすると、第1絶縁膜(第3TFTのゲート絶縁膜)は、第2絶縁膜(保持容量素子の絶縁膜)よりも膜厚が小さいことから、第1回路素子は、高速な動作を実現することができる高性能なTFTとして機能することができ、第2回路素子は、絶縁破壊電圧が大きい高耐圧な保持容量素子として機能することができる。

なお、上記第1半導体装置内のTFTとしては、 トップゲート構造のTFT、デュアルゲート構造のTFT等が挙げられ、微細化の観点からは、トップゲート構造のTFTが好適である。

したがって、本発明の第1半導体装置によれば、信頼性を充分に確保しつつ、高性能化を図ることができる回路素子と高耐圧化を図ることができる回路素子とを同一の基板上に有する半導体装置の量産化を図ることができる。

上記基板としては、絶縁性を有する基板(絶縁基板)が好ましく、例えばガラス基板、プラスチック基板が挙げられる。

上記第2絶縁膜の上層部は、最下層が窒化シリコン又は酸化シリコンからなることが好ましい。これによれば、上記第2絶縁膜の下層部の最上層であるSiNx層上に付着した不純物を、該SiNx層と第2絶縁膜の上層部の最下層であるSiNx層又はSiO2層との界面にトラップすることができる。したがって、第2回路素子の信頼性を向上させることができるため、本発明の第1半導体装置の信頼性をより充分に確保することができる。また、第3絶縁膜は、最下層が窒化シリコン又は酸化シリコンからなることが好ましい。これによれば、上記第1絶縁膜の最上層であるSiNx層上に付着した不純物を、該SiNx層と第3絶縁膜(第1絶縁膜上に配置された部分のうち、第1導電層を介さずに第1絶縁膜上に配置された部分)の最下層であるSiNx層又はSiO2層との界面にトラップすることができる。したがって、第1回路素子の信頼性を向上させることができるため、本発明の第1半導体装置の信頼性をより充分に確保することができる。

なお、第2絶縁膜の上層部は、最下層が窒化シリコンからなることがより好ましい。また、第3絶縁膜は、最下層が窒化シリコンからなることがより好ましい。これらによれば、不純物が付着する界面を構成する膜材料が同一であるため、界面の整合性に優れ、電荷を発生しにくくすることができる。

なお、上述したのと同様の理由により、上記第1絶縁膜、及び、第2絶縁膜の下層部は、酸化シリコン層及び窒化シリコン層がこの順に積層された構造を有し、上記第2絶縁膜の上層部は、窒化シリコン層であることがより好ましい。

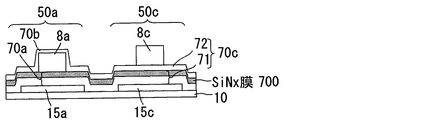

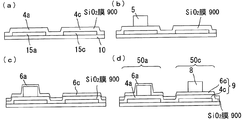

本発明の第2半導体装置は、第1半導体層、第1絶縁膜及び第1導電層がこの順に積層された構造を有する第1回路素子と、第2半導体層、第1絶縁膜よりも膜厚が大きい第2絶縁膜及び第2導電層がこの順に積層された構造を有する第2回路素子とを基板上に有する半導体装置であって、上記第2絶縁膜は、最上層が窒化シリコンからなる下層部と、第1絶縁膜の構造を有する上層部とから構成される半導体装置である(例えば、図2(a)参照。)。本発明の第2半導体装置は、第2絶縁膜の下層部の最上層が窒化シリコンからなる点で、上記第1半導体装置と共通する(例えば、図1及び2(a)参照。)。したがって、本発明の第2半導体装置によれば、第2回路素子に関し、第1半導体装置と同様の作用効果を得ることができる。

なお、上記第1導電層と第2導電層とは、同一の工程で形成されることが好ましい。

なお、上記第3絶縁膜の構造は、単層構造であってもよく、積層構造であってもよい。また、第2絶縁膜の下層部の形態としては、(1)第3絶縁膜の中層部の構造を有する形態、(2)第3絶縁膜の下層部の構造を有する形態、(3)第3絶縁膜の上層部の構造を有する形態、(4)第3絶縁膜の全体の構造を有する形態が挙げられるが、第3絶縁膜の形成する際のパターニング工程等の削減を図る観点からは、(2)及び(3)の形態が好ましく、(4)の形態がより好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の薄膜トランジスタであることが好ましい。

上記第1回路素子及び第2回路素子が薄膜トランジスタである場合、上記第1回路素子又は第2回路素子は、窒化シリコン層を貫通するコンタクトホールを有することが好ましい。

上記第2半導体装置は、第1回路素子が薄膜トランジスタであり、第2回路素子が保持容量素子であることが好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の保持容量素子であることが好ましい。

これらによれば、本発明の第1半導体装置と同様の作用効果を得ることができる。

本発明は更に、上記第2半導体装置の製造方法であって、上記製造方法は、第3絶縁膜の少なくとも一部と第2絶縁膜の下層部とを同一の工程で形成する半導体装置の製造方法でもある。

これらによれば、本発明の第1半導体装置の製造方法と同様の作用効果を得ることができる。

本発明の第3半導体装置は、第1導電層、第1絶縁膜及び第1半導体層がこの順に積層された構造を有する第1回路素子と、第2導電層、第1絶縁膜よりも膜厚が大きい第2絶縁膜、及び、第2半導体層がこの順に積層された構造を有する第2回路素子とを基板上に有する半導体装置であって、上記第1絶縁膜は、最下層が窒化シリコンからなる構造を有し、上記第2絶縁膜は、下層部と、第1絶縁膜の構造を有する上層部とから構成される半導体装置である(例えば、図3(a)参照。)。本発明の第3半導体装置は、第1回路素子及び第2回路素子において、半導体層、絶縁膜及び導電層の積層順序が上下反対であること、及び、第2絶縁膜の下層部(第1半導体装置における第2絶縁膜の上層部に当たる)の構造が必ずしも特定されていないこと以外は、第1半導体装置と共通する(例えば、図1及び3(a)参照。)。したがって、本発明の第3半導体装置によれば、上記第2回路素子に関し、第2絶縁膜の下層部が積層構造を有することにより奏される作用効果を除き、第1半導体装置と同様の作用効果を得ることができる。

なお、上記第3半導体装置内のTFTとしては、 ボトムゲート構造のTFT、デュアルゲート構造のTFT等が挙げられ、ボトムゲート構造のTFTが好適である。

上記第2絶縁膜の下層部は、最下層が窒化シリコンからなることが好ましい。これにより、ガラス基板等からなる基板からのNa等の可動イオンの拡散を防止し、TFT等の第2回路素子の信頼性を保つことができる。

なお、上記第3絶縁膜の構造は、単層構造であってもよく、積層構造であってもよい。また、第2絶縁膜の下層部の形態としては、(1)第3絶縁膜の中層部の構造を有する形態、(2)第3絶縁膜の下層部の構造を有する形態、(3)第3絶縁膜の上層部の構造を有する形態、(4)第3絶縁膜の全体の構造を有する形態が挙げられるが、第3絶縁膜の形成する際のパターニング工程等の削減を図る観点からは、(2)及び(3)の形態が好ましく、(4)の形態がより好ましい。

上記第2絶縁膜の下層部は、最上層が酸化シリコンからなることが好ましい。

上記第1絶縁膜及び第2絶縁膜は、最上層が酸化シリコンからなることが好ましい。

上記第1絶縁膜、及び、第2絶縁膜の上層部は、窒化シリコン層及び酸化シリコン層がこの順に積層された構造を有し、上記第2絶縁膜の下層部は、窒化シリコン層であることが好ましい。

上記第1絶縁膜、及び、第2絶縁膜の上層部は、窒化シリコン層及び酸化シリコン層がこの順に積層された構造を有し、上記第2絶縁膜の下層部は、酸化シリコン層であることが好ましい。

上記第3半導体装置は、第1回路素子及び第2回路素子が薄膜トランジスタであることが好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の薄膜トランジスタであることが好ましい。

上記第3半導体装置は、第1回路素子が薄膜トランジスタであり、第2回路素子が保持容量素子であることが好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の保持容量素子であることが好ましい。

これらによれば、本発明の第1半導体装置と同様の作用効果を得ることができる。

本発明は更に、上記第3半導体装置の製造方法であって、上記製造方法は、第3絶縁膜の少なくとも一部と第2絶縁膜の下層部とを同一の工程で形成する半導体装置の製造方法でもある。これらによれば、本発明の第1半導体装置の製造方法と同様の作用効果を得ることができる。

本発明の第4半導体装置は、第1導電層、第1絶縁膜及び第1半導体層がこの順に積層された構造を有する第1回路素子と、第2導電層、第1絶縁膜よりも膜厚が大きい第2絶縁膜、及び、第2半導体層がこの順に積層された構造を有する第2回路素子とを基板上に有する半導体装置であって、上記第2絶縁膜は、第1絶縁膜の構造を有する下層部と、最下層が窒化シリコンからなる上層部とから構成される半導体装置である(例えば、図4(a)参照。)。

本発明の第4半導体装置は、第2絶縁膜の上層部の最下層がSiNxからなる点で、上記第3半導体装置と共通する(例えば、図3及び4(a)参照。)。したがって、本発明の第4半導体装置によれば、上記第2回路素子に関し、第3半導体装置と同様の作用効果を得ることができる。

なお、上記第4半導体装置内のTFTとしては、 ボトムゲート構造のTFT、デュアルゲート構造のTFT等が挙げられ、ボトムゲート構造のTFTが好適である。

なお、上記第1導電層と第2導電層とは、同一の工程で形成されることが好ましい。

なお、上記第3絶縁膜の構造は、単層構造であってもよく、積層構造であってもよい。また、上記第2絶縁膜の上層部の形態としては、(1)第3絶縁膜の中層部の構造を有する形態、(2)第3絶縁膜の下層部の構造を有する形態、(3)第3絶縁膜の上層部の構造を有する形態、(4)第3絶縁膜の全体の構造を有する形態が挙げられるが、第3絶縁膜の形成する際のパターニング工程等の削減を図る観点からは、(2)及び(3)の形態が好ましく、(4)の形態がより好ましい。

上記第1絶縁膜、及び、第2絶縁膜の下層部は、最上層が酸化シリコンからなることが好ましい。

上記第1絶縁膜及び第2絶縁膜は、最上層が酸化シリコンからなることが好ましい。

上記第1絶縁膜、及び、第2絶縁膜の下層部は、窒化シリコン層であり、上記第2絶縁膜の上層部は、窒化シリコン層及び酸化シリコン層がこの順に積層された構造を有することが好ましい。

上記第1絶縁膜、及び、第2絶縁膜の下層部は、酸化シリコン層であり、上記第2絶縁膜の上層部は、窒化シリコン層及び酸化シリコン層がこの順に積層された構造を有することが好ましい。

上記第4半導体装置は、第1回路素子及び第2回路素子が薄膜トランジスタであることが好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の薄膜トランジスタであることが好ましい。

上記第4半導体装置は、第1回路素子が薄膜トランジスタであり、第2回路素子が保持容量素子であることが好ましい。

上記第1回路素子は、駆動回路部の薄膜トランジスタであり、上記第2回路素子は、画素回路部の保持容量素子であることが好ましい。

これらによれば、本発明の第1半導体装置と同様の作用効果を得ることができる。

本発明は更に、上記第4半導体装置の製造方法であって、上記製造方法は、第3絶縁膜の少なくとも一部と第2絶縁膜の上層部とを同一の工程で形成する半導体装置の製造方法でもある。

これらによれば、本発明の第1半導体装置の製造方法と同様の作用効果を得ることができる。

図5は、本発明の実施形態1に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

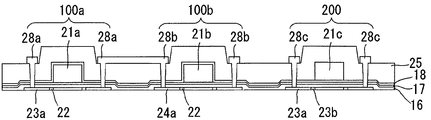

本実施形態に係るアクティブマトリクス基板は、図5に示すように、駆動回路用オフセット構造のトップゲート型NチャネルTFT(第1回路素子)100a及びトップゲート型PチャネルTFT(第1回路素子)100b、並びに、画素スイッチング用LDD(Lightly Doped Drain)構造のトップゲート型NチャネルTFT(第2回路素子)200等をガラス基板10上に有するものである。図5に示すように、TFT100a、100bのゲート絶縁膜(第1絶縁膜)は、酸化シリコン(SiO2)膜16及び窒化シリコン(SiNx)膜17の2層構造を有する。これに対し、TFT200のゲート絶縁膜(第2絶縁膜)は、SiO2膜16、SiNx膜17及びSiNx膜18の3層構造を有する。

以下、図6−1(a)〜(f)及び6−2(a)〜(g)を用いて、本実施形態に係るアクティブマトリクス基板の製造工程を説明する。

次に、図6−1(c)に示すように、p−Si膜14を各TFTのサイズにパターニングすることにより、p−Si層(第1半導体層)15a、15b及びp−Si層(第2半導体層)15cを形成する。

続いて、アニール(活性化アニール)を行うことにより、注入した不純物を活性化させる。

したがって、本実施形態の製造方法によれば、高い信頼性を有するアクティブマトリクス基板を作製することができる。

図7は、本発明の実施形態2に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

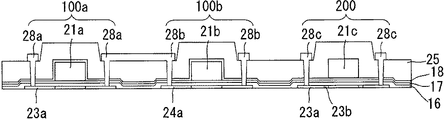

本実施形態に係るアクティブマトリクス基板は、駆動回路用TFT100a、100bがセルフアライン構造を有すること以外は、実施形態1に係るアクティブマトリクス基板と同様である。すなわち、本実施形態に係るアクティブマトリクス基板は、図7に示すように、駆動回路用セルフアライン構造のトップゲート型NチャネルTFT(第1回路素子)100a及びトップゲート型PチャネルTFT(第1回路素子)100b、並びに、画素スイッチング用LDD構造のトップゲート型NチャネルTFT(第2回路素子)200等をガラス基板10上に有するものである。図7に示すように、TFT100a、100bのゲート絶縁膜(第1絶縁膜)は、酸化シリコン(SiO2)膜16及び窒化シリコン(SiNx)膜17の2層構造を有する。これに対し、TFT200のゲート絶縁膜(第2絶縁膜)は、SiO2膜16、SiNx膜17及びSiNx膜18の3層構造を有する。

以下、図6−1(a)〜(f)及び図8(a)〜(h)を用いて、本実施形態に係るアクティブマトリクス基板の製造工程を説明する。

次に、図8(a)に示すように、p−Si層15a、15bに不純物3を注入する。具体的には、p−Si層15aにはリンイオン(P+)を注入し、p−Si層15bにはホウ素イオン(B+)を注入する。これにより、p−Si層15aには、n型の高濃度不純物領域23aが自己整合的に形成され、p−Si層15bには、p型の高濃度不純物領域24aが自己整合的に形成される。

続いて、アニール(活性化アニール)を行うことにより、注入した不純物を活性化させる。

続いて、アニール(水素化アニール)を行うことにより、p−Si層15a〜15cを水素化し、ダングリングボンド(未結合手)をターミネート(終端化)させる。

本実施形態によっても、SiNx膜17により、実施形態1と同様の作用効果を得ることができる。

図9は、本発明の実施形態3に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

本実施形態に係るアクティブマトリクス基板は、図9に示すように、駆動回路用セルフアライン構造のトップゲート型NチャネルTFT(第1回路素子)100a及びトップゲート型PチャネルTFT(第1回路素子)100b、並びに、トップゲート型NチャネルTFT(第2回路素子)200等をガラス基板10上に有するものである。図9に示すように、TFT100a、100bのゲート絶縁膜(第1絶縁膜)が酸化シリコン(SiO2)膜63及び窒化シリコン(SiNx)膜64の2層構造を有する。これに対し、TFT200のゲート絶縁膜(第2絶縁膜)は、SiO2膜61、SiNx膜62、SiO2膜63及びSiNx膜64の4層構造を有する。

以下、図6−1(a)〜(e)及び図10(a)〜(f)を用いて、本実施形態に係るアクティブマトリクス基板の製造工程を説明する。

次に、SiO2膜16及びSiNx膜17上にフォトレジスト層を形成した後、4層構造のゲート絶縁膜とするところ以外をウェットエッチングで除去することにより、図10(a)に示すように、p−Si層15cを被覆するSiO2膜61及びSiNx膜62を形成する。

続いて、アニール(活性化アニール)を行うことにより、注入した不純物を活性化させる。

続いて、アニール(水素化アニール)を行うことにより、p−Si層15a〜15cを水素化し、ダングリングボンド(未結合手)をターミネート(終端化)させる。

したがって、本実施形態の製造方法によれば、高い信頼性を有するアクティブマトリクス基板を作製することができる。

図11は、本発明の実施形態4に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

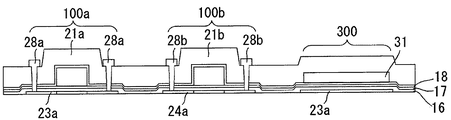

本実施形態に係るアクティブマトリクス基板は、図11に示すように、駆動回路用セルフアライン構造のトップゲート型NチャネルTFT(第1回路素子)100a及びトップゲート型PチャネルTFT(第1回路素子)100b、並びに、保持容量(Cs)素子(第2回路素子)300等をガラス基板10上に有するものである。図11に示すように、TFT100a、100bのゲート絶縁膜(第1絶縁膜)が酸化シリコン(SiO2)膜16及び窒化シリコン(SiNx)膜17の2層構造を有する。これに対し、Cs素子300の絶縁膜(第2絶縁膜)は、SiO2膜16、SiNx膜17及びSiNx膜18の3層構造を有する。

以下、図6−1(a)〜(f)及び図12(a)〜(g)を用いて、本実施形態に係るアクティブマトリクス基板の製造工程を説明する。

次に、図12(a)に示すように、p−Si層15a〜15cに不純物3を注入する。具体的には、p−Si層15a、15cにはリンイオン(P+)を注入し、p−Si層15bにはホウ素イオン(B+)を注入する。これにより、p−Si層15aには、n型の高濃度不純物領域23aが自己整合的に形成され、p−Si層15bには、p型の高濃度不純物領域24aが自己整合的に形成される。また、p−Si層15cは、全体がn型の高濃度不純物領域23aとなる。

続いて、アニール(活性化アニール)を行うことにより、注入した不純物を活性化させる。

続いて、アニール(水素化アニール)を行うことにより、p−Si層15a〜15cを水素化し、ダングリングボンド(未結合手)をターミネート(終端化)させる。

本実施形態によっても、SiNX膜17により、実施形態1と同様の作用効果を得ることができる。

図13は、本発明の実施形態5に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

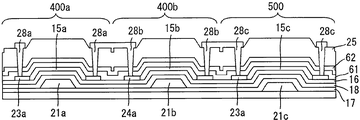

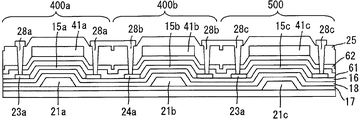

本実施形態に係るアクティブマトリクス基板は、図13に示すように、駆動回路用セルフアライン構造のボトムゲート型NチャネルTFT(第1回路素子)400a及びボトムゲート型NチャネルTFT(第1回路素子)400b、並びに、画素スイッチング用セルフアライン構造のボトムゲート型NチャネルTFT(第2回路素子)500等をガラス基板10上に有するものである。図13に示すように、TFT400a、400bのゲート絶縁膜(第1絶縁膜)は、窒化シリコン(SiNx)膜18、酸化シリコン(SiO2)膜16の2層構造を有するのに対し、TFT500のゲート絶縁膜(第2絶縁膜)は、SiNx膜17、SiNx膜18及びSiO2膜16の3層構造を有する。

以下、図14−1(a)〜(h)及び14−2(a)〜(c)を用いて、本実施形態に係るアクティブマトリクス基板の製造工程を説明する。

次に、図14−1(c)に示すように、ゲート電極(第1導電層)21a、21bを形成する。ゲート電極21a、21bの材料、膜厚及び形成方法は、ゲート電極21cと異なっていてもよい。

次に、図14−1(f)に示すように、p−Si膜14を各TFTのサイズにパターニングすることにより、p−Si層(第1半導体層)15a、15b及びp−Si層(第2半導体層)15cを形成する。

なお、H2プラズマ又はH2ガス2への暴露は、SiO2膜61の形成後に行ってもよい。

続いて、アニール(活性化アニール)を行うことにより、注入した不純物を活性化させる。

したがって、本実施形態の製造方法によれば、高い信頼性を有するアクティブマトリクス基板を作製することができる。

図15は、本発明の実施形態6に係るアクティブマトリクス基板(半導体装置)の構成を示す断面模式図である。

本実施形態に係るアクティブマトリクス基板は、図15に示すように、駆動回路用セルフアライン構造のNチャネルTFT(第1回路素子)400a、NチャネルTFT(第1回路素子)400b、及び、画素スイッチング用セルフアライン構造のNチャネルTFT(第2回路素子)500が、デュアルゲート型であること以外は、実施形態5に係るアクティブマトリクス基板と同様の構成を有する。すなわち、本実施形態の製造方法は、上層ゲート電極41a〜41cを形成する工程を含むこと以外は、実施形態5の製造方法と同様である。したがって、本実施形態の製造方法によっても、高い信頼性を有するアクティブマトリクス基板を作製することができる。

本実験では、酸化シリコン(SiO2)と窒化シリコン(SiNx)とのプラズマ耐性を比較する実験を行った。具体的には、膜厚70nmのSiO2層からなるゲート絶縁膜を成膜した後、酸素(O2)プラズマ処理(誘導結合プラズマ(ICP)条件:Bias400W)を施したTFTについて、BTS(bias temperature stress)試験(BTS条件:150℃、+20V、30分間)前後の閾値電圧(Vth)特性の変化を調べた。一方、膜厚50nmのSiO2層(下層)及び膜厚40nmのSiNx層(上層)の2層構造からなるゲート絶縁膜(EOT≒70nm)を有するTFTについても、同様の試験を行った。その結果を図16及び17に示す。

以上により、SiNxは、SiO2よりも高いO2プラズマ耐性を有することが分かった。

2:水素(H2)プラズマ又はH2ガス

3:不純物

4a:第1ゲート絶縁膜(第1絶縁膜)

4c:第2ゲート絶縁膜(第2絶縁膜)の下層部

5:第1ゲート電極(第1導電層)

6a:第3絶縁膜(その下層部、中層部、上層部又は全体)

6c:第2ゲート絶縁膜(第2絶縁膜)の上層部

7a:第1ゲート絶縁膜(第1絶縁膜)の最下層

7c:第2ゲート絶縁膜(第2絶縁膜)の下層部の最下層

8:第2ゲート電極(第2導電層)

8a:第1ゲート電極(第1導電層)

8c:第2ゲート電極(第2導電層)

9:第2ゲート絶縁膜(第2絶縁膜)

10:ガラス基板(基板)

11:水素バリア及び不純物拡散防止膜

12:緩衝膜

13:アモルファスシリコン(a−Si)膜

14:ポリシリコン(p−Si)膜

15a、15b:p−Si層(第1半導体層)

15c:p−Si層(第2半導体層)

16、61、63:酸化シリコン(SiO2)膜

17、18、62、64:窒化シリコン(SiNx)膜

19、68:フォトレジスト層

21a、21b:ゲート電極(第1導電層)

21c:ゲート電極(第2導電層)

22:オフセット(offset)領域

23a:n型の高濃度不純物領域

23b:n型の低濃度不純物領域(LDD領域)

24a:p型の高濃度不純物領域

25:層間絶縁膜

27a〜27c:コンタクトホール

28a〜28c:ソース電極

31:保持容量配線(第2導電層)

35:金属膜

41a〜41c:上層ゲート電極

50a:第1TFT(第1回路素子)

50c:第2TFT(第2回路素子)

70a:第1ゲート絶縁膜(第1絶縁膜)

70b:第3絶縁膜(その下層部、中層部、上層部又は全体)

70c:第2ゲート絶縁膜(第2絶縁膜)

71:第2ゲート絶縁膜(第2絶縁膜)の下層部

72:第2ゲート絶縁膜(第2絶縁膜)の上層部

100a、400a:駆動回路用NチャネルTFT(第1回路素子)

100b、400b:駆動回路用PチャネルTFT(第1回路素子)

200、500:画素スイッチング用TFT(第2回路素子)

300:保持容量素子(第2回路素子)

700:SiNx膜

900:SiO2膜

Claims (19)

- 第1半導体層、第1絶縁膜、第1導電層及び第3絶縁膜がこの順に積層された構造を有する第1回路素子と、第2半導体層、第1絶縁膜よりも膜厚が大きい第2絶縁膜及び第2導電層がこの順に積層された構造を有する第2回路素子とを基板上に有する半導体装置であって、

該第1絶縁膜は、最上層が窒化シリコンからなる積層構造を有し、

該第2絶縁膜は、第1絶縁膜の積層構造を有する下層部と、第1導電層上の第3絶縁膜の構造を含む上層部とから構成され、

該第1絶縁膜、及び、第2絶縁膜の下層部は、酸化シリコン層及び窒化シリコン層がこの順に積層された構造を有し、

該第2絶縁膜の上層部は、窒化シリコン層であり、

該第1絶縁膜、及び、第2絶縁膜の下層部がそれぞれ有する該酸化シリコン層及び該窒化シリコン層、並びに、該第2絶縁膜の上層部である該窒化シリコン層は、プラズマ化学的気相成長法で形成されたものである

ことを特徴とする半導体装置。 - 前記半導体装置は、第1回路素子及び第2回路素子が薄膜トランジスタであることを特徴とする請求項1記載の半導体装置。

- 前記第1回路素子は、駆動回路部の薄膜トランジスタであり、

前記第2回路素子は、画素回路部の薄膜トランジスタであることを特徴とする請求項2記載の半導体装置。 - 前記第1回路素子又は第2回路素子は、窒化シリコン層を貫通するコンタクトホールを有することを特徴とする請求項1記載の半導体装置。

- 前記半導体装置は、第1回路素子が薄膜トランジスタであり、第2回路素子が保持容量素子であることを特徴とする請求項1記載の半導体装置。

- 前記第1回路素子は、駆動回路部の薄膜トランジスタであり、

前記第2回路素子は、画素回路部の保持容量素子であることを特徴とする請求項5記載の半導体装置。 - 請求項1記載の半導体装置の製造方法であって、

該製造方法は、第1絶縁膜と第2絶縁膜の下層部とを同一の工程で形成することを特徴とする半導体装置の製造方法。 - 請求項1記載の半導体装置の製造方法であって、

該製造方法は、第3絶縁膜の少なくとも一部と第2絶縁膜の上層部とを同一の工程で形成することを特徴とする半導体装置の製造方法。 - 第1半導体層、第1絶縁膜及び第1導電層がこの順に積層された構造を有する第1回路素子と、第2半導体層、第1絶縁膜よりも膜厚が大きい第2絶縁膜及び第2導電層がこの順に積層された構造を有する第2回路素子とを基板上に有する半導体装置であって、

該第2絶縁膜は、最上層が窒化シリコンからなる下層部と、第1絶縁膜の構造を有する上層部とから構成され、

該第1絶縁膜、及び、第2絶縁膜の下層部、並びに、第2絶縁膜の上層部は、酸化シリコン層及び窒化シリコン層がこの順に積層された構造を有し、

該第1絶縁膜、及び、第2絶縁膜の下層部、並びに、第2絶縁膜の上層部がそれぞれ有する該酸化シリコン層及び該窒化シリコン層は、プラズマ化学的気相成長法で形成されたものである

ことを特徴とする半導体装置。 - 前記第1回路素子は、第1半導体層下に、第3絶縁膜を有し、

前記第2絶縁膜の下層部は、第1半導体層下の第3絶縁膜の構造を含むことを特徴とする請求項9記載の半導体装置。 - 前記半導体装置は、第1回路素子及び第2回路素子が薄膜トランジスタであることを特徴とする請求項9記載の半導体装置。

- 前記第1回路素子は、駆動回路部の薄膜トランジスタであり、

前記第2回路素子は、画素回路部の薄膜トランジスタであることを特徴とする請求項11記載の半導体装置。 - 前記第1回路素子又は第2回路素子は、窒化シリコン層を貫通するコンタクトホールを有することを特徴とする請求項9記載の半導体装置。

- 前記半導体装置は、第1回路素子が薄膜トランジスタであり、第2回路素子が保持容量素子であることを特徴とする請求項9記載の半導体装置。

- 前記第1回路素子は、駆動回路部の薄膜トランジスタであり、

前記第2回路素子は、画素回路部の保持容量素子であることを特徴とする請求項14記載の半導体装置。 - 請求項9記載の半導体装置の製造方法であって、

該製造方法は、第1絶縁膜と第2絶縁膜の上層部とを同一の工程で形成することを特徴とする半導体装置の製造方法。 - 請求項10記載の半導体装置の製造方法であって、

該製造方法は、第3絶縁膜の少なくとも一部と第2絶縁膜の下層部とを同一の工程で形成することを特徴とする半導体装置の製造方法。 - 前記窒化シリコン層を構成する材料は、四窒化三ケイ素であることを特徴とする請求項1又は9記載の半導体装置。

- 請求項1又は9記載の半導体装置を含んで構成されることを特徴とする表示装置。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2007553828A JP5154951B2 (ja) | 2006-01-12 | 2006-09-06 | 半導体装置及び表示装置 |

Applications Claiming Priority (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006005402 | 2006-01-12 | ||

| JP2006005402 | 2006-01-12 | ||

| JP2007553828A JP5154951B2 (ja) | 2006-01-12 | 2006-09-06 | 半導体装置及び表示装置 |

| PCT/JP2006/317641 WO2007080672A1 (ja) | 2006-01-12 | 2006-09-06 | 半導体装置及び表示装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2007080672A1 JPWO2007080672A1 (ja) | 2009-06-11 |

| JP5154951B2 true JP5154951B2 (ja) | 2013-02-27 |

Family

ID=38256086

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007553828A Expired - Fee Related JP5154951B2 (ja) | 2006-01-12 | 2006-09-06 | 半導体装置及び表示装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7700995B2 (ja) |

| JP (1) | JP5154951B2 (ja) |

| CN (1) | CN101356650B (ja) |

| WO (1) | WO2007080672A1 (ja) |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12120919B2 (en) | 2021-06-11 | 2024-10-15 | Samsung Display Co., Ltd. | Display apparatus and method of manufacturing the same |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8227808B2 (en) * | 2007-12-06 | 2012-07-24 | Chimei Innolux Corporation | Method for manufacturing thin film transistor (TFT) and OLED display having TFTS manufactured by the same |

| KR102219095B1 (ko) | 2009-09-24 | 2021-02-23 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제조 방법 |

| KR20120084751A (ko) | 2009-10-05 | 2012-07-30 | 가부시키가이샤 한도오따이 에네루기 켄큐쇼 | 반도체 장치 및 그 제작 방법 |

| EP2494601A4 (en) | 2009-10-30 | 2016-09-07 | Semiconductor Energy Lab | SEMICONDUCTOR COMPONENT AND MANUFACTURING METHOD THEREFOR |

| US8053818B2 (en) * | 2009-12-18 | 2011-11-08 | Palo Alto Research Center Incorporated | Thin film field effect transistor with dual semiconductor layers |

| CN102194679B (zh) * | 2010-03-15 | 2013-08-14 | 中芯国际集成电路制造(上海)有限公司 | 半导体器件的制作方法 |

| US9147613B2 (en) * | 2010-05-07 | 2015-09-29 | Intersil Americas LLC | Method of forming an insulator layer in a semiconductor structure and structures resulting therefrom |

| US9305941B2 (en) * | 2012-11-02 | 2016-04-05 | Apple Inc. | Device and method for improving AMOLED driving |

| US9293512B2 (en) * | 2012-11-02 | 2016-03-22 | Apple Inc. | Device and method for improving AMOLED driving |

| CN103456765B (zh) * | 2013-09-10 | 2015-09-16 | 深圳市华星光电技术有限公司 | 有源式有机电致发光器件背板及其制作方法 |

| CN104091810A (zh) * | 2014-06-30 | 2014-10-08 | 京东方科技集团股份有限公司 | 阵列基板及其制作方法、显示装置 |

| CN105070724A (zh) * | 2015-07-16 | 2015-11-18 | 深圳市华星光电技术有限公司 | Tft基板的制作方法及制得的tft基板 |

| CN108463889B (zh) * | 2016-03-31 | 2020-11-06 | 华为技术有限公司 | 场效应管及其制造方法 |

| JP2017220174A (ja) * | 2016-06-10 | 2017-12-14 | 株式会社ジャパンディスプレイ | 表示装置 |

| CN107170784A (zh) * | 2017-05-25 | 2017-09-15 | 京东方科技集团股份有限公司 | 一种oled阵列基板及其制备方法和oled显示装置 |

| CN107068771B (zh) * | 2017-06-01 | 2020-08-04 | 武汉华星光电技术有限公司 | 低温多晶硅薄膜晶体管及其制造方法 |

| KR102601596B1 (ko) * | 2019-06-17 | 2023-11-10 | 어플라이드 머티어리얼스, 인코포레이티드 | 박막 트랜지스터들을 형성하는 방법 |

| KR102740671B1 (ko) * | 2020-04-17 | 2024-12-10 | 삼성디스플레이 주식회사 | 표시 장치 및 그 제조 방법 |

| CN112186042B (zh) * | 2020-10-13 | 2024-05-21 | 京东方科技集团股份有限公司 | 薄膜晶体管及其制备方法、显示装置 |

| US20240250133A1 (en) * | 2022-09-30 | 2024-07-25 | Taiwan Semiconductor Manufacturing Company, Ltd. | Semiconductor device and manufacturing method thereof |

Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05152569A (ja) * | 1991-11-25 | 1993-06-18 | Casio Comput Co Ltd | 電界効果型薄膜トランジスタおよびその製造方法 |

| JPH07130668A (ja) * | 1993-09-08 | 1995-05-19 | Seiko Epson Corp | 半導体膜形成方法及び薄膜半導体装置の製造方法と、基板熱処理方法及び化学気相堆積方法 |

| JPH1027778A (ja) * | 1996-07-09 | 1998-01-27 | Komatsu Ltd | 表面処理装置及びこれに用いられるノズル |

| JPH11168215A (ja) * | 1997-12-03 | 1999-06-22 | Seiko Epson Corp | アクティブマトリクス基板およびその製造方法、並びに液晶表示装置 |

| JPH11281943A (ja) * | 1998-03-31 | 1999-10-15 | Sanyo Electric Co Ltd | 液晶表示装置の膜厚設定方法及び液晶表示装置 |

| JP2000304603A (ja) * | 1999-04-20 | 2000-11-02 | Tdk Corp | 赤外線検出器 |

| JP2003045892A (ja) * | 2001-08-02 | 2003-02-14 | Fujitsu Display Technologies Corp | 薄膜トランジスタ装置及びその製造方法 |

| JP2005012003A (ja) * | 2003-06-19 | 2005-01-13 | Sharp Corp | 結晶質半導体膜およびその製造方法 |

| JP2005260168A (ja) * | 2004-03-15 | 2005-09-22 | Sharp Corp | トランジスタを備えた装置およびその製造方法 |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH04171767A (ja) * | 1990-11-02 | 1992-06-18 | Sharp Corp | 薄膜トランジスタ及びその製造方法 |

| JP2666103B2 (ja) | 1992-06-03 | 1997-10-22 | カシオ計算機株式会社 | 薄膜半導体装置 |

| US5614731A (en) * | 1993-03-15 | 1997-03-25 | Kabushiki Kaisha Toshiba | Thin-film transistor element having a structure promoting reduction of light-induced leakage current |

| US6005270A (en) * | 1997-11-10 | 1999-12-21 | Sony Corporation | Semiconductor nonvolatile memory device and method of production of same |

| JP2005072461A (ja) | 2003-08-27 | 2005-03-17 | Seiko Epson Corp | 半導体装置の製造方法、半導体装置、電気光学装置および電子機器 |

-

2006

- 2006-09-06 US US12/093,791 patent/US7700995B2/en not_active Expired - Fee Related

- 2006-09-06 WO PCT/JP2006/317641 patent/WO2007080672A1/ja not_active Ceased

- 2006-09-06 CN CN2006800509335A patent/CN101356650B/zh not_active Expired - Fee Related

- 2006-09-06 JP JP2007553828A patent/JP5154951B2/ja not_active Expired - Fee Related

Patent Citations (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH05152569A (ja) * | 1991-11-25 | 1993-06-18 | Casio Comput Co Ltd | 電界効果型薄膜トランジスタおよびその製造方法 |

| JPH07130668A (ja) * | 1993-09-08 | 1995-05-19 | Seiko Epson Corp | 半導体膜形成方法及び薄膜半導体装置の製造方法と、基板熱処理方法及び化学気相堆積方法 |

| JPH1027778A (ja) * | 1996-07-09 | 1998-01-27 | Komatsu Ltd | 表面処理装置及びこれに用いられるノズル |

| JPH11168215A (ja) * | 1997-12-03 | 1999-06-22 | Seiko Epson Corp | アクティブマトリクス基板およびその製造方法、並びに液晶表示装置 |

| JPH11281943A (ja) * | 1998-03-31 | 1999-10-15 | Sanyo Electric Co Ltd | 液晶表示装置の膜厚設定方法及び液晶表示装置 |

| JP2000304603A (ja) * | 1999-04-20 | 2000-11-02 | Tdk Corp | 赤外線検出器 |

| JP2003045892A (ja) * | 2001-08-02 | 2003-02-14 | Fujitsu Display Technologies Corp | 薄膜トランジスタ装置及びその製造方法 |

| JP2005012003A (ja) * | 2003-06-19 | 2005-01-13 | Sharp Corp | 結晶質半導体膜およびその製造方法 |

| JP2005260168A (ja) * | 2004-03-15 | 2005-09-22 | Sharp Corp | トランジスタを備えた装置およびその製造方法 |

Cited By (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US12120919B2 (en) | 2021-06-11 | 2024-10-15 | Samsung Display Co., Ltd. | Display apparatus and method of manufacturing the same |

Also Published As

| Publication number | Publication date |

|---|---|

| US20090159894A1 (en) | 2009-06-25 |

| US7700995B2 (en) | 2010-04-20 |

| CN101356650A (zh) | 2009-01-28 |

| WO2007080672A1 (ja) | 2007-07-19 |

| CN101356650B (zh) | 2012-04-04 |

| JPWO2007080672A1 (ja) | 2009-06-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5154951B2 (ja) | 半導体装置及び表示装置 | |

| KR101847355B1 (ko) | 박막 트랜지스터 및 그 제조 방법과 디스플레이 장치 | |

| JP6502454B2 (ja) | 半導体装置 | |

| JP6951103B2 (ja) | 半導体装置、及び半導体装置の作製方法 | |

| JP5670028B2 (ja) | トランジスタとこれを含む半導体素子及びそれらの製造方法 | |

| CN101681931B (zh) | 电路基板和显示装置 | |

| US20050285197A1 (en) | Thin film transistor and method of fabricating the same | |

| US20100044699A1 (en) | Thin film transistor and method of fabricating the same | |

| JP2017199901A (ja) | 半導体装置、及び半導体装置の作製方法 | |

| WO2016076168A1 (ja) | 半導体装置およびその製造方法 | |

| JP2007220816A (ja) | 薄膜トランジスタ及びその製法 | |

| JP2007220818A (ja) | 薄膜トランジスタ及びその製法 | |

| US20210399133A1 (en) | Semiconductor device and manufacturing method thereof | |

| CN110299368A (zh) | 有源矩阵基板及其制造方法 | |

| CN101263604B (zh) | 薄膜晶体管 | |

| JP2006229185A (ja) | 薄膜トランジスタ基板、その製造方法、半導体装置及び液晶表示装置 | |

| KR20110080118A (ko) | 다층의 식각 정지층을 구비한 박막 트랜지스터 및 그 제조방법 | |

| WO2016104253A1 (ja) | 半導体装置 | |

| US20200388709A1 (en) | Thin film transistor, method for manufacturing same, and display apparatus | |

| US7335915B2 (en) | Image displaying device and method for manufacturing same | |

| JP2009117717A (ja) | 半導体装置及びその製造方法 | |

| CN107004603B (zh) | 半导体装置及其制造方法 | |

| CN101300681B (zh) | 半导体装置及其制造方法 | |

| JP2007157986A (ja) | トランジスタを備えた装置 | |

| JP2007123297A (ja) | 半導体装置及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110301 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110414 |

|

| RD02 | Notification of acceptance of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7422 Effective date: 20110414 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110809 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111024 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20111101 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20111125 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20121023 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20121206 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20151214 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5154951 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |