JP5094441B2 - 演算増幅器 - Google Patents

演算増幅器 Download PDFInfo

- Publication number

- JP5094441B2 JP5094441B2 JP2008009991A JP2008009991A JP5094441B2 JP 5094441 B2 JP5094441 B2 JP 5094441B2 JP 2008009991 A JP2008009991 A JP 2008009991A JP 2008009991 A JP2008009991 A JP 2008009991A JP 5094441 B2 JP5094441 B2 JP 5094441B2

- Authority

- JP

- Japan

- Prior art keywords

- current

- conversion circuit

- voltage

- potential

- output

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/45—Differential amplifiers

- H03F3/45071—Differential amplifiers with semiconductor devices only

- H03F3/45076—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier

- H03F3/45179—Differential amplifiers with semiconductor devices only characterised by the way of implementation of the active amplifying circuit in the differential amplifier using MOSFET transistors as the active amplifying circuit

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F3/00—Amplifiers with only discharge tubes or only semiconductor devices as amplifying elements

- H03F3/30—Single-ended push-pull [SEPP] amplifiers; Phase-splitters therefor

- H03F3/3001—Single-ended push-pull [SEPP] amplifiers; Phase-splitters therefor with field-effect transistors

- H03F3/3022—CMOS common source output SEPP amplifiers

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45248—Indexing scheme relating to differential amplifiers the dif amp being designed for improving the slew rate

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03F—AMPLIFIERS

- H03F2203/00—Indexing scheme relating to amplifiers with only discharge tubes or only semiconductor devices as amplifying elements covered by H03F3/00

- H03F2203/45—Indexing scheme relating to differential amplifiers

- H03F2203/45612—Indexing scheme relating to differential amplifiers the IC comprising one or more input source followers as input stages in the IC

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Amplifiers (AREA)

Description

4,R5の抵抗値をr4,r5とすると、(r4+r5)/r5倍し、本発明の演算増幅

器をボルテージホロワとして用いたバッファを介して出力している。この回路では、レベ

ル変換回路の低電力化を行うため、演算増幅器の前段の情報を用いてバイアス電流を制御

している。なお、演算増幅器前段の増幅回路の構成は、実施例の形式に限定されない。

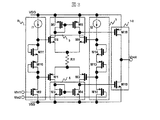

ってバイアスされた差動トランジスタ対M21,M22によって電流に変換される。変換

された電流は、M23とM25、M24とM26のカレントミラー対によって折り返され

る。M25で折り返された電流は、ゲート接地回路M27を介してVDD2よりも高い電

源VDDに接続されたカレントミラーM29,M30で再び折り返される。この電流は、

M26によって折り返された電流と比較され、ソースフォロワを構成するM31に入力さ

れる。抵抗R4、R5で分圧された電圧がVinと等しくなるように帰還がかかるため、

ソースフォロワの出力電位は、Vinの(r4+r5)/r5倍となる。この電圧は、ボ

ルテージホロワとして用いられる本発明の演算増幅器に入力され、バッファされて出力さ

れる。演算増幅器のレベル変換回路15,16は、前段のM29,M30で構成されるカ

レントミラーを用いて、バイアス電流を生成している。演算増幅器の入力Vin1,Vi

n2が増加したときには、M32,M33が流すバイアス電流がレベル変換回路出力の動

作速度が遅くなってしまうため、バイアス電流を多く流すことが求められる。一方。Vi

n1,Vin2が減少したときには、M9,M12がレベル変換回路の動作速度を決定す

るため、バイアス電流は小さくても良い。また、変化しないときには、レベル変換回路は

定常状態であるため電流は少なくても良い。このように、レベル変換回路のバイアス電流

が動作速度を決めているのは、演算増幅器の入力電圧が増加する場合である。前段のM2

9に流れる電流は、演算増幅器の入力電圧が増加する場合に多く、減少または入力が等し

い場合には減少するので、M29を用いてレベル変換回路の電流を生成することで、定常

状態での電力消費量を減少させることができる。

3,4,8,9,13,14‥‥電流電圧変換回路、

5,10‥‥出力段、

M1,M2,M7,M8,M9,M10,M12,M13,M16,M19,M20,M21,M22,M29,M30‥‥PMOS、

M3,M4,M5,M6,M9,M10,M11,M14,M15,M17,M18,M23,M24,M25,M26,M27,M28,M31‥‥NMOS、

I1,I2,I3‥‥定電流源、

D1〜D8‥‥耐圧保護用ダイオード、

R1,R2,R3,R4,R5‥‥抵抗。

Claims (18)

- 差動入力信号のレベルを変換して差動出力するレベル変換回路と、

前記レベル変換回路の差動出力が入力される差動増幅器と、

前記差動増幅器の出力に入力が接続される出力段と、

を備えて構成され、

前記レベル変換回路と前記差動増幅器との組合せが、前記差動入力信号のレベル差の検出と、該レベル差に応じた前記出力段に対する駆動能力の制御とを共通に行い、

前記レベル変換回路は、

前記差動入力信号の一方を入力とし、前記入力に所定の電圧を加えた第1の電位と前記第1の電位より高電位の第2の電位を出力する第1の出力対と、

前記差動入力信号の他方を入力とし、前記所定の電圧を加えた第3の電位と前記第3の電位より高電位の第4の電位を出力する第2の出力対とを有し、

前記差動増幅器は、

前記第2の電位及び前記第4の電位の出力を入力とし、それぞれの一端が第1の接続部で互いに接続される第1導電型トランジスタの差動対と、

前記第1の電位及び前記第3の電位の出力を入力とし、それぞれの一端が第2の接続部で互いに接続される第2導電型トランジスタの差動対と、

前記第1導電型トランジスタの差動対それぞれの他端が接続される第1の電流電圧変換回路と、

前記第2導電型トランジスタの差動対それぞれの他端が接続される第2の電流電圧変換回路と、

前記第1導電型トランジスタの差動対及び前記第2導電型トランジスタの差動対に流れる電流を低減する駆動電流制御回路と、を有し、

前記第1の電流電圧変換回路は第1の電源に接続され、

前記第2の電流電圧変換回路は前記第1の電源より低電位の第2の電源に接続され、

前記第1の接続部と前記第2の接続部とが、前記駆動電流制御回路を介して前記第1の電源と前記第2の電源に対して直列に接続されていることを特徴とする演算増幅器。 - 請求項1において、

前記第1導電型トランジスタの差動対は、前記第2の電位及び前記第4の電位の出力がゲートに入力され、ソース同士が前記第1の接続部で接続されるN型MOSトランジスタの差動対であり、

前記第2導電型トランジスタの差動対は、前記第1の電位及び前記第3の電位の出力がゲートに入力され、ソース同士が前記第2の接続部で接続されるP型MOSトランジスタの差動対であり、

前記N型MOSトランジスタの差動対それぞれのドレインが前記第1の電流電圧変換回路に接続され、

前記P型MOSトランジスタの差動対それぞれのドレインが前記第2の電流電圧変換回路に接続され、

前記駆動電流制御回路により、前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対のゲート−ソース間電圧が減少することを特徴とする演算増幅器。 - 請求項1において、

前記駆動電流制御回路は抵抗素子を含んで構成されていることを特徴とする演算増幅器。 - 請求項1において、

前記第1導電型トランジスタの差動対それぞれの一端に、前記第1の接続部に対して第1の耐圧保護素子が直列に接続され、

前記第2導電型トランジスタの差動対それぞれの一端に、前記第2の接続部に対して第2の耐圧保護素子が直列に接続されていることを特徴とする演算増幅器。 - 請求項1において、

前記差動入力信号が無い定常状態にて前記第1の電流電圧変換回路の出力電圧を第1の所定電圧以下に抑えるための第1の抵抗素子が、前記第1の電流電圧変換回路の出力と前記第1の電源間に接続され、

前記差動入力信号が無い定常状態にて前記第2の電流電圧変換回路の出力電圧を第2の所定電圧以下に抑えるための第2の抵抗素子が、前記第2の電流電圧変換回路の出力と前記第2の電源間に接続され、

前記第1の所定電圧は、前記出力段を構成する第1のトランジスタに電流が流れない状態になるための閾値電圧であり、

前記第2の所定電圧は、前記出力段を構成する第2のトランジスタに電流が流れない状態になるための閾値電圧であることを特徴とする演算増幅器。 - 請求項1において、

前記レベル変換回路は、

前記第1の電源に接続される電流源とドレインが前記第2の電源に接続されるMOSトランジスタとの間に、ドレインとゲートを接続したP型MOSトランジスタ及びドレインとゲートを接続したN型MOSトランジスタとを含んで構成され、

前記出力段は、

前記第1の電流電圧変換回路の出力を入力とするソース接地P型MOSトランジスタと、前記第2の電流電圧変換回路の出力を入力とするソース接地N型MOSトランジスタを備えることを特徴とする演算増幅器。 - 請求項1において、

前記第1の電流電圧変換回路は、前記第1導電型トランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記第1導電型トランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記第1導電型トランジスタの差動対の他方のドレインが出力となっている第1の能動負荷トランジスタ対を含んで構成され、

前記第2の電流電圧変換回路は、前記第2導電型トランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記第2導電型トランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記第2導電型トランジスタの差動対の他方のドレインが出力となっている第2の能動負荷トランジスタ対を含んで構成されることを特徴とする演算増幅器。 - 請求項4において、

前記第1および第2の耐圧保護素子はダイオードを含んで構成されていることを特徴とする演算増幅器。 - 請求項4において、

前記第1および第2の耐圧保護素子はMOSトランジスタを含んで構成されていることを特徴とする演算増幅器。 - 入力信号の電位を変換して第1の電位と前記第1の電位より高電位の第2の電位を出力する第1のレベル変換回路と、

前記入力信号の電位を変換して第3の電位と前記第3の電位より高電位の第4の電位を出力する第2のレベル変換回路と、

前記第2の電位及び前記第4の電位の出力がゲートに入力され、ソース同士が前記第1の接続部で接続されるN型MOSトランジスタの差動対と、

前記第1の電位及び前記第3の電位の出力がゲートに入力され、ソース同士が前記第2の接続部で接続されるP型MOSトランジスタの差動対と、

前記N型MOSトランジスタの差動対それぞれのドレインが接続される第1の電流電圧変換回路と、

前記P型MOSトランジスタの差動対それぞれのドレインが接続される第2の電流電圧変換回路と、

前記第1及び第2の電流電圧変換回路の出力と電気的に接続され、前記第1及び第2の電流電圧変換回路により制御される出力段と、

前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対に流れる電流を低減する駆動電流制御回路と、を有し、

前記第1の電流電圧変換回路は第1の電源に接続され、

前記第2の電流電圧変換回路は前記第1の電源より低電位の第2の電源に接続され、

前記第1の接続部と前記第2の接続部とが、前記駆動電流制御回路を介して前記第1の電源と前記第2の電源に対して直列に接続されていることを特徴とする演算増幅器。 - 請求項10において、

前記駆動電流制御回路により、前記N型MOSトランジスタの差動対及び前記P型MOSトランジスタの差動対に流れる電流によって電位降下が発生して、前記ゲート−ソース間の電圧が減少することを特徴とする演算増幅器。 - 請求項10において、

前記駆動電流制御回路は抵抗素子を含んで構成されていることを特徴とする演算増幅器。 - 請求項10において、

前記N型MOSトランジスタの差動対それぞれのソースに、前記第1の接続部に対して第1の耐圧保護素子が直列に接続され、

前記P型MOSトランジスタの差動対それぞれのソースに、前記第2の接続部に対して第2の耐圧保護素子が直列に接続されていることを特徴とする演算増幅器。 - 請求項10において、

前記入力信号差が無い定常状態にて前記第1の電流電圧変換回路の出力電圧を第1の所定電圧以下に抑えるための第1の抵抗素子が、前記第1の電流電圧変換回路の出力と前記第1の電源間に接続され、

前記入力信号差が無い定常状態にて前記第2の電流電圧変換回路の出力電圧を第2の所定電圧以下に抑えるための第2の抵抗素子が、前記第2の電流電圧変換回路の出力と前記第2の電源間に接続され、

前記第1の所定電圧は、前記出力段を構成する第1のトランジスタに電流が流れない状態になるための閾値電圧であり、

前記第2の所定電圧は、前記出力段を構成する第2のトランジスタに電流が流れない状態になるための閾値電圧であることを特徴とする演算増幅器。 - 請求項10において、

前記第1及び第2のレベル変換回路それぞれは、

前記第1の電源に接続される電流源とドレインが前記第2の電源に接続されるMOSトランジスタとの間に、ドレインとゲートを接続したP型MOSトランジスタ及びドレインとゲートを接続したN型MOSトランジスタとを含んで構成され、

前記出力段は、

前記第1の電流電圧変換回路の出力を入力とするソース接地P型MOSトランジスタと、前記第2の電流電圧変換回路の出力を入力とするソース接地N型MOSトランジスタを備えることを特徴とする演算増幅器。 - 請求項10において、

前記第1の電流電圧変換回路は、前記N型MOSトランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記N型MOSトランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記N型MOSトランジスタの差動対の他方のドレインが出力となっている第1の能動負荷トランジスタ対を含んで構成され、

前記第2の電流電圧変換回路は、前記P型MOSトランジスタの差動対それぞれのドレインにそれぞれのドレインが接続され、かつ、前記P型MOSトランジスタの差動対の一方のドレインに共通のゲートが接続され、かつ、前記P型MOSトランジスタの差動対の他方のドレインが出力となっている第2の能動負荷トランジスタ対を含んで構成されることを特徴とする演算増幅器。 - 請求項13において、

前記第1および第2の耐圧保護素子はダイオードを含んで構成されていることを特徴とする演算増幅器。 - 請求項13において、

前記第1および第2の耐圧保護素子はMOSトランジスタを含んで構成されていることを特徴とする演算増幅器。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008009991A JP5094441B2 (ja) | 2008-01-21 | 2008-01-21 | 演算増幅器 |

| US12/354,309 US7982537B2 (en) | 2008-01-21 | 2009-01-15 | Operational amplifier |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008009991A JP5094441B2 (ja) | 2008-01-21 | 2008-01-21 | 演算増幅器 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2009171479A JP2009171479A (ja) | 2009-07-30 |

| JP2009171479A5 JP2009171479A5 (ja) | 2011-01-20 |

| JP5094441B2 true JP5094441B2 (ja) | 2012-12-12 |

Family

ID=40875993

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008009991A Expired - Fee Related JP5094441B2 (ja) | 2008-01-21 | 2008-01-21 | 演算増幅器 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US7982537B2 (ja) |

| JP (1) | JP5094441B2 (ja) |

Families Citing this family (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US8692615B2 (en) * | 2012-03-20 | 2014-04-08 | Analog Devices, Inc. | Enhanced transconductance circuit |

| JP6124290B2 (ja) * | 2013-03-15 | 2017-05-10 | 国立大学法人東京工業大学 | 演算増幅器 |

| TWI561006B (en) * | 2013-05-24 | 2016-12-01 | Marvell Israel Misl Ltd | Systems and methods for data receipt from devices of disparate types |

| EP3113359B1 (en) * | 2013-11-28 | 2019-01-02 | ams AG | Amplifier arrangement |

| US9912229B2 (en) * | 2013-12-31 | 2018-03-06 | Texas Instruments Incorporated | Multiple output integrated power factor correction |

| WO2015190030A1 (ja) * | 2014-06-12 | 2015-12-17 | 富士電機株式会社 | 演算増幅器及びこれを使用したチャージアンプ |

| EP3176945B1 (en) * | 2015-12-04 | 2019-09-11 | ams AG | Switched capacitor integrator |

| JP2019012949A (ja) * | 2017-06-30 | 2019-01-24 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| US10659033B2 (en) * | 2017-11-03 | 2020-05-19 | Texas Instruments Incorporated | High voltage gate driver current source |

| US11469727B2 (en) * | 2020-02-27 | 2022-10-11 | Texas Instruments Incorporated | Pre-driver stage with adjustable biasing |

| JP2021175124A (ja) | 2020-04-28 | 2021-11-01 | キオクシア株式会社 | 半導体集積回路及び半導体記憶装置 |

| CN113067557B (zh) * | 2021-04-01 | 2023-11-24 | 西安邮电大学 | 一种带电平转换的高速全差分比较器电路 |

| WO2024188760A1 (en) * | 2023-03-15 | 2024-09-19 | Ams International Ag | Comparator, discriminator, photon counting system, device for medical diagnostics and electronic device |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4180780A (en) * | 1978-10-02 | 1979-12-25 | Altec Corporation | Input decoupling circuit for transistor differential amplifier |

| US5343164A (en) * | 1993-03-25 | 1994-08-30 | John Fluke Mfg. Co., Inc. | Operational amplifier circuit with slew rate enhancement |

| JP3338771B2 (ja) * | 1997-09-04 | 2002-10-28 | 山形日本電気株式会社 | 演算増幅器 |

| JP3376259B2 (ja) | 1997-11-04 | 2003-02-10 | 日本電気株式会社 | 差動増幅器 |

| JP3818793B2 (ja) * | 1999-04-07 | 2006-09-06 | シャープ株式会社 | サンプルホールド回路 |

| JP2000349570A (ja) | 1999-06-07 | 2000-12-15 | Toshiba Corp | バッファ回路 |

| US6262633B1 (en) * | 2000-04-27 | 2001-07-17 | Analog Devices, Inc. | High output current operational amplifier output stage |

| JP3847241B2 (ja) | 2002-10-01 | 2006-11-22 | Necエレクトロニクス株式会社 | 演算増幅器 |

| JP2005303497A (ja) * | 2004-04-08 | 2005-10-27 | Denso Corp | 差動増幅回路 |

| JP3976097B2 (ja) * | 2004-11-30 | 2007-09-12 | 日本テキサス・インスツルメンツ株式会社 | 増幅器 |

-

2008

- 2008-01-21 JP JP2008009991A patent/JP5094441B2/ja not_active Expired - Fee Related

-

2009

- 2009-01-15 US US12/354,309 patent/US7982537B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7982537B2 (en) | 2011-07-19 |

| JP2009171479A (ja) | 2009-07-30 |

| US20090184767A1 (en) | 2009-07-23 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5094441B2 (ja) | 演算増幅器 | |

| JP4616067B2 (ja) | 定電圧電源回路 | |

| TWI411904B (zh) | Voltage regulator | |

| JP4805699B2 (ja) | 半導体装置 | |

| US7301322B2 (en) | CMOS constant voltage generator | |

| JP4443301B2 (ja) | ボルテージ・レギュレータ | |

| JP5657853B2 (ja) | 定電流源回路 | |

| US7907003B2 (en) | Method for improving power-supply rejection | |

| JP4996203B2 (ja) | 電源電圧回路 | |

| JP2008015925A (ja) | 基準電圧発生回路 | |

| WO2010026674A1 (ja) | 基準電圧発生回路 | |

| JPH10509013A (ja) | ゲート−ソース電圧の和を一定に調整することによるCMOS給電線間入力段用のg▲下m▼−制御回路 | |

| US7683687B2 (en) | Hysteresis characteristic input circuit including resistors capable of suppressing penetration current | |

| JP2003298368A (ja) | 増幅回路 | |

| TWI769327B (zh) | 電壓調節器 | |

| JP4717692B2 (ja) | リミッタ回路 | |

| KR100560260B1 (ko) | 바이어스 전압 발생 회로 및 차동 증폭 회로 | |

| JP2010141589A (ja) | 差動増幅回路 | |

| JP2009094878A (ja) | 差動増幅回路 | |

| JP4555131B2 (ja) | 定電圧電源回路 | |

| JP5369749B2 (ja) | 定電圧回路 | |

| JP5403592B2 (ja) | 電流駆動回路 | |

| JP2007180796A (ja) | 差動増幅回路 | |

| JP5849585B2 (ja) | 過電流検出回路 | |

| JP2005333736A (ja) | 過電流防止回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101126 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20101126 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111129 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120104 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120301 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120821 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120918 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 5094441 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150928 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |