JP5069449B2 - 配線基板及びその製造方法 - Google Patents

配線基板及びその製造方法 Download PDFInfo

- Publication number

- JP5069449B2 JP5069449B2 JP2006308322A JP2006308322A JP5069449B2 JP 5069449 B2 JP5069449 B2 JP 5069449B2 JP 2006308322 A JP2006308322 A JP 2006308322A JP 2006308322 A JP2006308322 A JP 2006308322A JP 5069449 B2 JP5069449 B2 JP 5069449B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- wiring

- substrate

- pad

- resist

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/10—Bump connectors; Manufacturing methods related thereto

- H01L2224/15—Structure, shape, material or disposition of the bump connectors after the connecting process

- H01L2224/16—Structure, shape, material or disposition of the bump connectors after the connecting process of an individual bump connector

- H01L2224/161—Disposition

- H01L2224/16151—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/16221—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/16225—Disposition the bump connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/01—Means for bonding being attached to, or being formed on, the surface to be connected, e.g. chip-to-package, die-attach, "first-level" interconnects; Manufacturing methods related thereto

- H01L2224/26—Layer connectors, e.g. plate connectors, solder or adhesive layers; Manufacturing methods related thereto

- H01L2224/31—Structure, shape, material or disposition of the layer connectors after the connecting process

- H01L2224/32—Structure, shape, material or disposition of the layer connectors after the connecting process of an individual layer connector

- H01L2224/321—Disposition

- H01L2224/32151—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive

- H01L2224/32221—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked

- H01L2224/32225—Disposition the layer connector connecting between a semiconductor or solid-state body and an item not being a semiconductor or solid-state body, e.g. chip-to-substrate, chip-to-passive the body and the item being stacked the item being non-metallic, e.g. insulating substrate with or without metallisation

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/73—Means for bonding being of different types provided for in two or more of groups H01L2224/10, H01L2224/18, H01L2224/26, H01L2224/34, H01L2224/42, H01L2224/50, H01L2224/63, H01L2224/71

- H01L2224/732—Location after the connecting process

- H01L2224/73201—Location after the connecting process on the same surface

- H01L2224/73203—Bump and layer connectors

- H01L2224/73204—Bump and layer connectors the bump connector being embedded into the layer connector

Landscapes

- Structure Of Printed Boards (AREA)

- Manufacturing Of Printed Wiring (AREA)

Description

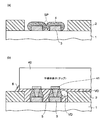

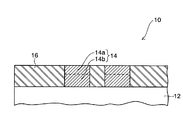

12…樹脂基板、

13…シード層(導体層)、

14…配線層、

14a…基板パッド(配線層の「基板パッド」部分)、

14b…下配線(配線層の「下配線」部分)、

16…ソルダレジスト層(絶縁層/保護膜)、

21,22,22a…レジスト層、

30…はんだ粉、

31…はんだバンプ、

32…アンダーフィル樹脂、

40…半導体素子(チップ)、

41…電極端子(チップパッド)、

SP…隣接する基板パッド(側面)上のはんだ粉同士がショートしている部分、

VD…ボイド(空洞部分)。

Claims (6)

- ベース基材としての基板上に形成されたフリップチップ接続用のパッド部分を含む配線層と、前記パッド部分のみを露出させて前記基板及び前記配線層を覆うように形成された絶縁層とを備え、

前記配線層は、配線部分を構成する第1のめっき配線の一部領域上にのみ、前記パッド部分を構成する、前記第1のめっき配線と結晶配向が異なる第2のめっき配線が積み重ねられた構造を有し、前記パッド部分の上面が前記絶縁層の表面と同一面上に位置するように形成されていることを特徴とする配線基板。 - 少なくとも最表層に導体層が形成された基板の一方の面に、形成すべきフリップチップ接続用のパッド部分を含む所要の配線層の形状に従ってパターニングされた開口部を備えた第1のレジスト層を形成する工程と、

前記第1のレジスト層の開口部から露出している前記導体層を給電層として電解めっきを施し、当該開口部内を部分的に埋め込むように第1の配線層を形成する工程と、

電解めっきの条件を変えて前記第1の配線層に電解めっきを施し、当該開口部内の残りの部分を埋め込むように前記第1の配線層と結晶配向が異なる第2の配線層を形成する工程と、

前記第2の配線層のパッド部分に対応する領域にパターンが残るように、前記第1のレジスト層及び前記第2の配線層の上に第2のレジスト層を形成する工程と、

前記第2のレジスト層をマスクにして、前記第2の配線層の露出している部分のみをエッチングすることで、前記第1の配線層を露出させる工程と、

前記第2のレジスト層及び第1のレジスト層を除去した後、前記基板及び前記第1、第2の配線層を覆って全面に絶縁層を形成する工程と、

前記絶縁層を研磨して前記パッド部分の上面を露出させると共に、基板表面全体を平坦化する工程とを含むことを特徴とする配線基板の製造方法。 - 前記電解めっきの条件を変えて前記第2の配線層を形成する工程に代えて、

前記第1の配線層上にバリヤメタル層を形成し、さらに該バリヤメタル層に電解めっきを施し、当該開口部内の残りの部分を埋め込むように第2の配線層を形成する工程を含むことを特徴とする請求項2に記載の配線基板の製造方法。 - 前記第2のレジスト層及び前記第1のレジスト層の除去後に前記基板から露出している前記導体層を除去した後に、前記基板及び前記第1、第2の配線層を覆って全面に絶縁層を形成することを特徴とする請求項2又は3に記載の配線基板の製造方法。

- 前記バリヤメタル層は、前記第2の配線層の露出している部分のみをエッチングする際のストッパ層として機能することを特徴とする請求項3に記載の配線基板の製造方法。

- 前記バリヤメタル層は、ニッケル層上に金層が積層された2層構造を有していることを特徴とする請求項3に記載の配線基板の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006308322A JP5069449B2 (ja) | 2006-11-14 | 2006-11-14 | 配線基板及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2006308322A JP5069449B2 (ja) | 2006-11-14 | 2006-11-14 | 配線基板及びその製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2008124339A JP2008124339A (ja) | 2008-05-29 |

| JP2008124339A5 JP2008124339A5 (ja) | 2009-11-05 |

| JP5069449B2 true JP5069449B2 (ja) | 2012-11-07 |

Family

ID=39508751

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006308322A Active JP5069449B2 (ja) | 2006-11-14 | 2006-11-14 | 配線基板及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5069449B2 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR20110038521A (ko) * | 2009-10-08 | 2011-04-14 | 엘지이노텍 주식회사 | 인쇄회로기판 및 그 제조방법 |

| US10388608B2 (en) * | 2015-08-28 | 2019-08-20 | Hitachi Chemical Company, Ltd. | Semiconductor device and method for manufacturing same |

| JP7048593B2 (ja) * | 2017-05-19 | 2022-04-05 | ベジ 佐々木 | 電子部品搭載用基板及びその製造方法 |

| TWI705747B (zh) * | 2019-08-30 | 2020-09-21 | 嘉聯益科技股份有限公司 | 多層軟性電路板及其製造方法 |

| TWI831123B (zh) * | 2022-01-28 | 2024-02-01 | 巨擘科技股份有限公司 | 多層基板表面處理層結構 |

| CN115190701B (zh) * | 2022-05-13 | 2023-06-02 | 广州广芯封装基板有限公司 | 一种埋入式线路封装基板及其加工方法 |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH03253091A (ja) * | 1990-03-02 | 1991-11-12 | Tokuyama Soda Co Ltd | プリント配線板の製造方法 |

| JPH11126974A (ja) * | 1997-10-24 | 1999-05-11 | Asahi Chem Res Lab Ltd | 多層配線板の製造方法 |

| JP2002299779A (ja) * | 2001-03-30 | 2002-10-11 | Hitachi Metals Ltd | 配線形成用帯材及びそれを用いたバンプ付き配線を有する配線板並びに配線形成用帯材を用いた転写配線板の製造方法 |

| JP2003008228A (ja) * | 2001-06-22 | 2003-01-10 | Ibiden Co Ltd | 多層プリント配線板およびその製造方法 |

| JP2004095972A (ja) * | 2002-09-03 | 2004-03-25 | Sumitomo Metal Electronics Devices Inc | プラスチックパッケージの製造方法 |

| JP2005166910A (ja) * | 2003-12-02 | 2005-06-23 | Fujikura Ltd | プリント配線板およびその製造方法 |

-

2006

- 2006-11-14 JP JP2006308322A patent/JP5069449B2/ja active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2008124339A (ja) | 2008-05-29 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| TWI471956B (zh) | 半導體封裝與製造方法 | |

| JP5113114B2 (ja) | 配線基板の製造方法及び配線基板 | |

| KR101551898B1 (ko) | 배선 기판, 반도체 장치 및 이들의 제조 방법 | |

| US9681546B2 (en) | Wiring substrate and semiconductor device | |

| JP5886617B2 (ja) | 配線基板及びその製造方法、半導体パッケージ | |

| US8304663B2 (en) | Wiring board and manufacturing method thereof | |

| JP6661232B2 (ja) | 配線基板、半導体装置、配線基板の製造方法及び半導体装置の製造方法 | |

| WO2011089936A1 (ja) | 機能素子内蔵基板及び配線基板 | |

| JP5091469B2 (ja) | 配線基板およびその製造方法 | |

| JPWO2004103039A1 (ja) | 両面配線基板および両面配線基板の製造方法 | |

| JPWO2007126090A1 (ja) | 回路基板、電子デバイス装置及び回路基板の製造方法 | |

| US9997474B2 (en) | Wiring board and semiconductor device | |

| US9935053B2 (en) | Electronic component integrated substrate | |

| JP2017073520A (ja) | 配線基板、半導体装置及び配線基板の製造方法 | |

| JP5069449B2 (ja) | 配線基板及びその製造方法 | |

| WO2004014114A1 (ja) | 素子内蔵基板の製造方法および素子内蔵基板、ならびに、プリント配線板の製造方法およびプリント配線板 | |

| JP7253946B2 (ja) | 配線基板及びその製造方法、半導体パッケージ | |

| JP2015159197A (ja) | 配線基板及びその製造方法 | |

| JP4170266B2 (ja) | 配線基板の製造方法 | |

| JP4835629B2 (ja) | 半導体装置の製造方法 | |

| TWI771573B (zh) | 配線基板、半導體裝置及配線基板的製造方法 | |

| JP5599860B2 (ja) | 半導体パッケージ基板の製造方法 | |

| JP2007158069A (ja) | 半導体パッケージの外部接続構造及びその製造方法 | |

| JP2004200412A (ja) | 半田バンプ付き配線基板およびその製造方法 | |

| JP2004356219A (ja) | 配線基板及びその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090916 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20090916 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20110719 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110927 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111128 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120605 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120712 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120814 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120817 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150824 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5069449 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |