JP5052007B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP5052007B2 JP5052007B2 JP2005379661A JP2005379661A JP5052007B2 JP 5052007 B2 JP5052007 B2 JP 5052007B2 JP 2005379661 A JP2005379661 A JP 2005379661A JP 2005379661 A JP2005379661 A JP 2005379661A JP 5052007 B2 JP5052007 B2 JP 5052007B2

- Authority

- JP

- Japan

- Prior art keywords

- capacitor

- electrode pad

- semiconductor device

- substrate

- region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D84/00—Integrated devices formed in or on semiconductor substrates that comprise only semiconducting layers, e.g. on Si wafers or on GaAs-on-Si wafers

- H10D84/01—Manufacture or treatment

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10F—INORGANIC SEMICONDUCTOR DEVICES SENSITIVE TO INFRARED RADIATION, LIGHT, ELECTROMAGNETIC RADIATION OF SHORTER WAVELENGTH OR CORPUSCULAR RADIATION

- H10F30/00—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors

- H10F30/20—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors

- H10F30/21—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation

- H10F30/22—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation the devices having only one potential barrier, e.g. photodiodes

- H10F30/223—Individual radiation-sensitive semiconductor devices in which radiation controls the flow of current through the devices, e.g. photodetectors the devices having potential barriers, e.g. phototransistors the devices being sensitive to infrared, visible or ultraviolet radiation the devices having only one potential barrier, e.g. photodiodes the potential barrier being a PIN barrier

Landscapes

- Semiconductor Integrated Circuits (AREA)

- Solid State Image Pick-Up Elements (AREA)

- Light Receiving Elements (AREA)

Description

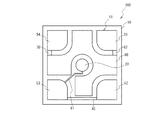

11,210 配置領域

20 フォトダイオード

30,40,202 抵抗素子

51〜54,203〜205 電極パッド

60,206 キャパシタ

100,100a,100b,100c 光半導体装置

200 電子部品

Claims (5)

- 電極パッドと、

キャパシタと、

前記電極パッドおよび前記キャパシタが所定の領域に配置された基板とを備え、

前記キャパシタおよび前記電極パッドは、前記キャパシタおよび前記電極パッドの各々の少なくとも2辺が所定の間隔で隣接する、平面上の配置関係を有し、

前記キャパシタは、前記キャパシタの当該2辺を連結して前記電極パッドと対向する接続辺をさらに備え、

前記接続辺と前記2辺の各々とがなす前記キャパシタの外側の角度は、90度よりも大きく、

前記キャパシタは、第1のキャパシタ上に第2のキャパシタが積層された構造を有し、

前記第1のキャパシタおよび前記第2のキャパシタは、電極によって絶縁体が挟持された構成を有し、

前記2辺および前記接続辺は、前記第2のキャパシタの辺であり、

前記第1のキャパシタは、前記第2のキャパシタよりも前記電極パッド側に延在していることを特徴とする半導体装置。 - 前記第1のキャパシタおよび前記第2のキャパシタは、MIS構造またはMIM構造からなることを特徴とする請求項1記載の半導体装置。

- 前記基板上にさらに受光素子を備え、

前記基板上の中央部に前記受光素子の受光面が配置され、前記基板上の少なくとも4隅の1つに前記電極パッドとが配置されていることを特徴とする請求項1または2記載の半導体装置。 - 前記受光素子は、アバランシェフォトダイオードまたはPINフォトダイオードであることを特徴とする請求項3記載の半導体装置。

- 前記基板上にさらに抵抗素子を備えることを特徴とする請求項1〜4のいずれか一項に記載の半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005379661A JP5052007B2 (ja) | 2005-12-28 | 2005-12-28 | 半導体装置 |

| US11/642,896 US7332758B2 (en) | 2005-12-28 | 2006-12-21 | Semiconductor device |

| CN200610171482A CN100587948C (zh) | 2005-12-28 | 2006-12-28 | 半导体器件 |

| US12/003,111 US7692227B2 (en) | 2005-12-28 | 2007-12-20 | Semiconductor device having an electrode pad |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005379661A JP5052007B2 (ja) | 2005-12-28 | 2005-12-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007180425A JP2007180425A (ja) | 2007-07-12 |

| JP2007180425A5 JP2007180425A5 (ja) | 2009-02-19 |

| JP5052007B2 true JP5052007B2 (ja) | 2012-10-17 |

Family

ID=38192635

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005379661A Expired - Fee Related JP5052007B2 (ja) | 2005-12-28 | 2005-12-28 | 半導体装置 |

Country Status (3)

| Country | Link |

|---|---|

| US (2) | US7332758B2 (ja) |

| JP (1) | JP5052007B2 (ja) |

| CN (1) | CN100587948C (ja) |

Families Citing this family (15)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5197930B2 (ja) * | 2006-06-30 | 2013-05-15 | 住友電工デバイス・イノベーション株式会社 | 半導体受光素子の製造方法 |

| US7919860B2 (en) * | 2007-08-27 | 2011-04-05 | Texas Instruments Incorporated | Semiconductor device having wafer level chip scale packaging substrate decoupling |

| JP5401817B2 (ja) * | 2008-03-25 | 2014-01-29 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法及び半導体装置 |

| JP5474662B2 (ja) * | 2010-05-27 | 2014-04-16 | 住友電工デバイス・イノベーション株式会社 | 半導体受光素子 |

| JP5761533B2 (ja) | 2010-08-27 | 2015-08-12 | 国立大学法人 奈良先端科学技術大学院大学 | SiC半導体素子 |

| JP5734784B2 (ja) | 2011-08-05 | 2015-06-17 | 株式会社東芝 | 光結合装置 |

| JP2013115371A (ja) | 2011-11-30 | 2013-06-10 | Sumitomo Electric Device Innovations Inc | 容量素子 |

| JP5920128B2 (ja) | 2012-09-07 | 2016-05-18 | 住友電気工業株式会社 | 光導波路型受光素子の製造方法および光導波路型受光素子 |

| KR102037866B1 (ko) * | 2013-02-05 | 2019-10-29 | 삼성전자주식회사 | 전자장치 |

| JP6094268B2 (ja) | 2013-03-04 | 2017-03-15 | 住友電気工業株式会社 | 半導体集積受光デバイス |

| JP6330549B2 (ja) | 2014-07-25 | 2018-05-30 | 住友電気工業株式会社 | 光半導体素子およびその製造方法 |

| USD760230S1 (en) * | 2014-09-16 | 2016-06-28 | Daishinku Corporation | Piezoelectric vibration device |

| CN106981542A (zh) * | 2017-03-29 | 2017-07-25 | 武汉京邦科技有限公司 | 一种半导体光电倍增器件的制造方法 |

| KR102668436B1 (ko) * | 2021-11-08 | 2024-05-24 | (주)위드멤스 | 트렌치 커패시터 및 이의 제조 방법 |

| CN114362119B (zh) * | 2022-01-04 | 2024-05-14 | 武汉电信器件有限公司 | 一种apd保护电路结构 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5698859A (en) * | 1980-01-07 | 1981-08-08 | Mitsubishi Electric Corp | Solid-state electronic device |

| EP0093818A1 (de) * | 1982-05-07 | 1983-11-16 | Deutsche ITT Industries GmbH | Monolithisch integrierte Schaltung mit integrierten Kondensatoren |

| JPS63186448A (ja) * | 1987-01-28 | 1988-08-02 | Mitsubishi Electric Corp | 半導体装置 |

| JPH0758294A (ja) * | 1993-08-19 | 1995-03-03 | Kawasaki Steel Corp | 半導体集積回路チップ |

| JP4136009B2 (ja) * | 1995-02-02 | 2008-08-20 | 住友電気工業株式会社 | pin型受光素子、およびpin型受光素子の製造方法 |

| JPH0936305A (ja) * | 1995-07-20 | 1997-02-07 | Rohm Co Ltd | ダイオードとコンデンサとを備えたチップ型複合素子の構造 |

| US6902981B2 (en) * | 2002-10-10 | 2005-06-07 | Chartered Semiconductor Manufacturing Ltd | Structure and process for a capacitor and other devices |

| JP2005129689A (ja) | 2003-10-23 | 2005-05-19 | Sumitomo Electric Ind Ltd | 半導体受光素子及び光受信モジュール |

| JP4502278B2 (ja) * | 2004-02-27 | 2010-07-14 | 国立大学法人東北大学 | 固体撮像装置、ラインセンサ、光センサおよび固体撮像装置の動作方法 |

| KR100672993B1 (ko) * | 2005-01-19 | 2007-01-24 | 삼성전자주식회사 | 자가 승압 기능을 갖는 이미지 센서, 자가 승압 방법 및상기 이미지 센서 형성 방법 |

| JP4911445B2 (ja) * | 2005-06-29 | 2012-04-04 | 富士フイルム株式会社 | 有機と無機のハイブリッド光電変換素子 |

-

2005

- 2005-12-28 JP JP2005379661A patent/JP5052007B2/ja not_active Expired - Fee Related

-

2006

- 2006-12-21 US US11/642,896 patent/US7332758B2/en not_active Expired - Fee Related

- 2006-12-28 CN CN200610171482A patent/CN100587948C/zh not_active Expired - Fee Related

-

2007

- 2007-12-20 US US12/003,111 patent/US7692227B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US7692227B2 (en) | 2010-04-06 |

| JP2007180425A (ja) | 2007-07-12 |

| CN100587948C (zh) | 2010-02-03 |

| US20070145527A1 (en) | 2007-06-28 |

| US20080135961A1 (en) | 2008-06-12 |

| CN1992251A (zh) | 2007-07-04 |

| US7332758B2 (en) | 2008-02-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7692227B2 (en) | Semiconductor device having an electrode pad | |

| US9847299B2 (en) | Semiconductor package and mounting structure thereof | |

| JP5483544B2 (ja) | 半導体受光装置 | |

| US10895681B2 (en) | Semiconductor module, manufacturing method thereof, and communication method using the same | |

| US5753537A (en) | Method of manufacturing a semiconductor device for surface mounting | |

| JP4034153B2 (ja) | 半導体受光装置 | |

| KR100809702B1 (ko) | 반도체 패키지 | |

| JP2011253987A (ja) | 半導体受光素子及び光モジュール | |

| EP2747528B1 (fr) | Dispositif d'interconnexion pour circuits électroniques, notamment des circuits électroniques hyperfrequence | |

| USRE47171E1 (en) | Integrated circuit device having pads structure formed thereon and method for forming the same | |

| US20070268674A1 (en) | Electronic Module with a Semiconductor Chip and a Component Housing and Methods for Producing the Same | |

| JP4124618B2 (ja) | 半導体装置 | |

| JP2005129689A (ja) | 半導体受光素子及び光受信モジュール | |

| JP5982711B2 (ja) | 半導体受光装置 | |

| CN109844963B (zh) | 背面入射型受光元件及光模块 | |

| JP2015130492A (ja) | 半導体モジュール | |

| US8368131B2 (en) | Light detecting apparatus | |

| JP5474662B2 (ja) | 半導体受光素子 | |

| JP2005277057A (ja) | 半導体受光素子及び半導体受光装置 | |

| US9013020B2 (en) | Photodiode carrier and photo sensor using the same | |

| JP2013030689A (ja) | 半導体受光装置 | |

| JP2005327987A (ja) | 半導体装置 | |

| JP5188039B2 (ja) | 半導体装置及び半導体構成体並びにそれらの製造方法 | |

| JPH04251987A (ja) | 光・電子集積素子及びその製造方法 | |

| JP2005209994A (ja) | 受光素子およびその製造方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20081219 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081219 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081219 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120105 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120312 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20120403 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120702 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20120709 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120724 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120724 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150803 Year of fee payment: 3 |

|

| LAPS | Cancellation because of no payment of annual fees |