JP5010031B2 - ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 - Google Patents

ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 Download PDFInfo

- Publication number

- JP5010031B2 JP5010031B2 JP2010524087A JP2010524087A JP5010031B2 JP 5010031 B2 JP5010031 B2 JP 5010031B2 JP 2010524087 A JP2010524087 A JP 2010524087A JP 2010524087 A JP2010524087 A JP 2010524087A JP 5010031 B2 JP5010031 B2 JP 5010031B2

- Authority

- JP

- Japan

- Prior art keywords

- page

- data

- memory

- programming

- read

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 230000015654 memory Effects 0.000 title claims abstract description 238

- 238000000034 method Methods 0.000 title claims description 92

- 230000006870 function Effects 0.000 claims description 22

- 230000001960 triggered effect Effects 0.000 claims description 6

- 230000004044 response Effects 0.000 claims 1

- 238000003860 storage Methods 0.000 abstract description 45

- 238000007667 floating Methods 0.000 abstract description 43

- 230000008878 coupling Effects 0.000 abstract description 15

- 238000010168 coupling process Methods 0.000 abstract description 15

- 238000005859 coupling reaction Methods 0.000 abstract description 15

- 230000007774 longterm Effects 0.000 abstract description 2

- 230000008569 process Effects 0.000 description 33

- 238000006243 chemical reaction Methods 0.000 description 14

- 238000012546 transfer Methods 0.000 description 11

- 238000012795 verification Methods 0.000 description 11

- 238000001514 detection method Methods 0.000 description 10

- 230000000694 effects Effects 0.000 description 8

- 230000005684 electric field Effects 0.000 description 8

- 238000012545 processing Methods 0.000 description 7

- 230000008859 change Effects 0.000 description 6

- 239000000758 substrate Substances 0.000 description 6

- 238000004891 communication Methods 0.000 description 5

- 238000013461 design Methods 0.000 description 5

- 101001072191 Homo sapiens Protein disulfide-isomerase A2 Proteins 0.000 description 4

- 101001098828 Homo sapiens Protein disulfide-isomerase A5 Proteins 0.000 description 4

- 102100036351 Protein disulfide-isomerase A2 Human genes 0.000 description 4

- 238000010586 diagram Methods 0.000 description 4

- 230000000630 rising effect Effects 0.000 description 4

- 230000009471 action Effects 0.000 description 3

- 238000013459 approach Methods 0.000 description 3

- 230000008901 benefit Effects 0.000 description 3

- 230000000295 complement effect Effects 0.000 description 3

- 238000013500 data storage Methods 0.000 description 3

- 238000009792 diffusion process Methods 0.000 description 3

- 238000002347 injection Methods 0.000 description 3

- 239000007924 injection Substances 0.000 description 3

- 230000007246 mechanism Effects 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012986 modification Methods 0.000 description 3

- 238000001745 non-dispersive infrared spectroscopy Methods 0.000 description 3

- 230000002093 peripheral effect Effects 0.000 description 3

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 2

- 238000003491 array Methods 0.000 description 2

- 230000006399 behavior Effects 0.000 description 2

- 230000007423 decrease Effects 0.000 description 2

- 238000009826 distribution Methods 0.000 description 2

- 230000005669 field effect Effects 0.000 description 2

- 239000002784 hot electron Substances 0.000 description 2

- 238000004519 manufacturing process Methods 0.000 description 2

- 230000036961 partial effect Effects 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- 229920005591 polysilicon Polymers 0.000 description 2

- 230000001603 reducing effect Effects 0.000 description 2

- 230000002829 reductive effect Effects 0.000 description 2

- 230000003252 repetitive effect Effects 0.000 description 2

- 239000004065 semiconductor Substances 0.000 description 2

- 239000007787 solid Substances 0.000 description 2

- 108091026890 Coding region Proteins 0.000 description 1

- 230000005689 Fowler Nordheim tunneling Effects 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000003044 adaptive effect Effects 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 230000001010 compromised effect Effects 0.000 description 1

- 238000012937 correction Methods 0.000 description 1

- 230000001808 coupling effect Effects 0.000 description 1

- 230000001351 cycling effect Effects 0.000 description 1

- 230000002950 deficient Effects 0.000 description 1

- 230000001419 dependent effect Effects 0.000 description 1

- 238000007599 discharging Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 230000005283 ground state Effects 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 239000011159 matrix material Substances 0.000 description 1

- 239000002184 metal Substances 0.000 description 1

- 230000005012 migration Effects 0.000 description 1

- 238000013508 migration Methods 0.000 description 1

- 230000000116 mitigating effect Effects 0.000 description 1

- 230000008707 rearrangement Effects 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 239000013643 reference control Substances 0.000 description 1

- 230000002441 reversible effect Effects 0.000 description 1

- 235000012239 silicon dioxide Nutrition 0.000 description 1

- 239000000377 silicon dioxide Substances 0.000 description 1

- 239000000243 solution Substances 0.000 description 1

- 238000000638 solvent extraction Methods 0.000 description 1

- 230000001360 synchronised effect Effects 0.000 description 1

- 230000007704 transition Effects 0.000 description 1

- 238000010200 validation analysis Methods 0.000 description 1

- 239000002699 waste material Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5621—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using charge storage in a floating gate

- G11C11/5628—Programming or writing circuits; Data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/10—Programming or data input circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/34—Determination of programming status, e.g. threshold voltage, overprogramming or underprogramming, retention

- G11C16/3418—Disturbance prevention or evaluation; Refreshing of disturbed memory data

- G11C16/3427—Circuits or methods to prevent or reduce disturbance of the state of a memory cell when neighbouring cells are read or written

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1006—Data managing, e.g. manipulating data before writing or reading out, data bus switches or control circuits therefor

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C2211/00—Indexing scheme relating to digital stores characterized by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C2211/56—Indexing scheme relating to G11C11/56 and sub-groups for features not covered by these groups

- G11C2211/564—Miscellaneous aspects

- G11C2211/5647—Multilevel memory with bit inversion arrangement

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Read Only Memory (AREA)

- Techniques For Improving Reliability Of Storages (AREA)

Description

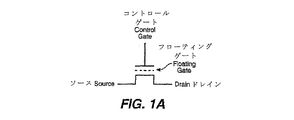

メモリ装置は通常、1つ以上のメモリチップをカード上に実装する。それぞれのメモリチップは、デコーダや消去回路、書き込み回路、および読み出し回路等の周辺回路によって支援されるメモリセルアレイを備える。より精緻なメモリ装置にはコントローラも搭載され、これは知的で高度なメモリ操作とインターフェイスを実行する。今日、商業的に成功を収めた不揮発性ソリッドステートメモリ装置が数多く使われている。これらのメモリ装置には様々なタイプのメモリセルが採用されてよく、各種のメモリセルは1つ以上の電荷蓄積素子を具備する。

メモリ装置は通常、行列に配置され、ワード線とビット線によりアドレス可能である二次元メモリセルアレイを備える。アレイはNORタイプかNANDタイプのアーキテクチャに従って形成できる。

図2は、NORメモリセルアレイの一例を示す。これまでNORタイプのアーキテクチャを持つメモリ装置は、図1Bまたは図1Cに描かれたタイプのセルを用いて実装されてきた。メモリセル行は、それぞれのソースとドレインによりデイジーチェーン接続される。この設計は仮想接地設計と呼ばれることがある。各々のメモリセル10はソース14と、ドレイン16と、コントロールゲート30と、選択ゲート40とを具備する。行内のセルの選択ゲートはワード線42へ接続する。列内のセルのソースおよびドレインは選択されたビット線34および36へ接続する。メモリセルのコントロールゲートと選択ゲートを別々に制御する一部の実施形態では、ステアリング線36によって列内のセルのコントロールゲートが接続される。

図3は、図1Dに見られるメモリセル等からなるNANDアレイの一例を示す。ビット線は各NANDセル列に沿って各NANDセルのドレイン端子56へ結合する。ソース線はNANDセル行に沿って、全ソース端子54へ接続し得る。さらに、行沿いのNANDセルのコントロールゲートは一連の対応するワード線へ接続する。接続されたワード線を通じてコントロールゲートにしかるべき電圧をかけて1対の選択トランジスタ(図1D参照)をオンにすることにより、行全体のNANDセルをアドレスできる。NANDセルのチェーンの中のひとつのメモリトランジスタを読み出すときには、チェーンの中の残りのメモリトランジスタがそれぞれの関連するワード線を通じてハードオンになるため、チェーンの中を流れる電流は、基本的には読み出しの対象となるセルに蓄積される電荷レベルに左右される。米国特許第5,570,315号(特許文献14)、第5,774,397号(特許文献21)、および第6,046,935号(特許文献16)には、NANDアーキテクチャアレイの例とメモリシステムの一部としてのこの動作が記載されている。

電荷蓄積メモリ装置のプログラミングではひたすら電荷蓄積素子に電荷が加えられる。このためプログラミング操作にあたっては、電荷蓄積素子に既に存在する電荷を事前に除去(または、消去)しなければならない。1つ以上のメモリセルブロックを消去するため、消去回路(図示せず)を設ける。セルアレイ全体あるいはアレイのかなりのセル群を、電気的に一斉に(すなわち、瞬時に)消去するEEPROM等の不揮発性メモリは「フラッシュ」EEPROMと呼ばれる。消去の後にはセル群を再プログラムできる。一斉に消去できるセル群は1つ以上のアドレス可能な消去単位からなってよい。消去単位またはブロックは通常1ページ以上のデータを蓄積し、このページがプログラミングと読み出しの単位となるが、1回の操作で2ページ以上をプログラムしたり読み出したりする場合もある。各ページには通常1セクタ以上のデータが蓄積され、このセクタのサイズはホストシステムによって決まる。例えば、磁気ディスクドライブの場合は512バイトのユーザデータからなるセクタが標準となり、さらにここにユーザデータおよび/またはこれを蓄積するブロックに関する何バイトかのオーバーヘッド情報が加わる。

通常の2状態EEPROMセルでは、1つ以上の電流区切りレベルを設定して伝導ウィンドウを2つの領域に分割する。予め決められた一定の電圧を印加することによってセルを読み出すときには、そのソース/ドレイン電流を区切りレベル(または基準電流IREF)と比較することによって記憶状態を決定する。読み出される電流が区切りレベルの電流より高ければ、セルはひとつの論理状態(例えば「0」状態)にあると判断される。その一方で、電流が区切りレベルの電流に満たなければ、セルはもうひとつの論理状態(例えば、「1」状態)にあると判断される。かかる2状態セルは1ビットのデジタル情報を蓄積する。基準電流源は外部からプログラムでき、通常はメモリシステムの一部として用意され、区切りレベル電流を生成する。

読み出しとプログラミングの性能を上げるには、アレイの中にある複数の電荷蓄積素子またはメモリトランジスタを並行して読み出すかまたはプログラムする。つまり、記憶素子からなる論理「ページ」の読み出しまたはプログラミングは一斉に行われる。既存のメモリアーキテクチャでは通常、1行の中にいくつかの交互ページがある。読み出しまたはプログラミングは1ページの全記憶素子で一斉に行われる。列デコーダは交互ページの各々を対応する数の読み出し/書き込みモジュールへ選択的に接続する。例えば、一実施例において、532バイト(512バイトにオーバーヘッドの20バイトを加えたもの)のページサイズでメモリアレイを設計する。各列にドレインビット線があって各行につき2つの交互ページがあるならば、列は8,512列になり、各ページに4,256列が対応する。全ての偶数ビット線か奇数ビット線を並行して読み書きするには、4,256個のセンスモジュールを接続することになる。こうして、記憶素子のページには1ページ4,256ビット(すなわち、532バイト)のデータを並行して読み出すかまたはプログラムする。読み出し/書き込み回路170を形成する読み出し/書き込みモジュールは、様々なアーキテクチャに組むことができる。

好適な実施形態において、ページ上でデータをスクランブルするシンプルな方法により、データはページごとに独立しているかまたは異なる開始アドレスに書き込まれる。メモリセルの各ページには、ページごとに異なる開始位置に対応するデータページが書き込まれる。ページの終わりまでデータで埋め尽くされると、ページの最初のアドレスからラップアラウンドし、開始位置の手前まで書き込みを継続する。

別の好適な実施形態では、擬似ランダムジェネレータによって一連の開始物理列アドレスが各ページにつき1つずつ提供される。

それには、ページ内の個々のビットをランダム化する。好ましくは、それぞれ特定の極性を指定する一連の擬似ランダムビットを使ってページ内のビットを符号化する。一実施形態において、ページ内の各データビットにつき極性ビットがある。別の実施形態では、ページ内の各データバイトにつき極性ビットがある。この実施形態で、極性ビットによってビットの反転が指定される場合は、データバイト内の全ビットが反転される。

別の実施形態では、各ページに個別の開始位置を用意するページ内ランダム化に加えて、ページ内の各データビットセットに個別の符号化極性を用意する。

本発明は、プログラムディスターブやユーザリードディスターブの原因となる特定のデータパターンを軽減もしくは解消するほか、NANDストリング抵抗効果を抑え、メモリの耐久性と信頼性を高める。フローティングゲート間結合の問題も緩和する。

図7Aは、1バンクの分割読み出し/書き込みスタックを有するコンパクトなメモリ装置を概略的に示すものであり、ここに本発明の改良されたプロセッサが実装される。このメモリ装置は、二次元のメモリセルアレイ300と、制御回路310と、読み出し/書き込み回路370とを備える。メモリアレイ300は、行デコーダ330によりワード線ごとにアドレスでき、列デコーダ360によりビット線ごとにアドレスできる。読み出し/書き込み回路370は1バンクの分割読み出し/書き込みスタック400として実装され、メモリセルからなるブロック(「ページ」とも呼ばれる)の読み出しまたはプログラミングを並行して行うことができる。好適な実施形態において、ページは一連のメモリセル行から構成される。1行のメモリセルを多数のブロックまたはページに分割する別の実施形態において、個々のブロックに向けて読み出し/書き込み回路370を多重化するためにブロックマルチプレクサ350を設ける。

分割読み出し/書き込みスタック400からなるバンク全体が並行して作動することにより、行沿いにp個のセルからなるブロック(またはページ)の読み出しまたはプログラミングを並行して行うことができる。この場合は、セル行全体に対してp個の読み出し/書き込みモジュールが存在することになる。各スタックでk個のメモリセルを処理するならば、バンク内の合計読み出し/書き込みスタック数はr=p/kで求められる。例えば、バンク内のスタック数がrならば、p=r*kである。例えば、メモリアレイにおいてk=8、r=512ならば、p=512バイト(512×8ビット)となる。ブロックは、好適な実施形態において、セル行全体である。ブロックは、別の実施形態において、行内のセルの小集団である。セルの小集団とは、例えば行全体の2分の1であったり、行全体の4分の1であったりする。セルの小集団は連続するセルであったり、1つおきのセルであったり、一定セル数おきのセルである。

スタックバスコントローラ410は、線411を通じて読み出し/書き込み回路370へ制御信号とタイミング信号を提供する。スタックバスコントローラ自体は、線311を通じてメモリコントローラ310に従属する。各読み出し/書き込みスタック400内の通信は相互接続スタックバス421(図8参照)によって行われ、スタックバスコントローラ410によって制御される。制御線411は、スタックバスコントローラ410から読み出し/書き込みスタック400−1のコンポーネントへ制御信号とクロック信号を提供する。

データラッチ430のスタックには、当該スタックに対応する各メモリセルにつき1つずつ、430−1から430−kまでのデータラッチがある。I/Oモジュール440は、データラッチがI/Oバス231を通じて外部とデータをやり取りできるようにする。 共通プロセッサはまた、エラー状態等、メモリの動作状態を伝えるステータス信号を出力する出力507を含む。このステータス信号は、Wired−OR構成でフラグバス509へ結合されたn−トランジスタ550のゲートを駆動するために使われる。フラグバスは、好ましくはコントローラ310によって予め荷電され、いずれかの読み出し/書き込みスタックによってステータス信号がアサートされるとプルダウンされる。

入力ロジック510はPバスからデータを受信し、スタックバスコントローラ410から信号線411経由で届く制御信号に応じて論理状態「1」、「0」、または「Z」(フローティング)のいずれかひとつに変換されるデータとして、BSIノードへ出力する。次に、セット/リセットラッチであるPラッチ520がBSIをラッチすることで、MTCHおよびMTCH*として一対の相補出力信号が用意される。

出力ロジック530はMTCH信号とMTCH*信号を受信し、スタックバスコントローラ410から信号線411経由で届く制御信号に応じて論理状態「1」、「0」、または「Z」(フローティング)のいずれかひとつに変換されるデータを、Pバス505沿いに出力する。

BSIが入力データと同じになるPASSTHROUGHモードの場合、信号ONEは論理「1」、ONEB<0>は「0」、ONEB<1>は「0」となる。これによりプルアップまたはプルダウンはディスエーブルされるが、転送ゲート522はイネーブルされ、データはPバス505に沿って出力523へ引き渡される。BSIが入力データの逆になるINVERTEDモードの場合、信号ONEは「0」、ONEB<0>は「1」、ONEB<1>は「1」となる。これにより、転送ゲート522はディスエーブルされる。また、PBUSが「0」ならプルダウン回路はディスエーブルされ、プルアップ回路はイネーブルされ、結果的にBSIは「1」になる。同様に、PBUSが「1」ならば、プルアップ回路はディスエーブルされ、プルダウン回路はイネーブルされ、結果的にBSIは「0」になる。最後に、FLOATEDモードの場合は、信号ONEが「1」、ONEB<0>が「1」、ONEB<1>が「0」となり、出力BSIをフローティングさせることができる。FLOATEDモードは完全を期するために記載されているが、実際には使われない。

その全体が本願明細書において参照により援用されている米国公開特許出願第2006−0140007号(特許文献25)では、共通プロセッサの動作がより詳しく説明されている。

本発明のいくつかの態様において、読み出し、書き込み、消去といったほかの作業に内部メモリが従事しているときにデータを出し入れするキャッシュ操作にあたって、図10で前述した読み出し/書き込みスタックのデータラッチを利用する。前述したアーキテクチャでは、多数の物理ページによってデータラッチが共用される。例えば、ビット線の読み出し/書き込みスタックを全てのワード線で共用すれば、あるひとつの操作が進行しているときに空いているラッチがあれば、同じワード線か別のワード線における先々の操作に向けて空いているラッチにデータをキャッシュできるため、転送時間は他の操作の背後に潜在化され、時間の節約になる。この場合は異なる操作または操作段階のパイプライン処理の拡大により性能を上げることができる。例えば、キャッシュプログラミング操作で1ページのデータをプログラムしているときに別のページのデータを読み込めば、転送時間を節約できる。他の例として、例示的な実施形態において、あるひとつのワード線における読み出し操作を別のワード線における書き込み操作に挿入することにより、データの書き込みを継続しながら読み出しデータをメモリから出すことができる。

データ書き込み:〜700μs(下位ページ〜600μs、上位ページ800μs)

バイナリデータ書き込み:〜200μs

消去:〜2,500μs

読み出し:〜20−40μs

読み出しとトグルアウトデータ:2KBデータ、〜80μs;4KB〜160μs;8KB〜320μs

これ以降、タイミング図との関係で相対的時間を説明する際には、これらの値を基準として使用し得る。主要な態様において、読み出し/書き込みスタックの共用ラッチが使用可能であれば、複数の段階をともなう長い操作の合間に短い操作を差しはさむ。例えば、プログラミング操作や消去操作の中に読み出しを挿し込んだり、消去中にバイナリプログラミングを挿し込んだりすることができる。主要な例示的な実施形態において、同じ読み出し/書き込みスタックを共用するページのプログラミング操作のときに別のページのデータをトグルイン/アウトする。例えば、データ書き込みのベリファイ段階に、トグルアウトされ修正されるデータの読み出しを挿し込む。

(1)このプロセスは、データラッチDL0 434−0をデフォルト値「1」にリセットすることから始まる。この変換は部分ページプログラミングを簡素化するためのものであり、選択された行の中でプログラミングの対象とならないセルはプログラム禁止になる。

(2)I/O線231に沿ってDL0 434−0にプログラムデータが供給される。

(3)DL1 434−1とDL2 434−2(このラッチを使用し、クイックパス書き込みを実施する場合)へプログラムデータが転送される。

(4)DL1 434−1へプログラムデータが転送されたら、データラッチDL0 434−0を「1」にリセットでき、プログラミング中はI/O線231に沿って次のデータページをDL0 434−0に読み込むことができ、第1のページが書き込まれているときには第2のページをキャッシュできる。

(5)DL1 434−1に第1のページが読み込まれたら、プログラミングを開始できる。DL1 434−1のデータによりセルはロックアウトされ、それ以上プログラムできなくなる。本願と同時に出願された「Use of Data Latches in Multi-Phase Programming of Non-Volatile Memories 」という米国特許出願(特許文献26)で説明されているように、DL2 434−2のデータは、クイックパス書き込みの第2段階への移行を決定づける下位ベリファイロックアウトに使われる。

(6)プログラミングが始まると、プログラミングパルスの後に下位ベリファイ結果をもとにDL2 434−2を更新し、上位ベリファイ結果をもとにDL1 434−1を更新する。(これは、下位ページプログラミングがA状態に至る「従来の」符号化に基づく説明である。本願と同時に出願された「Use of Data Latches in Multi-Phase Programming of Non-Volatile Memories 」という米国特許出願(特許文献26)と、2005年3月16日に出願された「Non-Volatile Memory and Method with Power-Saving Read and Program-Verify Operations 」という米国特許出願(特許文献27)では、この符号化とその他の符号化が説明されている。ここでの説明は他の符号化にも容易く敷衍できる。)

(7)プログラミングが完了したか否かの判断にあたっては、セル行(またはしかるべき物理的プログラミング単位)のDL1 434−1レジスタだけをチェックする。

(1)下位ページのプログラミングが終了したら、(未実行)キャッシュプログラミングコマンドを保持する状態マシンのコントローラからの信号により上位ページ(または次のページ)の書き込みが始まる。

(2)DL0 434−0(下位ページ書き込みのステップ(3)でプログラムデータが読み込まれたところ)からDL1 434−1とDL2 434−2へプログラムデータが転送される。

(3)アレイから下位ページが読み出され、DL0 434−0の中に置かれる。

(4)ベリファイハイおよびベリファイローロックアウトデータのためにDL1 434−1とDL2 434−2が再び使用される。ラッチDL0 434−0(下位ページデータを保持)はプログラム基準データとしてチェックされるが、ベリファイ結果によりこれが更新されることはない。

(5)B状態ベリファイの一部として、下位ベリファイVBLでの検知の後にはDL2 434−2でデータが更新され、DL1 434−1データは上位ベリファイVBH結果によって更新される。同様に、CベリファイにもVCL結果とVCH結果によりラッチDL2 434−2およびDL1 434−1を更新するための対応するコマンドがある。

(6)Bデータが完了したらC状態をベリファイするだけでよいので、下位ページデータ(基準としてDL0 434−0に保持されたもの)は必要ない。DL0 434−0を「1」にリセットし、I/O線231から別のページのプログラムデータを読み込み、ラッチDL0 434−0にキャッシュできる。共通プロセッサ500はC状態のみのベリファイを指示できる。

(7)B状態について上位ページのプログラミングが完了したか否かを判断するにあたっては、ラッチDL1 434−1とDL0 434−0の両方をチェックする。セルがB状態までプログラムされ、ベリファイするのがC状態だけになったら、ラッチDL1

434−1のデータだけをチェックし、プログラムされていないビットの有無を確認すればよい。

前述したように、図15に示されたキャッシュプログラミングをともなうシングルページアルゴリズムの場合は、たとえ時間t3 で上位ページデータが用意されても、メモリはこのデータの書き込みに着手する前に時間t4 まで待つことになる。米国特許出願第11/013,125号(特許文献28)等に詳述されているフルシーケンスプログラム動作に転換すれば、上位ページが用意された時点で上位ページと下位ページのデータを同時にプログラムできる。

(1)このプロセスは、データラッチDL0 434−0をデフォルト値「1」にリセットすることから始まる。この変換は部分ページプログラミングを簡素化するためのものであり、選択された行の中でプログラミングの対象とならないセルはプログラム禁止になる。

(2)I/O線231に沿ってDL0 434−0にプログラムデータが供給される。 (3)DL1 434−1とDL2 434−2(このラッチを使用し、クイックパス書き込みを実施する場合)へプログラムデータが転送される。

(4)DL1 434−1へプログラムデータが転送されたら、データラッチDL0

434−0を「1」にリセットでき、プログラミング中はI/O線231に沿って次のデータページをDL0 434−0に読み込むことができ、第1のページが書き込まれているときには第2のページをキャッシュできる。

第2のページのデータが読み込まれた時点で、これが書き込み中の下位ページの上位に相当し、下位ページのプログラミングがまだ終わっていなければ、フルシーケンス書き込みへの転換を実施できる。ここでの説明はかかるアルゴリズムにおけるデータラッチの使用に注目するものであり、詳細は同一出願人による同時係属の米国特許第7,120,051号(特許文献29)で詳述されている。

(5)上位ページデータがラッチDL0 434−0に読み込まれた後にはアドレスブロックで判断を下す。つまり、2つのページが同じワード線と同じブロックにあって、一方のページが下位ページであり、他方のページが上位ページであることをチェックする。そのとおりに下位ページプログラミングからフルシーケンスプログラミングへの転換が可能であれば、プログラム状態マシンがこの転換をトリガする。移行は未完了のベリファイが完了した後に行われる。

(6)プログラミングシーケンスが下位ページからフルシーケンスへ変化する場合は、通常ならばいくつかの操作パラメータが変更される。これは例示的な実施形態において次のものを含む。

(i)下位ページデータがロックアウトされていなければ、パルスベリファイサイクル数の最大プログラムループが下位ページアルゴリズムの最大プログラムループからフルシーケンスの最大プログラムループに変更される。しかし、完了プログラムループ数は転換によりリセットされない。

(ii)図16に見られるように、プログラミング波形は下位ページプログラミングプロセスで使われる値VPGM_Lで始まる。プログラミング波形が進展し、上位ページプロセスで使う初期値VPGM_Uを超えると、フルシーケンスへの転換にあたって階段はVPGM_Uまで戻り、そこから上昇を続ける。

(iii)プログラムパルスの最大値とステップサイズを決定するパラメータは変更されない。

(7)マルチレベル符号化で適切なデータのプログラミングを保証するため、メモリセルの現在状態のフルシーケンス読み出しを行わねばならない。こうすれば、フルシーケンスが始まるときに、下位ページのプログラミングでロックアウトされていて上位ページのデータを考慮に入れるためにさらなるプログラミングを必要とする状態はプログラム禁止にならない。

(8)クイックパス書き込みが行われる場合は、上位ページのプログラムデータを反映させるため、A状態のみの下位ベリファイに基づくラッチDL2 434−2のデータも更新される。

(9)マルチレベル、フルシーケンスのプログラムアルゴリズムによるプログラミングが再開する。図16に見られるように、下位ページプロセスのプログラミング波形が上位ページの初期レベルを超えると、波形は転換時にこのレベルに戻される。

キャッシュプログラミングアルゴリズムを使用する場合は、AおよびBデータがプログラムされた後に、プログラミングを完了するためにラッチDL1 434−1へC状態が転送される。この場合、下位ページは既にプログラムを通過していて不良ビットはないから、下位ページについてラッチをスキャンする必要はない。

(1)コピーするページ(「ページM」)がラッチDL1 434−1に読み込まれる。これは上位ページか下位ページのデータであり得る。

(2)次にページMがDL0 434−0へ移される。

(3)次にDL0 434−0のデータがトグルアウトされ、修正され、ラッチに戻される。

(4)ここでプログラミングシーケンスを開始できる。下位ページNに書き込むデータがDL1 434−1とDL2 434−2に移されたら、ラッチDL0 434−0はデータをキャッシュできる状態になる。この下位ページはプログラムされる。この実施形態の場合、プログラム状態マシンはここで停止する。

(5)コピーする次のページがDL0 434−0に読み込まれる。ここでプログラミングを再開できる。ステップ(4)の終わりに停止した状態マシンは、プログラミングシーケンスを最初から再開する。

(6)プログラミングは下位ページが完了するまで続く。

下位ページに対する書き込みか上位ページに対する書き込みかは、コピー先ページアドレスによって決まる。プログラムアドレスが上位ページアドレスなら、プログラミングシーケンスはプログラミングが完了するまで停止せず、ステップ(5)の読み出しは書き込みが完了した後に行われる。

(1)コピーするページ(「ページM」)がラッチDL1 434−1に読み込まれる。これは上位ページか下位ページであり得る。

(2)次にページMのデータがDL0 434−0へ移される。(前と同様に、N等は書き込みアドレスを表し、M等は読み出しアドレスを表す。)

(3)次にDL0 434−0のデータがトグルアウトされ、修正され、ラッチに戻される。

(4)状態マシンプログラミングは読み出しコマンドが届くまで無限待機状態に入り、その後には別のページ、例えば次のページM+1のラッチDL0 434−0への読み込みが始まる。

(5)ステップ(4)の読み込みが完了したら、ステップ(1〜3)のデータをページN(ここでは、下位ページ)にプログラムするためのワード線とブロックアドレスにアドレスが戻され、プログラミングが再開する。

(6)ページM+1の読み込みが完了したらデータをトグルアウトし、修正し、元に戻すことができる。処理が完了し、2つのページが同一WL上の対応する上位および下位ページなら、フルシーケンス書き込み操作に転換できる。

(7)フルシーケンス書き込みでAレベルとBレベルが終了したら、前に説明した通常のキャッシュプログラミングと同様に、DL0 434−0のデータがDL1 434−1へ移され、別のページ(例えば、M+2)の読み出しコマンドを発行できる。シングルページからフルシーケンスへの転換がない場合は、下位ページの書き込みが完了し、上位ページが始まる。Bレベル状態が完了すると再びDL0 434−0からDL1 434−1へデータが移され、状態マシンはページM+2の読み出しコマンドを待機する。

(8)読み出しコマンドが届くとアドレスは読み出しアドレスに切り替えられ、次のページ(ページM+2)が読み出される。

(9)読み出しが完了したら、アドレスは書き込みが終了するまで以前の上位ページアドレス(プログラムアドレスN+1)に戻される。

プログラミング操作とこれにともなうバックグラウンドデータキャッシングを、好適な多状態符号化との関係で説明する。

図20は、2ビット論理符号(「LM」符号)で符号化される4状態メモリのプログラミングと読み出しを示す。この符号は耐障害性を提供し、ユーピン効果による隣接セル結合を緩和する。図20は、LM符号を使用して各メモリセルに2ビットのデータを蓄積する場合の4状態メモリアレイのしきい値電圧分布を示す。LM符号化は、上位および下位ビットが状態「A」および「C」とで逆になる点が従来のグレイコードと異なる。米国特許第6,657,891号(特許文献35)に開示された「LM」符号は、電荷の大きな変化を要するプログラム操作を回避することによって隣接フローティングゲート間の電界効果結合を抑えるのに有利である。

メモリEEPROMまたはチップとランダム化手法の種々の実施形態は、NANDストリング抵抗の増加、耐久性と信頼性の低下、好ましくない結合等、反復データ蓄積パターンに起因する問題を最小限に抑えることを目指す。本発明の擬似ランダム化手法は実用的で、データ処理能力の点で実装コストは高くつかない。

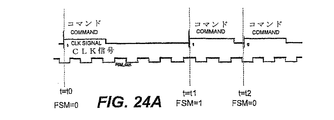

図21〜図25とこれらの図に対応する本願明細書での説明のように、共通のワード線によってアクセスされる各データページのプログラミングまたは読み出しは並行して行われる。ページ単位のランダム化にあたっては、ビットの極性を反転させるページを擬似ランダム的に選択する。

その全体が本願明細書において参照により援用されている2006年9月8日に出願されたYan Liらによる「Methods in a Pseudo Random and Command Driven Bit Compensation for the Cycling Effects in Flash Memory」という米国特許出願第11/530,392号(特許文献36)には、ページ単位のオンチップデータランダム化が開示されている。

ページ内データスクランブリングも望ましい。これは、プログラミング中に問題となる規則性の高いデータパターンを回避したり、ページデータを並行して検知する際のソース負荷誤差を制御したりするうえで有利である。

ユーザかコントローラによって反復するデータパターンが特定のページに蓄積されると、データが一定のパターンに並ぶことがあり、一部のNANDチェーンのプログラミングでブーストモードに悪影響がおよぶ。プログラミングのときに複数のNANDチェーン(図1Dおよび図3参照)に共通のワード線が選択される場合、プログラミングの対象とはならないチェーンはプログラム禁止にする。プログラム禁止にするにはチャネル領域をブーストし、選択されたワード線に印加される有効プログラミング電圧を減らす。例えば、NANDタイプのメモリでは通常、ソース側からドレイン側にかけてNANDチェーンがプログラムされる。消去済み状態の多数のメモリセルがソース側にあると、プログラム禁止のときにブーストされるドレイン側のチャネルから消去済みセルによって形成される高伝導性チャネルを通じてソースへ電荷が漏れ、効率が悪くなる。効果的でないチャネルブーストとプログラム禁止によってプログラムディスターブが起こり、結果に誤りが生じるおそれがある。その全体が本願明細書において参照により援用されている米国公開特許出願第2006−0198195号(特許文献37)および2006年12月29日に出願されたFarookh Moogatらによる「Method of NAND Flash Memory Cell Array with Adaptive Memory State Partitioning」というおよび米国特許出願第11/618,482号(特許文献38)には、ブースト効率の問題が記載されている。

本発明の一態様によると、ページ内データのランダム化により、複数のページでデータが並ぶ場合でも、プログラミング中に問題となるデータパターンは回避される。

好適な実施形態において、ページ上でデータをスクランブルするシンプルな方法により、データはページごとに独立しているかまたは異なる開始アドレスに書き込まれる。メモリセルの各ページには、ページごとに異なる開始位置に対応するデータページが書き込まれる。ページの終わりまでデータで埋め尽くされると、ページの最初のアドレスからラップアラウンドし、開始位置の手前まで書き込みを継続する。

ステップ700:集積回路メモリチップを提供する。このメモリチップは、ページ単位でアクセス可能な不揮発性メモリセルアレイを有し、各ページは1グループのメモリセルからなり、1グループの各メモリセルはアレイの列内にあり、かつ共通ワード線によりアクセス可能な行沿いに並ぶ。

ステップ710:プログラムされる各ページに対応する開始列位置からなる一連の開始列位置をオンチップで生成する。

ステップ720:各ページにプログラムされるデータを、対応する開始列位置から始めてページが埋め尽くされるまでラップアラウンドする。

ステップ730:配列されたデータを各ページに並行してプログラムする。

別の好適な実施形態において、図23Aに見られる擬似ランダムジェネレータ等によって、一連の開始物理列アドレスが、各ページにつき1つずつ、提供される。

各ページの開始位置シフトにより、NANDチェーンの中で望ましくないデータパターンの並びを回避できるほか、プログラミング中のブースト問題の緩和に役立つ。

プログラミング中のチャネルブースト問題の緩和に加え、ページの中でデータをスクランブリングすれば、検知中のソース負荷誤差制御に役立つ。

ソース負荷誤差は、ソース線とチップの接地パッドとの間の有限抵抗によって生じる。メモリセルの検知にあたっては、有限抵抗にまたがるソース負荷によってソース線バイアスが生じることがある。多数のメモリセルを並行して検知すると、メモリセルの総電流のため、有限抵抗により接地ループで著しい電圧降下が生じることがある。その結果、ソース線バイアスが生じ、しきい値電圧検知による読み出し操作に誤りが生じる。

それには、ページ内の個々のビットをランダム化する。好ましくは、ある極性を指定する一連の擬似ランダムビットを使ってページ内のビットを符号化する。一実施形態において、ページ内の各データビットにつき極性ビットがある。別の実施形態では、ページ内の各データバイトにつき極性ビットがある。この実施形態で、極性ビットによってビットの反転が指定される場合は、データバイト内の全ビットが反転される。

ステップ750:集積回路メモリチップを提供する。このメモリチップは、ページ単位でアクセス可能な不揮発性メモリセルアレイを有し、各ページは1グループのメモリセルからなり、1グループの各メモリセルはアレイの列内にあり、かつ共通ワード線によりアクセス可能な行沿いに並ぶ。

ステップ760:プログラムされるページの各データビットセットにつき第1および第2の符号化法を提供する。

ステップ762:一連の極性ビットを、各データビットセットにつき1つずつ、オンチップで生成する。

ステップ764:各データビットセットの極性ビットが第1の状態にあるか、それとも第2の状態にあるかに応じて、第1または第2の符号化法により各データビットセットを符号化する。

ステップ770:符号化された全データビットセットをページに並行してプログラムする。

全面的に消去済み状態になっているページ等、極端に規則性のあるデータパターンの場合は、ページ内スクランブリング方式では不十分である。

本発明のもうひとつの態様によると、ページ内ランダム化にページ単位のランダム化を組み合わせる。具体的にはオンチップ回路の限りあるリソースを踏まえ、ページ内ランダム化にあたっては各ページに個別の開始位置を用意するのが望ましく、ページ単位ランダム化にあたっては各ページに個別の符号化極性を用意するのが望ましい。

ステップ750:集積回路メモリチップを提供する。このメモリチップは、ページ単位でアクセス可能な不揮発性メモリセルアレイを有し、各ページは1グループのメモリセルからなり、1グループの各メモリセルはアレイの列内にあり、かつ共通ワード線によりアクセス可能な行沿いに並ぶ。

ステップ760:プログラムされる各データページにつき第1および第2の符号化法を提供する。

ステップ762:一連の極性ビットを、各ページにつき1つずつ、オンチップで生成する。

ステップ764:ページの極性ビットが第1の状態にあるか、それとも第2の状態にあるかに応じて、第1または第2の符号化法によりデータページを符号化する。

ステップ770:プログラムされる各ページに対応する開始列位置からなる一連の開始列位置をオンチップで生成する。

ステップ772:各ページにプログラムされるデータを、対応する開始列位置から始めてページが埋め尽くされるまでラップアラウンドする。

ステップ780:配列されたデータを各ページに並行してプログラムする。

これまで本発明の実施形態を説明してきたが、本発明はこれらの例示的な実施形態に限定されず、添付の特許請求の範囲によって規定されることを理解すべきである。

Claims (17)

- 集積回路メモリチップであって、

ページ単位でアクセス可能な不揮発性メモリセルアレイであって、各ページが1グループのメモリセルからなり、前記1グループの各メモリセルが前記アレイの列内にあり、かつ共通ワード線によりアクセス可能な行沿いに並ぶ不揮発性メモリセルアレイと、

プログラムされる各ページに対応する開始列位置を有する一連の同一ではない開始列位置と、

前記対応開始列位置のアドレスを生成するアドレスジェネレータと、

前記アドレスジェネレータに応答して、前記対応開始列位置から始めて前記ページが埋め尽くされるまで各ページにプログラムされるデータをラップアラウンドする各列につき1セットのデータラッチと、

配列されたデータを各ページに並行してプログラムするプログラミング回路と、

を備えるメモリチップ。 - 請求項1記載のメモリチップにおいて、

前記ページには連続番号が付され、ページに対応する前記開始列位置は前記ページ番号の関数であるメモリチップ。 - 請求項2記載のメモリチップにおいて、

前記関数により、前記列位置は前記グループ内のセル数のモジュロに所定数を加えたものとなるメモリチップ。 - 請求項3記載のメモリチップにおいて、

前記所定数は、0であるメモリチップ。 - 請求項1記載のメモリチップにおいて、

擬似ランダムジェネレータをさらに備え、

前記一連の同一ではない開始列位置は、前記擬似ランダムジェネレータによりオンチップで生成されるメモリチップ。 - 請求項5記載のメモリチップにおいて、

前記擬似ランダムジェネレータは、前記メモリチップの外部のイベントによってトリガされるタイミングにも応答し、

前記一連の同一ではない開始列位置は、前記タイミングの関数でもあるメモリチップ。 - 請求項1記載のメモリチップにおいて、

プログラムされる各データページの第1および第2の符号化法と、

各ページにつき1つの一連の極性ビットと、

前記ページの前記極性ビットが第1の状態にあるか、それとも第2の状態にあるかに応じて、第1または第2の符号化法により、前記データページを符号化するエンコーダと、をさらに備え、

前記第1の符号化法は、各列に対応するデータビットを変えずに残し、前記第2の符号化法は、データビットを反転させるメモリチップ。 - 請求項1記載のメモリチップにおいて、

前記アレイの前記メモリセルは、NANDアーキテクチャで構成されるメモリチップ。 - ページ単位でアクセス可能な不揮発性メモリセルアレイを有し、各ページが1グループのメモリセルからなり、前記1グループの各メモリセルが前記アレイの列内にあり、かつ共通ワード線によりアクセス可能な行沿いに並ぶ集積回路メモリチップで、前記アレイにデータをプログラムする方法であって、

プログラムされる各ページに対応する開始列位置を有する一連の同一ではない開始列位置をオンチップで生成するステップと、

各ページにプログラムされるデータを、前記対応開始列位置から始めて前記ページが埋め尽くされるまでラップアラウンドするステップと、

配列されたデータを各ページに並行してプログラムするステップと、

を含む方法。 - 請求項9記載の方法において、

前記ページには連続番号が付され、ページに対応する前記開始列位置は前記ページ番号の関数である方法。 - 請求項10記載の方法において、

前記関数により、前記列位置は前記グループ内のセル数のモジュロに所定数を加えたものとなる方法。 - 請求項11記載の方法において、

前記所定数は、0である方法。 - 請求項9記載の方法において、

前記一連の同一ではない開始列位置は、擬似ランダムジェネレータによりオンチップで生成される方法。 - 請求項13記載の方法において、

前記擬似ランダムジェネレータは、前記メモリチップの外部のイベントによってトリガされるタイミングにも応答し、

前記一連の同一ではない開始列位置は、前記タイミングの関数でもある方法。 - 請求項14記載の方法において、

前記外部イベントは、前記メモリチップのユーザによって生起される方法。 - 請求項14記載の方法において、

前記外部イベントは、外部のメモリコントローラによって生起される方法。 - 請求項9記載の方法において、

プログラムされる各データページにつき第1および第2の符号化法を提供するステップと、

一連の同一ではない極性ビットを、各ページにつき1つずつ、オンチップで生成するステップと、

前記ページの前記極性ビットが第1の状態にあるか、それとも第2の状態にあるかに応じて、第1または第2の符号化法により、前記データページを符号化するステップと、をさらに含み、

前記第1の符号化法は、各列に対応するデータビットを変えずに残し、前記第2の符号化法は、データビットを反転させる方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US11/852,229 US7885112B2 (en) | 2007-09-07 | 2007-09-07 | Nonvolatile memory and method for on-chip pseudo-randomization of data within a page and between pages |

| US11/852,229 | 2007-09-07 | ||

| PCT/US2008/073750 WO2009035834A2 (en) | 2007-09-07 | 2008-08-20 | Nonvolatile memory and method for on-chip pseudo-randomization of data within a page and between pages |

Related Child Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012087398A Division JP5537590B2 (ja) | 2007-09-07 | 2012-04-06 | ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2010538408A JP2010538408A (ja) | 2010-12-09 |

| JP2010538408A5 JP2010538408A5 (ja) | 2011-09-22 |

| JP5010031B2 true JP5010031B2 (ja) | 2012-08-29 |

Family

ID=40118001

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2010524087A Expired - Fee Related JP5010031B2 (ja) | 2007-09-07 | 2008-08-20 | ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 |

| JP2012087398A Expired - Fee Related JP5537590B2 (ja) | 2007-09-07 | 2012-04-06 | ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2012087398A Expired - Fee Related JP5537590B2 (ja) | 2007-09-07 | 2012-04-06 | ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US7885112B2 (ja) |

| EP (1) | EP2186094B1 (ja) |

| JP (2) | JP5010031B2 (ja) |

| KR (1) | KR101533965B1 (ja) |

| CN (1) | CN102318007B (ja) |

| AT (1) | ATE549719T1 (ja) |

| TW (1) | TWI383396B (ja) |

| WO (1) | WO2009035834A2 (ja) |

Families Citing this family (55)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7734861B2 (en) * | 2006-09-08 | 2010-06-08 | Sandisk Corporation | Pseudo random and command driven bit compensation for the cycling effects in flash memory |

| US7606966B2 (en) | 2006-09-08 | 2009-10-20 | Sandisk Corporation | Methods in a pseudo random and command driven bit compensation for the cycling effects in flash memory |

| US7764533B2 (en) * | 2007-09-18 | 2010-07-27 | International Business Machines Corporation | Multi-level memory cell utilizing measurement time delay as the characteristic parameter for level definition |

| JP5019611B2 (ja) * | 2007-12-27 | 2012-09-05 | 株式会社東芝 | メモリシステム |

| US8145855B2 (en) | 2008-09-12 | 2012-03-27 | Sandisk Technologies Inc. | Built in on-chip data scrambler for non-volatile memory |

| KR101082650B1 (ko) * | 2009-01-21 | 2011-11-14 | 주식회사 하이닉스반도체 | 불휘발성 메모리 장치 및 그 동작 방법 |

| KR101504338B1 (ko) * | 2009-03-04 | 2015-03-23 | 삼성전자주식회사 | 불휘발성 메모리 장치의 동작 방법 |

| KR20100099961A (ko) * | 2009-03-04 | 2010-09-15 | 삼성전자주식회사 | 불휘발성 메모리 장치 및 그 동작 방법 |

| KR20100124087A (ko) * | 2009-05-18 | 2010-11-26 | 삼성전자주식회사 | 메모리 컨트롤러, 그것을 포함하는 메모리 시스템 그리고 그것의 동작 방법 |

| US8102705B2 (en) | 2009-06-05 | 2012-01-24 | Sandisk Technologies Inc. | Structure and method for shuffling data within non-volatile memory devices |

| US20110002169A1 (en) | 2009-07-06 | 2011-01-06 | Yan Li | Bad Column Management with Bit Information in Non-Volatile Memory Systems |

| WO2011058657A1 (ja) * | 2009-11-16 | 2011-05-19 | 富士通株式会社 | 並列計算装置、並列計算方法、および並列計算プログラム |

| KR20110055178A (ko) * | 2009-11-19 | 2011-05-25 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것을 포함한 메모리 시스템 |

| US8495281B2 (en) * | 2009-12-04 | 2013-07-23 | International Business Machines Corporation | Intra-block memory wear leveling |

| US8725935B2 (en) | 2009-12-18 | 2014-05-13 | Sandisk Technologies Inc. | Balanced performance for on-chip folding of non-volatile memories |

| US8468294B2 (en) * | 2009-12-18 | 2013-06-18 | Sandisk Technologies Inc. | Non-volatile memory with multi-gear control using on-chip folding of data |

| US8144512B2 (en) * | 2009-12-18 | 2012-03-27 | Sandisk Technologies Inc. | Data transfer flows for on-chip folding |

| TWI438778B (zh) | 2010-03-25 | 2014-05-21 | Silicon Motion Inc | 用來抑制資料錯誤之方法以及相關之記憶裝置及其控制器 |

| KR20120002760A (ko) * | 2010-07-01 | 2012-01-09 | 삼성전자주식회사 | 낸드 플래쉬 메모리의 동작 신뢰성을 향상시키는 데이터 기록 방법 및 데이터 기록 장치 |

| US9342446B2 (en) | 2011-03-29 | 2016-05-17 | SanDisk Technologies, Inc. | Non-volatile memory system allowing reverse eviction of data updates to non-volatile binary cache |

| US8843693B2 (en) | 2011-05-17 | 2014-09-23 | SanDisk Technologies, Inc. | Non-volatile memory and method with improved data scrambling |

| US8762626B2 (en) | 2011-09-12 | 2014-06-24 | Sandisk Technologies Inc. | Data modification based on matching bit patterns |

| KR20130046190A (ko) * | 2011-10-27 | 2013-05-07 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 이의 동작 방법 |

| US8842473B2 (en) | 2012-03-15 | 2014-09-23 | Sandisk Technologies Inc. | Techniques for accessing column selecting shift register with skipped entries in non-volatile memories |

| US8681548B2 (en) | 2012-05-03 | 2014-03-25 | Sandisk Technologies Inc. | Column redundancy circuitry for non-volatile memory |

| US9292428B2 (en) * | 2012-09-05 | 2016-03-22 | Kabushiki Kaisha Toshiba | Memory system |

| US8897080B2 (en) | 2012-09-28 | 2014-11-25 | Sandisk Technologies Inc. | Variable rate serial to parallel shift register |

| US9076506B2 (en) | 2012-09-28 | 2015-07-07 | Sandisk Technologies Inc. | Variable rate parallel to serial shift register |

| US9490035B2 (en) | 2012-09-28 | 2016-11-08 | SanDisk Technologies, Inc. | Centralized variable rate serializer and deserializer for bad column management |

| TWI502597B (zh) * | 2013-05-13 | 2015-10-01 | Univ Nat Taiwan Science Tech | 非揮發性記憶體的資料反轉與回復方法 |

| KR102164630B1 (ko) | 2013-06-28 | 2020-10-12 | 삼성전자주식회사 | 메모리 컨트롤러 및 상기 메모리 컨트롤러의 동작 방법 |

| TWI527039B (zh) * | 2013-08-02 | 2016-03-21 | Toshiba Kk | Semiconductor memory device and data reading method |

| US9129701B2 (en) | 2013-12-19 | 2015-09-08 | Sandisk Technologies Inc. | Asymmetric state detection for non-volatile storage |

| US9576624B2 (en) | 2014-06-30 | 2017-02-21 | Seagate Technology Llc | Multi-dimentional data randomization |

| US9934872B2 (en) | 2014-10-30 | 2018-04-03 | Sandisk Technologies Llc | Erase stress and delta erase loop count methods for various fail modes in non-volatile memory |

| TWI566249B (zh) * | 2014-11-21 | 2017-01-11 | 慧榮科技股份有限公司 | 快閃記憶體的資料寫入方法與其控制裝置 |

| US9224502B1 (en) | 2015-01-14 | 2015-12-29 | Sandisk Technologies Inc. | Techniques for detection and treating memory hole to local interconnect marginality defects |

| US10032524B2 (en) | 2015-02-09 | 2018-07-24 | Sandisk Technologies Llc | Techniques for determining local interconnect defects |

| JP5940705B1 (ja) * | 2015-03-27 | 2016-06-29 | ウィンボンド エレクトロニクス コーポレーション | 半導体記憶装置 |

| US9564219B2 (en) | 2015-04-08 | 2017-02-07 | Sandisk Technologies Llc | Current based detection and recording of memory hole-interconnect spacing defects |

| US9269446B1 (en) | 2015-04-08 | 2016-02-23 | Sandisk Technologies Inc. | Methods to improve programming of slow cells |

| JP6958363B2 (ja) * | 2016-02-08 | 2021-11-02 | ソニーグループ株式会社 | メモリコントローラ、不揮発性メモリおよびメモリコントローラの制御方法 |

| KR102511459B1 (ko) * | 2016-03-17 | 2023-03-17 | 삼성전자주식회사 | 비휘발성 메모리 장치 및 그 동작 방법 |

| SG10201605746RA (en) * | 2016-07-13 | 2018-02-27 | Micron Technology Inc | Data storage with data randomizer in multiple operating modes |

| KR20190006760A (ko) * | 2017-07-11 | 2019-01-21 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그것의 동작 방법 |

| US10319444B2 (en) | 2017-10-30 | 2019-06-11 | International Business Machines Corporation | Memory data randomizer |

| TWI709855B (zh) * | 2018-01-26 | 2020-11-11 | 慧榮科技股份有限公司 | 用來於一記憶裝置中進行寫入管理之方法以及記憶裝置及其控制器 |

| TWI660269B (zh) | 2018-01-26 | 2019-05-21 | 慧榮科技股份有限公司 | 用來於一記憶裝置中進行寫入管理之方法以及記憶裝置及其控制器 |

| TWI641223B (zh) * | 2018-02-07 | 2018-11-11 | 大陸商北京集創北方科技股份有限公司 | Pseudo random bit sequence generation method and device, and integrated circuit generation system for generating pseudo random bit sequence generation device |

| US11012425B2 (en) | 2018-12-28 | 2021-05-18 | Micron Technology, Inc. | Replay protection nonce generation |

| US10937510B2 (en) | 2019-06-28 | 2021-03-02 | Western Digital Technologies, Inc. | Multidimensional pseudorandom binary sequence analysis for a memory device |

| JP2021140837A (ja) * | 2020-03-02 | 2021-09-16 | キオクシア株式会社 | 半導体記憶装置 |

| US11462278B2 (en) * | 2020-05-26 | 2022-10-04 | Samsung Electronics Co., Ltd. | Method and apparatus for managing seed value for data scrambling in NAND memory |

| WO2022192049A1 (en) * | 2021-03-10 | 2022-09-15 | Sunrise Memory Corporation | Semiconductor memory device with write disturb reduction |

| US11462279B1 (en) * | 2021-05-13 | 2022-10-04 | Western Digital Technologies, Inc. | Modified distribution of memory device states |

Family Cites Families (66)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| IT1224062B (it) | 1979-09-28 | 1990-09-26 | Ates Componenti Elettron | Metodo di programmazione per una memoria a semiconduttore non volatile elettricamente alterabile |

| US5095344A (en) | 1988-06-08 | 1992-03-10 | Eliyahou Harari | Highly compact eprom and flash eeprom devices |

| US4993029A (en) | 1989-03-13 | 1991-02-12 | International Business Machines Corporation | Method and apparatus for randomizing data in a direct access storage device |

| US5070032A (en) | 1989-03-15 | 1991-12-03 | Sundisk Corporation | Method of making dense flash eeprom semiconductor memory structures |

| EP0675502B1 (en) | 1989-04-13 | 2005-05-25 | SanDisk Corporation | Multiple sector erase flash EEPROM system |

| US5172338B1 (en) | 1989-04-13 | 1997-07-08 | Sandisk Corp | Multi-state eeprom read and write circuits and techniques |

| US5343063A (en) | 1990-12-18 | 1994-08-30 | Sundisk Corporation | Dense vertical programmable read only memory cell structure and processes for making them |

| JP3992757B2 (ja) * | 1991-04-23 | 2007-10-17 | テキサス インスツルメンツ インコーポレイテツド | マイクロプロセッサと同期するメモリ、及びデータプロセッサ、同期メモリ、周辺装置とシステムクロックを含むシステム |

| US6222762B1 (en) | 1992-01-14 | 2001-04-24 | Sandisk Corporation | Multi-state memory |

| US5313421A (en) | 1992-01-14 | 1994-05-17 | Sundisk Corporation | EEPROM with split gate source side injection |

| US5315541A (en) | 1992-07-24 | 1994-05-24 | Sundisk Corporation | Segmented column memory array |

| US5555204A (en) | 1993-06-29 | 1996-09-10 | Kabushiki Kaisha Toshiba | Non-volatile semiconductor memory device |

| KR0169267B1 (ko) | 1993-09-21 | 1999-02-01 | 사토 후미오 | 불휘발성 반도체 기억장치 |

| JPH07228407A (ja) * | 1994-02-17 | 1995-08-29 | Shinko Electric Co Ltd | カード処理装置 |

| JPH07240098A (ja) | 1994-02-25 | 1995-09-12 | Sony Corp | 半導体不揮発性記憶装置 |

| US5661053A (en) | 1994-05-25 | 1997-08-26 | Sandisk Corporation | Method of making dense flash EEPROM cell array and peripheral supporting circuits formed in deposited field oxide with the use of spacers |

| KR0172366B1 (ko) | 1995-11-10 | 1999-03-30 | 김광호 | 불휘발성 반도체 메모리 장치의 독출 및 프로그램 방법과 그 회로 |

| JPH09204783A (ja) * | 1996-01-25 | 1997-08-05 | Sony Corp | 半導体不揮発性記憶装置 |

| US5903495A (en) | 1996-03-18 | 1999-05-11 | Kabushiki Kaisha Toshiba | Semiconductor device and memory system |

| US5768192A (en) | 1996-07-23 | 1998-06-16 | Saifun Semiconductors, Ltd. | Non-volatile semiconductor memory cell utilizing asymmetrical charge trapping |

| JPH10302490A (ja) * | 1997-04-25 | 1998-11-13 | Mitsubishi Electric Corp | 読み出し専用半導体記憶装置 |

| US6768165B1 (en) | 1997-08-01 | 2004-07-27 | Saifun Semiconductors Ltd. | Two bit non-volatile electrically erasable and programmable semiconductor memory cell utilizing asymmetrical charge trapping |

| US6333871B1 (en) * | 1998-02-16 | 2001-12-25 | Hitachi, Ltd. | Nonvolatile semiconductor memory including a controller for providing an improved reprogram operation |

| JP3999900B2 (ja) * | 1998-09-10 | 2007-10-31 | 株式会社東芝 | 不揮発性半導体メモリ |

| EP1130600A1 (en) | 2000-03-01 | 2001-09-05 | Hewlett-Packard Company, A Delaware Corporation | Data balancing scheme in solid state storage devices |

| JP3940544B2 (ja) * | 2000-04-27 | 2007-07-04 | 株式会社東芝 | 不揮発性半導体メモリのベリファイ方法 |

| US6266273B1 (en) | 2000-08-21 | 2001-07-24 | Sandisk Corporation | Method and structure for reliable data copy operation for non-volatile memories |

| JP3829088B2 (ja) * | 2001-03-29 | 2006-10-04 | 株式会社東芝 | 半導体記憶装置 |

| US7549011B2 (en) | 2001-08-30 | 2009-06-16 | Micron Technology, Inc. | Bit inversion in memory devices |

| JP3881869B2 (ja) | 2001-11-05 | 2007-02-14 | 株式会社ルネサステクノロジ | 半導体記憶装置 |

| US6781877B2 (en) | 2002-09-06 | 2004-08-24 | Sandisk Corporation | Techniques for reducing effects of coupling between storage elements of adjacent rows of memory cells |

| US7196931B2 (en) | 2002-09-24 | 2007-03-27 | Sandisk Corporation | Non-volatile memory and method with reduced source line bias errors |

| US6983428B2 (en) | 2002-09-24 | 2006-01-03 | Sandisk Corporation | Highly compact non-volatile memory and method thereof |

| US6657891B1 (en) | 2002-11-29 | 2003-12-02 | Kabushiki Kaisha Toshiba | Semiconductor memory device for storing multivalued data |

| US7073103B2 (en) | 2002-12-05 | 2006-07-04 | Sandisk Corporation | Smart verify for multi-state memories |

| US7237074B2 (en) * | 2003-06-13 | 2007-06-26 | Sandisk Corporation | Tracking cells for a memory system |

| US7173863B2 (en) | 2004-03-08 | 2007-02-06 | Sandisk Corporation | Flash controller cache architecture |

| US7466590B2 (en) | 2004-02-06 | 2008-12-16 | Sandisk Corporation | Self-boosting method for flash memory cells |

| EP1729305A4 (en) * | 2004-03-26 | 2007-08-22 | Spansion Llc | SEMICONDUCTOR DEVICE AND METHOD FOR RECORDING DATA IN A SEMICONDUCTOR DEVICE |

| US7490283B2 (en) | 2004-05-13 | 2009-02-10 | Sandisk Corporation | Pipelined data relocation and improved chip architectures |

| US7274596B2 (en) | 2004-06-30 | 2007-09-25 | Micron Technology, Inc. | Reduction of adjacent floating gate data pattern sensitivity |

| US20060001400A1 (en) | 2004-06-30 | 2006-01-05 | Zedell Karl F | Battery charger with retention arms |

| EP1622009A1 (en) | 2004-07-27 | 2006-02-01 | Texas Instruments Incorporated | JSM architecture and systems |

| US8375146B2 (en) | 2004-08-09 | 2013-02-12 | SanDisk Technologies, Inc. | Ring bus structure and its use in flash memory systems |

| US7158421B2 (en) * | 2005-04-01 | 2007-01-02 | Sandisk Corporation | Use of data latches in multi-phase programming of non-volatile memories |

| US7120051B2 (en) | 2004-12-14 | 2006-10-10 | Sandisk Corporation | Pipelined programming of non-volatile memories using early data |

| US7409473B2 (en) | 2004-12-21 | 2008-08-05 | Sandisk Corporation | Off-chip data relocation |

| US7230851B2 (en) | 2004-12-23 | 2007-06-12 | Sandisk Corporation | Reducing floating gate to floating gate coupling effect |

| US20060140007A1 (en) | 2004-12-29 | 2006-06-29 | Raul-Adrian Cernea | Non-volatile memory and method with shared processing for an aggregate of read/write circuits |

| EP1686592A3 (en) | 2005-01-19 | 2007-04-25 | Saifun Semiconductors Ltd. | Partial erase verify |

| US7251160B2 (en) | 2005-03-16 | 2007-07-31 | Sandisk Corporation | Non-volatile memory and method with power-saving read and program-verify operations |

| US7447078B2 (en) | 2005-04-01 | 2008-11-04 | Sandisk Corporation | Method for non-volatile memory with background data latch caching during read operations |

| US7206230B2 (en) | 2005-04-01 | 2007-04-17 | Sandisk Corporation | Use of data latches in cache operations of non-volatile memories |

| WO2006107651A1 (en) | 2005-04-01 | 2006-10-12 | Sandisk Corporation | Multi-state memory having data recovery after program fail |

| US7564713B2 (en) * | 2005-04-28 | 2009-07-21 | Kabushiki Kaisha Toshiba | Semiconductor integrated circuit device wherein during data write a potential transferred to each bit line is changed in accordance with program order of program data |

| US7203092B2 (en) * | 2005-05-12 | 2007-04-10 | Micron Technology, Inc. | Flash memory array using adjacent bit line as source |

| US7975304B2 (en) | 2006-04-28 | 2011-07-05 | Trend Micro Incorporated | Portable storage device with stand-alone antivirus capability |

| US7558131B2 (en) | 2006-05-18 | 2009-07-07 | Micron Technology, Inc. | NAND system with a data write frequency greater than a command-and-address-load frequency |

| US7734861B2 (en) | 2006-09-08 | 2010-06-08 | Sandisk Corporation | Pseudo random and command driven bit compensation for the cycling effects in flash memory |

| US7606966B2 (en) | 2006-09-08 | 2009-10-20 | Sandisk Corporation | Methods in a pseudo random and command driven bit compensation for the cycling effects in flash memory |

| JP4778585B2 (ja) * | 2006-09-08 | 2011-09-21 | サンディスク コーポレイション | フラッシュメモリにおけるサイクル効果の擬似ランダムおよびコマンド主導型ビット補償とその方法 |

| US7489547B2 (en) | 2006-12-29 | 2009-02-10 | Sandisk Corporation | Method of NAND flash memory cell array with adaptive memory state partitioning |

| JP4498370B2 (ja) * | 2007-02-14 | 2010-07-07 | 株式会社東芝 | データ書き込み方法 |

| JP2008217857A (ja) * | 2007-02-28 | 2008-09-18 | Toshiba Corp | メモリコントローラ及び半導体装置 |

| KR100857252B1 (ko) * | 2007-12-27 | 2008-09-05 | (주)인디링스 | 마모도를 비트 수준에서 평준화하는 플래시 메모리 장치 및플래시 메모리 프로그래밍 방법 |

| US8301912B2 (en) * | 2007-12-31 | 2012-10-30 | Sandisk Technologies Inc. | System, method and memory device providing data scrambling compatible with on-chip copy operation |

-

2007

- 2007-09-07 US US11/852,229 patent/US7885112B2/en active Active

-

2008

- 2008-08-20 CN CN200880115127.0A patent/CN102318007B/zh active Active

- 2008-08-20 WO PCT/US2008/073750 patent/WO2009035834A2/en active Application Filing

- 2008-08-20 JP JP2010524087A patent/JP5010031B2/ja not_active Expired - Fee Related

- 2008-08-20 EP EP08830722A patent/EP2186094B1/en not_active Not-in-force

- 2008-08-20 AT AT08830722T patent/ATE549719T1/de active

- 2008-08-20 KR KR1020107005088A patent/KR101533965B1/ko active IP Right Grant

- 2008-08-28 TW TW097132939A patent/TWI383396B/zh not_active IP Right Cessation

-

2012

- 2012-04-06 JP JP2012087398A patent/JP5537590B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| EP2186094A2 (en) | 2010-05-19 |

| KR20100075833A (ko) | 2010-07-05 |

| WO2009035834A2 (en) | 2009-03-19 |

| JP5537590B2 (ja) | 2014-07-02 |

| TWI383396B (zh) | 2013-01-21 |

| CN102318007B (zh) | 2015-02-18 |

| JP2012169034A (ja) | 2012-09-06 |

| WO2009035834A3 (en) | 2009-05-22 |

| EP2186094B1 (en) | 2012-03-14 |

| US7885112B2 (en) | 2011-02-08 |

| ATE549719T1 (de) | 2012-03-15 |

| TW200929219A (en) | 2009-07-01 |

| US20090067244A1 (en) | 2009-03-12 |

| KR101533965B1 (ko) | 2015-07-06 |

| CN102318007A (zh) | 2012-01-11 |

| JP2010538408A (ja) | 2010-12-09 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP5537590B2 (ja) | ページ内・ページ間オンチップデータ擬似ランダム化のための不揮発性メモリおよび方法 | |

| KR101106977B1 (ko) | 비휘발성 메모리의 캐시 동작에서의 데이터 래치의 사용 | |

| US7734861B2 (en) | Pseudo random and command driven bit compensation for the cycling effects in flash memory | |

| JP4814995B2 (ja) | 読み出し操作中にデータラッチでバックグラウンドキャッシングを行う不揮発性メモリとその方法 | |

| JP4778585B2 (ja) | フラッシュメモリにおけるサイクル効果の擬似ランダムおよびコマンド主導型ビット補償とその方法 | |

| US8027195B2 (en) | Folding data stored in binary format into multi-state format within non-volatile memory devices | |

| US7606966B2 (en) | Methods in a pseudo random and command driven bit compensation for the cycling effects in flash memory | |

| EP2438595A1 (en) | Folding data stored in binary format into multi-state format within non-volatile memory devices | |

| JP2008535138A (ja) | 不揮発性メモリの複数段階プログラミングにおけるデータラッチの使用 | |

| JP4791580B2 (ja) | 不揮発性メモリおよびキャッシュページコピー方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110802 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20110802 |

|

| A871 | Explanation of circumstances concerning accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A871 Effective date: 20110802 |

|

| A975 | Report on accelerated examination |

Free format text: JAPANESE INTERMEDIATE CODE: A971005 Effective date: 20110830 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111011 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20120105 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20120113 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120406 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120531 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 5010031 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150608 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150608 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313113 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150608 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |