JP4987696B2 - 分離トレンチ - Google Patents

分離トレンチ Download PDFInfo

- Publication number

- JP4987696B2 JP4987696B2 JP2007510752A JP2007510752A JP4987696B2 JP 4987696 B2 JP4987696 B2 JP 4987696B2 JP 2007510752 A JP2007510752 A JP 2007510752A JP 2007510752 A JP2007510752 A JP 2007510752A JP 4987696 B2 JP4987696 B2 JP 4987696B2

- Authority

- JP

- Japan

- Prior art keywords

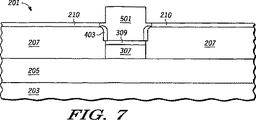

- trench

- layer

- dielectric material

- semiconductor

- wafer

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D86/00—Integrated devices formed in or on insulating or conducting substrates, e.g. formed in silicon-on-insulator [SOI] substrates or on stainless steel or glass substrates

- H10D86/01—Manufacture or treatment

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Element Separation (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/836,150 | 2004-04-30 | ||

| US10/836,150 US6979627B2 (en) | 2004-04-30 | 2004-04-30 | Isolation trench |

| PCT/US2005/011553 WO2005112124A2 (en) | 2004-04-30 | 2005-04-05 | Isolation trench |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2007535815A JP2007535815A (ja) | 2007-12-06 |

| JP2007535815A5 JP2007535815A5 (enExample) | 2008-05-29 |

| JP4987696B2 true JP4987696B2 (ja) | 2012-07-25 |

Family

ID=35186204

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007510752A Expired - Fee Related JP4987696B2 (ja) | 2004-04-30 | 2005-04-05 | 分離トレンチ |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6979627B2 (enExample) |

| JP (1) | JP4987696B2 (enExample) |

| KR (1) | KR20070007870A (enExample) |

| CN (1) | CN100524814C (enExample) |

| TW (1) | TWI379340B (enExample) |

| WO (1) | WO2005112124A2 (enExample) |

Families Citing this family (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6949443B2 (en) * | 2003-10-10 | 2005-09-27 | Taiwan Semiconductor Manufacturing Company | High performance semiconductor devices fabricated with strain-induced processes and methods for making same |

| JP2006278754A (ja) | 2005-03-29 | 2006-10-12 | Fujitsu Ltd | 半導体装置及びその製造方法 |

| JP2006351694A (ja) * | 2005-06-14 | 2006-12-28 | Fujitsu Ltd | 半導体装置およびその製造方法 |

| KR100698085B1 (ko) * | 2005-12-29 | 2007-03-23 | 동부일렉트로닉스 주식회사 | 트랜치 형성방법 |

| US7670895B2 (en) * | 2006-04-24 | 2010-03-02 | Freescale Semiconductor, Inc | Process of forming an electronic device including a semiconductor layer and another layer adjacent to an opening within the semiconductor layer |

| US7491622B2 (en) | 2006-04-24 | 2009-02-17 | Freescale Semiconductor, Inc. | Process of forming an electronic device including a layer formed using an inductively coupled plasma |

| US7528078B2 (en) * | 2006-05-12 | 2009-05-05 | Freescale Semiconductor, Inc. | Process of forming electronic device including a densified nitride layer adjacent to an opening within a semiconductor layer |

| US7514317B2 (en) * | 2006-08-31 | 2009-04-07 | Infineon Technologies Ag | Strained semiconductor device and method of making same |

| US7704823B2 (en) * | 2006-08-31 | 2010-04-27 | Infineon Technologies Ag | Strained semiconductor device and method of making same |

| US20080057636A1 (en) * | 2006-08-31 | 2008-03-06 | Richard Lindsay | Strained semiconductor device and method of making same |

| US8236638B2 (en) | 2007-04-18 | 2012-08-07 | Freescale Semiconductor, Inc. | Shallow trench isolation for SOI structures combining sidewall spacer and bottom liner |

| US20090289280A1 (en) * | 2008-05-22 | 2009-11-26 | Da Zhang | Method for Making Transistors and the Device Thereof |

| US8003454B2 (en) * | 2008-05-22 | 2011-08-23 | Freescale Semiconductor, Inc. | CMOS process with optimized PMOS and NMOS transistor devices |

| KR20120083142A (ko) * | 2011-01-17 | 2012-07-25 | 삼성전자주식회사 | 반도체 장치 및 반도체 장치의 형성 방법 |

| FR2990057A1 (fr) * | 2012-04-26 | 2013-11-01 | St Microelectronics Crolles 2 | Procede de formation de tranchees peu profondes |

| CN105008593B (zh) | 2013-02-28 | 2018-08-24 | 三井金属矿业株式会社 | 黑化表面处理铜箔、黑化表面处理铜箔的制造方法、覆铜层压板及柔性印刷线路板 |

| CN104299938B (zh) * | 2013-07-16 | 2018-03-30 | 中芯国际集成电路制造(上海)有限公司 | 浅沟槽隔离结构的形成方法 |

| US9076868B1 (en) * | 2014-07-18 | 2015-07-07 | Globalfoundries Inc. | Shallow trench isolation structure with sigma cavity |

| US10707330B2 (en) * | 2018-02-15 | 2020-07-07 | Globalfoundries Inc. | Semiconductor device with interconnect to source/drain |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS61198745A (ja) * | 1985-02-28 | 1986-09-03 | Fujitsu Ltd | 半導体装置の製造方法 |

| DE3639058A1 (de) * | 1985-12-16 | 1987-06-19 | Mitsubishi Electric Corp | Verfahren zur herstellung einer halbleitereinrichtung |

| JP2955459B2 (ja) * | 1993-12-20 | 1999-10-04 | 株式会社東芝 | 半導体装置の製造方法 |

| US5872058A (en) * | 1997-06-17 | 1999-02-16 | Novellus Systems, Inc. | High aspect ratio gapfill process by using HDP |

| US6121133A (en) * | 1997-08-22 | 2000-09-19 | Micron Technology, Inc. | Isolation using an antireflective coating |

| TW434786B (en) * | 1999-03-04 | 2001-05-16 | Mosel Vitelic Inc | Method for fabricating a trench isolation |

| KR100312943B1 (ko) * | 1999-03-18 | 2001-11-03 | 김영환 | 반도체장치 및 그의 제조방법 |

| US6576949B1 (en) * | 1999-08-30 | 2003-06-10 | Advanced Micro Devices, Inc. | Integrated circuit having optimized gate coupling capacitance |

| EP1257367A4 (en) * | 2000-02-08 | 2005-01-26 | Adsil Lc | METHOD FOR INCREASING THE THERMAL EFFICIENCY THROUGH THE USE OF SILANE COATINGS AND COATED ARTICLES |

| US6541382B1 (en) * | 2000-04-17 | 2003-04-01 | Taiwan Semiconductor Manufacturing Company | Lining and corner rounding method for shallow trench isolation |

| US6277709B1 (en) * | 2000-07-28 | 2001-08-21 | Vanguard International Semiconductor Corp. | Method of forming shallow trench isolation structure |

| KR100363558B1 (ko) * | 2001-02-23 | 2002-12-05 | 삼성전자 주식회사 | 반도체 장치의 트렌치 격리 형성 방법 |

| US6524929B1 (en) * | 2001-02-26 | 2003-02-25 | Advanced Micro Devices, Inc. | Method for shallow trench isolation using passivation material for trench bottom liner |

| US6645867B2 (en) * | 2001-05-24 | 2003-11-11 | International Business Machines Corporation | Structure and method to preserve STI during etching |

| US6531377B2 (en) * | 2001-07-13 | 2003-03-11 | Infineon Technologies Ag | Method for high aspect ratio gap fill using sequential HDP-CVD |

| US6602792B2 (en) * | 2001-08-02 | 2003-08-05 | Macronix International Co., Ltd. | Method for reducing stress of sidewall oxide layer of shallow trench isolation |

| US6798038B2 (en) * | 2001-09-20 | 2004-09-28 | Kabushiki Kaisha Toshiba | Manufacturing method of semiconductor device with filling insulating film into trench |

| DE10154346C2 (de) * | 2001-11-06 | 2003-11-20 | Infineon Technologies Ag | Ausffüllen von Substratvertiefungen mit siliziumoxidhaltigem Material durch eine HDP-Gasphasenabscheidung unter Beteiligung von H¶2¶O¶2¶ oder H¶2¶O als Reaktionsgas |

| US6613649B2 (en) * | 2001-12-05 | 2003-09-02 | Chartered Semiconductor Manufacturing Ltd | Method for buffer STI scheme with a hard mask layer as an oxidation barrier |

| JP4258159B2 (ja) * | 2002-03-07 | 2009-04-30 | セイコーエプソン株式会社 | 半導体装置の製造方法 |

| KR100474591B1 (ko) * | 2002-04-23 | 2005-03-08 | 주식회사 하이닉스반도체 | 트렌치 분리 구조를 가지는 디램 셀 트랜지스터의 제조 방법 |

| US6656817B2 (en) * | 2002-04-30 | 2003-12-02 | International Business Machines Corporation | Method of filling isolation trenches in a substrate |

| JP2004111429A (ja) * | 2002-09-13 | 2004-04-08 | Renesas Technology Corp | 半導体装置 |

| TWI224821B (en) * | 2003-04-11 | 2004-12-01 | Mosel Vitelic Inc | Bottom oxide formation process for preventing formation of voids in the trench |

-

2004

- 2004-04-30 US US10/836,150 patent/US6979627B2/en not_active Expired - Lifetime

-

2005

- 2005-04-05 JP JP2007510752A patent/JP4987696B2/ja not_active Expired - Fee Related

- 2005-04-05 WO PCT/US2005/011553 patent/WO2005112124A2/en not_active Ceased

- 2005-04-05 CN CNB2005800134999A patent/CN100524814C/zh not_active Expired - Fee Related

- 2005-04-05 KR KR1020067022633A patent/KR20070007870A/ko not_active Withdrawn

- 2005-04-22 TW TW094112923A patent/TWI379340B/zh not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US20050242403A1 (en) | 2005-11-03 |

| WO2005112124A3 (en) | 2006-01-12 |

| WO2005112124A2 (en) | 2005-11-24 |

| CN100524814C (zh) | 2009-08-05 |

| JP2007535815A (ja) | 2007-12-06 |

| KR20070007870A (ko) | 2007-01-16 |

| TW200605157A (en) | 2006-02-01 |

| TWI379340B (en) | 2012-12-11 |

| US6979627B2 (en) | 2005-12-27 |

| CN1947260A (zh) | 2007-04-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4987696B2 (ja) | 分離トレンチ | |

| CN100334708C (zh) | 半导体器件的制造方法 | |

| US7803684B2 (en) | Method of fabricating semiconductor device having a junction extended by a selective epitaxial growth (SEG) layer | |

| US6737706B2 (en) | Silicon on insulator device having trench isolation layer and method for manufacturing the same | |

| US8115252B2 (en) | Elimination of gate oxide weak spot in deep trench | |

| US6828210B2 (en) | Method of forming a device isolation trench in an integrated circuit device | |

| US20020127818A1 (en) | Recess-free trench isolation structure and method of forming the same | |

| US20080003773A1 (en) | Method for forming isolation structure of semiconductor device | |

| KR101608902B1 (ko) | 소자 분리 구조물을 갖는 반도체 소자 | |

| US7033907B2 (en) | Method for forming isolation layer of semiconductor device | |

| KR100966957B1 (ko) | 플래시 메모리 소자 및 그 제조 방법 | |

| KR100766232B1 (ko) | 비휘발성 메모리 소자 및 그 제조 방법 | |

| US6893940B2 (en) | Method of manufacturing semiconductor device | |

| US7956417B2 (en) | Method of reducing stacking faults through annealing | |

| US6900112B2 (en) | Process for forming shallow trench isolation region with corner protection layer | |

| US20080206957A1 (en) | Method of Forming Isolation Layer of Semiconductor Memory Device | |

| KR20070000758A (ko) | 수직 채널을 갖는 전계 효과 트랜지스터의 제조방법 | |

| JP3397693B2 (ja) | 半導体装置とその製造方法 | |

| US7563654B2 (en) | Method of manufacturing semiconductor device for formation of pin transistor | |

| US6200880B1 (en) | Method for forming shallow trench isolation | |

| KR100624330B1 (ko) | 소자분리 구조 형성 방법 | |

| KR100539005B1 (ko) | 반도체 소자의 제조 방법 | |

| KR20070001740A (ko) | 반도체소자의 트랜치 소자분리막 형성방법 | |

| KR20070032473A (ko) | 반도체 소자의 제조방법 | |

| KR20030006425A (ko) | 반도체장치의 소자격리영역 및 그의 형성방법 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080407 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080407 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111125 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111206 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120306 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120403 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120425 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150511 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |