JP4928748B2 - 半導体装置およびその製造方法 - Google Patents

半導体装置およびその製造方法 Download PDFInfo

- Publication number

- JP4928748B2 JP4928748B2 JP2005186967A JP2005186967A JP4928748B2 JP 4928748 B2 JP4928748 B2 JP 4928748B2 JP 2005186967 A JP2005186967 A JP 2005186967A JP 2005186967 A JP2005186967 A JP 2005186967A JP 4928748 B2 JP4928748 B2 JP 4928748B2

- Authority

- JP

- Japan

- Prior art keywords

- insulating film

- electrode

- film

- opening

- capacitive

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active

Links

- 239000004065 semiconductor Substances 0.000 title claims description 45

- 238000004519 manufacturing process Methods 0.000 title claims description 37

- 239000003990 capacitor Substances 0.000 claims description 121

- 229910052782 aluminium Inorganic materials 0.000 claims description 34

- XAGFODPZIPBFFR-UHFFFAOYSA-N aluminium Chemical compound [Al] XAGFODPZIPBFFR-UHFFFAOYSA-N 0.000 claims description 34

- 238000000034 method Methods 0.000 claims description 32

- 238000000059 patterning Methods 0.000 claims description 21

- 238000005530 etching Methods 0.000 claims description 20

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 claims description 14

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 14

- 239000004020 conductor Substances 0.000 claims description 13

- 239000000758 substrate Substances 0.000 claims description 12

- 229910052581 Si3N4 Inorganic materials 0.000 claims description 6

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 claims description 6

- WFKWXMTUELFFGS-UHFFFAOYSA-N tungsten Chemical compound [W] WFKWXMTUELFFGS-UHFFFAOYSA-N 0.000 claims description 6

- 229910052721 tungsten Inorganic materials 0.000 claims description 6

- 239000010937 tungsten Substances 0.000 claims description 6

- 229910052735 hafnium Inorganic materials 0.000 claims description 4

- VBJZVLUMGGDVMO-UHFFFAOYSA-N hafnium atom Chemical compound [Hf] VBJZVLUMGGDVMO-UHFFFAOYSA-N 0.000 claims description 4

- 229910052715 tantalum Inorganic materials 0.000 claims description 4

- GUVRBAGPIYLISA-UHFFFAOYSA-N tantalum atom Chemical compound [Ta] GUVRBAGPIYLISA-UHFFFAOYSA-N 0.000 claims description 4

- PNEYBMLMFCGWSK-UHFFFAOYSA-N aluminium oxide Inorganic materials [O-2].[O-2].[O-2].[Al+3].[Al+3] PNEYBMLMFCGWSK-UHFFFAOYSA-N 0.000 claims 1

- NRTOMJZYCJJWKI-UHFFFAOYSA-N Titanium nitride Chemical compound [Ti]#N NRTOMJZYCJJWKI-UHFFFAOYSA-N 0.000 description 90

- 230000003071 parasitic effect Effects 0.000 description 39

- 230000015572 biosynthetic process Effects 0.000 description 26

- 239000010410 layer Substances 0.000 description 17

- 229910052751 metal Inorganic materials 0.000 description 12

- 239000002184 metal Substances 0.000 description 12

- 238000005229 chemical vapour deposition Methods 0.000 description 10

- 238000011161 development Methods 0.000 description 10

- 238000012545 processing Methods 0.000 description 10

- 238000010586 diagram Methods 0.000 description 9

- 230000015556 catabolic process Effects 0.000 description 8

- 238000004544 sputter deposition Methods 0.000 description 8

- 238000000206 photolithography Methods 0.000 description 7

- 230000005540 biological transmission Effects 0.000 description 6

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 6

- 229920005591 polysilicon Polymers 0.000 description 6

- 239000011229 interlayer Substances 0.000 description 5

- 230000008569 process Effects 0.000 description 4

- TWNQGVIAIRXVLR-UHFFFAOYSA-N oxo(oxoalumanyloxy)alumane Chemical compound O=[Al]O[Al]=O TWNQGVIAIRXVLR-UHFFFAOYSA-N 0.000 description 3

- 238000005498 polishing Methods 0.000 description 3

- 230000009467 reduction Effects 0.000 description 3

- 239000002356 single layer Substances 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000000694 effects Effects 0.000 description 2

- 239000012212 insulator Substances 0.000 description 2

- 238000012986 modification Methods 0.000 description 2

- 230000004048 modification Effects 0.000 description 2

- 238000005268 plasma chemical vapour deposition Methods 0.000 description 2

- 229910052710 silicon Inorganic materials 0.000 description 2

- 239000010703 silicon Substances 0.000 description 2

- RTAQQCXQSZGOHL-UHFFFAOYSA-N Titanium Chemical compound [Ti] RTAQQCXQSZGOHL-UHFFFAOYSA-N 0.000 description 1

- 238000013459 approach Methods 0.000 description 1

- 230000008901 benefit Effects 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 239000000470 constituent Substances 0.000 description 1

- 239000013078 crystal Substances 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000005669 field effect Effects 0.000 description 1

- 239000000463 material Substances 0.000 description 1

- 239000003870 refractory metal Substances 0.000 description 1

- 230000003252 repetitive effect Effects 0.000 description 1

- 238000007790 scraping Methods 0.000 description 1

- 239000000126 substance Substances 0.000 description 1

- 239000010936 titanium Substances 0.000 description 1

- 229910052719 titanium Inorganic materials 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/01—Manufacture or treatment

- H10D1/041—Manufacture or treatment of capacitors having no potential barriers

- H10D1/042—Manufacture or treatment of capacitors having no potential barriers using deposition processes to form electrode extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/711—Electrodes having non-planar surfaces, e.g. formed by texturisation

- H10D1/714—Electrodes having non-planar surfaces, e.g. formed by texturisation having horizontal extensions

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10D—INORGANIC ELECTRIC SEMICONDUCTOR DEVICES

- H10D1/00—Resistors, capacitors or inductors

- H10D1/60—Capacitors

- H10D1/68—Capacitors having no potential barriers

- H10D1/692—Electrodes

- H10D1/711—Electrodes having non-planar surfaces, e.g. formed by texturisation

- H10D1/716—Electrodes having non-planar surfaces, e.g. formed by texturisation having vertical extensions

Landscapes

- Engineering & Computer Science (AREA)

- Manufacturing & Machinery (AREA)

- Semiconductor Integrated Circuits (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Inductance-Capacitance Distribution Constants And Capacitance-Resistance Oscillators (AREA)

Description

図1は、本実施の形態1における半導体装置の一部を示した断面図である。図1に示すように、シリコン単結晶よりなる半導体基板1には、nチャネル型MISFET(Metal Insulator Semiconductor Field Effect Transistor)2およびpチャネル型MISFET3が形成されている。また、nチャネル型MISFET2およびpチャネル型MISFET3の形成領域とは別の領域には、MIM構造を有する容量素子4が形成されている。すなわち、半導体基板1上には、MISFETや容量素子などが形成されている。以下の図面においては、半導体基板1に形成されているMISFETの図示は省略し、層間絶縁膜上に形成された容量素子だけを図示するものとする。

前記実施の形態1では、中間配線39が上層の配線に接続される例について説明したが、本実施の形態2では、中間配線39が上層の配線だけでなく下層の配線にも接続される製造方法について、図面を参照しながら説明する。

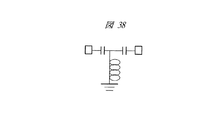

本実施の形態3では、積層構造で可変容量を形成する例について説明する。図22は、本実施の形態3における容量素子を示した平面図である。図22において、下部電極10が形成されており、この下部電極10上には絶縁膜(図示せず)を介して中間電極11が形成されている。この下部電極10と中間電極11が平面上で重なり合う領域に容量素子Caが形成されている。さらに、中間電極11上には、絶縁膜(図示せず)を介して上部電極12a〜12cおよび配線13が形成されている。中間電極11と上部電極12aが平面的に重なり合う領域には、容量素子Cbが形成されており、中間電極11と上部電極12bが平面的に重なり合う領域には、容量素子Ccが形成されている。さらに、中間電極11と上部電極12cが平面的に重なり合う領域には、容量素子Cdが形成されている。このように本実施の形態3では、容量素子Ca上に容量素子Cb、Cc、Cdが形成された構造をしている。上部電極12a〜12cは、例えばプラグ14を介して下部電極10に接続されており、中間電極11は、例えばプラグ15を介して配線13に接続されている。したがって、容量素子Ca、Cb、Cc、Cdは、互いに並列接続されている。このときの回路図を図24に示す。図24に示すように、容量素子Ca、Cb、Cc、Cdは、並列接続されており、それぞれの容量素子にはスイッチが設けられている。これにより、可変容量素子を形成することができる。例えば、容量素子Caに接続されているスイッチだけをオンにすると、可変容量素子の容量は容量素子Caの容量になる。また、容量素子Caのスイッチと容量素子Cbのスイッチをオンにすると、可変容量素子の容量は、容量素子Caの容量と容量素子Cbの容量との和になる。このようにスイッチを適宜選択することにより、所望の容量を得ることができる。本実施の形態3によれば、積層化された複数の容量素子とスイッチを組み合わせることで、容量素子の占有面積を低減させながら柔軟度の高い可変容量素子を形成することができる。

本実施の形態4は、開口部の側壁にサイドウォールを形成した容量素子について説明する。図25は、図3に示す容量素子の開口部19a付近を拡大した断面図である。図25において、アルミニウム膜17b上には窒化チタン膜17cが形成されており、この窒化チタン膜17c上に絶縁膜19が形成されている。そして、絶縁膜19には、開口部19aが形成されており、この開口部19aの底面および側面には容量絶縁膜18が形成されている。なお、図示はされていないが、容量絶縁膜18上には上部電極12が形成されている。

本実施の形態5では、3つの容量素子を積層した構造の容量素子について説明する。図34は、本実施の形態5における容量素子を示した断面図である。図34において、2つの容量素子(第1容量素子および第2容量素子)が積層されている下部電極32から上部電極52までの構造は、前記実施の形態1と同様である。本実施の形態5では、上部電極52上に絶縁膜70が形成されており、この絶縁膜70に開口部71が形成されている。開口部71内を含む絶縁膜70上には、容量絶縁膜72、窒化チタン膜73および最上部電極75が形成されている。最上部電極75は、例えば窒化チタン膜74a、アルミニウム膜74bおよび窒化チタン膜74cの積層膜から構成されている。

本実施の形態6では、2つの容量素子を積層した構造の容量素子と、積層構造を有さない容量素子とを設ける例について説明する。図35は、本実施の形態6における容量素子を示した断面図である。図35に示すように、本実施の形態6における容量素子は、2つの容量素子を積層した構造の容量素子76と単層構造の容量素子(第4容量素子)77が設けられている。容量素子76は、前記実施の形態1で説明した容量素子と同様である。

この容量素子76と容量素子77は、互いに並列接続されており、容量素子77をオン/オフするスイッチが設けられている。このように構成することで、容量の微調整が可能となる。すなわち、容量素子76は積層構造をしているので大きな容量をしている。一方、容量素子77は単層構造をしているので小さな容量をしている。ここで、容量素子77に接続されたスイッチをオンすることで、容量素子76だけの容量から容量素子77の容量だけ増加させることができる。回路の特性などの関係から容量素子76の容量からわずかに容量を増加させたい場合には、低容量の容量素子77に接続されたスイッチをオンさせることで対応できる。このように本実施の形態6によれば、積層構造をした容量素子76と単層構造をした容量素子77を組み合わせることにより、容量の微調整が可能となる。

本実施の形態7では、前記実施の形態1〜6で説明した容量素子を使用する電子装置について説明する。電子装置の一例として携帯電話機を説明する。図36は、携帯電話機における送受信部の構成を示したブロック図である。図36に示すように、送受信部80は、アンテナ81、アンテナスイッチ82、RF(Radio Frequency)フィルタ83、RF−IC(送受信装置)84、ベースバンド部85およびPAモジュール86を有している。さらに、RF−IC84は、LNA(Low Noise Amplifier)87、PGA88、TXVCO(電圧制御発振器)89、RFVCO90、IFVCO91、DC/VCXO92などから構成されている。

RF−IC84で生成されたRF信号は、PAモジュール86で増幅される。そして、アンテナスイッチ82を介してアンテナ81からRF信号が送信される。このようにして電波を送信することができる。

2 nチャネル型MISFET

3 pチャネル型MISFET

4 容量素子

10 下部電極

11 中間電極

12 上部電極

13 配線

14 プラグ

15 プラグ

16 絶縁膜

17a 窒化チタン膜

17b アルミニウム膜

17c 窒化チタン膜

18 容量絶縁膜

19 絶縁膜

19a 開口部

20a 窒化チタン膜

20b アルミニウム膜

20c 窒化チタン膜

21 容量絶縁膜

22 絶縁膜

22a 開口部

23 窒化チタン膜

24a 窒化チタン膜

24b アルミニウム膜

24c 窒化チタン膜

30 絶縁膜

31a 窒化チタン膜

31b アルミニウム膜

31c 窒化チタン膜

32 下部電極

33 絶縁膜

34 レジスト膜

35 開口部

36 容量絶縁膜

37a 窒化チタン膜

37b アルミニウム膜

37c 窒化チタン膜

38 レジスト膜

39 中間電極

40 絶縁膜

41 レジスト膜

42 接続孔

43 接続孔

44 プラグ

45 プラグ

46 レジスト膜

47 開口部

48 容量絶縁膜

49 窒化チタン膜

50 レジスト膜

51a 窒化チタン膜

51b アルミニウム膜

51c 窒化チタン膜

52 上部電極

53 下層配線

54 プラグ

55 プラグ

56 レジスト膜

57 レジスト膜

58 配線

59 接続孔

60 プラグ

61 プラグ

66 絶縁膜

67 サイドウォール

68 サイドウォール

70 絶縁膜

71 開口部

72 容量絶縁膜

73 窒化チタン膜

74a 窒化チタン膜

74b アルミニウム膜

74c 窒化チタン膜

75 最上部電極

76 容量素子

77 容量素子

80 送受信部

81 アンテナ

82 アンテナスイッチ

83 RFフィルタ

84 RF−IC

85 ベースバンド部

86 PAモジュール

87 LNA

88 PGA

89 TXVCO

90 RFVCO

91 IFVCO

92 DC/VCXO

100 下部電極

101 容量絶縁膜

102 中間電極

103 容量絶縁膜

104 上部電極

C1 容量素子

C2 容量素子

Ca〜Cd 容量素子

Claims (18)

- 第1電極と、

前記第1電極上に形成された第1絶縁膜と、

前記第1絶縁膜に形成され、且つ、前記第1電極が露出するように形成された第1開口部と、

前記第1開口部の側壁に形成され、且つ、第3絶縁膜からなる第1サイドウォールと、

前記第1絶縁膜上に形成され、且つ、前記第1開口部内にて前記第1サイドウォールを覆うように前記第1電極上に形成された第1容量絶縁膜と、

前記第1容量絶縁膜上に形成された第2電極と、

前記第2電極上に形成された第2絶縁膜と、

前記第2絶縁膜に形成され、且つ、前記第2電極が露出するように形成された第2開口部と、

前記第2開口部の側壁に形成され、且つ、第4絶縁膜からなる第2サイドウォールと、

前記第2絶縁膜上に形成され、且つ、前記第2開口部内にて前記第2サイドウォールを覆うように前記第2電極上に形成された第2容量絶縁膜と、

前記第2容量絶縁膜上に形成された第3電極と、を備えることを特徴とする半導体装置。 - 請求項1において、

前記第1容量絶縁膜と前記第1電極の接触面積は、前記第2容量絶縁膜と前記第2電極の接触面積よりも大きいことを特徴とする半導体装置。 - 請求項1または2において、

前記第2電極は、信号配線あるいは電源配線に使用されることを特徴とする半導体装置。 - 請求項1〜3の何れか1項において、

前記第1電極と前記第3電極とは、電気的に接続されていることを特徴とする半導体装置。 - 請求項4において、

前記第1電極、前記第1容量絶縁膜および前記第2電極からなる第1容量素子と、前記第2電極、前記第2容量絶縁膜および前記第3電極からなる第2容量素子は、並列接続されていることを特徴とする半導体装置。 - 請求項1〜5の何れか1項において、

前記第1電極、前記第2電極および前記第3電極は、アルミニウム膜あるいはタングステン膜から形成されていることを特徴とする半導体装置。 - 請求項1〜6の何れか1項において、

前記第1容量絶縁膜および前記第2容量絶縁膜は、酸化シリコン膜、窒化シリコン膜、アルミナ膜、タンタルあるいはハフニウムの酸化物を含む膜のいずれかより形成されていることを特徴とする半導体装置。 - 請求項1〜7の何れか1項において、

前記第1開口部内において、前記第1サイドウォールを介して前記第1開口部の側壁に形成されている前記第1容量絶縁膜の膜厚は、前記第1電極上に形成されている前記第1容量絶縁膜の膜厚よりも薄いことを特徴とする半導体装置。 - 請求項1〜8の何れか1項において、

前記第2開口部内において、前記第2サイドウォールを介して前記第2開口部の側壁に形成されている前記第2容量絶縁膜の膜厚は、前記第2電極上に形成されている前記第2容量絶縁膜の膜厚よりも薄いことを特徴とする半導体装置。 - 請求項1〜9の何れか1項において、

前記第1開口部内において、前記第1容量絶縁膜は、前記第1電極および前記第1サイドウォールと直接接していることを特徴とする半導体装置。 - 請求項1〜10の何れか1項において、

前記第2開口部内において、前記第2容量絶縁膜は、前記第2電極および前記第2サイドウォールと直接接していることを特徴とする半導体装置。 - (a)半導体基板上に第1電極を形成する工程と、

(b)前記第1電極上に第1絶縁膜を形成する工程と、

(c)前記第1絶縁膜に前記第1電極に達する第1開口部を形成する工程と、

(d)前記第1開口部の側壁に、第3絶縁膜からなる第1サイドウォールを形成する工程と、

(e)前記第1絶縁膜上に第1容量絶縁膜を形成する工程であって、前記第1開口部内にて前記第1サイドウォールを覆うように前記第1電極上に前記第1容量絶縁膜を形成する工程と、

(f)前記第1開口部内を含む前記第1容量絶縁膜上に第1導体膜を形成する工程と、

(g)前記第1導体膜をパターニングして第2電極を形成する工程と、

(h)前記第2電極上に第2絶縁膜を形成する工程と、

(i)前記第2絶縁膜に前記第2電極に達する第2開口部を形成する工程と、

(j)前記第2開口部の側壁に、第4絶縁膜からなる第2サイドウォールを形成する工程と、

(k)前記第2絶縁膜上に第2容量絶縁膜を形成する工程であって、前記第2開口部内にて前記第2サイドウォールを覆うように前記第2電極上に前記第2容量絶縁膜を形成する工程と、

(l)前記第2開口部内を含む前記第2容量絶縁膜上に第2導体膜を形成する工程と、

(m)前記第2導体膜をパターニングして第3電極を形成する工程と、を備えることを特徴とする半導体装置の製造方法。 - 請求項12において、

前記第1開口部内において、前記第1サイドウォールを介して前記第1開口部の側壁に形成されている前記第1容量絶縁膜の膜厚は、前記第1電極上に形成されている前記第1容量絶縁膜の膜厚よりも薄いことを特徴とする半導体装置の製造方法。 - 請求項12または13において、

前記第2開口部内において、前記第2サイドウォールを介して前記第2開口部の側壁に形成されている前記第2容量絶縁膜の膜厚は、前記第2電極上に形成されている前記第2容量絶縁膜の膜厚よりも薄いことを特徴とする半導体装置の製造方法。 - 請求項12〜14の何れか1項において、

前記第1開口部内において、前記第1容量絶縁膜は、前記第1電極および前記第1サイドウォールと直接接していることを特徴とする半導体装置の製造方法。 - 請求項12〜15の何れか1項において、

前記第2開口部内において、前記第2容量絶縁膜は、前記第2電極および前記第2サイドウォールと直接接していることを特徴とする半導体装置の製造方法。 - 請求項12〜16の何れか1項において、

前記(d)工程は、

(d1)前記第1絶縁膜上、及び、前記第1開口部にて前記第1電極上に前記第3絶縁膜を形成する工程と、

(d2)前記第3絶縁膜を異方性エッチングすることにより、前記第1開口部の側壁に前記第3絶縁膜を残すことで、前記第1サイドウォールを形成する工程と、を有することを特徴とする半導体装置の製造方法。 - 請求項12〜17の何れか1項において、

前記(j)工程は、

(j1)前記第2絶縁膜上、及び、前記第2開口部にて前記第2電極上に前記第4絶縁膜を形成する工程と、

(j2)前記第4絶縁膜を異方性エッチングすることにより、前記第2開口部の側壁に前記第4絶縁膜を残すことで、前記第2サイドウォールを形成する工程と、を有することを特徴とする半導体装置の製造方法。

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005186967A JP4928748B2 (ja) | 2005-06-27 | 2005-06-27 | 半導体装置およびその製造方法 |

| US11/473,229 US20060289917A1 (en) | 2005-06-27 | 2006-06-23 | Semiconductor device, RF-IC and manufacturing method of the same |

| CNA2006100935372A CN1893067A (zh) | 2005-06-27 | 2006-06-26 | 半导体器件、rf-ic及其制造方法 |

| US12/565,963 US20100013568A1 (en) | 2005-06-27 | 2009-09-24 | Semiconductor device, rf-ic and manufacturing method of the same |

| US12/873,668 US8183616B2 (en) | 2005-06-27 | 2010-09-01 | Semiconductor device, RF-IC and manufacturing method of the same |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005186967A JP4928748B2 (ja) | 2005-06-27 | 2005-06-27 | 半導体装置およびその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2007005719A JP2007005719A (ja) | 2007-01-11 |

| JP4928748B2 true JP4928748B2 (ja) | 2012-05-09 |

Family

ID=37566316

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005186967A Active JP4928748B2 (ja) | 2005-06-27 | 2005-06-27 | 半導体装置およびその製造方法 |

Country Status (3)

| Country | Link |

|---|---|

| US (3) | US20060289917A1 (ja) |

| JP (1) | JP4928748B2 (ja) |

| CN (1) | CN1893067A (ja) |

Families Citing this family (12)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2008016490A (ja) * | 2006-07-03 | 2008-01-24 | Nec Electronics Corp | 半導体装置 |

| JP5135827B2 (ja) * | 2007-02-27 | 2013-02-06 | 株式会社日立製作所 | 半導体装置及びその製造方法 |

| WO2008114418A1 (ja) | 2007-03-20 | 2008-09-25 | Fujitsu Microelectronics Limited | 半導体装置及びその製造方法 |

| JP5194549B2 (ja) * | 2007-04-27 | 2013-05-08 | 富士通セミコンダクター株式会社 | 半導体装置の製造方法 |

| JP2010003742A (ja) * | 2008-06-18 | 2010-01-07 | Fujitsu Microelectronics Ltd | 半導体装置、及び薄膜キャパシタの製造方法 |

| JP2010135453A (ja) * | 2008-12-03 | 2010-06-17 | Renesas Electronics Corp | 半導体装置、半導体装置の製造方法 |

| JP2010140972A (ja) | 2008-12-09 | 2010-06-24 | Renesas Electronics Corp | 半導体装置 |

| CN102449846B (zh) * | 2009-06-03 | 2015-02-04 | 株式会社村田制作所 | 无线ic器件及其制造方法 |

| US8854865B2 (en) * | 2010-11-24 | 2014-10-07 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor memory device |

| JP2016162904A (ja) * | 2015-03-03 | 2016-09-05 | ルネサスエレクトロニクス株式会社 | 半導体装置の製造方法 |

| CN116325121A (zh) * | 2020-11-10 | 2023-06-23 | 松下知识产权经营株式会社 | 半导体装置及摄像装置 |

| US11894297B2 (en) * | 2021-07-29 | 2024-02-06 | Taiwan Semiconductor Manufacturing Company, Ltd. | Metal-insulator-metal capacitor having electrodes with increasing thickness |

Family Cites Families (28)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5745335A (en) * | 1996-06-27 | 1998-04-28 | Gennum Corporation | Multi-layer film capacitor structures and method |

| JP3749776B2 (ja) * | 1997-02-28 | 2006-03-01 | 株式会社東芝 | 半導体装置 |

| SE520173C2 (sv) * | 1997-04-29 | 2003-06-03 | Ericsson Telefon Ab L M | Förfarande för tillverkning av en kondensator i en integrerad krets |

| TW386289B (en) * | 1997-07-03 | 2000-04-01 | Matsushita Electronics Corp | Capacitance element and manufacturing thereof |

| JP3199004B2 (ja) * | 1997-11-10 | 2001-08-13 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US6911371B2 (en) * | 1997-12-19 | 2005-06-28 | Micron Technology, Inc. | Capacitor forming methods with barrier layers to threshold voltage shift inducing material |

| JP3516593B2 (ja) * | 1998-09-22 | 2004-04-05 | シャープ株式会社 | 半導体装置及びその製造方法 |

| JP2001102529A (ja) * | 1999-09-28 | 2001-04-13 | Hitachi Ltd | Mim構造の容量素子及びそれを有する半導体集積回路装置 |

| US6411494B1 (en) * | 2000-04-06 | 2002-06-25 | Gennum Corporation | Distributed capacitor |

| DE10141877B4 (de) * | 2001-08-28 | 2007-02-08 | Infineon Technologies Ag | Halbleiterbauteil und Konvertereinrichtung |

| JP3553535B2 (ja) * | 2001-09-28 | 2004-08-11 | ユーディナデバイス株式会社 | 容量素子及びその製造方法 |

| DE10161285A1 (de) * | 2001-12-13 | 2003-07-03 | Infineon Technologies Ag | Integriertes Halbleiterprodukt mit Metall-Isolator-Metall-Kondensator |

| FR2834387B1 (fr) * | 2001-12-31 | 2004-02-27 | Memscap | Composant electronique incorporant un circuit integre et un micro-condensateur |

| JP2003218219A (ja) * | 2002-01-22 | 2003-07-31 | Nec Kansai Ltd | 半導体キャパシタおよびその製造方法 |

| US20030197215A1 (en) * | 2002-02-05 | 2003-10-23 | International Business Machines Corporation | A dual stacked metal-insulator-metal capacitor and method for making same |

| JP2003289134A (ja) * | 2002-03-28 | 2003-10-10 | Matsushita Electric Ind Co Ltd | 半導体装置及びその製造方法 |

| JP4094904B2 (ja) * | 2002-07-22 | 2008-06-04 | 三菱電機株式会社 | 半導体装置 |

| KR100482029B1 (ko) * | 2002-07-25 | 2005-04-13 | 동부아남반도체 주식회사 | 엠아이엠 캐패시터 형성방법 |

| JP2004179419A (ja) * | 2002-11-27 | 2004-06-24 | Toshiba Corp | 半導体装置及びその製造方法 |

| DE10341564B4 (de) * | 2003-09-09 | 2007-11-22 | Infineon Technologies Ag | Kondensatoranordnung und Verfahren zur Herstellung derselben |

| US20050082592A1 (en) * | 2003-10-16 | 2005-04-21 | Taiwan Semiconductor Manufacturing Co., Ltd. | Compact capacitor structure having high unit capacitance |

| US20050116276A1 (en) * | 2003-11-28 | 2005-06-02 | Jing-Horng Gau | Metal-insulator-metal (MIM) capacitor and fabrication method for making the same |

| JP2005167536A (ja) | 2003-12-02 | 2005-06-23 | Renesas Technology Corp | 通信用半導体集積回路および無線通信システム |

| KR100549223B1 (ko) * | 2003-12-24 | 2006-02-03 | 한국전자통신연구원 | 전류궤환형 전압제어발진기 |

| KR100591148B1 (ko) * | 2003-12-31 | 2006-06-19 | 동부일렉트로닉스 주식회사 | 반도체 장치의 캐패시터 및 그의 제조 방법 |

| KR100549002B1 (ko) * | 2004-02-04 | 2006-02-02 | 삼성전자주식회사 | 복층 엠아이엠 커패시터를 갖는 반도체소자 및 그것을제조하는 방법 |

| US7603098B2 (en) * | 2004-03-31 | 2009-10-13 | Broadcom Corporation | Programmable IF frequency filter for enabling a compromise between DC offset rejection and image rejection |

| EP1628327A2 (en) * | 2004-08-20 | 2006-02-22 | Matsushita Electric Industrial Co., Ltd. | Dielectric memory device and method for fabricating the same |

-

2005

- 2005-06-27 JP JP2005186967A patent/JP4928748B2/ja active Active

-

2006

- 2006-06-23 US US11/473,229 patent/US20060289917A1/en not_active Abandoned

- 2006-06-26 CN CNA2006100935372A patent/CN1893067A/zh active Pending

-

2009

- 2009-09-24 US US12/565,963 patent/US20100013568A1/en not_active Abandoned

-

2010

- 2010-09-01 US US12/873,668 patent/US8183616B2/en active Active

Also Published As

| Publication number | Publication date |

|---|---|

| JP2007005719A (ja) | 2007-01-11 |

| US20100320568A1 (en) | 2010-12-23 |

| US20100013568A1 (en) | 2010-01-21 |

| US8183616B2 (en) | 2012-05-22 |

| CN1893067A (zh) | 2007-01-10 |

| US20060289917A1 (en) | 2006-12-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8183616B2 (en) | Semiconductor device, RF-IC and manufacturing method of the same | |

| US8610248B2 (en) | Capacitor structure and method of manufacture | |

| US7884409B2 (en) | Semiconductor device and method of fabricating the same | |

| US6891218B2 (en) | Semiconductor device and method of manufacturing same | |

| JP6224737B2 (ja) | キャパシタンスを高めた金属−酸化物−金属(mom)キャパシタ | |

| US10797057B2 (en) | DRAM semiconductor device having reduced parasitic capacitance between capacitor contacts and bit line structures and method for manufacturing the same | |

| US9871095B2 (en) | Stacked capacitor with enhanced capacitance and method of manufacturing the same | |

| US6999298B2 (en) | MIM multilayer capacitor | |

| CN113130490A (zh) | 具有铁电随机存取存储器和可调电容器的片上系统 | |

| US7579643B2 (en) | Capacitor having high electrostatic capacity, integrated circuit device including the capacitor and method of fabricating the same | |

| KR100698089B1 (ko) | 커패시터를 갖는 반도체 소자 및 이의 제조방법 | |

| US20090057828A1 (en) | Metal-insulator-metal capacitor and method for manufacturing the same | |

| CN101383347A (zh) | 具有mim电容器的半导体器件及其制造方法 | |

| KR20150028881A (ko) | 캐패시터를 포함하는 반도체 소자 및 그 제조 방법 | |

| JP4837943B2 (ja) | 半導体装置およびその製造方法 | |

| US11688683B2 (en) | Semiconductor structure and manufacturing method thereof | |

| US11245000B1 (en) | Metal-insulator-metal capacitor | |

| JP2005072233A (ja) | 半導体装置 | |

| JP2010040775A (ja) | 半導体装置及びその製造方法 | |

| JP2007311785A (ja) | Mimキャパシタを含む半導体集積回路素子およびその製造方法 | |

| CN116581086A (zh) | 在后段结构中集成mim电容的方法 | |

| JP2005079523A (ja) | 半導体装置およびその製造方法 | |

| KR20060017023A (ko) | 고 커패시턴스를 지니는 금속-절연체-금속 커패시터 및 그제조방법 | |

| KR100508860B1 (ko) | 박막 커패시터 및 그 제조 방법 | |

| CN118511273A (zh) | 金属-绝缘体-金属(mim)电容器模块 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20080617 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100528 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20111003 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111025 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111222 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120117 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120213 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150217 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4928748 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |