JP4748841B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4748841B2 JP4748841B2 JP2000323797A JP2000323797A JP4748841B2 JP 4748841 B2 JP4748841 B2 JP 4748841B2 JP 2000323797 A JP2000323797 A JP 2000323797A JP 2000323797 A JP2000323797 A JP 2000323797A JP 4748841 B2 JP4748841 B2 JP 4748841B2

- Authority

- JP

- Japan

- Prior art keywords

- power supply

- channel mos

- mos transistor

- supply potential

- circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F1/00—Automatic systems in which deviations of an electric quantity from one or more predetermined values are detected at the output of the system and fed back to a device within the system to restore the detected quantity to its predetermined value or values, i.e. retroactive systems

- G05F1/10—Regulating voltage or current

- G05F1/46—Regulating voltage or current wherein the variable actually regulated by the final control device is DC

- G05F1/462—Regulating voltage or current wherein the variable actually regulated by the final control device is DC as a function of the requirements of the load, e.g. delay, temperature, specific voltage/current characteristic

- G05F1/465—Internal voltage generators for integrated circuits, e.g. step down generators

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- General Physics & Mathematics (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Dram (AREA)

- Semiconductor Integrated Circuits (AREA)

Description

【発明の属する技術分野】

この発明は、半導体装置に関し、より特定的には、複数の電源電位をそれぞれ用いる複数の内部回路を含む半導体装置に関する。

【0002】

【従来の技術】

複数の外部電源電位を受ける半導体装置において、電源投入時にその投入の順序によっては、多大な貫通電流が流れてしまう場合がある。たとえば、第1の外部電源電位と第2の外部電源電位とを受ける場合において第1の外部電源電位が第2の外部電源電位よりも高い場合に、半導体装置に含まれる第2の外部電源電位から第1の外部電源電位へのレベル変換を行なうレベル変換回路などこの貫通電流が流れる回路である。

【0003】

すなわち、第2の外部電源電位を先に印加し、その後、第1の外部電源電位を印加するのであれば、貫通電流は流れない。しかし、逆の順序で外部電源電位を印加すると貫通電流が流れてしまう。

【0004】

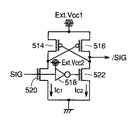

このレベル変換回路における貫通電流について図を用いて説明する。

図21は、本明細書において用いる記号を説明するための図である。

【0005】

図21を参照して、PチャネルMOSトランジスタ502,NチャネルMOSトランジスタ504,インバータ506は、第2の外部電源電位である電源電位Ext.Vcc2を電源電位として用いる回路において使用されるゲート酸化膜が薄いタイプのMOSトランジスタで構成される回路要素である。

【0006】

一方、PチャネルMOSトランジスタ508,NチャネルMOSトランジスタ510,インバータ512は、第2の内部電源電位よりも高い第1の外部電源電位である電源電位Ext.Vcc1を電源電位とする回路において用いられるゲート酸化膜の厚いMOSトランジスタで構成された回路要素である。ゲート酸化膜を厚くすることにより、より高い電圧を印加することができる。

【0007】

図22は、低振幅から高振幅に変換する、従来の第1のレベル変換回路の構成を示した回路図である。

【0008】

図21、図22を参照して、このレベル変換回路は、信号SIGを受けて反転するインバータ518と、ゲートに信号SIGを受けソースが接地ノードに接続されるNチャネルMOSトランジスタ520と、インバータ518の出力を受けソースが接地ノードに接続されるNチャネルMOSトランジスタ522と、電源電位Ext.Vcc1を受けるノードとNチャネルMOSトランジスタ520のドレインとの間に接続されゲートにNチャネルMOSトランジスタ522のドレインが接続されるPチャネルMOSトランジスタ514と、電源電位Ext.Vcc1を受けるノードとNチャネルMOSトランジスタ522のドレインとの間に接続されゲートがNチャネルMOSトランジスタ520のドレインと接続されるPチャネルMOSトランジスタ516とを含む。

【0009】

NチャネルMOSトランジスタ522のドレインからは0Vから外部電源電位Ext.Vcc2との間で振幅する信号SIGが反転されレベル変換され0Vから電源電位Ext.Vcc1の間で振幅する信号/SIGが出力される。

【0010】

インバータ518は電源電位Ext.Vcc2を電源電位として受ける。したがって、インバータ518は、ゲート酸化膜が薄い、いわゆる薄膜トランジスタで構成されている。他のトランジスタ514,516,520,522は、ゲート酸化膜が厚い、いわゆる厚膜トランジスタである。

【0011】

このようなレベル変換回路において、外部から電源電位Ext.Vcc1が印加され、かつ、電源電位Ext.Vcc2がまだ印加されていない場合には、貫通電流が流れる。すなわち、信号SIGがNチャネルMOSトランジスタ520のしきい値電圧付近またはそれ以上の中間電位にある場合には、NチャネルMOSトランジスタ520に貫通電流Ic1が流れる。また、電源電位Ext.Vcc1が印加されており、電源電位Ext.Vcc2がまだ印加されていない場合には、インバータ518の出力が不安定な状態であるため、NチャネルMOSトランジスタ522のゲート電位がしきい値電圧付近あるいはそれ以上の中間電位にある場合には、NチャネルMOSトランジスタ522に貫通電流Ic2が流れてしまう。

【0012】

図23は、高振幅から低振幅に変換する、従来の第2のレベル変換回路の構成を示した回路図である。

【0013】

図21、図23を参照して、このレベル変換回路は、信号SIGAをゲートに受けソースが外部電源電位Ext.Vcc2に結合されるPチャネルMOSトランジスタ582と、ゲートに信号SIGAを受けPチャネルMOSトランジスタ582のドレインと接地ノードとの間に接続されるNチャネルMOSトランジスタ584とを含む。PチャネルMOSトランジスタ582のドレインからは信号/SIGAが出力される。

【0014】

信号SIGAのLレベルは0Vであり、Hレベルは電源電位Ext.Vcc1と同じである。一方出力信号/SIGAのLレベルは0Vであり、Hレベルは電源電位Ext.Vcc2である。ただし、電源電位Ext.Vcc2は、電源電位Ext.Vcc1より低い電源電位である。また、トランジスタ582、584は、Ext.Vcc1の電源電圧に耐えうるだけのゲート酸化膜厚を有するトランジスタである。このような回路構成の場合であっても、外部電源電位Ext.Vcc2の電位が十分に高い状態であっても外部電源電位Ext.Vcc1の電位がまだ与えられていない場合には、信号SIGAが中間電位すなわちNチャネルMOSトランジスタ584のしきい値電圧を超える付近でふらつくと貫通電流が流れてしまう。

【0015】

【発明が解決しようとする課題】

どのような電化製品も、基本的に電源投入時の貫通電流はただでさえ多い。このような貫通電流を少しでも削減する必要がある中で、図22で示したような電源投入時の貫通電流を増加させる構成の半導体装置は望ましくない。しかし、電源投入の順序を規定してしまうと、使用者側にとっては使いにくい半導体装置になりかねない。

【0016】

図22で示したようなレベル変換回路は、主として2つのケースで用いられる。

【0017】

1つは、図22で示したように、外部電源電位Ext.Vcc1,Ext.Vcc2が内部回路の電源電位としてそれぞれ用いられており、電源電位Ext.Vcc2よりも電源電位Ext.Vcc1が高い場合である。この場合に電源電位Ext.Vcc2を電源電位とする回路から電源電位Ext.Vcc1を電源電位とする回路に信号を与える場合である。

【0018】

このような場合には、レベル変換回路の貫通電流のパスを切断するような構成とする必要がある。

【0019】

他の1つは、外部電源電位Ext.Vcc2を電源電位とする回路からより高い内部電源電位を電源電位とする回路に対して信号を受け渡す場合のレベル変換回路である。そして、この内部電源電位が外部電源電位Ext.Vcc1から内部で発生されたものである場合である。

【0020】

この場合には、図22のレベル変換回路において電源電位Ext.Vcc1に代えて内部電源電位が与えられたレベル変換回路が用いられる。第2のケースの場合には、レベル変換回路の貫通電流のパスを切断するような構成か、または、電源電位Ext.Vcc2が十分に立上がっていない場合には、内部電源電位の発生を止めてしまうような構成が必要となる。

【0021】

本発明の目的は、複数の電源電位が内部回路において用いられる半導体装置において、貫通電流を低減させることが可能な半導体装置を提供することである。

【0022】

【課題を解決するための手段】

この発明は、半導体装置であって、第1の電源電位を受ける第1の端子と、第2の電源電位を受ける第2の端子と、第1の端子から動作電源電位を受け、第2の端子の電位を検知する検知回路と、第2の端子の電位に応じた振幅の入力信号を受け、検知回路の出力に応じて動作を行なう内部回路とを備え、内部回路は、検知回路の出力に応じて活性化し、第1の電源電位から内部電源電位を発生する内部電源回路と、内部電源回路から動作電流の供給を受け、入力信号に応じて動作する回路とを含む。

【0029】

好ましくは、検知回路は、第2の端子の電位が所定の電位に達していないときは、内部電源回路に対し、内部電源電位の発生を停止させる。

【0030】

好ましくは、内部電源回路は、内部電源電位が所定の電位に到達しているか否かを検出するレベル検出回路と、レベル検出回路の出力と検知回路の出力とに応じて活性化して発振する発振器と、発振器の出力に応じて第1の電源電位を昇圧して内部電源電位を発生するチャージポンプ回路とを有する。

【0031】

好ましくは、内部電源回路は、内部電源電位を供給する出力ノードを第1の電源電位に結合する駆動トランジスタと、検知回路の出力に応じて活性化し、出力ノードの電位を参照電位と比較して駆動トランジスタの導通状態を制御する比較回路とを有し、比較回路は、自己が非活性化時に駆動トランジスタを非導通状態とする。

【0035】

【発明の実施の形態】

以下において、本発明の実施の形態について図面を参照して詳しく説明する。

なお、図中同一符号は同一または相当部分を示す。

【0036】

[実施の形態1]

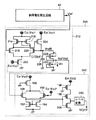

図1は、本発明の実施の形態1の半導体装置1の構成を示す概略ブロック図である。半導体装置の例として複数の電源電位を受けるダイナミックランダムアクセスメモリ(DRAM)を取上げている。

【0037】

図1を参照して、半導体装置1は、制御信号Ext./RAS,Ext./CAS,Ext./WEをそれぞれ受ける制御信号入力端子2〜6と、アドレス入力端子群8と、データ信号Dinが入力される入力端子群14と、データ信号Doutを出力する出力端子群16と、接地電位Vssが与えられる接地端子12と、電源電位Ext.Vcc1が与えられる電源端子10と、電源電位Ext.Vcc2が与えられる電源端子11を備える。

【0038】

半導体装置1は、さらに、クロック発生回路22と、行および列アドレスバッファ24と、リフレッシュアドレスカウンタ25と、行デコーダ26と、列デコーダ28と、センスアンプ+入出力制御回路30と、メモリセルアレイ32と、ゲート回路18と、データ入力バッファ20およびデータ出力バッファ34とを備える。

【0039】

クロック発生回路22は、制御信号入力端子2、4を介して外部から与えられる外部行アドレスストローブ信号Ext./RASと外部列アドレスストローブ信号Ext./CASとに基づいた所定の動作モードに相当する制御クロックを発生して半導体装置全体の動作を制御する。

【0040】

行および列アドレスバッファ24は、外部から与えられるアドレス信号A0〜Ai(iは自然数)に基づいて生成したアドレス信号を行デコーダ26および列デコーダ28に与える。

【0041】

リフレッシュアドレスカウンタ25は、クロック発生回路22によって制御されリフレッシュモードにおいて一定周期でリフレッシュアドレスを発生し、発生したアドレスを行デコーダ26に与える。

【0042】

行デコーダ26と列デコーダ28とによって指定されたメモリセルアレイ32中のメモリセルは、センスアンプ+入出力制御回路30とデータ入力バッファ20またはデータ出力バッファ34とを介して入力端子群14または出力端子群16を通じて外部とデータをやり取りする。

【0043】

半導体装置1は、さらに、電源電位Ext.Vcc1を昇圧して内部昇圧電位Vppを発生する昇圧電源回路36と、電源電位Ext.Vcc2を受けて降圧して内部電源電位int.Vccを発生する電圧降下回路38とを含む。

【0044】

各電源電位は、たとえば、電源電位Ext.Vcc1は3.3Vであり、電源電位Ext.Vcc2は1.5Vであり、内部昇圧電位Vppは3.6Vであり、内部電源電位int.Vccは2.0Vである。

【0045】

ゲート回路18、クロック発生回路22、データ入力バッファ20、行および列アドレスバッファ24、リフレッシュアドレスカウンタ25およびデータ出力バッファ34は、電源電位Ext.Vcc2を電源電位として受ける回路である。行デコーダ26は、内部昇圧電位Vppを電源電位として受け、この内部昇圧電位がワード線の活性化レベルとなる。列デコーダ28、センスアンプ+入出力制御回路30は、内部電源電位int.Vccを電源電位として受ける回路である。

【0046】

半導体装置1は、さらに、電源電位Ext.Vcc1を動作電源電位として受け電源電位Ext.Vcc2の電位を検知する電源レベル検知回路56と、異なる電源電位を動作電源電位とする回路間での信号のレベル変換を行なうレベル変換回路42〜52とを含む。レベル変換回路42は行および列アドレスバッファ24から受けた信号をレベル変換して行デコーダ26に出力する。

【0047】

レベル変換回路44は、リフレッシュアドレスカウンタ25から信号を受けてレベル変換し行デコーダ26に出力する。レベル変換回路48は、行および列アドレスバッファ24から受けた列アドレス信号をレベル変換して列デコーダ28に出力する。

【0048】

レベル変換回路46,50は、制御信号Ext./WEを受けてレベル変換してそれぞれ行デコーダ26、列デコーダ28に出力する。レベル変換回路52は、クロック発生回路22の出力する制御信号をレベル変換してセンスアンプ+入出力制御回路30に対して出力する。レベル変換回路54は、電源レベル検知回路56の出力を受けてレベル変換して列デコーダ28の出力信号線に対して出力する。

【0049】

なお、図1に示した半導体装置1は、代表的な一例であり、たとえば、同期型半導体装置(例、SDRAM)などにも本発明は適用可能である。他にも、複数の電源電位を受ける回路を含んでいる半導体装置であれば種々のものに適用可能である。

【0050】

図2は、図1に示した電源レベル検知回路56の第1の構成例を示した図である。

【0051】

図2を参照して、電源レベル検知回路56は、接地電位または電源電位Ext.Vcc2をゲートに受け電源電位Ext.Vcc1が与えられるノードとノードNBとの間に接続されるゲート長Lが大きいPチャネルMOSトランジスタ62と、ノードNBと接地ノードとの間に接続されゲートに電源電位Ext.Vcc2を受けるNチャネルMOSトランジスタ64と、ノードNBにゲートが接続されノードNCと接地ノードとの間に接続されるNチャネルMOSトランジスタ66と、ノードNCが入力に接続されるインバータ68と、インバータ68の出力を受けて反転しノードNCに帰還させるインバータ70と、インバータ68の出力と接地ノードとの間に接続されゲートに電源電位Ext.Vcc2を受けるNチャネルMOSトランジスタ72とを含む。

【0052】

インバータ68,70は、動作電源電位として電源電位Ext.Vcc1が与えられる。また、インバータ68の出力は、信号IVOFFとなる。信号IVOFFは、外部から与えられる電源電位Ext.Vcc2がまだ電位が立上がっていない場合にはHレベルとなり、電源電位Ext.Vcc2の電位が十分に立上がった場合には、Lレベルとなる信号である。

【0053】

なお、電源レベル検知回路56の構成要素であるトランジスタやインバータは、すべてExt.Vcc1の電源電圧に耐えうるだけのゲート酸化膜厚を有するトランジスタで構成されている。

【0054】

電源電位Ext.Vcc1,Ext.Vcc2ともに十分に電位が立上がっているときは、ノードNBを経由して電源電位Ext.Vcc1から接地ノードに向けて貫通電流が流れる。この電流量を制限するために、PチャネルMOSトランジスタ62はゲート長Lが大きいトランジスタが使用される。また、信号IVOFFがHレベルからLレベルに遷移するときの電源電位Ext.Vcc2の値は、インバータ68とNチャネルMOSトランジスタ72との電流駆動力のバランスによって定められる。

【0055】

電源レベル検知回路56を用いることにより、半導体装置に電源電位Ext.Vcc2が外部から印加されているか否かを識別することができる。

【0056】

図3は、図2に示した電源レベル検知回路56の動作を説明するための動作波形図である。

【0057】

図2、図3を参照して、電源電位Ext.Vcc1が立上がると時刻t1において、ノードNBの電位がNチャネルMOSトランジスタ66のしきい値電圧を超える。すると、ノードNCの電位はLレベルに確定し、信号IVOFFはHレベルに確定する。

【0058】

次に、時刻t2において、電源電位Ext.Vcc2が立上がり、電源電位Ext.Vcc2の電位がNチャネルMOSトランジスタ64のしきい値電圧を超えると、ノードNBの電位はLレベルに立下がる。

【0059】

続いて時刻t3において、電源電位Ext.Vcc2の電位がさらに上昇し、NチャネルMOSトランジスタ72の駆動力がインバータ68の駆動力に打ち勝つと、ノードNCの電位はLレベルからHレベルに立上がり、信号IVOFFはHレベルからLレベルに立下がる。

【0060】

すなわち、時刻t1〜t3においては、外部電源電位Ext.Vcc2がまだ印加されていないと電源レベル検知回路56が検知し、時刻t3以降においては、電源電位Ext.Vcc2が印加されていると電源レベル検知回路56が検知する。

【0061】

また、電源レベル検知回路56の出力は、図1には示されていないが、電源電位Ext.Vcc2に応じた振幅の入力信号を受ける内部回路にも与えられる。かかる内部回路では、電源電位Ext.Vcc2が十分に立上がっていない場合には入力信号が不確定で中間電位となるときがある。チップの内部や外部において、電源電位Ext.Vcc2を動作電源電位とする回路によって入力信号が発生されるケースがこの場合に該当する。

【0062】

たとえば、半導体装置が搭載されるプリント配線基板上で電源電位Ext.Vcc2を動作電源電位とする他の半導体装置から信号Ext./WEが与えられるとき、信号Ext./WEはそのような入力信号に該当する。また、チップ内部で電源電位Ext.Vcc2を動作電源電位として受ける行および列アドレスバッファ24から与えられる信号もそのような入力信号に該当する。

【0063】

このような入力信号を受ける内部回路は、入力信号を受ける部分に、レベル変換回路が設けられる場合が多い。たとえば、図1でこの内部回路に対応するのは、列デコーダ28およびレベル変換回路48、50である。

【0064】

以上説明したように、電源レベル検知回路56によって、複数の外部電源電位のうちいずれかが与えられていない場合に、既に与えられている外部電源電位を電源電位として受ける回路で発生する貫通電流の防止のための制御などに使用できる検知信号を発生することができる。

【0065】

[実施の形態1の変形例]

図2に示した電源レベル検知回路では、電源電位Ext.Vcc1,Ext.Vcc2がともに立上がっている場合に流れる定常電流を制限するのにゲート長Lが大きいトランジスタ62を使用した。しかし、他の方法でこの定常電流を制限することも可能である。たとえば、DRAMに通常内蔵されている参照電位発生回路の内部電位を用いることが考えられる。

【0066】

図4は、図1における電圧降下回路38の構成を示したブロック図である。

図4を参照して、電圧降下回路38は、内部電源電位int.Vccの基準となる参照電位Vrefを発生する参照電位発生回路82と、参照電位Vrefを受けて内部電源電位int.Vccを出力する電圧変換部84とを含む。

【0067】

電圧変換部84は、参照電位Vrefおよび内部電源電位int.Vccを受けて比較する差動アンプ86と、差動アンプ86の出力をゲートに受け、外部電源電位Ext.Vcc1を受ける電源ノードと内部電源電位int.Vccを出力する出力ノードとの間に接続されるPチャネルMOSトランジスタ88とを含む。

【0068】

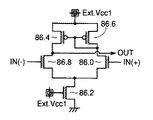

図5は、図4における差動アンプ86の構成例を示した回路図である。

図5を参照して、差動アンプ86は、外部電源電位Ext.Vcc1をゲートに受けソースが接地ノードに接続されるNチャネルMOSトランジスタ86.2と、入力信号IN(−)をゲートに受けソースがNチャネルMOSトランジスタ86.2のドレインと接続されるNチャネルMOSトランジスタ86.8と、電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ86.8のドレインとの間に接続されるPチャネルMOSトランジスタ86.4と、ソースが電源電位Ext.Vcc1と結合されゲートおよびドレインがPチャネルMOSトランジスタ86.4のゲートと接続されるPチャネルMOSトランジスタ86.6と、入力信号IN(−)をゲートに受けPチャネルMOSトランジスタ86.6のドレインとNチャネルMOSトランジスタ86.2のドレインとの間に接続されるNチャネルMOSトランジスタ86.0とを含む。

【0069】

NチャネルMOSトランジスタ86.8のドレインからは、出力信号OUTが出力される。

【0070】

図6は、実施の形態1の第1の変形例である電源レベル検知回路140の構成および図4における参照電位発生回路82の構成を示した回路図である。

【0071】

図6を参照して、参照電位発生回路82は、定電流発生回路91と、定電流発生回路91の出力に応じて参照電位Vrefを出力する出力回路92とを含む。

【0072】

定電流発生回路91は、電源電位Ext.Vcc1とノードNDとの間に接続されるローパスフィルタ120を含む。ローパスフィルタ120は、電源電位Ext.Vcc1を受けるノードとノードNDとの間に接続される抵抗122と、ノードNDと接地ノードとの間に接続されるキャパシタ124とを含む。

【0073】

定電流発生回路91は、さらに、ノードNDにドレインおよびバックゲートが接続されゲートがドレインが接続されているPチャネルMOSトランジスタ126と、PチャネルMOSトランジスタ126のドレインと接地ノードとの間に接続されるNチャネルMOSトランジスタ132と、ソースが接地ノードに接続されゲートおよびドレインがNチャネルMOSトランジスタ132のゲートと接続されるNチャネルMOSトランジスタ134と、ドレインがNチャネルMOSトランジスタ134のドレインと接続されゲートがPチャネルMOSトランジスタ126のドレインと接続されるPチャネルMOSトランジスタ128と、一方端にPチャネルMOSトランジスタ128のソースおよびバックゲートが接続され他方端がノードNDに接続される抵抗130とを含む。

【0074】

NチャネルMOSトランジスタ132,134のゲート幅とゲート長はともにWn/Lnで等しい。一方、PチャネルMOSトランジスタ126のゲート幅とゲート長をWp/Lpとすると、PチャネルMOSトランジスタ128のゲート幅とゲート長は10Wp/Lpである。

【0075】

このような構成とすることで、PチャネルMOSトランジスタ126とPチャネルMOSトランジスタ128にはともに、温度や電源電圧(Ext.Vcc1)の変化の影響が少ない定電流Iconstが流れる。

【0076】

出力回路92は、ノードNDにソースおよびバックゲートが接続されゲートがPチャネルMOSトランジスタ126のドレインに接続されるPチャネルMOSトランジスタ93と、PチャネルMOSトランジスタ93のドレインと接地ノードとの間に直列に接続されるPチャネルMOSトランジスタ94,96,98,100,112,116および118と、参照電位Vrefをチューニングするためのチューニング回路102とを含む。

【0077】

PチャネルMOSトランジスタ94〜100のゲートはともに接地ノードに接続され、バックゲートはともにPチャネルMOSトランジスタ93のドレインと接続される。PチャネルMOSトランジスタ112は自己のソースとバックゲートとが結合されており、ゲートは接地ノードに接続されている。PチャネルMOSトランジスタ116は、自己のソースとバックゲートとが接続されており、ゲートは自己のドレインと接続されている。PチャネルMOSトランジスタ118は、自己のソースとバックゲートとが接続されており、ゲートは接地ノードに接続されている。

【0078】

チューニング回路102は、PチャネルMOSトランジスタ93のドレインとPチャネルMOSトランジスタ94のドレインとの間に接続されるヒューズ104と、PチャネルMOSトランジスタ94のドレインとPチャネルMOSトランジスタ96のドレインとの間に接続されるヒューズ106と、PチャネルMOSトランジスタ96のドレインとPチャネルMOSトランジスタ98のドレインとの間に接続されるヒューズ108と、PチャネルMOSトランジスタ98のドレインとPチャネルMOSトランジスタ100のドレインとの間に接続されるヒューズ110とを含む。

【0079】

ヒューズ104〜110を選択的に切断することにより、PチャネルMOSトランジスタ93のドレインから出力される参照電位Vrefの電位を調整することができる。

【0080】

電源レベル検知回路140は、ゲート幅およびゲート長がPチャネルMOSトランジスタ126と等しいPチャネルMOSトランジスタ142を含む。PチャネルMOSトランジスタ142のソースは電源電位Ext.Vcc1またはノードNDに接続される。PチャネルMOSトランジスタ142のゲートはPチャネルMOSトランジスタ126のドレインと接続され、PチャネルMOSトランジスタ142のドレインはノードNB1に接続される。

【0081】

電源レベル検知回路140は、さらに、ゲートに外部電源電位Ext.Vcc2を受けノードNB1と接地ノードとの間に接続されるNチャネルMOSトランジスタ146と、ゲートがノードNB1に接続されノードNC1と接地ノードとの間に接続されるNチャネルMOSトランジスタ148と、ノードNC1に入力が接続されるインバータ150とインバータ150の出力を反転してノードNC1に帰還させるインバータ152と、インバータ150の出力と接地ノードとの間に接続されゲートに外部電源電位Ext.Vcc2を受けるNチャネルMOSトランジスタ154とを含む。

【0082】

インバータ150,152は、動作電源電位として電源電位Ext.Vcc1を受けて動作する。インバータ150の出力からは信号IVOFFが出力される。

【0083】

このような構成とすれば、図2で示したように、ゲート長Lの大きいPチャネルMOSトランジスタ62を使用しなくても電源レベル検知回路を構成することができる。

【0084】

図7は、電源レベル検知回路の第2の変形例の構成を示す回路図である。

図7を参照して、電源レベル検知回路160は、参照電位発生回路82の出力部の内部電位である電位V1を受ける。電位V1は、たとえば、PチャネルMOSトランジスタ112のドレインの電位を用いることができる。

【0085】

電源レベル検知回路160は、ソースが外部電源電位Ext.Vcc1と結合されゲートが接地ノードに接続されるPチャネルMOSトランジスタ162と、ゲートに電位V1を受けソースがPチャネルMOSトランジスタ162のドレインと接続されるPチャネルMOSトランジスタ164と、ゲートに外部電源電位Ext.Vcc2を受けソースがPチャネルMOSトランジスタ162のドレインと接続されるPチャネルMOSトランジスタ166と、PチャネルMOSトランジスタ164のドレインと接地ノードとの間に接続されゲートがPチャネルMOSトランジスタ166のドレインと接続されるNチャネルMOSトランジスタ168と、ゲートおよびドレインがPチャネルMOSトランジスタ166のドレインと接続されソースが接地ノードに接続されるNチャネルMOSトランジスタ170とを含む。

【0086】

電源レベル検知回路160は、さらに、ソースが外部電源電位Ext.Vcc1と結合されゲートが接地ノードと接続されるPチャネルMOSトランジスタ172と、ゲートがPチャネルMOSトランジスタ164のドレインと接続されソースがPチャネルMOSトランジスタ172のドレインと接続されるPチャネルMOSトランジスタ174と、ゲートがPチャネルMOSトランジスタ164のドレインと接続されPチャネルMOSトランジスタ174のドレインと接地ノードとの間に接続されるNチャネルMOSトランジスタ176と、NチャネルMOSトランジスタ176のドレインが入力に接続されるインバータ178と、インバータ178の出力を受けて反転し信号IVOFFを出力するインバータ179とを含む。

【0087】

PチャネルMOSトランジスタ162,172は、ともにゲート長Lが大きい電流制限用のトランジスタである。また、インバータ178,179は動作電源電位として電源電位Ext.Vcc1を受けて動作する。

【0088】

このような構成とすれば、中間電位V1と外部電源電位Ext.Vcc2とを比較して電源レベル検知回路160は外部電源電位Ext.Vcc2がオフ状態のときは信号IVOFFとしてHレベルを出力し、外部電源電位Ext.Vcc2がオン状態の場合には信号IVOFFとしてLレベルを出力する。

【0089】

図8は、電源レベル検知回路の第3の変形例を示した回路図である。

図8を参照して、電源レベル検知回路180では、参照電位発生回路82の内部のPチャネルMOSトランジスタ126のドレインの電位を受ける。電源レベル検知回路180は、外部電源電位Ext.Vcc2のオン状態/オフ状態を判断するための電位を発生する電位発生部181と、電位発生部181の出力と外部電源電位Ext.Vcc2とを比較して信号IVOFFを出力する電位比較部183とを含む。

【0090】

電位発生部181は、ソースが電源電位Ext.Vcc1またはノードNDと接続されゲートにPチャネルMOSトランジスタ126のドレインの電位を受けるPチャネルMOSトランジスタ182と、PチャネルMOSトランジスタ182のドレインと接地ノードとの間に接続されゲートに電源電位Ext.Vcc2を受けるNチャネルMOSトランジスタ184とを含む。

【0091】

PチャネルMOSトランジスタ182のゲート幅およびゲート長はPチャネルMOSトランジスタ126と等しい値に設定されている。

【0092】

電位比較部183は、ソースが外部電源電位Ext.Vcc1に接続されゲートが接地ノードに接続されるPチャネルMOSトランジスタ186と、ソースがPチャネルMOSトランジスタ186のドレインと接続されゲートにNチャネルMOSトランジスタ184のドレインの電位を受けるPチャネルMOSトランジスタ188と、ソースがPチャネルMOSトランジスタ186のドレインと接続されゲートに外部電源電位Ext.Vcc2を受けるPチャネルMOSトランジスタ190と、PチャネルMOSトランジスタ188のドレインと接地ノードとの間に接続されゲートにPチャネルMOSトランジスタ190のドレインの電位を受けるNチャネルMOSトランジスタ192と、ドレインおよびゲートがPチャネルMOSトランジスタ190のドレインと接続されソースが接地ノードに接続されるNチャネルMOSトランジスタ194とを含む。

【0093】

電位比較部183は、さらに、ソースが外部電源電位Ext.Vcc1と結合されゲートが接地ノードと接続されるPチャネルMOSトランジスタ196と、ゲートがNチャネルMOSトランジスタ192のドレインと接続されソースがPチャネルMOSトランジスタ196のドレインと接続されるPチャネルMOSトランジスタ198と、ゲートがNチャネルMOSトランジスタ192のドレインと接続されPチャネルMOSトランジスタ198のドレインと接地ノードとの間に接続されるNチャネルMOSトランジスタ200と、NチャネルMOSトランジスタ200のドレインが入力に接続されるインバータ202と、インバータ202の出力を受けて反転し信号IVOFFを出力するインバータ204とを含む。

【0094】

インバータ202,204は外部電源電位Ext.Vcc1を動作電源電位として受けて動作を行なう。

【0095】

このような構成としても、外部電源電位Ext.Vcc2がオフ状態のときにHレベルとなりオン状態のときにLレベルとなる信号IVOFFを発生させることができる。

【0096】

図9は、電源レベル検知回路の第4の変形例を示した回路図である。

図9を参照して、電源レベル検知回路210は、参照電位発生回路82が出力する参照電位Vrefを受け電位halfVrefを出力する電位発生部212と、電位halfVrefを外部電源電位Ext.Vcc2と比較して信号IVOFFを出力する電位比較部138とを含む。

【0097】

電位発生部212は、外部電源電位Ext.Vcc1をゲートに受けソースが接地ノードに接続されるNチャネルMOSトランジスタ222と、参照電位Vrefをゲートに受けソースがNチャネルMOSトランジスタ222のドレインと接続されるNチャネルMOSトランジスタ218と、電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ218のドレインとの間に接続されるPチャネルMOSトランジスタ214と、ソースが電源電位Ext.Vcc1と結合されゲートおよびドレインがPチャネルMOSトランジスタ214のゲートと接続されるPチャネルMOSトランジスタ216と、PチャネルMOSトランジスタ216のドレインとNチャネルMOSトランジスタ222のドレインとの間に接続されるNチャネルMOSトランジスタ220とを含む。

【0098】

電位発生部212は、さらに、外部電源電位Ext.Vcc1にソースが結合されゲートがPチャネルMOSトランジスタ214のドレインと接続されドレインがNチャネルMOSトランジスタ220のゲートと接続されるPチャネルMOSトランジスタ224と、NチャネルMOSトランジスタ220のゲートと接地ノードとの間に接続されるキャパシタ226と、PチャネルMOSトランジスタ224のドレインと接地ノードとの間に直列に接続されるPチャネルMOSトランジスタ228,230とを含む。

【0099】

なお、キャパシタ226の容量値は、たとえば50pF程度にすることが望ましい。

【0100】

PチャネルMOSトランジスタ228のバックゲートは自己のソースと接続されておりゲートは自己のドレインと接続されている。PチャネルMOSトランジスタ230のバックゲートは自己のソースと接続されておりゲートは接地ノードに接続されている。なお、PチャネルMOSトランジスタ228、230は、ゲート幅、ゲート長とも同一のトランジスタである。

【0101】

PチャネルMOSトランジスタ228のソースの電位を電位VrefBとするとPチャネルMOSトランジスタ230のソースの電位はその半分の電位である電位halfVrefとなる。

【0102】

電位比較部183は、電位halfVrefと外部電源電位Ext.Vcc2とを比較して信号IVOFFを出力するが、その構成は図8に示した場合と同様であり説明は繰返さない。

【0103】

図7で示したような中間電位V1は、外部電源電位Ext.Vcc1の変化や温度の変化の影響を受けやすい。これに対し、既存の参照電位発生回路82が発生する参照電位Vrefは、温度変化や電源電位の変化に起因する変動が少ない。したがって、図9に示す電源レベル検知回路210では、既存の参照電位Vrefの2分の1の分圧ノードを利用している。既存の参照電位Vrefそのものの温度依存性および電源電圧依存性が少ないため、その分圧ノードの変動も小さいので、安定した判定が可能となる。

【0104】

以上、図9に示した構成とすることで、さらに精密な制御を実現することができる。

【0105】

図10は、電源レベル検知回路の第5の変形例を示した回路図である。

図10を参照して、電源レベル検知回路240は、図9で示した電源レベル検知回路210の構成において電位比較部183に代えて電位比較部242を有する点が電源レベル検知回路210の構成と異なる。

【0106】

電位比較部242は、図9における電位比較部183の構成において、PチャネルMOSトランジスタ186のソースが外部電源電位Ext.Vcc2に結合され、PチャネルMOSトランジスタ196のソースが外部電源電位Ext.Vcc2に結合され、さらにインバータ202,204に代えてレベル変換回路246を含んでいる点が電位比較部183の構成と異なっている。

【0107】

レベル変換回路286は、図22に示したような構成を有している小振幅の信号をより大きな振幅の信号に変換するためのレベル変換回路である。

【0108】

電源レベル検知回路240の他の構成は図9で示した電源レベル検知回路210と同様であり説明は繰返さない。

【0109】

[実施の形態2]

実施の形態2では、実施の形態1で説明した電源レベル検知回路の出力信号を用いて内部電源発生回路を制御する場合について述べる。この電源レベル検知回路の出力信号を用いて、内部電源発生回路の動作を停止すれば、内部電源電位を動作電源電位として受けて動作する回路の貫通電流を低減させることができる。

【0110】

図11は、図1に示した昇圧電源回路36の構成を示した回路図である。

図11を参照して、昇圧電源回路36は、内部昇圧電位Vppのレベルを検出して、内部昇圧電位Vppが十分に昇圧されているか否かに応じて制御信号DECOUTを出力するレベル検出回路252と、実施の形態1およびその変形例のいずれかの回路で発生した信号IVOFFを受けて反転するインバータ256と、制御信号DECOUTおよびインバータ256の出力を受けて発振器制御信号OSCONTを出力するAND回路258と、発振器制御信号OSCONTが活性化された場合に発振を開始する発振器260と、発振器260の出力するクロック信号に応じて昇圧動作を行ない昇圧電位Vppを出力するチャージポンプ262とを含む。

【0111】

レベル検出回路252、インバータ256、AND回路258、発振器260およびチャージポンプ262は、すべて外部電源電位Ext.Vcc1を動作電源電位として受ける回路である。また、これらの回路は図21で説明したようなExt.Vcc1の電源電圧に耐えうるだけのゲート酸化膜厚を有するトランジスタで構成されている。

【0112】

レベル検出回路252は、内部昇圧電位Vppが所定の電位に到達していない場合には、制御信号DECOUTをHレベルに活性化する。一方、レベル検出回路252は、内部昇圧電位Vppが十分高い電位である場合には、制御信号DECOUTをLレベルに非活性化する。

【0113】

通常の昇圧電源回路であれば、外部電源電位Ext.Vcc1が外部から印加されておれば発振器260が動作してチャージポンプ262により昇圧電位Vppが発生する。

【0114】

しかし、図1で示したレベル変換回路42,44,46,48,50,52,54および、後に説明する図20のレベル変換回路42,44,46,454,452として、図22,図23に示したような従来のレベル変換回路をそのまま使用すると、外部電源電位Ext.Vcc2が十分に立上がっていない場合に昇圧電位Vppが高い電位になると貫通電流が流れてしまう。

【0115】

そこで、図11で示した構成とすれば、信号IVOFFによって外部電源電位Ext.Vcc2が十分な電位になっていない場合には発振器260の発振を停止しチャージポンプ262の動作を停止したままとするので昇圧電位Vppが高い電位になることはない。したがってレベル変換回路における貫通電流を防止することができる。

【0116】

[実施の形態3]

実施の形態3では、図1における電圧降下回路38に信号IVOFFによる制御を適用した場合を示す。

【0117】

図12は、電圧降下回路38aの構成を示した回路図である。

図12を参照して、電圧降下回路38は、信号IVOFFを受けて反転するインバータ272と、インバータ272の出力をゲートに受けソースが接地ノードに接続されるNチャネルMOSトランジスタ276と、参照電位Vrefをゲートに受けソースがNチャネルMOSトランジスタ276のドレインと接続されるNチャネルMOSトランジスタ278と、ゲートに内部電源電位int.Vccを受けソースがNチャネルMOSトランジスタ276のドレインと接続されるNチャネルMOSトランジスタ280と、ゲートにインバータ272の出力を受け外部電源電位Ext.Vcc1にソースが接続されドレインがNチャネルMOSトランジスタ280のドレインと接続されるPチャネルMOSトランジスタ274と、ゲートにインバータ272の出力を受けソースが外部電源電位Ext.Vcc1を受けるノードと接続されドレインがNチャネルMOSトランジスタ278のドレインと接続されるPチャネルMOSトランジスタ286とを含む。

【0118】

電圧降下回路38aは、さらに、外部電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ278のドレインとの間に接続されゲートがNチャネルMOSトランジスタ280のドレインと接続されるPチャネルMOSトランジスタ282と、外部電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ280のドレインとの間に接続されゲートがNチャネルMOSトランジスタ280のドレインと接続されるPチャネルMOSトランジスタ284と、外部電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ280のゲートとの間に接続されゲートがNチャネルMOSトランジスタ278のドレインと接続されるPチャネルMOSトランジスタ288とを含む。

【0119】

なお、参照電位Vrefを発生する回路は、図示しないが図6で示した参照電位発生回路82と同様な構成を有しており説明は繰返さない。

【0120】

このような回路構成とすれば、外部電源電位Ext.Vcc1が一定値以上に立上がっていても外部電源電位Ext.Vcc2がまだ立上がっていない場合には、PチャネルMOSトランジスタ274および286が導通状態となりNチャネルMOSトランジスタ276が非導通状態となる。すると、ゲート電位が外部電源電位Ext.Vcc1となりドライバトランジスタであるPチャネルMOSトランジスタ288は非導通状態となるため、内部電源電位int.Vccを出力するノードには電流が供給されない。

【0121】

つまり、内部電源電位int.Vccは電位が上昇しない。したがって、図1のレベル変換回路48のような、外部電源電位Ext.Vcc2を動作電源電位とする回路系から内部電源電位int.Vccを動作電源電位とする回路系に伝達される信号のレベル変換を行なうレベル変換回路においても、貫通電流を低減させることができる。

【0122】

[実施の形態4]

DRAMでは、メモリセルアレイのキャパシタの一方の電極にセルプレート電位Vcpを与えるが、このセルプレート電位Vcpは書込データのHレベルとLレベルの2分の1程度の電位とすることが多い。セルプレート電位Vcpを接地電位にした場合よりも、キャパシタの両端に印加される最大電圧が小さいので、信頼性を維持しつつキャパシタの絶縁膜厚を薄くでき、キャパシタの容量値を大きくすることができるからである。

【0123】

図13は、電源電位の2分の1の電位を発生する内部電源回路290の構成を示した回路図である。

【0124】

図13を参照して、内部電源回路290は、信号IVOFFを受けて反転し信号/IVOFFを出力するインバータ292と、内部電源電位int.Vccが与えられるノードとノードN20との間に接続される抵抗298と、ノードN20にゲートおよびドレインが接続されるNチャネルMOSトランジスタ294と、NチャネルMOSトランジスタ294のソースにバックゲートおよびソースが接続されゲートおよびドレインがノードN21に接続されるPチャネルMOSトランジスタ296と、ノードN21と接地ノードとの間に接続される抵抗300とを含む。

【0125】

内部電源回路290は、さらに、外部電源電位Ext.Vcc1が与えられるノードと接地ノードとの間に直列に接続されるNチャネルMOSトランジスタ312,PチャネルMOSトランジスタ314と、NチャネルMOSトランジスタ314のゲートにドレインが接続されソースが接地ノードに接続されゲートに信号IVOFFを受けるNチャネルMOSトランジスタ310と、ソースに外部電源電位Ext.Vcc1が結合されドレインがPチャネルMOSトランジスタ314のゲートに接続されゲートに信号/IVOFFを受けるPチャネルMOSトランジスタ316とを含む。

【0126】

内部電源回路290は、さらに、信号IVOFF,/IVOFFをそれぞれゲートに受けノードN20の電位をNチャネルMOSトランジスタ312のゲートに伝達するPチャネルMOSトランジスタ302,NチャネルMOSトランジスタ304と、信号IVOFF,/IVOFFをそれぞれゲートに受けノードN21の電位をPチャネルMOSトランジスタ314のゲートに伝達するPチャネルMOSトランジスタ306,NチャネルMOSトランジスタ308とを含む。

【0127】

このような構成とすれば、外部電源電位Ext.Vcc1の電位が十分に立上がっている場合において外部電源電位Ext.Vcc2の電位がまだ立上がっていない場合には、内部電源回路290の駆動するトランジスタであるNチャネルMOSトランジスタ312のゲート電位は接地電位とされ、PチャネルMOSトランジスタ314の電位は外部電源電位Ext.Vcc1とされ、これら2つのドライバトランジスタはともに非導通状態となるため、内部電源電位int.Vcc3は発生されない。

【0128】

したがって、外部電源電位Ext.Vcc2を動作電源電位とする回路系から内部電源電位int.Vccを動作電源電位とする回路系への信号のレベル変換に用いられるレベル変換回路においても貫通電流を低減させることができる。

【0129】

[実施の形態5]

実施の形態5においては、レベル変換回路における貫通電流を防止する構成について説明する。

【0130】

図14は、実施の形態5に係るレベル変換回路48の構成を示した回路図である。

【0131】

図14を参照して、レベル変換回路48は、信号IVOFFをゲートに受けソースが接地ノードに接続され、ドレインが信号SIGAが与えられるノードに接続されるNチャネルMOSトランジスタ322と、信号SIGAを受けて反転するインバータ326と、信号SIGAをゲートに受けソースが接地ノードに接続されるNチャネルMOSトランジスタ332と、ゲートにインバータ326の出力を受けソースが接地ノードに接続されるNチャネルMOSトランジスタ334と、内部電源電位int.Vccが与えられるノードとNチャネルMOSトランジスタ332のドレインとの間に接続されゲートがNチャネルMOSトランジスタ334のドレインと接続されるPチャネルMOSトランジスタ328と、内部電源電位int.Vccが与えられるノードとNチャネルMOSトランジスタ334のドレインとの間に接続されゲートがNチャネルMOSトランジスタ332のドレインと接続されるPチャネルMOSトランジスタ330と、NチャネルMOSトランジスタ334のドレインと接地ノードとの間に接続されゲートに信号IVOFFを受けるNチャネルMOSトランジスタ324とを含む。

【0132】

信号SIGAはLレベルが0Vであり、Hレベルが外部電源電位Ext.Vcc2である信号であり、インバータ326は外部電源電位Ext.Vcc2を動作電源電位として受けて動作するインバータである。そしてNチャネルMOSトランジスタ334のドレインからはLレベルが0VでありHレベルが内部電源電位int.Vccである信号/SIGAが出力される。

【0133】

このような構成とすることにより、たとえば、図1の行および列アドレスバッファ24から列デコーダ28に対して信号を伝達する経路上のレベル変換回路などにおいて貫通電流を低減させることができる。

【0134】

具体的には、外部電源電位Ext.Vcc2の電位が十分に立上がっていない場合には信号IVOFFがHレベルに活性化されるため、信号SIGAおよび信号/SIGAは強制的にNチャネルMOSトランジスタ322,324によってそれぞれ接地電位に設定されることになる。したがって、NチャネルMOSトランジスタ332,334に流れる貫通電流を除くことが可能となる。

【0135】

[実施の形態6]

実施の形態6では、高い側の外部電源電位のオン状態/オフ状態を低い側の内部電源電位を動作電源電位とする回路で検知する構成について説明する。

【0136】

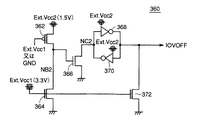

図15は、電源レベル検知回路360の構成を示した回路図である。

図15を参照して、電源レベル検知回路360は、接地電位または電源電位Ext.Vcc2をゲートに受け、電源電位Ext.Vcc2が与えられるノードとノードNB2との間に接続されるゲート長Lが大きいPチャネルMOSトランジスタ362と、ノードNB2と接地ノードとの間に接続されゲートに電源電位Ext.Vcc1を受けるNチャネルMOSトランジスタ364と、ノードNB2にゲートが接続されノードNC2と接地ノードとの間に接続されるNチャネルMOSトランジスタ366と、ノードNC2が入力に接続されるインバータ368と、インバータ368の出力を受けて反転しノードNC2に帰還させるインバータ370と、インバータ368の出力と接地ノードとの間に接続されゲートに電源電位Ext.Vcc1を受けるNチャネルMOSトランジスタ372とを含む。

【0137】

インバータ368,370には、動作電源電位として電源電位Ext.Vcc2が与えられる。また、インバータ368の出力は、信号IOVOFFとなる。信号IOVOFFは、外部から与えられる電源電位Ext.Vcc1がまだ立上がっていない場合にはHレベルとなり、電源電位Ext.Vcc1が十分に立上がった場合には、Lレベルとなる信号である。

【0138】

なお、電源レベル検知回路360の構成要素であるトランジスタ362,364および372は、Ext.Vcc1の電源電圧に耐えうるだけのゲート酸化膜厚を有するトランジスタである。また、トランジスタ366およびインバータ368,370は、Ext.Vcc2の電源電圧に耐えうるだけのゲート酸化膜厚を有するトランジスタで構成される要素である。

【0139】

電源電位Ext.Vcc1,Ext.Vcc2ともに十分に電位が立上がっているときは、ノードNB2を経由して電源電位Ext.Vcc2から接地ノードに向けて貫通電流が流れる。この電流量を制限するために、PチャネルMOSトランジスタ362はゲート長Lが大きいトランジスタが使用される。また、信号IOVOFFがHレベルからLレベルに遷移するときの電源電位Ext.Vcc1の値は、インバータ368とNチャネルMOSトランジスタ372との電流駆動力のバランスによって定められる。

【0140】

出力信号IOVOFFが、外部電源電位Ext.Vcc1がオン状態にあるかオフ状態にあるかを識別する信号である。この信号IOVOFFを発生する電源レベル検知回路360そのものの動作電源電位は低い側の外部電源電位Ext.Vcc2である。

【0141】

このような回路を用いることにより、外部電源電位Ext.Vcc1が印加されているか否かを識別することが可能となる。

【0142】

[実施の形態7]

実施の形態7では、Hレベルが高い外部電源電位Ext.Vcc1である信号からHレベルが低い電源電位であるExt.Vcc2である信号に変換するレベル変換回路における貫通電流について説明する。

【0143】

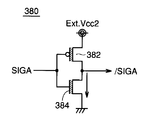

図16は、通常のレベル変換部380の構成を示した回路図である。

図16を参照して、レベル変換部380は、信号SIGAをゲートに受けソースが外部電源電位Ext.Vcc2に結合されるPチャネルMOSトランジスタ382と、ゲートに信号SIGAを受けPチャネルMOSトランジスタ382のドレインと接地ノードとの間に接続されるNチャネルMOSトランジスタ384とを含む。PチャネルMOSトランジスタ382のドレインからは信号/SIGAが出力される。

【0144】

信号SIGAのLレベルは0Vであり、Hレベルは電源電位Ext.Vcc1と同じである。一方出力信号/SIGAのLレベルは0Vであり、Hレベルは電源電位Ext.Vcc2である。このような回路構成の場合であっても、外部電源電位Ext.Vcc2の電位が十分に高い状態であっても外部電源電位Ext.Vcc1の電位がまだ与えられていない場合には、信号SIGAが中間電位すなわちNチャネルMOSトランジスタ384のしきい値電圧を超える付近でふらつくと貫通電流が流れてしまう。

【0145】

図17は、貫通電流を低減させるためのレベル変換部381の構成を示した回路図である。

【0146】

図17を参照して、レベル変換部381は、図16に示したレベル変換部380の構成において、図15で説明した信号IOVOFFをゲートに受けNチャネルMOSトランジスタ384のゲートと接地ノードとの間に接続されるNチャネルMOSトランジスタ386をさらに備える点がレベル変換部380の構成と異なる。他の構成はレベル変換部380と同様であり説明は繰返さない。

【0147】

このような構成とすることにより、外部電源電位Ext.Vcc1の電位が十分に立上がっていない場合にはNチャネルMOSトランジスタ386が導通状態となりNチャネルMOSトランジスタ384のゲート電位を接地レベルとするため貫通電流を低減させることができる。

【0148】

なお、レベル変換部381の信号SIGAを出力する回路は外部電源電位Ext.Vcc1を動作電源電位として動作する内部回路に限らない。レベル変換部381は、外部電源電位Ext.Vcc2よりも高いあらゆる外部電源電位および内部電源電位を動作電源電位とする回路から信号を受ける場合に適用することができる。

【0149】

[実施の形態8]

たとえば、図14で示したレベル変換回路48を使用する場合において、電源電位int.Vcc1が所定の電位となっており、外部電源電位Ext.Vcc2が未だに与えられていない時間帯においては、入力信号SIGAは接地電位に固定される。そして、外部電源電位Ext.Vcc2の立上がり時において外部電源電位Ext.Vcc2を受けてリセット信号を出力するパワーオンリセット回路によって信号SIGAがHレベルに初期化される場合には、外部電源電位Ext.Vcc2が立上がり始めてから信号IVOFFがLレベルになるまでの時間帯にはNチャネルMOSトランジスタ322には貫通電流が流れることになる。

【0150】

図18は、実施の形態8に係るレベル変換回路390の構成を示した回路図である。

【0151】

図18を参照して、レベル変換回路390は、外部電源電位Ext.Vcc2の電位を介してその立上がり時にリセット信号/PORを出力するパワーオンリセット回路392と、パワーオンリセット信号/PORに応じて初期化され入力信号IN1を受けて信号SIGAを出力する入力分離回路394と、信号SIGAをレベル変換して信号/SIGAを出力するレベル変換部396とを含む。

【0152】

入力分離回路394は、リセット信号/PORを受けて反転するインバータ398と、インバータ398の出力をゲートに受けソースが電源電位Ext.Vcc2に結合されるPチャネルMOSトランジスタ400と、ゲートに信号IN1を受けソースがPチャネルMOSトランジスタ400のドレインと接続されるPチャネルMOSトランジスタ402と、ゲートに信号IN1を受けドレインがPチャネルMOSトランジスタ402のドレインと接続されるNチャネルMOSトランジスタ404と、リセット信号/PORをゲートに受けNチャネルMOSトランジスタ404のソースと接地ノードとの間に接続されるNチャネルMOSトランジスタ408とを含む。

【0153】

入力分離回路394は、さらに、電源電位Ext.Vcc2が与えられるノードとNチャネルMOSトランジスタ404のドレインとの間に接続されゲートにリセット信号/PORを受けるPチャネルMOSトランジスタ410と、NチャネルMOSトランジスタ404のドレインに入力が接続され信号SIGAを出力するインバータ412と、インバータ412の出力を受けて反転してインバータ412の入力に帰還させるインバータ414とを含む。

【0154】

インバータ398,412,414は外部電源電位Ext.Vcc2を動作電源電位として受けて動作するインバータである。

【0155】

レベル変換部396は、信号IVOFFをゲートに受けソースが接地ノードに接続され、ドレインが信号SIGAが与えられるノードに接続されるNチャネルMOSトランジスタ422と、信号SIGAを受けて反転するインバータ426と、信号SIGAをゲートに受けソースが接地ノードに接続されるNチャネルMOSトランジスタ432と、ゲートにインバータ426の出力を受けソースが接地ノードに接続されるNチャネルMOSトランジスタ434と、電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ432のドレインとの間に接続されゲートがNチャネルMOSトランジスタ434のドレインと接続されるPチャネルMOSトランジスタ428と、電源電位Ext.Vcc1が与えられるノードとNチャネルMOSトランジスタ434のドレインとの間に接続されゲートがNチャネルMOSトランジスタ432のドレインと接続されるPチャネルMOSトランジスタ430と、NチャネルMOSトランジスタ434のドレインと接地ノードとの間に接続されゲートに信号IVOFFを受けるNチャネルMOSトランジスタ424とを含む。

【0156】

信号SIGAはLレベルが0Vであり、Hレベルが外部電源電位Ext.Vcc2である信号であり、インバータ426は外部電源電位Ext.Vcc2を動作電源電位として受けて動作するインバータである。そしてNチャネルMOSトランジスタ434のドレインからはLレベルが0VでありHレベルが電源電位Ext.Vcc1である信号/SIGAが出力される。

【0157】

図19は、レベル変換回路390の動作を説明する動作波形図である。

図18、図19を参照して、電源電位Ext.Vcc1が電位VDDHまで立上がると、時刻t1において、信号IVOFFがHレベルに確定し、また、信号SIGAがLレベルに確定する。

【0158】

続いて、電源電位Ext.Vcc2が立上り始めると、時刻t2において、パワーオンリセット回路392がリセット信号/PORをLレベルに活性化する。

【0159】

さらに、電源電位Ext.Vcc2が上昇すると、時刻t3においてパワーオンリセット回路392がリセット信号/PORをHレベルに非活性化し、入力分離回路394は、リセットが解除され、入力信号IN1を受け、受けた信号を信号SIGAとして出力する。

【0160】

時刻t2〜t3の期間T1の間は、リセット信号/PORによってトランジスタ400,402,404および408から構成されるクロックドインバータが非活性化され、入力信号IN1が与えられるノードが信号SIGAを出力するインバータ412の入力から分離されることになる。

【0161】

そして、インバータ412の入力が、PチャネルMOSトランジスタ410によってHレベルに固定される。応じて信号SIGAがLレベルとなり、信号IVOFFがHレベルのときに設定される設定値と一致する。したがって、入力信号IN1の初期状態に拘らず、NチャネルMOSトランジスタ422に流れる貫通電流を低減させることができる。

【0162】

なお、パワーオンリセット期間において入力信号IN1が信号SIGAに影響を与えない構成であれば、同様な効果が得られるので種々の変形が可能である。

たとえば、入力信号IN1の伝達される距離が短い場合は、クロックドインバータで入力信号IN1を受ける代わりに、通常時は導通状態とされるトランスミッションゲートで入力信号IN1を信号SIGAとして伝達しても良い。パワーオンリセット期間にトランスミッションゲートを非導通状態になるように制御すれば、PチャネルMOSトランジスタ410、インバータ412,414が無くても同様な効果が得られる。

【0163】

[他の応用例]

図20は、単一電源で動作するDRAMの構成を示したブロック図である。

【0164】

本発明は、図1で示したように外部から複数の外部電源電位が供給される半導体装置にその適用が限定されるものではなく、図20に示すように、外部から単一の外部電源電位を受け、昇圧電源回路36、電圧降下回路38で内部昇圧電位Vppや内部電源電位int.Vccを発生させる構成の場合でも適用することが可能である。

【0165】

半導体装置450では、各電源電位は、たとえば、電源電位Ext.Vccは3.3Vであり、内部昇圧電位Vppは3.6Vであり、内部電源電位int.Vccは2.0Vである。

【0166】

また、半導体装置450では、ゲート回路18、クロック発生回路22、データ入力バッファ20、行および列アドレスバッファ24、リフレッシュアドレスカウンタ25およびデータ出力バッファ34、列デコーダ28、センスアンプ+入出力制御回路30が、内部電源電位int.Vccを動作電源電位として受ける回路となっている。そして、行デコーダ26は、内部昇圧電位Vppを動作電源電位として受け、この内部昇圧電位がワード線の活性化レベルとなる。

【0167】

半導体装置450の場合にも、異なる電源電位を動作電源電位とする回路間での信号のレベル変換を行なうレベル変換回路42〜46,452,454を含んでおり、このようなレベル変換回路に本発明を適用することにより貫通電流が低減され、消費電力を低く抑えることができる。

【0168】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0169】

【発明の効果】

請求項1に記載の半導体装置は、複数の電源電位を受ける半導体装置において電源電位が立上がっていないことを検出し、内部回路に貫通電流低減等をするための所定の動作を行なわせることができる。

【0170】

請求項2〜4に記載の半導体装置は、請求項1に記載の半導体装置の奏する効果に加えて、レベル変換回路における貫通電流を低減させることができる。

【0171】

請求項5、6に記載の半導体装置は、請求項2に記載の半導体装置の奏する効果に加えて、レベル変換回路を電源電位が立上がっていないときに貫通電流が少ない状態にすることができる。

【0172】

請求項7〜10に記載の半導体装置は、請求項1に記載の半導体装置の奏する効果に加えて、外部電源電位に応じて発生される内部電源電位を制御することで、貫通電流を低減させることができる。

【0173】

請求項11に記載の半導体装置は、請求項1に記載の半導体装置の奏する効果に加えて、パワーオン時にリセットされた入力信号と検知回路による貫通電流防止のための内部ノードの固定が異なる極性の場合に、貫通電流を低減させることができる。

【0174】

請求項12、13に記載の半導体装置は、請求項1に記載の半導体装置の奏する効果に加えて、他の回路に使用される安定した参照電位を発生する参照電位発生回路を利用することで、チップ面積の増加を防ぎつつより安定した動作をさせることができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態1の半導体装置1の構成を示す概略ブロック図である。

【図2】 図1に示した電源レベル検知回路56の第1の構成例を示した図である。

【図3】 図2に示した電源レベル検知回路56の動作を説明するための動作波形図である。

【図4】 図1における電圧降下回路38の構成を示したブロック図である。

【図5】 図4における差動アンプ86の構成例を示した回路図である。

【図6】 実施の形態1の第1の変形例である電源レベル検知回路140の構成および図4における参照電位発生回路82の構成を示した回路図である。

【図7】 電源レベル検知回路の第2の変形例の構成を示す回路図である。

【図8】 電源レベル検知回路の第3の変形例を示した回路図である。

【図9】 電源レベル検知回路の第4の変形例を示した回路図である。

【図10】 電源レベル検知回路の第5の変形例を示した回路図である。

【図11】 図1に示した昇圧電源回路36の構成を示した回路図である。

【図12】 電圧降下回路38aの構成を示した回路図である。

【図13】 電源電位の2分の1の電位を発生する内部電源回路290の構成を示した回路図である。

【図14】 実施の形態5に係るレベル変換回路48の構成を示した回路図である。

【図15】 電源レベル検知回路360の構成を示した回路図である。

【図16】 通常のレベル変換部380の構成を示した回路図である。

【図17】 貫通電流を低減させるためのレベル変換部381の構成を示した回路図である。

【図18】 実施の形態8に係るレベル変換回路390の構成を示した回路図である。

【図19】 レベル変換回路390の動作を説明する動作波形図である。

【図20】 単一電源で動作するDRAMの構成を示したブロック図である。

【図21】 本明細書において用いる記号を説明するための図である。

【図22】 低振幅から高振幅に変換する、従来の第1のレベル変換回路の構成を示した回路図である。

【図23】 高振幅から低振幅に変換する、従来の第2のレベル変換回路の構成を示した回路図である。

【符号の説明】

1,450 半導体装置、2 制御信号入力端子、8 アドレス入力端子群、10,11 電源端子、12 接地端子、14 入力端子群、16 出力端子群、18 ゲート回路、20 データ入力バッファ、22 クロック発生回路、24 列アドレスバッファ、25 リフレッシュアドレスカウンタ、26 行デコーダ、28 列デコーダ、30 入出力制御回路、32 メモリセルアレイ、34 データ出力バッファ、36 昇圧電源回路、38,38a 電圧降下回路、42,44,46,50,48,52,54,246,286,390 レベル変換回路、56,140,160,180,210,240,360 電源レベル検知回路、82 参照電位発生回路、84 電圧変換部、86 差動アンプ、91 定電流発生回路、92 出力回路、102 チューニング回路、104〜110 ヒューズ、120 ローパスフィルタ、122,130 抵抗、124,226 キャパシタ、138,183,242 電位比較部、181,212電位発生部、252 レベル検出回路、258 AND回路、260 発振器、262 チャージポンプ、290 内部電源回路、380,381,396 レベル変換部、392 パワーオンリセット回路、394 入力分離回路。

Claims (4)

- 第1の電源電位を受ける第1の端子と、

第2の電源電位を受ける第2の端子と、

前記第1の端子から動作電源電位を受け、前記第2の端子の電位を検知する検知回路と、

前記第2の端子の電位に応じた振幅の入力信号を受け、前記検知回路の出力に応じて動作を行なう内部回路とを備え、

前記内部回路は、前記検知回路の出力に応じて活性化し、前記第1の電源電位から内部電源電位を発生する内部電源回路と、

前記内部電源回路から動作電流の供給を受け、前記入力信号に応じて動作する回路とを含む、半導体装置。 - 前記検知回路は、前記第2の端子の電位が所定の電位に達していないときは、前記内部電源回路に対し、前記内部電源電位の発生を停止させる、請求項1に記載の半導体装置。

- 前記内部電源回路は、

前記内部電源電位が所定の電位に到達しているか否かを検出するレベル検出回路と、

前記レベル検出回路の出力と前記検知回路の出力とに応じて活性化して発振する発振器と、

前記発振器の出力に応じて前記第1の電源電位を昇圧して前記内部電源電位を発生するチャージポンプ回路とを有する、請求項1に記載の半導体装置。 - 前記内部電源回路は、

前記内部電源電位を供給する出力ノードを前記第1の電源電位に結合する駆動トランジスタと、

前記検知回路の出力に応じて活性化し、前記出力ノードの電位を参照電位と比較して前記駆動トランジスタの導通状態を制御する比較回路とを有し、

前記比較回路は、自己が非活性化時に前記駆動トランジスタを非導通状態とする、請求項1に記載の半導体装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000323797A JP4748841B2 (ja) | 2000-10-24 | 2000-10-24 | 半導体装置 |

| US09/811,578 US6483357B2 (en) | 2000-10-24 | 2001-03-20 | Semiconductor device reduced in through current |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000323797A JP4748841B2 (ja) | 2000-10-24 | 2000-10-24 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2002134695A JP2002134695A (ja) | 2002-05-10 |

| JP2002134695A5 JP2002134695A5 (ja) | 2007-11-15 |

| JP4748841B2 true JP4748841B2 (ja) | 2011-08-17 |

Family

ID=18801420

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000323797A Expired - Fee Related JP4748841B2 (ja) | 2000-10-24 | 2000-10-24 | 半導体装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6483357B2 (ja) |

| JP (1) | JP4748841B2 (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6650155B1 (en) * | 2002-08-07 | 2003-11-18 | Lsi Logic Corporation | Power-on reset circuit |

| KR100569558B1 (ko) * | 2003-11-10 | 2006-04-10 | 주식회사 하이닉스반도체 | 전원 제어 기능을 갖는 불휘발성 강유전체 메모리 장치 |

| JP4159454B2 (ja) * | 2003-11-27 | 2008-10-01 | エルピーダメモリ株式会社 | 半導体装置 |

| KR100520653B1 (ko) * | 2003-12-01 | 2005-10-13 | 주식회사 하이닉스반도체 | 전원 제어 기능을 갖는 불휘발성 강유전체 메모리 장치 |

| US7378886B2 (en) * | 2004-10-14 | 2008-05-27 | Fairchild Semiconductor | Voltage detection circuit with hysteresis for low power, portable products |

| KR100697284B1 (ko) * | 2005-05-02 | 2007-03-20 | 삼성전자주식회사 | 플래시 메모리 장치 및 그것의 프로그램 방법 |

| KR100763331B1 (ko) * | 2005-06-24 | 2007-10-04 | 삼성전자주식회사 | 반도체 메모리 장치 |

| KR100885491B1 (ko) * | 2007-03-31 | 2009-02-24 | 주식회사 하이닉스반도체 | 고전위전압 공급장치를 포함하는 반도체메모리소자 |

| US8139426B2 (en) * | 2008-08-15 | 2012-03-20 | Qualcomm Incorporated | Dual power scheme in memory circuit |

| US7936632B2 (en) * | 2008-09-19 | 2011-05-03 | Hynix Semiconductor Inc. | Semiconductor device including an internal circuit receiving two different power supply sources |

| JP2012142562A (ja) * | 2010-12-17 | 2012-07-26 | Semiconductor Energy Lab Co Ltd | 半導体記憶装置 |

| JP6769130B2 (ja) | 2016-06-22 | 2020-10-14 | セイコーエプソン株式会社 | 電源回路、回路装置、表示装置及び電子機器 |

| US9972388B2 (en) * | 2016-10-12 | 2018-05-15 | Arm Ltd. | Method, system and device for power-up operation |

| CN119993221B (zh) * | 2023-11-13 | 2025-11-18 | 长江存储科技有限责任公司 | 存储器件中的电压控制 |

Family Cites Families (16)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5891680A (ja) * | 1981-11-26 | 1983-05-31 | Fujitsu Ltd | 半導体装置 |

| JP2906509B2 (ja) * | 1990-01-12 | 1999-06-21 | 日本電気株式会社 | 信号処理装置 |

| JPH04285437A (ja) | 1991-03-12 | 1992-10-09 | Fujitsu Ltd | 停電検出装置 |

| JPH0583109A (ja) * | 1991-09-25 | 1993-04-02 | Mitsubishi Denki Eng Kk | 半導体集積回路 |

| US5369310A (en) * | 1992-06-01 | 1994-11-29 | Hewlett-Packard Corporation | CMOS power-on reset circuit |

| JPH06140499A (ja) | 1992-10-27 | 1994-05-20 | Toyota Motor Corp | 半導体集積回路 |

| JPH0778472A (ja) * | 1993-09-10 | 1995-03-20 | Toshiba Corp | 半導体集積回路 |

| JPH07229932A (ja) * | 1994-02-17 | 1995-08-29 | Toshiba Corp | 電位検知回路 |

| JP3072254B2 (ja) * | 1995-09-29 | 2000-07-31 | 川崎製鉄株式会社 | レベルシフト回路 |

| US5847587A (en) * | 1997-01-07 | 1998-12-08 | Holtek Microelectronics Inc. | Means for instantaneously detecting abnormal voltage in a micro controller |

| JPH10290526A (ja) | 1997-04-14 | 1998-10-27 | Denso Corp | 車載コンピュータの電源装置 |

| JPH10336007A (ja) * | 1997-05-29 | 1998-12-18 | Fujitsu Ltd | レベルコンバータ、出力回路及び入出力回路 |

| JP3558520B2 (ja) * | 1998-04-22 | 2004-08-25 | 松下電器産業株式会社 | レベルシフト回路 |

| JP3935266B2 (ja) * | 1998-05-08 | 2007-06-20 | 松下電器産業株式会社 | 電圧検知回路 |

| JP2000019200A (ja) * | 1998-07-01 | 2000-01-21 | Mitsubishi Electric Corp | 電位検出回路 |

| JP3549186B2 (ja) * | 1998-08-25 | 2004-08-04 | 株式会社東芝 | 半導体装置 |

-

2000

- 2000-10-24 JP JP2000323797A patent/JP4748841B2/ja not_active Expired - Fee Related

-

2001

- 2001-03-20 US US09/811,578 patent/US6483357B2/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US20020047741A1 (en) | 2002-04-25 |

| JP2002134695A (ja) | 2002-05-10 |

| US6483357B2 (en) | 2002-11-19 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR960009394B1 (ko) | 동적 임의 접근 메모리용 전원 회로 | |

| JP3650186B2 (ja) | 半導体装置および比較回路 | |

| US6642757B2 (en) | Semiconductor memory device having a power-on reset circuit | |

| TWI222639B (en) | Semiconductor device | |

| JP3759758B2 (ja) | 半導体記憶装置 | |

| JP4748841B2 (ja) | 半導体装置 | |

| US20020089370A1 (en) | Internal voltage generator for semiconductor memory device | |

| US6525972B2 (en) | Semiconductor memory device with boosting control circuit and control method | |

| KR100302589B1 (ko) | 기준전압발생기의스타트업회로 | |

| US7436226B2 (en) | Power-up detection circuit that operates stably regardless of variations in process, voltage, and temperature, and semiconductor device thereof | |

| JPH04351791A (ja) | 半導体メモリー装置のデータ入力バッファー | |

| KR20040094224A (ko) | 파워-온 초기화 회로 및 그를 포함하는 반도체 집적 회로장치 | |

| JPH05101658A (ja) | ダイナミツク型ランダムアクセスメモリ装置 | |

| JP2727809B2 (ja) | 半導体集積回路 | |

| US6518831B1 (en) | Boosting circuit for high voltage operation | |

| US20040251957A1 (en) | Internal voltage generator | |

| US6771115B2 (en) | Internal voltage generating circuit with variable reference voltage | |

| US6661218B2 (en) | High voltage detector | |

| US6052317A (en) | Output circuit of semiconductor memory device | |

| KR100812299B1 (ko) | 전압 강하 회로 | |

| US20010026189A1 (en) | Intermediate voltage control circuit having reduced power consumption five | |

| US20090115380A1 (en) | Internal voltage generator | |

| KR100762842B1 (ko) | 반도체 메모리 장치의 초기화 시스템 | |

| KR0183874B1 (ko) | 반도체 메모리장치의 내부 전원전압 발생회로 | |

| JP3369771B2 (ja) | 半導体集積回路 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070927 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20070927 |

|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20100519 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20100913 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100928 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101122 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110118 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110318 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20110510 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20110517 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140527 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |