JP4439794B2 - 半導体装置の作製方法 - Google Patents

半導体装置の作製方法 Download PDFInfo

- Publication number

- JP4439794B2 JP4439794B2 JP2002264226A JP2002264226A JP4439794B2 JP 4439794 B2 JP4439794 B2 JP 4439794B2 JP 2002264226 A JP2002264226 A JP 2002264226A JP 2002264226 A JP2002264226 A JP 2002264226A JP 4439794 B2 JP4439794 B2 JP 4439794B2

- Authority

- JP

- Japan

- Prior art keywords

- laser

- substrate

- film

- thin film

- film transistor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Thin Film Transistor (AREA)

- Recrystallisation Techniques (AREA)

Description

【発明の属する技術分野】

本願発明は、レーザー光を用いた半導体膜のアニール(以下、レーザーアニールという)の方法及びそれを行うためのレーザー処理装置(レーザーと該レーザーから出力されるレーザー光を被処理体まで導くための光学を含む装置)に関する。また、前記レーザーアニールを工程に含んで作製された半導体装置及びその作製方法に関する。なお、ここでいう半導体装置には、液晶表示装置やEL表示装置等の電気光学装置も含まれるものとする。

【0002】

【従来の技術】

近年、薄膜トランジスタ(以下、TFTという)の開発が進められ、結晶性半導体膜として多結晶シリコン膜(ポリシリコン膜)を用いたTFTが注目されている。特に、液晶表示装置(液晶ディスプレイ)やEL(エレクトロルミネッセンス)表示装置(ELディスプレイ)においては、画素をスイッチングする素子やその画素を制御するための駆動回路を形成する素子として用いられる。

【0003】

多結晶半導体膜は、薄膜トランジスタの活性層として用いられる。多結晶半導体膜は、不純物の添加によりソース領域、ドレイン領域及びチャネル形成領域が形成される。また、オフセット領域やLDD領域を設けても良い。

【0004】

ポリシリコン膜を得る手段としては、非晶質シリコン膜(アモルファスシリコン膜)を結晶化させてポリシリコン膜とする技術が一般的である。特に、最近ではレーザー光を用いてアモルファスシリコン膜を結晶化する方法が注目されている。本明細書中では、非晶質半導体膜をレーザー光で結晶化し、結晶性半導体膜を得る手段をレーザー結晶化という。

【0005】

レーザー結晶化は、半導体膜の瞬間的な加熱が可能であり、ガラス基板やプラスチック基板等の耐熱性の低い基板上に形成された半導体膜のアニール手段として有効な技術である。

【0006】

レーザー光にも様々な種類があり、連続発振型とパルス発振型に大別されている。レーザー結晶化に関し良好な結晶を得ることができるという点で、連続発振型のレーザーが注目されている。

【0007】

従来のレーザー結晶化技術では、ビームを線状に形成した線状ビームによりレーザー結晶化をしている。(例えば、特許文献1参照。)。

【0008】

【特許文献1】

特開平8−195357号公報

【0009】

【発明が解決しようとする課題】

本願発明は、連続発振型のレーザーの新規な光学系により、一枚の基板上に形成された薄膜トランジスタにおいて、これらを作り分け、要求される特性をすべて満たす薄膜トランジスタを作製することを課題とする。

【0010】

液晶表示装置やEL表示装置においては、画素をスイッチングする素子やその画素を制御するための駆動回路を形成する素子は一つの基板上に形成される。これらの素子はその役割に応じて様々な特性を必要とされる。しかしながら、基板一面に形成された非晶質シリコン膜に連続発振型のレーザーを一様に照射して結晶性半導体膜を得る方法で作製された薄膜トランジスタは、要求される様々な特性を満足することは難しい。

【0011】

【課題を解決するための手段】

薄膜トランジスタと半導体膜の結晶性について述べる。薄膜トランジスタの電気的特性は、半導体膜の結晶性に依るところが大きい。特に、結晶粒界といった結晶と結晶の間にある境界は、キャリアの移動を妨げる。キャリアの移動が妨げられることによって、薄膜トランジスタの電気的抵抗が大きくなる。したがって、薄膜トランジスタの電気的特性を制御するには結晶粒界の数を制御する必要がある。

【0012】

結晶粒界の数は結晶の成長方向により制御することができる。基板を加熱することで結晶化を行うことでは、結晶の成長方向を制御することはできなかったが、レーザー結晶化では局所的に加熱し溶融することができるため結晶の成長方向を制御することが可能である。

【0013】

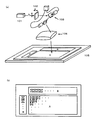

半導体膜の結晶の成長方向は、連続発振型のレーザーから発振されたレーザー光のビーム形状を線状に成形し、その線の方向に対して垂直な方向に合わせることで制御することができる。この場合、図2のように半導体膜の結晶の成長方向は、線状に成形されたレーザー光の線の方向(長軸方向)に対して垂直な方向(短軸方向)に従う。結晶の成長方向は結晶粒界の発生方向でわかる。ここでは、ビームを線状に成形し、被照射物(具体的には基板)上を走査することが重要になる。また、レーザ光のビーム形状は、正確には楕円形状もしくは矩形状としているが、そのアスペクト比は大きいので、ここでは線状と定義する。図1a)に本願発明を構成する光学系を示し、以下にその説明を行う。

【0014】

円形に発振されたレーザービームはシリンドリカルレンズ102で一軸方向に拡散される。レーザービームはガルバノミラー103により制御され、f−θレンズに入射する。焦点距離をf−θレンズ104により調整することで、ある平面上のどの位置でも焦点を結ぶ(ピントを合わす)ことができる。焦点を結ぶ(ピントを合わす)とは被照射物上の線状のビーム形状及び大きさを被照射物どの位置でも同じにすることである。ガルバノミラー103を動かすことでレーザーの照射位置を変え、基板上を走査することができる。このようにすると、基板を動かすことなく基板上に楕円形のレーザービームを走査することができる。

【0015】

レーザーの単位面積当たりのエネルギー密度を変えたければ、この光学系にレンズを挿入する、基板の距離を変える等が考えられる。シリンドリカルレンズ102の焦点距離を変えることで、ビーム形状を調整することができる。また、ガルバノミラー103により走査速度を変えることができる。

【0016】

ここで重要なのは、シリンドリカルレンズ102を回転させることで、基板上に投影される線形ビームを回転させることができることである。通常基板上に形成されるアクティブマトリクス回路等の薄膜トランジスタは多数存在し、その向き、即ち電荷移動方向はバラバラである。したがって、本願発明のようにシリンドリカルレンズ102を回転できる構成で線の方向に走査する結晶の成長方向を制御する構成を組み合わせることで、基板上の各薄膜トランジスタの電気的特性を制御することができる。

【0017】

【発明の実施の形態】

(実施形態1)本願発明の実施形態の一つについて説明する。本願発明の実施形態は基板の縦方向と横方向に電荷移動方向を有する薄膜トランジスタにおいて、結晶成長方向と電荷移動方向を揃えた薄膜トランジスタを作製するものである。

【0018】

図1a)は本願発明のレーザーを含むレーザー装置の構成を示す図である。連続発振型Nd:YVO4レーザ101、連続発振型Nd:YVO4レーザ101を発振源とするレーザー光(第2高調波、波長532nm)を楕円状に加工する凸型シリンドリカルレンズ102、レーザー光を走査するガルバノミラー103、焦点距離を調整するf−θレンズ104、基板を固定するステージ105を有している。凸型シリンドリカルレンズ102は回転ステージに設置され、任意に回転できる構成になっている。基板には非晶質シリコン膜が成膜され、領域Aと領域Bがもうけられている。図1b)は基板の上面図であり、領域Aには基板の横方向に電荷移動方向がある薄膜トランジスタが形成され、また領域Bには基板の縦方向に電荷移動方向がある薄膜トランジスタが形成されることを示すものである。

【0019】

ここでは、レーザーの出力は10Wである。レーザービーム形状は短軸方向20μm、長軸方向400μmの楕円形を形成した。走査速度20cm/sである。半導体膜の溶融は、単位面積あたりのエネルギー密度が問題となる。したがって、これと類似するエネルギー密度であれば、レーザービームの形状または大きさを変化させてもよい。

【0020】

このような構成で非晶質シリコン膜にレーザー光の照射が行われる。領域Aにおいては、凸型シリンドリカルレンズ102は回転ステージ(詳細は図示しない)によりシリンドリカルレンズのパワーの方向がaの方向に設定され、ガルバノミラー103により基板の横方向にレーザー光が走査される。一方、領域Bでは凸型シリンドリカルレンズ102は回転ステージによりaより90°回転したシリンドリカルレンズのパワーの方向がbの方向に設定され、ガルバノミラー103により基板の縦方向にレーザー光が走査される。

【0021】

このようにすると、レーザーの走査方向、即ち結晶成長方向と電荷移動方向を揃えた薄膜トランジスタを作製することができる。このような方法で作製された薄膜トランジスタは図3a)で示されるような結晶粒界を有する。なお、結晶粒は単結晶になっている。薄膜トランジスタに要求される電気的特性によっては、レーザーの走査方向、即ち結晶成長方向と電荷移動方向を垂直にしてもよい。垂直にした場合、図3b)のように薄膜トランジスタの電荷移動方向に複数の結晶粒界が存在するため、キャリアの移動度が下がる。しかしながら、薄膜トランジスタのスイッチがオフ状態おけるリーク電流が低減できるという利点がある。

【0022】

また、ガルバノミラー103によりレーザーが走査され、凸型シリンドリカルレンズ102によりレーザービームの形状が制御されるため、基板を動かすことなく結晶化を行うことができる。

【0023】

(実施形態2)実施形態1とは異なる実施の形態について説明する。この実施形態は基板の縦方向と横方向に電荷移動方向を有する薄膜トランジスタにおいて、結晶の成長方向と電荷移動方向をそろえずに均一な電気特性を有する薄膜トランジスタを作製するものである。図1a)、b)と同じ構成の光学系、基板を用いる。

【0024】

回転ステージに設置された凸型シリンドリカルレンズ102は、aとbの中間すなわち45°に設定される。このような構成でレーザー光を発振すると基板上には、斜め方向に楕円形状が投影される。基板の縦方向または横方向から45°の方向に結晶成長がおこることになる。

【0025】

このように結晶化された基板から図3c)のような薄膜トランジスタを形成する。基板の横方向に電荷移動方向を有する薄膜トランジスタと基板の縦方向に電荷移動方向を有する薄膜トランジスタとは電荷移動方向を横切る結晶粒界の数がほとんど同じになるため電気的特性が均一になる。

【0026】

図12にあるように薄膜トランジスタが縦、横交互に形成され、その特性を均一なものに統一する必要がある場合にも適用できる。

【0027】

また、薄膜トランジスタの大きさや形によっては、シリンドリカルレンズの角度を45°に限定する必要はない。薄膜トランジスタの電気的特性を均一にすればよいので、0°から90°の間で回転させ、走査すればよい。このようにして形成された薄膜トランジスタに用いられる半導体膜の結晶成長方向は、基板の縦軸および横軸とは平行にならず、斜め方向になる。

【0028】

(実施形態3)この実施形態は、ビーム形状を楕円形状にするに当たり、より光学調整が行いやすい光学系について述べる。実施形態1及び2では、楕円形状を作るための凸型シリンドリカルレンズは、1枚であった。しかしながら本実施の形態では2枚用いる。

【0029】

2枚のレンズにより、ビームを拡大または縮小する方法は、ガリレオ式、ケプラー式の二つがある。ガリレオ式は図4のように凹レンズと凸レンズを用いてビームの大きさを変える方式である。一方、ケプラー式は図4のように2枚の凸レンズを用いてビームの大きさを変える方式である。

【0030】

このレンズをシリンドリカルレンズに変えると、一軸方向のみビームを拡大または縮小し、長軸と短軸の比を容易に調整することができる。ただし、2つのシリンドリカルレンズは軸方向をそろえる必要がある。したがって、回転ステージ等で回転させる際に同時に動かす必要がある。

【0031】

シリンドリカルレンズの他にプリズムを2対使ってビームを1軸方向のみに拡大または縮小させることもできる。その他同等の作用を持つものを利用してもよい。

【0032】

(実施形態4)この実施形態は、より均一なレーザー照射をするための光学系について述べる。本実施形態では計算機ホログラムを光学系に導入する。計算機ホログラムはビームの形状を成形する方法であり、ビームのエネルギー分布を自在に変えることも可能である。したがって計算機ホログラムの導入によって、ビームのエネルギー分布をより均一にし、均一なレーザー照射することができる。

【0033】

(実施形態5)この実施形態は、実際に基板に照射するにおいて必要とする装置について述べる。図1a)のようにガルバノミラーにより、基板上でビームが走査される場合、基板中央に照射されたビームは、反射されてレーザー装置に戻ってしまう。この戻りレーザービームは、レーザー装置に使われる高調波変換素子を痛める原因になる。したがってこれを回避するためにアイソレーターといった一方向のビームしか通さない装置を光学系に導入する。

【0034】

図1a)において、レーザービームの形状が変わらないシリンドリカルレンズの前に入れておくことが有効である。先ほどの計算機ホログラムとは順不同で用いることができる。

【0035】

(実施形態6)この実施形態は、実際に基板に照射するにおいて必要とする実施形態5とは異なる装置について述べる。基板上を走査されるレーザー光は、エネルギー密度が高いため長時間基板に照射されると基板を溶かす。したがって、ガルバノミラーの故障等何らかの原因でレーザー光の走査が停止した場合、基板への照射を停止する必要がある。そこで本願発明では、インターロックをガルバノミラーの先にもうける。インターロックは、ステージ上に設けられたセンサーで異常を感知するまたはガルバノミラーの故障を感知することで発動し、金属板などでビームにシャッターをかける。

【0036】

(実施形態7)この実施形態は、実際に基板に照射するにおいて必要とされる実施形態5および6とは異なる装置について述べる。基板上を走査されるレーザー光は非常に強いため、非晶質シリコン膜に吸収されなかった反射光や透過光も周囲に被害を与える。したがって、これらの光を周囲にまき散らさないためにチャンバーもしくは反射光を吸収するダンパーを基板の周囲に設ける必要がある。

【0037】

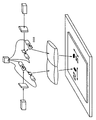

(実施形態8)この実施形態は量産体制において必要とする光学系について述べる。図5で示されるようにガルバノミラー503を一つのコントローラーで制御することにより二つの光源からのレーザー光の走査を同時に行うものである。このようにすると、レーザー結晶化のスループットを2倍にすることができる。

【0038】

また、二つのレーザー光を同時に走査する別の方法として、図6に示すように、一方を基板の表側から照射し、もう一方を基板の裏側から照射することができる。ただし、基板およびステージがレーザー光を透過できることが必要である。

【0039】

本願発明は実施形態1〜8のいずれにおいても組み合わせることができる。また、実施形態1〜8では非晶質シリコン膜の表側からレーザー光を照射したが、基板を透過し、半導体膜で吸収される波長のレーザー光であれば基板の裏側から照射することができる。

【0040】

【実施例1】

本発明の実施例を図9〜図11を用いて説明する。本実施例では、基板の縦方向と横方向に電荷移動方向を有する薄膜トランジスタを作製する方法について説明する。図7は基板上に周辺駆動回路と画素回路が形成されたEL表示装置の上面図である。周辺駆動回路は基板の縦方向に電荷移動方向を有する薄膜トランジスタと横方向に電荷移動方向を有する薄膜トランジスタが混在して構成されている。図7上図は周辺駆動回路の一部であるインバータ回路を構成する薄膜トランジスタを示したものであり、基板の縦方向に電荷移動方向を有する薄膜トランジスタが形成されている。一方、画素回路は、複数の画素がマトリクス状に形成された構成を有しており、その一部を拡大すると図8のようになっている。一つの画素は、横方向に電荷移動方向を有する薄膜トランジスタのみで構成されている。

【0041】

ここでは、画素回路を構成するスイッチング用薄膜トランジスタおよび駆動用薄膜トランジスタと、周辺駆動回路のインバーター回路を構成する薄膜トランジスタを同時に作製する方法について、工程に従って詳細に説明する。また、消去用薄膜トランジスタは、スイッチング用薄膜トランジスタと同様に作製することができるので、ここでは説明を省略した。

【0042】

図9において、基板900にはコーニング社の#7059ガラスや#1737ガラスなどに代表されるバリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板の他に、石英基板、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルフォン(PES)などのプラスチック基板を用いることができる。

【0043】

そして、基板900のTFTを形成する表面に、基板900からの不純物拡散を防ぐために、酸化シリコン膜、窒化シリコン膜または酸化窒化シリコン膜などの絶縁膜からなる下地膜901を形成する。本実施例では下地膜901として2層構造を用いるが、前記絶縁膜の単層膜または2層以上積層させた構造を用いても良い。下地膜901の1層目としてはプラズマCVD法を用い、SiH4、NH3、及びN2Oを反応ガスとして成膜される酸化窒化シリコン膜901aを10〜200nm(好ましくは50〜100nm)形成する。本実施例では、膜厚50nmの酸化窒化シリコン膜901a(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。次いで、下地膜901の2層目としては、プラズマCVD法を用い、SiH4、及びN2Oを反応ガスとして成膜される酸化窒化シリコン膜901bを50〜200nm(好ましくは100〜150nm)の厚さに積層形成する。本実施例では、膜厚100nmの酸化窒化シリコン膜901b(組成比Si=32%、O=27%、N=24%、H=17%)を形成した。

【0044】

次に、25〜150nm(好ましくは30〜60nm)の厚さで非晶質半導体膜903を、プラズマCVD法、LPCVD法やスパッタ法などの公知の方法で形成する。半導体膜の材料には限定はないが、好ましくはシリコンまたはシリコンゲルマニウム(SixGe1-x(x=0.0001〜0.02))合金などで形成すると良い。本実施例では、プラズマCVD法を用い、55nmの非晶質シリコン膜を成膜した。

【0045】

基板に非晶質シリコン膜の上から図1(a)で示されるようなレーザー照射装置によりレーザーが照射される。領域Aは画素回路であり、図8のように、基板の横方向に電荷移動方向がある薄膜トランジスタが形成される。ここでは、シリンドリカルレンズはaの方向に設定され、ガルバノミラーにより基板の横方向にレーザー光が照射される。

【0046】

ここでは、画素回路にはレーザーの走査方向、即ち結晶成長方向と電荷移動方向を揃えた薄膜トランジスタを作製したが、薄膜トランジスタに要求される電気的特性によっては、レーザーの走査方向、即ち結晶成長方向と電荷移動方向を垂直にしてもよい。垂直にした場合、図3b)のように薄膜トランジスタの電荷移動方向に複数の結晶粒界が存在するため、キャリアの移動度が下がる。しかしながら、薄膜トランジスタのスイッチがオフ状態におけるリーク電流が低減できるという利点がある。

【0047】

一方、領域Bは、周辺駆動回路であり、基板の縦方向に電荷移動方向を有する薄膜トランジスタと横方向に電荷移動方向を有する薄膜トランジスタが混在して形成される。ここではシリンドリカルレンズはaとbの中間すなわち45°の方向に設定されガルバノミラーにより基板の斜め方向、厳密には基板に投影された楕円状のビームの短軸方向にレーザー光が走査される。

【0048】

周辺駆動回路は、基板の縦方向に電荷移動方向を有する薄膜トランジスタと横方向に電荷移動方向を有する薄膜トランジスタが混在している。しかしながら、回路内では同一周波数で動いているため、それぞれの薄膜トランジスタの電気的特性をそろえる必要がある。従って上記のように基板の縦方向もしくは横方向に45°の角度をもって走査を行った。回路の配置によっては、シリンドリカルレンズの角度を調整しうる。

【0049】

この結晶質シリコン膜をフォトリソグラフィー法を用いたパターニング処理によって、半導体層902〜905を作製した。

【0050】

また、半導体層902〜905を形成した後、TFTのしきい値を制御するために、半導体層902〜905に微量な不純物元素(ボロンまたはリン)をドーピングしても良い。

【0051】

次いで、半導体層902〜905を覆うゲート絶縁膜906を形成する。ゲート絶縁膜906はプラズマCVD法またはスパッタ法を用い、厚さを40〜150nmとしてシリコンを含む絶縁膜で形成する。本実施例では、プラズマCVD法により110nmの厚さで酸化窒化シリコン膜(組成比Si=32%、O=59%、N=7%、H=2%)で形成した。勿論、ゲート絶縁膜は酸化窒化シリコン膜に限定されるものではなく、ほかのシリコンを含む絶縁膜を単層または積層構造として用いても良い。

【0052】

また、酸化シリコン膜を用いる場合には、プラズマCVD法でTEOS(Tetraethyl Orthosilicate)とO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。このようにして作製される酸化シリコン膜は、その後400〜500℃の熱アニールによりゲート絶縁膜として良好な特性を得ることができる。

【0053】

そして、ゲート絶縁膜906上にゲート電極を形成するための耐熱性導電層907を200〜400nm(好ましくは250〜350nm)の厚さで形成する。耐熱性導電層907は単層で形成しても良いし、必要に応じて2層あるいは3層といった複数の層からなる積層構造としても良い。耐熱性導電層にはTa、Ti、Wから選ばれた元素、または前記元素を成分とする合金か、前記元素を組み合わせた合金膜が含まれる。これらの耐熱性導電層はスパッタ法やCVD法で形成されるものであり、低抵抗化を図るために含有する不純物濃度を低減させることが好ましく、特に酸素濃度に関しては30ppm以下とすると良い。本実施例ではW膜はWをターゲットとしてスパッタ法で形成しても良いし、6フッ化タングステン(WF6)を用いて熱CVD法で形成することもできる。いずれにしてもゲート電極として使用するためには低抵抗化を図る必要があり、W膜の抵抗率は20μΩcm以下にすることが望ましい。W膜は結晶粒を大きくすることで低抵抗率化を図ることができるが、W中に酸素などの不純物元素が多い場合には結晶化が阻害され高抵抗化する。このことより、スパッタ法による場合、純度99.99%または99.999%のWターゲットを用い、さらに成膜時に気相中からの不純物の混入がないように十分に配慮してW膜を形成することにより抵抗率9〜20μΩcmを実現することができる。

【0054】

一方、耐熱性導電層907にTa膜を用いる場合には、同様にスパッタ法で形成することが可能である。Ta膜はスパッタガスにArを用いる。また、スパッタ時のガス中に適量のXeやKrを加えておくと、形成する膜の内部応力を緩和して膜の剥離を防止することができる。α相のTa膜の抵抗率は20μΩcm程度でありゲート電極に使用することができるが、β相のTa膜の抵抗率は180μΩcm程度でありゲート電極とするには不向きであった。TaN膜はα相に近い結晶構造を持つので、Ta膜の下地にTaN膜を形成すればα相のTa膜が容易に得られる。また、図示しないが、耐熱性導電膜907の下に2〜20nm程度の厚さでリン(P)をドープしたシリコン膜を形成しておくことは有効である。これにより、その上に形成される導電膜の密着性向上と酸化防止を図ると同時に、耐熱性導電層907が微量に含有するアルカリ金属元素が第1の形状のゲート絶縁膜906に拡散するのを防ぐことができる。いずれにしても、耐熱性導電層907は抵抗率を10〜50μΩcmの範囲ですることが好ましい。

【0055】

次にフォトリソグラフィーの技術を使用してレジストによるマスク908を形成する。そして、第1のエッチング処理を行う。本実施例ではICPエッチング装置を用い、エッチング用ガスにCl2とCF4を用い、1Paの圧力で3.2W/cm2のRF(13.56MHz)電力を投入してプラズマを形成して行う。基板側(試料ステージ)にも224mW/cm2のRF(13.56MHz)電力を投入し、これにより実質的に負の自己バイアス電圧が印加される。この条件でW膜のエッチング速度は約100nm/minである。第1のエッチング処理はこのエッチング速度を基にW膜がちょうどエッチングされる時間を推定し、それよりもエッチング時間を20%増加させた時間をエッチング時間とした。

【0056】

第1のエッチング処理により第1のテーパー形状を有する導電層909〜912が形成される。導電層909〜912のテーパー部の角度は15〜30°となるように形成される。残渣を残すことなくエッチングするためには、10〜20%程度の割合でエッチング時間を増加させるオーバーエッチングを施すものとする。W膜に対する酸化窒化シリコン膜(ゲート絶縁膜906)の選択比は2〜4(代表的には3)であるので、オーバーエッチング処理により、酸化窒化シリコン膜が露出した面は20〜50nm程度エッチングされる。(図9(B))

【0057】

そして、第1のドーピング処理を行い一導電型の不純物元素を半導体層に添加する。ここでは、n型を付与する不純物元素添加の工程を行う。第1の形状の導電層を形成したマスク908をそのまま残し、第1のテーパー形状を有する導電層909〜912をマスクとして自己整合的にn型を付与する不純物元素をイオンドープ法で添加する。n型を付与する不純物元素をゲート電極の端部におけるテーパー部とゲート絶縁膜906とを通して、その下に位置する半導体層に達するように添加するためにドーズ量を1×1013〜5×1014atoms/cm2とし、加速電圧を80〜160keVとして行う。n型を付与する不純物元素として15族に属する元素、典型的にはリン(P)または砒素(As)を用いるが、ここではリン(P)を用いた。このようなイオンドープ法により第1の不純物領域914〜917には1×1020〜1×1021atoms/cm3の濃度範囲でn型を付与する不純物元素が添加される。(図9(C))

【0058】

この工程において、ドーピングの条件によっては、不純物が、第1の形状の導電層909〜912の下に回り込み、第1の不純物領域914〜917が第1の形状の導電層909〜912に重なることも起こりうる。

【0059】

次に、図9(D)に示すように第2のエッチング処理を行う。エッチング処理も同様にICPエッチング装置により行い、エッチングガスにCF4とCl2の混合ガスを用い、RF電力3.2W/cm2(13.56MHz)、バイアス電力45mW/cm2(13.56MHz)、圧力1.0Paでエッチングを行う。この条件で形成される第2の形状を有する導電層918〜921が形成される。その端部にはテーパー部が形成され、該端部から内側にむかって徐々に厚さが増加するテーパー形状となる。第1のエッチング処理と比較して基板側に印加するバイアス電力を低くした分等方性エッチングの割合が多くなり、テーパー部の角度は30〜60°となる。マスク908はエッチングされて端部が削れ、マスク922となる。また、図9(D)の工程において、ゲート絶縁膜906の表面が40nm程度エッチングされる。

【0060】

そして、第1のドーピング処理よりもドーズ量を下げ高加速電圧の条件でn型を付与する不純物元素をドーピングする。例えば、加速電圧を70〜120keVとし、1×1013/cm2のドーズ量で行い、不純物濃度が大きくなった第1の不純物領域924〜927と、前記第1の不純物領域924〜927に接する第2の不純物領域928〜931とを形成する。この工程において、ドーピングの条件によっては、不純物が第2の形状の導電層918〜921の下に回りこみ、第2の不純物領域928〜931が第2の形状の導電層918〜921と重なることも起こりうる。第2の不純物領域における不純物濃度は、1×1016〜1×1018atoms/cm3となるようにする。(図10(A))

【0061】

そして、図10(B)に示すように、pチャネル型TFTを形成する半導体層902、905に一導電型とは逆の導電型の不純物領域933(933a、933b)及び934(934a、934b)を形成する。この場合も第2の形状の導電層918、921をマスクとしてp型を付与する不純物元素を添加し、自己整合的に不純物領域を形成する。このとき、nチャネル型TFTを形成する半導体層903、904は、レジストのマスク932を形成し全面を被覆しておく。ここで形成される不純物領域933、934はジボラン(B2H6)を用いたイオンドープ法で形成する。不純物領域933、934のp型を付与する不純物元素の濃度は、2×1020〜2×1021atoms/cm3となるようにする。

【0062】

しかしながら、この不純物領域933、934は詳細にはn型を付与する不純物元素を含有する2つの領域に分けて見ることができる。第3の不純物領域933a、934aは1×1020〜1×1021atoms/cm3の濃度でp型を付与する不純物元素を含み、第4の不純物領域933b、934bは1×1017〜1×1020atoms/cm3の濃度でn型を付与する不純物元素を含んでいる。しかし、これらの第4の不純物領域933b、934bのp型を付与する不純物元素の濃度を1×1019atoms/cm3以上となるようにし、第3の不純物領域933a、934aにおいては、p型を付与する不純物元素の濃度をn型を付与する不純物元素の濃度の1.5から3倍となるようにすることにより、第3の不純物領域でpチャネル型TFTのソース領域およびドレイン領域として機能するために何ら問題は生じない。

【0063】

その後、図10(C)に示すように、第2の形状を有する導電層918〜921およびゲート絶縁膜906上に第1の層間絶縁膜937を形成する。第1の層間絶縁膜937は酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜、またはこれらを組み合わせた積層膜で形成すれば良い。いずれにしても第1の層間絶縁膜937は無機絶縁物材料から形成する。第1の層間絶縁膜937の膜厚は100〜200nmとする。第1の層間絶縁膜937として酸化シリコン膜を用いる場合には、プラズマCVD法でTEOSとO2とを混合し、反応圧力40Pa、基板温度300〜400℃とし、高周波(13.56MHz)電力密度0.5〜0.8W/cm2で放電させて形成することができる。また、第1の層間絶縁膜937として酸化窒化シリコン膜を用いる場合には、プラズマCVD法でSiH4、N2O、NH3から作製される酸化窒化シリコン膜、またはSiH4、N2Oから作製される酸化窒化シリコン膜で形成すれば良い。この場合の作製条件は反応圧力20〜200Pa、基板温度300〜400℃とし、高周波(60MHz)電力密度0.1〜1.0W/cm2で形成することができる。また、第1の層間絶縁膜937としてSiH4、N2O、H2から作製される酸化窒化水素化シリコン膜を適用しても良い。窒化シリコン膜も同様にプラズマCVD法でSiH4、NH3から作製することが可能である。

【0064】

そして、それぞれの濃度で添加されたn型またはp型を付与する不純物元素を活性化する工程を行う。この工程はファーネスアニール炉を用いる熱アニール法で行う。その他に、レーザーアニール法、またはラピッドサーマルアニール法(RTA法)を適用することができる。熱アニール法では酸素濃度が1ppm以下、好ましくは0.1ppm以下の窒素雰囲気中で400〜700℃、代表的には500〜600℃で行うものであり、本実施例では550℃で4時間の熱処理を行った。また、基板501に耐熱温度が低いプラスチック基板を用いる場合にはレーザーアニール法を適用することが好ましい。

【0065】

活性化の工程に続いて、雰囲気ガスを変化させ、3〜100%の水素を含む雰囲気中で、300〜450℃で1〜12時間の熱処理を行い、半導体層を水素化する工程を行う。この工程は熱的に励起された水素により半導体層にある1016〜1018/cm3のダングリングボンドを終端する工程である。水素化の他の手段として、プラズマ水素化(プラズマにより励起された水素を用いる)を行っても良い。いずれにしても、半導体層902〜905中の欠陥密度を1016/cm3以下とすることが望ましく、そのために水素を0.01〜0.1atoms%程度付与すれば良い。

【0066】

そして、有機絶縁物材料からなる第2の層間絶縁膜939を1.0〜2.0μmの平均膜厚で形成する。有機樹脂材料としては、ポリイミド、アクリル、ポリアミド、ポリイミドアミド、BCB(ベンゾシクロブテン)等を使用することができる。例えば、基板に塗布後、熱重合するタイプのポリイミドを用いる場合には、クリーンオーブンで300℃で焼成して形成する。また、アクリルを用いる場合には、2液性のものを用い、主材と硬化剤を混合した後、スピナーを用いて基板全面に塗布した後、ホットプレートで80℃で60秒の予備加熱を行い、さらにクリーンオーブンで250℃で60分焼成して形成することができる。

【0067】

このように、第2の層間絶縁膜939を有機絶縁物材料で形成することにより、表面を良好に平坦化させることができる。また、有機樹脂材料は一般に誘電率が低いので、寄生容量を低減できる。しかし、吸湿性があり保護膜としては適さないので、本実施例のように、第1の層間絶縁膜937として形成した酸化シリコン膜、酸化窒化シリコン膜、窒化シリコン膜などと組み合わせて用いると良い。

【0068】

その後、所定のパターンのレジストマスクを形成し、それぞれの半導体層に形成されソース領域またはドレイン領域とする不純物領域に達するコンタクトホールを形成する。コンタクトホールはドライエッチング法で形成する。この場合、エッチングガスにCF4、O2、Heの混合ガスを用い有機樹脂材料から成る第2の層間絶縁膜939をまずエッチングし、その後、続いてエッチングガスをCF4、O2として第1の層間絶縁膜937をエッチングする。さらに、半導体層との選択比を高めるために、エッチングガスをCHF3に切り替えて第3の形状のゲート絶縁膜570をエッチングすることによりコンタクトホールを形成することができる。

【0069】

そして、導電性の金属膜をスパッタ法や真空蒸着法で形成し、マスクでパターニングし、その後エッチングすることで、ソース配線940〜943とドレイン配線944〜946を形成する。図示していないが、本実施例ではこの配線を、そして、膜厚50nmのTi膜と、膜厚500nmの合金膜(AlとTiとの合金膜)との積層膜で形成した。

【0070】

次いで、その上に透明導電膜を80〜120nmの厚さで形成し、パターニングすることによって画素電極947を形成する(図11(A))。なお、本実施例では、透明電極として酸化インジウム・スズ(ITO)膜や酸化インジウムに2〜20[%]の酸化亜鉛(ZnO)を混合した透明導電膜を用いる。

【0071】

また、画素電極947は、ドレイン配線946と接して重ねて形成することによって駆動用TFT963のドレイン領域と電気的な接続が形成される。

【0072】

次に、図11(B)に示すように、画素電極947に対応する位置に開口部を有する第3の層間絶縁膜949を形成する。第3の層間絶縁膜949は絶縁性を有していて、バンクとして機能し、隣接する画素の有機化合物層を分離する役割を有している。本実施例ではレジストを用いて第3の層間絶縁膜949を形成する。

【0073】

本実施例では、第3の層間絶縁膜949の厚さを1μm程度とし、開口部は画素電極947に近くなればなるほど広くなる、所謂逆テーパー状になるように形成する。これはレジストを成膜した後、開口部を形成しようとする部分以外をマスクで覆い、UV光を照射して露光し、露光された部分を現像液で除去することによって形成される。

【0074】

本実施例のように、第3の層間絶縁膜949を逆テーパー状にすることで、後の工程において有機化合物層を成膜した時に、隣り合う画素同士で有機化合物層が分断されるため、有機化合物層と、第3の層間絶縁膜949の熱膨張係数が異なっていても、有機化合物層がひび割れたり、剥離したりするのを抑えることができる。

【0075】

なお、本実施例においては、第3の層間絶縁膜としてレジストでなる膜を用いているが、場合によっては、ポリイミド、ポリアミド、アクリル、BCB(ベンゾシクロブテン)、酸化珪素膜等を用いることもできる。第3の層間絶縁膜949は絶縁性を有する物質であれば、有機物と無機物のどちらでも良い。

【0076】

次に、有機化合物層950を蒸着法により形成し、更に蒸着法により陰極(MgAg電極)951および保護電極952を形成する。このとき有機化合物層950及び陰極951を形成するに先立って画素電極947に対して熱処理を施し、水分を完全に除去しておくことが望ましい。なお、本実施例では発光素子の陰極としてMgAg電極を用いるが、公知の他の材料であっても良い。

【0077】

なお、有機化合物層950としては、公知の材料を用いることができる。本実施例では正孔輸送層(Hole transporting layer)及び発光層(Emitting layer)でなる2層構造を有機化合物層とするが、正孔注入層、電子注入層若しくは電子輸送層のいずれかを設ける場合もある。このように組み合わせは既に様々な例が報告されており、そのいずれの構成を用いても構わない。

【0078】

本実施例では正孔輸送層としてポリフェニレンビニレンを蒸着法により形成する。また、発光層としては、ポリビニルカルバゾールに1,3,4−オキサジアゾール誘導体のPBDを30〜40%分子分散させたものを蒸着法により形成し、緑色の発光中心としてクマリン6を約1%添加している。

【0079】

また、保護電極952でも有機化合物層950を水分や酸素から保護することは可能であるが、さらに好ましくは保護膜953を設けると良い。本実施例では保護膜953として300nm厚の窒化珪素膜を設ける。この保護膜も保護電極952の後に大気解放しないで連続的に形成しても構わない。

【0080】

また、保護電極952は陰極951の劣化を防ぐために設けられ、アルミニウムを主成分とする金属膜が代表的である。勿論、他の材料でも良い。また、有機化合物層950、陰極951は非常に水分に弱いので、保護電極952までを大気解放しないで連続的に形成し、外気から有機化合物層を保護することが望ましい。

【0081】

なお、有機化合物層950の膜厚は10〜400[nm](典型的には60〜150[nm])、陰極951の厚さは80〜200[nm](典型的には100〜150[nm])とすれば良い。

【0082】

こうして図11(B)に示すような構造の発光装置が完成する。なお、画素電極947、有機化合物層950、陰極951の重なっている部分954が発光素子に相当する。

【0083】

pチャネル型TFT960及びnチャネル型TFT961は駆動回路が有するTFTであり、CMOSを形成している。スイッチング用TFT962及び駆動用TFT963は画素部が有するTFTであり、駆動回路のTFTと画素部のTFTとは同一基板上に形成することができる。

【0084】

なお、発光素子を用いた発光装置の場合、駆動回路の電源の電圧が5〜6V程度、最大でも10V程度で十分なので、TFTにおいてホットエレクトロンによる劣化があまり問題にならない。また駆動回路を高速で動作させる必要があるので、TFTのゲート絶縁膜の容量は小さいほうが好ましい。よって、本実施例のように、発光素子を用いた発光装置の駆動回路では、TFTの半導体層が有する第2の不純物領域929と、第4の不純物領域933bとが、それぞれゲート電極918、919と重ならない構成にするのが好ましい。

【0085】

本発明の発光装置の作製方法は、本実施例において説明した作製方法に限定されない。本発明の発光装置は公知の方法を用いて作製することが可能である。

【0086】

また、本実施例では発光装置の作製方法のみについて示したが、薄膜トランジスタを有する液晶表示装置においても同様なレーザー結晶化を適用することができる。

【発明の効果】

本願発明により、特性を制御した薄膜トランジスタを作製することができた。また、基板を動かすことなくレーザービームを走査することができたので結晶化のスループットをあげることができた。さらにこの二つをあわせることにより、高性能な液晶表示装置およびEL表示装置を歩留まりよくかつ大量に作製することができた。

【図面の簡単な説明】

【図1】 本発明のレーザー照射装置および処理基板。

【図2】 楕円形のレーザービームにより結晶化された半導体膜。

【図3】 結晶の成長方向が制御された薄膜トランジスタ。

【図4】 実施形態3におけるビームエキスパンダ。

【図5】 実施形態7における本発明のレーザー照射装置。

【図6】 実施形態7における本発明のレーザー照射装置。

【図7】 実施例1の周辺駆動回路と画素回路が形成されたEL表示装置。

【図8】 実施例1の画素回路の拡大図。

【図9】 EL表示装置が有するTFTの作製工程を示す図。

【図10】 EL表示装置が有するTFTの作製工程を示す図。

【図11】 EL表示装置が有するTFTの作製工程を示す図。

【図12】 本発明のレーザー照射装置および処理基板。

Claims (5)

- 基板上に半導体膜を形成し、

レーザー装置からレーザー光を発振させ、

前記レーザー光を線状に成形し、前記半導体膜上で回転させることを、シリンドリカルレンズを回転させることにより行い、

前記レーザー光をf−θレンズにより前記半導体膜上で焦点を結び、

前記レーザー光を前記半導体膜上でガルバノミラーにより走査して前記半導体膜を結晶化し、

前記結晶化した半導体膜を薄膜トランジスタに用いる半導体装置の作製方法であって、

前記半導体装置は、第1の回路と前記第1の回路を駆動する第2の回路を有し、

前記第1の回路は、電荷移動方向が同一の方向に揃った複数の前記薄膜トランジスタを有し、

前記第2の回路は、電荷の移動方向が異なる複数の前記薄膜トランジスタを有し、

前記第2の回路の前記薄膜トランジスタの電荷移動方向に対して、斜めに前記レーザー光を走査し、走査方向に結晶成長させることを特徴とする半導体装置の作製方法。 - 請求項1において、前記第1の回路の前記薄膜トランジスタの電荷移動方向に対して、平行に前記レーザー光を走査することを特徴とする半導体装置の作製方法。

- 請求項1において、前記第1の回路の前記薄膜トランジスタの電荷移動方向に対して、垂直に前記レーザー光を走査することを特徴とする半導体装置の作製方法。

- 請求項1乃至請求項3のいずれか一項において、

前記レーザー装置は連続発振型のレーザー装置であることを特徴とする半導体装置の作製方法。 - 請求項1乃至請求項4のいずれか一項において、

前記レーザー装置を複数で用いることを特徴とする半導体装置の作製方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002264226A JP4439794B2 (ja) | 2001-09-10 | 2002-09-10 | 半導体装置の作製方法 |

Applications Claiming Priority (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2001273770 | 2001-09-10 | ||

| JP2001-273482 | 2001-09-10 | ||

| JP2001273482 | 2001-09-10 | ||

| JP2001-273770 | 2001-09-10 | ||

| JP2002264226A JP4439794B2 (ja) | 2001-09-10 | 2002-09-10 | 半導体装置の作製方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003158086A JP2003158086A (ja) | 2003-05-30 |

| JP2003158086A5 JP2003158086A5 (ja) | 2005-10-27 |

| JP4439794B2 true JP4439794B2 (ja) | 2010-03-24 |

Family

ID=27347471

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002264226A Expired - Fee Related JP4439794B2 (ja) | 2001-09-10 | 2002-09-10 | 半導体装置の作製方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4439794B2 (ja) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4838982B2 (ja) * | 2004-01-30 | 2011-12-14 | 株式会社 日立ディスプレイズ | レーザアニール方法およびレーザアニール装置 |

| KR100624427B1 (ko) * | 2004-07-08 | 2006-09-19 | 삼성전자주식회사 | 다결정 실리콘 제조방법 및 이를 이용하는 반도체 소자의제조방법 |

| JP2006134986A (ja) * | 2004-11-04 | 2006-05-25 | Sony Corp | レーザ処理装置 |

| US7393764B2 (en) | 2004-11-29 | 2008-07-01 | Semiconductor Energy Laboratory Co., Ltd. | Laser treatment apparatus, laser treatment method, and manufacturing method of semiconductor device |

| JP5019739B2 (ja) * | 2004-11-29 | 2012-09-05 | 株式会社半導体エネルギー研究所 | レーザ処理装置 |

| JP5210574B2 (ja) * | 2006-09-14 | 2013-06-12 | 株式会社半導体エネルギー研究所 | レーザ照射装置 |

| KR101777289B1 (ko) | 2010-11-05 | 2017-09-12 | 삼성디스플레이 주식회사 | 연속측면고상화(Sequential Lateral Solidification:SLS)를 이용한 결정화 장치 |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0220681A (ja) * | 1988-07-05 | 1990-01-24 | Fujitsu Ltd | レーザビームの集束方法 |

| JPH04256382A (ja) * | 1991-02-08 | 1992-09-11 | Matsushita Electric Ind Co Ltd | レーザ加工装置 |

| JP3027654B2 (ja) * | 1992-08-10 | 2000-04-04 | 新日本製鐵株式会社 | 鋼板へのレーザマーキング方法 |

| JPH0667119A (ja) * | 1992-08-24 | 1994-03-11 | Tokin Corp | 光アイソレータの作製方法 |

| JP3429129B2 (ja) * | 1996-04-26 | 2003-07-22 | 三菱電機株式会社 | 低温ポリシリコン薄膜トランジスタのレーザアニーリング方法 |

| JP2000243969A (ja) * | 1999-02-24 | 2000-09-08 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタとその製造方法及びそれを用いた液晶表示装置とその製造方法 |

| JP2000243968A (ja) * | 1999-02-24 | 2000-09-08 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタとその製造方法及びそれを用いた液晶表示装置とその製造方法 |

| JP2000243970A (ja) * | 1999-02-24 | 2000-09-08 | Matsushita Electric Ind Co Ltd | 薄膜トランジスタとその製造方法及びそれを用いた液晶表示装置とその製造方法 |

| JP4954359B2 (ja) * | 1999-02-12 | 2012-06-13 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP4731655B2 (ja) * | 1999-02-12 | 2011-07-27 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP3627096B2 (ja) * | 1999-12-28 | 2005-03-09 | 三菱電機株式会社 | レーザ加工機 |

-

2002

- 2002-09-10 JP JP2002264226A patent/JP4439794B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003158086A (ja) | 2003-05-30 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7682949B2 (en) | Laser treatment device, laser treatment method, and semiconductor device fabrication method | |

| JP3980465B2 (ja) | 半導体装置の作製方法 | |

| JP4127565B2 (ja) | 半導体装置の作製方法 | |

| JP3305961B2 (ja) | 多結晶シリコン薄膜トランジスタの製造方法 | |

| JP5412454B2 (ja) | 半導体装置の作製方法 | |

| JP5427753B2 (ja) | 半導体装置の作製方法 | |

| US6797550B2 (en) | Semiconductor device and manufacturing method therefor | |

| US8044372B2 (en) | Laser apparatus, laser irradiation method, semiconductor manufacturing method, semiconductor device, and electronic equipment | |

| US6844523B2 (en) | Laser apparatus, laser irradiation method, manufacturing method for a semiconductor device, semiconductor device and electronic equipment | |

| JP3968484B2 (ja) | 薄膜トランジスタの製造方法 | |

| JP2004179474A6 (ja) | レーザー照射装置 | |

| JP2004158720A6 (ja) | レーザー装置及びレーザー照射方法 | |

| JP4555568B2 (ja) | レーザ処理装置、レーザ処理方法および薄膜トランジスタの作製方法 | |

| JP2001156017A (ja) | レーザー装置及びレーザー光を用いた熱処理方法並びに半導体装置の作製方法 | |

| JP4439794B2 (ja) | 半導体装置の作製方法 | |

| US8603869B2 (en) | Method of fabricating thin film transistor having amorphous and polycrystalline silicon | |

| JP4637376B2 (ja) | レーザ照射装置及び半導体装置の作製方法 | |

| JP4519278B2 (ja) | 半導体装置の作製方法 | |

| JP3967259B2 (ja) | 半導体装置の作製方法 | |

| JP4841740B2 (ja) | 半導体装置の作製方法 | |

| JP2003224084A (ja) | 半導体製造装置 | |

| JP4463374B2 (ja) | 半導体装置の作製方法 | |

| JP2004193201A6 (ja) | レーザー照射方法 | |

| KR100719919B1 (ko) | 다결정실리콘 박막트랜지스터 형성방법 | |

| JP4531330B2 (ja) | レーザ光の照射方法 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050905 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050905 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20081001 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20090421 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20090615 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091006 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100105 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100106 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130115 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140115 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |