JP4171067B2 - 完全閉磁束作用を備える不揮発性磁気抵抗メモリ - Google Patents

完全閉磁束作用を備える不揮発性磁気抵抗メモリ Download PDFInfo

- Publication number

- JP4171067B2 JP4171067B2 JP52500696A JP52500696A JP4171067B2 JP 4171067 B2 JP4171067 B2 JP 4171067B2 JP 52500696 A JP52500696 A JP 52500696A JP 52500696 A JP52500696 A JP 52500696A JP 4171067 B2 JP4171067 B2 JP 4171067B2

- Authority

- JP

- Japan

- Prior art keywords

- magnetic

- layer

- memory

- coercive force

- conductor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/14—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements

- G11C11/15—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements using multiple magnetic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/56—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency

- G11C11/5607—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using storage elements with more than two stable states represented by steps, e.g. of voltage, current, phase, frequency using magnetic storage elements

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Mram Or Spin Memory Techniques (AREA)

- Semiconductor Memories (AREA)

- Hall/Mr Elements (AREA)

Description

本発明は、主として、磁気抵抗原理を使用する不揮発性、磁気性、ソリッドステートメモリに関する。電気、磁気、光分子、化学、及び生物を含むソリッドステートメモリ技術の概観は、1994年5月23日から同25日、カリフォルニア州パサデナ市にて開催された「ソリッドステートメモリ技術会議」の会議録中においてAshtonにより、及び1994年2月、National Media Lab発行の技術リポートRE−0013「ソリッドステートメモリの研究」中においてAshton等によって提供される。「ソリッドステートメモリ技術会議」の会議録および技術リポートRE−0013「ソリッドステートメモリの研究」をここに参考文献として挙げる。本発明は、さらに、各セルが記憶、読出し、及び書込み素子を有するメモリセルアレイに関する。さらに詳細には、本発明に係る磁気記憶素子は、閉磁束構造を使用し、また、磁束クロージャ方向から離れて回転させられる磁性を伴うことなく作用する。このことは、以下に説明する種々の利点をもたらす。

可動ディスク、及びテープを備える磁気大容量記憶装置は、コンピュータ産業において一般的なものである。このような磁気記憶装置の説明は、いくつかの操作上の問題、及び制限と共に、米国特許5,237,529中に記載されている。このような磁気体容量記憶装置は、実質的にパーマネント的な情報の記憶を提供するが、これらは、一般的に、比較的長いアクセス時間を要し、衝撃、振動に敏感であり、また、損傷、及び摩耗といった摩擦学上の制約を有している。

強磁性薄膜ランダムアクセスメモリは、不揮発性であり、高速なランダムアクセスを備えている。1960年代、強磁性膜メモリは、誘導読出しを使用していた。誘導読出しは、素子が小型化されると信号が小さくなりすぎるので、既にあきらめられていた。近代磁性膜メモリは、異方性磁気抵抗読出しを使用する。異方性磁気抵抗読出し(AMR)は、電流ベクトル及び磁性ベクトル間角度のサインの2乗に比例する。読出しは、成分が残余位置に対して垂直であるように磁性ベクトルが回転させられることを要求する。閉磁束作用は、絶縁ワード及びディジット導体周囲における2つの直交方向内にて磁束が閉じていることを要求し、問題は依然として解決されない。この結果、これらメモリは、一方向だけの磁束クロージャと共に作用させられ、磁性を非閉鎖構成中に回転させる。このことは、磁性クリープに起因する情報損失、大駆動電流要求、及び低信号といった多くの障害をもたらす。これについては、Daughton及びPohmの米国特許5,251,170にて議論されている。膜素子を小さくすればするほど、消磁フィールドが増加し、障害が大きくなる。

巨大磁気抵抗(GMR)は、AMRとは大きく異なる。GMRは、AMRよりも1桁大きくあり得ると共に、異質物質内、特に、層構造内においてだけ現れる。GMRの抵抗変化は、一領域内における磁性及び他領域内における磁性間角度のコサインに比例する。これは、電流−磁性間角度の2倍のサインであるAMRとは異なる。したがって、GMRに関する最大信号差は、一の層の磁性が180度変更された際に生じる。AMRにおいては、このことは何の変化ももたらさない。したがって、GMRメモリ素子を備えることにより、一軸に制限された磁性を伴い作用することが可能となり、また、その軸だけに沿う磁束クロージャが要求される。

GMR(時に、スピンバルブ効果と呼ばれる)は、そのほとんどがディスクの読み取りヘッド、あるいは、磁気フィールドセンサについての特許出願に関する多くの特許において議論されている。Diney等(米国特許5,159,513及び5,206,590)は、Cu、Au、またはAgの薄膜によって分離される2つの磁気層から構成されるGMRセンサについて述べている。磁気層の1つは、高保磁力Coである。2つの磁気層中の磁性は、互いに垂直のときに最大となる。サカキマ等(米国特許5,243,316)は、磁気センサ用、及び薄膜ヘッド用改良GMR素子のための物質について述べている。この特許では、高保磁力物質はCo−リッチFeCoであり、低保磁力物質は、Ni−リッチNiFeCoである。Cain等(米国特許5,301,079)は、その中に整列された磁化容易軸を備える2枚の低異方性磁気膜が耐電流非磁気伝導膜によって分離されている読取りヘッドについて説明している。この非磁気膜中の電流は、ディスク中ドメインのフィールドに対する最大感度を達成するために、2つの層内の磁性を反対向きに回転させる。サイトウ等(米国特許5,304,975)は、多数の交互に積層された磁気層、及び非磁気層から構成される磁気抵抗センサについて述べている。反転を助けるために、磁気バイアスが適用される層が含まれている。

A.V. Pohm及びC.S. Comstockは、題名「ソフトマルチレイヤーにおけるスピンバルブ効果のメモリインプリケーション(J. Appl. Phys 69, 5760, 1991)の論文を発表した。かれらは、ワード線に垂直なセンスディジット線を有するGMRメモリ素子について議論し、磁性は、ワード線中の電流によって磁束クロージャの軸外で回転させられる。このことは、大電流要求、及び、磁性クリープを通じた情報損失の危険をもたらす。

Kung等(米国特許5,343,422)は、GMRメモリ素子について教示している。これは、基板、及びその上に堆積されると共に非磁性金属伝導物質層によって分離される2つの強磁性物質層を有する長方形多層構造を備える。2枚の磁気膜の磁化容易軸は平行である。強磁性層の1層の磁性は、固定されており、他層の磁性は、「1」状態と「0」状態との間で方向を変えるために自由である。これは、ワード線及びセンスディジット線といった2本のストリップ線によって実行される。これら2本のストリップ線は、互いに垂直である。この発明は、閉磁束構造を提供せず、代わりに、磁壁を支持できない非常に小さい素子幅に依存するので、各膜は消磁され得ない。さらに、各メモリ素子は、2個の半導体ゲートを有しているので、素子は、恒久的に半選択パルスに煩わされる必要がない。素子当たり2個のゲートを有することによる1つの不利な点は、素子当たりの製造コストが高くつくことである。チップ当たりの総容量は、半減される。

半導体ランダムアクセスメモリ(RAM)はまた、当業者によって良く知られている。RAMは、一般的に、多くの周辺回路と共にチップ上に集積されているメモリセルセットを備えている。RAMは、例えば、Porat等のディジタル技術入門(Introduction to Digital Techniques)John Wiley, 1979に説明されている。一般的に、RAM回路は、アドレシング(アクセスする指定位置の選択)、電力供給、ファンアウト(多数のロードに対する信号の転送)、及び使用可能な出力信号を生成するために必要な条件設定といったいくつかの機能を実行する。RAMメモリでは、アドレシング方式は、セル位置に依存しないアクセス時間で要求セルに対するランダムアクセスを許容する。そして、選択部分が使用のために引き出される。RAMは、一般的に、CPUに適合し得るほど十分に速いが、大容量記憶装置として用いられるには高価すぎる。さらに、スタティックRAM(SRAM)及びダイナミックRAM(DRAM)は共に、メモリへの電力供給が失われるとその内容が失われる揮発性メモリである。DRAMはまた、周期的なリフレッシングを必要とする。したがって、DRAM、または、SRAMを長期記憶装置として使用することは現実的でない。

電気的にプログラム可能なリードオンリメモリ(EPROM)、及びリードオンリメモリ(ROM)は、RAMとは異なり不揮発性メモリである。しかしながら、これらのメモリはリフレッシュサイクルを必要としない一方で、1度だけしかプログラムすることができないという明らかな短所を有している。電気的に変更可能なリードオンリメモリ(EAROM)または、電気的に消去可能なリードオンリメモリ(EPROM)、あるいは、FLASH(応用最適化EPROM)といった、繰り返し書込み可能な他の不揮発性半導体メモリは、長期記憶装置として磁気メモリが有する信頼性をおよそ提供することができない。

以上説明したように、ランダムアクセス、速度、及びRAMの耐久性を提供するが、不揮発性であり、待機電力源、または、周期的リフレッシュ電力源のいずれも必要としない改良メモリがパーマネント記憶アプリケーションとして要求されている。

発明の概要

本発明によれば、巨大磁気抵抗を示す多層記憶素子を使用するメモリセルが記載されている。記憶素子の構造は、書込み動作、及び非破壊読出し動作を含むメモリセルの全作用を通じて、閉磁束パスが有効に維持される構造である。

異方性磁気抵抗(AMR)は、電流が物質の磁性に対して垂直でなく平行に流れるときの抵抗の相違に対応する。異方性磁気抵抗は、種々の強磁性薄膜メモリに用いられている。近年発見された磁気抵抗効果は、巨大磁気抵抗(GMR)として知られている。GMRは層構造、または、非等質構造中においてのみ発生するのに対して、AMRは等質バルクサンプル中で発生し得るので、GMRは、AMRとは異なる効果である。GMRは、磁性方向が層から層へと変化する所で発生する。GMR効果は、AMR効果よりも20倍以上大きくなり得る。さらに、AMR読出しのために最適化されたメモリセル設計は、GMRにとっては最適でなく、GMRのために最適化された設計はAMR信号を全く生成しない。

巨大磁気抵抗は、本発明に係る種々の発明の実施の形態の構造、及び方法において用いられる。巨大磁気抵抗効果は、メモリアプリケーション、詳細には、読み取りセンサ、記憶素子、及び全金属スピントランジスタのために用いられる。多層薄膜中における巨大磁気抵抗効果が、バルク物質、及び単層薄膜によって引き出される従来の異方性磁気抵抗効果よりも20倍以上大きいことが発見されているという事実にある程度起因するいくつかの利点が、巨大磁気抵抗を使用する本発明に係る発明の実施の形態によって認識される。

本発明に係る1つの発明の実施の形態によれば、メモリセルは、巨大磁気抵抗を示す多層記憶素子を有している。記憶素子は、1つ以上の次元中に閉磁束構造を有しており、個々の層の中の磁性ベクトルは、記憶素子の全作用段階を通じて、実質的に1つ以上の次元に閉じこめられる。メモリセルは、記憶素子から情報を読み出す手段、記憶素子へ情報を書き込む手段、及び記憶素子に対して選択信号を適用するための選択導体を有し、これにより、記憶素子からの読出し、記憶素子への書込みが可能になる。より詳細な発明の実施の形態では、読出し、及び書込み手段は、第1構造と電気的に結合されている読出し導体と、読出し導体、及び第1構造とは電気的に絶縁されている書込み導体とを有している。2つめの詳細な発明の実施の形態では、読出し、書込み手段は、第1構造と電気的に結合されている単一の導体である。

本発明に係る他の発明の実施の形態では、各々が記憶素子としても作用する多層巨大磁気抵抗素子を備えるサブミリメータトランジューサアレイ(センサ/アクチュエータ)が、チップ上にサポート電子回路と共に、あるいは、複合体として形成されている。このパーマネントランダムアクセスメモリ(PRAM)は、各記憶素子が閉磁束構造を有する、サブミリメータ情報セルのアドレス可能アレイ、書込み素子、及び読出し素子を単一基板上に有している。アドレシング方式は、アレイ中のセル位置に実質的に依存しないアクセス時間での、各セル全てに対するランダムアクセスを提供する。これにより、PRAMは、パーマネント記憶装置の磁気メモリ能力に、半導体メモリの耐久性及び速度を結合する。各トランジューサは、記憶装置に対する読出し、書込みのために、例えば、従来のロー/カラムアドレシングを用いるスイッチング回路構成により明確に関連付けられた位置及び時間で作動させられる。

本発明の実施の形態の1つにおける装置は、巨大磁気抵抗読出し素子、以下、「GMRトランジューサ」と呼ぶ、を備える。本発明の詳細な発明の実施の形態によれば、データ読出しは、(1)好適に内部接続されている、巨大磁気抵抗記憶媒体の状態を検出し得るサブミリメータトランジューサ、及び(2)個々の選択GMRトランジューサを作動させるための電子スイッチングを組み合わせることにより実行される。トランジューサが作動させられる空間位置は、読み出しされるメモリ位置に対応している。選択GMRトランジューサが作動させられる時間は、全データブロックが一時にアクセスされ得るよう、実質的に同一となるよう選択され得る。

前述のように、巨大磁気抵抗(すなわち、多層薄膜)を示す物質の使用は、いくつかの利点をもたらす個々のメモリ素子に関する読出し信号の大きさを増加させる。先ず、大きな読出し信号は、より大きなアレイ構造を許容する。それはまた、単一センス線を用いて読出しされるより多くの数のビットを許容する。さらに、S/N比が増加するので、高速な読出しが達成され得る。これらの利点に加え、巨大磁気抵抗は、幅広い動作温度範囲で実現可能である。

巨大磁気抵抗の最も重要な利点は、おそらく、何時でも、また、メモリセルの全作用段階を通じて、完全な磁束クロージャを許容することにある。換言すれば、書込み中、あるいは、読出し中のいずれにおいても消去されるフィールドは存在しない。このことは、AMRを採用するメモリには当てはまらない。GMR素子を用いることにより、層の一つの磁性が180度変更されるとき、最大抵抗変化、あるいは、信号が発生する。したがって、磁束を2本でなく、1本の軸周りに近接させることだけが要求される。得られる結果は、(1)消去フィールドの不存在、(2)磁性クリープに起因する障害となる問題の不存在、(3)低電力要求、(4)大きな信号である。

本発明は、本質的に、短いアクセス時間、衝撃及び振動に対する高耐久性、高信頼性、メンテナンスフリーオペレーション、ヘッドクラッシュの不存在とを有すると共に、自己調整するので、ディスク、及び、及びテープシステムよりも優れている。本発明は、パーマネント的記憶媒体を提供するので、DRAM、及びSRAMよりも優れている。本発明は、全ビット変更可能であり、高速であり、また、事実上、無制限の消去サイクルを有しているので、FLASHよりも優れており、最後の利点は、MRAMに対する利点でもある。

本発明は、明細書の残りの部分、及び図面を参照することにより、さらに理解されよう。

【図面の簡単な説明】

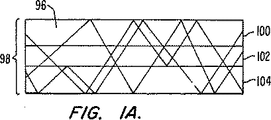

図1aは、上層、及び下層が磁性導体であり、中間層が非磁性導体である単一GMR三層膜を図示する。

図1bは、上層、及び下層の磁性が逆向きである図1の三層膜を図示する。

図2は、2つの磁気層が異なる保磁力を有するGMR三層膜についての主軸ヒステリシスループを図示する。

図3aは、「0」状態に対応するGMR三層膜についての従軸ヒステリシスループを図示する。

図3bは、「1」状態に対応するGMR三層膜についての従軸ヒステリシスループを図示する。

図4aは、「1」状態のGMRメモリセルからの非破壊読出し信号を図示する。

図4bは、「0」状態のGMRメモリセルからの非破壊読出し信号を図示する。

図5は、発明の実施の形態の1つにおける閉磁束記憶素子を備えるGMRPRAMメモリセルの断面図である。

図6は、ワード線、及びディジット線(ディジット線に隠れるのでセンス線は図示されていない)に関連する6個の図5に示すGMRPRAM記憶素子を図示する。

図7は、GMR素子が読出し、記憶の双方について機能するGMRPRAMメモリセルの概念図の参考例を図示する。

図8は、読出し、及び記憶の2つの役割を果たすため、GMRPRAMがどのようにしてワード、ディジット、及びセンス線と接続されるかを概念的に図示する。

図9は、デュアルロールGMR素子を備える16個のGMRPRAMメモリセルアレイの現実のジオメトリを図示する。

図10は、本発明に係る発明の実施の形態の1つに従い製造されたGMRPRAMの断面図である。

図11は、本発明に係る詳細な発明の実施の形態に従う6セルGMRPRAMの平面図である。

図12は、超密度テラビットメモリのための閉磁束GMRPRAMセルの縦方向図(b)、及びその部分分解図(a)を図示する。

図13は、図12に図示する16個のGMRPRAM素子アレイを図示する。

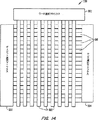

図14は、本発明に係る発明の実施の形態の1つに従い設計されたGMRPRAMモジュールを図示する。

発明の実施の形態

内容

I.定義

II.異方性磁気抵抗(AMR)を備えるメモリ

III.巨大磁気抵抗(GMR)を示す物質

IV.ソフトスクエアループフェライトを含むGMRPRAM

V.基板に対して垂直な軸を備えるトロイダルPRAM素子

VI.基板に対して平行なクロージャ軸を備えるPRAM素子

VII.垂直GMRを備える超小型PRAM素子

VIII.製造

IX.代表的な適用例

X.結論

I. 定義

本明細書中、以下の用語は以下の一般的な意味を有するものとする。

「作動」は、選択機能を実行するためのトランジューサをアドレシングするステップ、及びトランジューサのオペレーションステップを意味する。巨大磁気抵抗セルを特定する場合には、作動は、アドレシング、及び磁性によって変化するセル抵抗の検出を意味するものとする。

「異方性磁気抵抗」(AMR)は、いくつかの伝導性磁性物質が物質中の電流及び磁性ベクトル間の角度関数として示す抵抗に関する異方性を意味する。異方性磁気抵抗の抵抗成分は、その角度のサインの2乗に比例する。

「保磁力」は、物質の平均磁性を0に減らすために要求される磁性とは反対方向における外部から加えられる磁界を意味する。これは、時に「保磁力」あるいは、保磁力フィールド」と呼ばれる。

「巨大磁気抵抗」(GMR)は、連続磁気層中における磁性の相対方向に依存する、磁気多層膜を通じてパセージに現れる伝導性電子の抵抗の相違を意味する。この差は、伝導性電子の散乱が局部磁性に関連するスピン配位に依存するので発生する。一般的に、連続層間における磁性が平行なとき、散乱は弱くなり、そして、得られる抵抗値は小さくなる。特に、非磁気伝導層によって分離されている2つの異なる磁気層を備える多層膜は、2つの物質が平行でなく、逆向きに磁化されるとき大きな抵抗値を有する。

「情報セル」は、記憶素子、書込み素子、読出し素子、及びサポート電子回路を含むPRAMセルを意味する。

「磁気トランジューサ」は、記憶のための磁性を生成し、あるいは、読出しのための磁性フィールドを検出するトランジューサを意味する。

「メモリセル」は、「情報セル」と同義である。

「ソリッドステートメモリ」は、可動部品を備えないメモリを意味する。

「スピントランジューサ」は、そのゲートが磁気フィールドによって作動させられるGMR式スイッチング装置を意味する。

「サブミリメータ」は、ミクロンスケールからナノメータスケールまでを意味する。

「薄膜技術」は、(例えば、真空蒸着、スパッタリングによる)支持基板上への電気素子の形成を意味する。

「トランジューサ」は、物理量(例えば、システムの圧力、磁気フィールド、湿度等)を検出、あるいは、測定するために用いられる装置、及び/または、システム上の物理量を活性化し、あるいは、物理量を伝達するために用いられる装置を意味する。詳細な発明の実施の形態に従って用いられるミクロンスケール及びサブミクロンスケール間におけるトランジューサは、データビットの存在、あるいは、不存在を検知するよう結合磁性物質の特性を検出するために、また、データビットの存在、または、不存在を伝達するよう磁性物質を活性化するために用いられるトランジューサアレイである。

II. 異方性磁気抵抗を備えるメモリ

パーマネントランダムアクセスメモリ(PRAM)は、データを保持するために待機電力、及び、周期的リフレッシュ電力を共に必要としないランダムアクセスメモリである。PRAMは、公知であり、時に膜メモリ中に用いられる、異方性磁気抵抗(AMR)を用いて形成され得る。AMRは、多くの層を必要とせず、僅かに1枚の膜だけを必要とし、抵抗の差は、電流方向に対して平行な磁性に対する電流方向に対して垂直な磁性について発生する。

1次元にだけ閉磁束構造を備えるメモリ素子の形成は、二次元に閉磁束構造を備えるメモリ素子の形成よりもかなり容易である。メモリ素子の磁性ベクトルが、一次元(例えば、平行、及び逆平行)に閉じられている場合には、一次元の閉構造で十分である。しかしながら、異方性磁気抵抗信号は、磁性が実質的に90度回転することを要求し、この結果、閉磁束構造が要求される場合には、二次元のクロージャを要求する。

オープン構造は、膜メモリ中に不完全スイッチング、及び、好ましくない障害をもたらす。例えば、Gerald Granleyによる、CA、パサデナ市で5月23日から同25日開催された、1994ソリッドステートメモリ技術のスプリングカンファレンスの会議録97ページにある、このような障害をもたらす問題は、AMRメモリを100,000サイクルの後、不良にしてしまうという記述を参照。このような緩やかな障害不良は、磁性クリープと呼ばれている。これは、コヒーレント磁性ローテーション、あるいは、ウオールモーションスイッチングのいずれよりも低いスレッショルドを有するスイッチングの超低速モードである。磁性クリープによって切り替えるために、膜に関する多くの繰り返しパルスを必要とする。特に、磁化困難軸フィールドが変更されるとき、磁化容易軸フィールドと結合する磁化困難軸成分を有する多くのパルスを必要とする。磁化困難軸パルスは、磁性を前後に回転させ、磁化容易軸フィールドは、他の方向の上にある一の方向中におけるウオールモーションを好むエネルギー差を提供する。高密度では、全非閉磁束ジオメトリからの消磁フィールドは、非常に大きく、他のパラメータを独占してしまう。磁束構造が閉じていない場合には、近傍ビットもまた、クリープに寄与する。

磁束クロージャ方向から実質的に90度切り替えられる磁性を必要とするメモリ設計には、いくつかの深刻な短所が存在する。非閉エッジの形状異方性を克服するために巨大ドライブフィールドが要求される。Daughton及びPohmの米国特許5,251,170中にて述べられているように、磁性の除去は、信号損失を促進させる。磁性のローテーションは、次第にセル中の情報を喪失させる磁性クリープをもたらす。これとは逆に、磁束クロージャからの逸脱に磁性が要求されない場合には、メモリ素子は、論理的に、フェライトコアメモリ、あるいは、従来型のディスクドライブを備えた磁気メモリと同程度の、多くの誤りのない読出し/書込みサイクルを有する。後者は、1015サイクルまで誤りがないことが知られている。

AMRに基づくメモリ設計は、単層AMR膜をGMR多層膜と置き換えても機能し得るが、最適な設計ではない。GMRの全ての利点を得るためには、GMRメモリ設計は、磁束クロージャ軸から離れた磁性ベクトルの回転を回避しなければならず、これにより、駆動電流が低減され、また、磁性クリープによりもたらされる障害問題が回避される。

III. 巨大磁気抵抗を示す物質

近年における巨大磁気抵抗(GMR)の発見は、電子工学における革命的な変化である。GMR効果は、磁性金属と非磁性金属の交互層から構成される超薄膜構造といった、ある一定の多層中にて生じる。膜は、数百ナノメータ厚さ程度である。各区分が順序正しい(L1/L2/.../Lm)いくつかの層で構成されている、このような多重区分、多層GMR膜は、既に報告され、また、パラメータ的に研究されている。ヤマモト等[H. Yamamoto, T. Okuyama, H. Dohnomae及びT. Shinjo、J. Magn. & Magn. Mat. 99(1991)243]は、4層10%GMR、15区分構造(NiFe/Cu/Co/Cu)×15を、また、Petroff等[F. Petroff, A. Barthelemy, A. Hamzic, A. Fert, P. Etienne, S. Lequien及びG. Creuzet、J. Magn. & Magn. Mat. 93(1991)95]は、18層の(Fe/Cr)についての16%GMRをそれぞれ室温で発見した。

GMRは、主にバルク中に現れる異方性磁気抵抗(AMR)とは異なる効果である。AMRは、従来から知られており、GMRよりもかなり小さい効果である。AMRの源は、強磁性物質原子中のスピン軌道カップリングに存在する。それは、平行、及び逆平行配置を区別しない。GMRの抵抗変化は、磁気層近傍の磁性ベクトル間角度のコサインに比例する。上層、及び下層膜が平行に磁化されるときよりも、逆平行に磁化されるときの方が構造抵抗は大きくなる。電流が基板に対して平行であるか垂直であるかにかかわらず、このことは正しい。

あらゆる所定多層構造のGMR値は、電流が基板に対して平行に通過するか、垂直に通過するかに依存する。磁気抵抗は、抵抗のわずかな変化として説明される。膜平面に対して電子が平行に進行するときよりも、垂直に進行するとき、GMRはより大きくなる。それにもかかわらず、ほとんどの研究は、膜平面に対して平行な電流を用いて行われてきた。その理由は、メモリ素子の幅対厚さ比(形状要因)が非常に大きい場合、膜平面に対して垂直な抵抗は非常に低いからである。しかしながら、精密印刷が、幅が厚さと比較し得る素子を製造する能力を有する場合には、理にかなった平面対垂直抵抗、及び、平面内抵抗よりも格段に高いGMRに関するパーセンテージ変化を備えるメモリ素子を実現し得る。AMRは、物質によっては、約1%の効果である。平面内GMRは、AMRよりも1桁大きな読出し信号をもたらす。このことは、読出し信号をより大きくし、(信号対ノイズ比が高いので)より低廉な電子回路、及び、AMR式設計よりも高速な読出しを許容する。平面に対して垂直なGMRは、平面内GMRよりもさらに大きい。

GMRは、メモリアプリケーションに関して非常に魅力的な特性を有している。層状膜は、それを有することにより独立して切り替わる記憶素子として機能させられ得る。詳細な発明の実施の形態では、異なる組成、保磁力、及び異方性フィールドを備える連続磁気層を有することにより、それらの独立した切替を許容するために十分に弱い交換カップリングと結合される連続層変換を有することにより、及びワード線上の電流が遮断されたとき低保磁力膜を再設定するために磁気層間における十分に強力な交換カップリングを確実にするためのまさに適当な厚さに非常に近い非磁気伝導層を有することにより、層状膜は独立して切替えさせられる。したがって、低保磁力層の保磁力は、高保磁力層の保磁力よりも十分に低くなるよう選択されているので、低いフィールドにて低保磁力層を切り替えることが許容される。

最も簡単なGMR多層膜は3層である。図1a及び図1bは、GMRを示す単一3層膜98中の電子パス96を図示する。中央層は非磁気導体102である。上層100及び下層104は強磁性である。図1aにおける上層、及び下層中の磁性は、図1bにおけるそれが逆平行であるのに対して平行である。一般的に、GMR膜は、N層の磁気層、及びN−1層の非磁気伝導層を備えており、図1a及び図1bは説明を簡単にするための例示にすぎない。

図2は、GMR変換カップル3層膜の主ヒステリシスループを図示する。2つの磁気層130、134は、非磁気層132によって分離されている。2つの磁気層は、層130が高保磁力を有するように、少なくとも両者の間における交換カップリング分だけ異なる高保磁力であり、層134は低保磁力を有する。層断面136は、ループの各部分における磁性を図示する。上層130、及び下層134が同一方向で飽和されている右上象限から開始する。応用フィールドHが実質的に0に減少させられる場合には、左上象限の断面によって図示されるように、先ず低保磁力を有する層が方向を逆に切り替える。フィールドが低保磁力膜の保磁力とカップリングフィールドの保磁力との和と等しくなると切替が起こる。

続けて図2を参照すると、応用フィールドHが負方向に増加させられると、左下象限に示されるように、高保磁力を有する層が方向を切り替える。この切替は、フィールドの大きさが高保磁力膜の保磁力から交換カップリングの保磁力を引いた差と等しくなると生じる。したがって、このような膜において切替は、2段階プロセスで実行される。

交換カップルを利用したGMR膜を使用する実施の形態において重要な特徴は、従ヒステリシスループ及び比破壊読出しの効果に関連する。図3aは、高保磁力膜136が右向きに磁化されるときの「1」状態として知られている従ループを図示する。これとは逆に、図3bは、高保磁力膜136が左向きに磁化されるときの「0」状態として知られている従ループを図示する。

交換カップルを利用したGMR膜を使用する実施形態に従い設計されたメモリセルの読出しは、従来技術における磁化薄膜において使用される読出しとは異なる。この発明の実施の形態では、センス線に沿う1つの選択ビットの値は、ワード線の1つのフィールドを適用することにより取得された磁性変化に対応する抵抗変化を計測することにより非破壊方式で決定される。フィールドの適用は、低保磁力膜を一時的に切り替える。この例では、低保磁力膜の中で変換バイアスが低保磁力層の保磁力を超え、ワード線上の電流が遮断されると、この膜は再設定され、または、元に戻される。容量ノイズ、及び誘導ノイズは、読出しサイクル中に生じる。これらは、ダミー線、及び差動センスアンプを使用することにより最小化され得る。更なるノイズ排除は、センス信号の波形の差を外挿することにより達成され得る。ワード電流と同一波形を有するノイズも含まれる。図4a及び図4bは、三角ワード電流182が適用された際の抵抗信号を図示する。図4aは、「0」状態に対応する信号を図示し、図4bは、「1」状態に対応する信号を図示する。

信号波形は、保磁力に対する変換バイアスの割合によっていくらか変化するが、信号波形は、容量ノイズ、及び誘導ノイズとは異なるので、電気的に識別可能である。

GMRは、一般的に、多層構造中に見られるが、非磁気、または、弱磁気マトリックス中の単一ドメイン粒子から構成される好適な異種合金システム中にも発見され得る。そのような合金の1つに、Berkowitz等の「異種Cu−Co合金における巨大磁気抵抗」Physical Review Letter, vol. 68, no. 25,1992年6月22日、及びXiao等の「非多層磁気システムにおける巨大磁気抵抗」Physical Review Letter, vol. 68, no. 25,1992年6月22日中にて議論されているCu−Coがある。

IV. ソフトスクエアループフェライトを含むGMRPRAM

上述したように、詳細な発明の実施の形態は巨大磁気抵抗を用いる。図5は、巨大磁気抵抗検出多層膜を使用するセルの1例を図示する。図5からメモリセル198は、一般的に、軟鉄200からなる2つの要素、磁束クロージャ用パーマロイからなる1つの要素、及び巨大磁気抵抗多層214からなる第4の要素を有する長方形形状であることが判る。ソフトスクエアループフェライトの使用は、ミリアンペアよりも小さい小駆動電流、及び不等辺フェライトよりも高速な読出しを許容する。本発明によれば、メモリセルの4要素は、旧式コアメモリ素子に近似する閉磁束設計である。膜は、コアの周りに時計回りに磁化され得、あるいは、半時計回りに磁化され得る。コアを横断するのは、ワード線206及びディジットセンス線210からなる、フィルム上に堆積された2本のストリップ線である。層204,208,212は、絶縁層である。センス線(図示しない)は、巨大磁気抵抗多層214と電気的に結合されており、また、ワード線206、及びディジット線210の双方から絶縁されている。

図6は、アレイ中における6個のGMRメモリセルを図示する。セルは軟鉄素子230、及びパーマロイ層232と共に図示されている。ワード線236及びディジット線234は図示されているが、センス線はディジット線234によって覆われるので図示されていない。この実施の形態では、ディジット線とセンス線とは異なるものである。

本発明の実施の形態においては、2層中の磁性が平行から逆平行に変化するとき、構造の巨大磁気抵抗が変化することが重要である。本発明の実施の形態におけるメモリセルの読出しを取得する際、読み出されるセルと交差するワード線上に半選択電流が適用される。この電流は、セルを切り替えてしまうほど強力であるべきではないが、パルスのフィールドがセル中に存在する磁性と反対である場合、及びその場合だけは、多層巨大磁気抵抗膜の低保磁力膜を反転させるために有効である。

本発明の実施の形態によれば、ビットは、抵抗変化が正のワードパルスと共に起こるか、負のワードパルスと共に起こるかを決定することにより、「1」あるいは「0」のいずれかとして読み出しされる。図4a及び図4bは、この作用をグラフで表したものである。各ワード線は特定センスラインと一度だけ交差することに留意すべきである。したがって、ワードパルスの間、センス線上の1ビットだけが関連する抵抗変化を有する。この結果、所定センス線上に多くのビットを有することが可能になり、いつでも選択ビットを読み出すことができる。さらにまた、その性質上、読出しは非破壊的であるので、信号ノイズ比問題が存在する場合には、周知の信号処理方法を使用して情報を引き出すため複数パルスが使用され得る。さらに、センス線上の信号波形は、ワードパルスのそれとは異なる。したがって、信号は、ワード線上の容量ノイズと識別され得る。ダミーセンス線は、要求信号が要求センス線の信号とダミー線の信号との差となる所で用いられるのが好ましい。

V. 基板に対して垂直な軸を備えるトロイダルPRAM素子

図7にトロイダルPRAM素子を用いたメモリセルの参考例を示す。この参考例は、基板に対して垂直な軸を備える平らなトロイドである。基本磁気構成はリング周りに非磁気ギャップを備える磁束クロージャを有するコアである。図7は、関連するGMRコア248、ワード線250、ディジット線252、及びセンス線254を備える4個のPRAMセルを図示する。消磁フィールドは、磁性が円周方向から著しく逸脱することを防止する。旧式の2次元コアメモリのそれと同様に、駆動線はコアの中心を通過する。旧コアメモリとは異なり、センス線254は、巨大磁気抵抗を示す物質からなるコア248と電気的に接続されている。この構成は、通常の異方性磁気抵抗効果を示す物質に対しては機能しない。この発明の実施の形態では、GMR膜は、記憶素子として読出し素子と同様に作用する。高保磁力及び低保磁力の2つの磁性物質からなるGMR膜の存在が、このような2つの使用方法を許容する。

磁気膜は、エッチング済駆動線の段差を有する表面上よりも、平滑な未処理表面上に堆積されることが好ましいので図7は概念図である。したがって、磁気コア底面上の駆動線部分は、コア自身よりも大きいことが好ましい。また、この発明の実施の形態では、上部駆動線は、コア中心を介して下部駆動線と接続している。これは、図8に図示されている。

図8に図示されているメモリセルアレイは、先ず、下部ワード線270を配置することによって製造される。次に、絶縁層272の一つ(ワード線282の下)を配置し、エッチングする。そして、下部ディジット線274が堆積され、エッチングされる。次に、絶縁層272の1つが堆積される。コア276が配置され、各コアは、2つの底辺伝導層270,274の交差によって規定される幅広平面上にある。そして、底辺層に対するホール(ホール278は下部ワード線270に達し、また、ホール280は下部ディジット線274に達している)がエッチングされる。上部ワード線282、及び上部ディジット線284は、それぞれ、ホール278、280を通じて下部と接続されるように製造される。最後に、センス線286が堆積される。全体で、4層の金属層、及び3層の絶縁層を堆積する7つの堆積ステップが存在する。図8のA−A図は、破線A−Aに沿う断面図である。製造については、後述する章の1つにて詳述する。

発明の実施の形態の1つに従うメモリセルアレイの現実の形状が図9に図示されている。コア306、ワード線300、ディジット線302、及びセンス線304を備える16個のGMRメモリセルが図示されている。コアは、長方形に形成されている場合、かなり緊密に集約され得る。写真印刷プロセスにて達成され得る最小機能寸法が中心間隔2μmの1μm線の場合には、メモリセルは中心間隔が6μm×8μmである。写真印刷解像度が10倍細かければ、メモリセルのセンタ間間隔、及び電流要求も10だけ減少し、メモリ密度は100倍となる。写真印刷技術の現在の進歩が続くならば、(250nm(あるいは、120nm)単位の)最小機能寸法が比較的短期間に可能になるはずである。したがって、本メモリ密度は、写真印刷技術の制限によってだけ制限されている。さらに、完全磁束クロージャに起因して、本メモリアレイは磁気膜メモリに関連する通常の問題に悩まされることはない。

このようなメモリの電流要求は、特に魅力的である。形状が上述した通り(中心間隔が6μm×8μmのセル)であるならば、2つの層は、それぞれ20e.及び50e.の保磁力を有し、カップリングフィールドは10e.であり、したがって、最大電流は全ての線において4mAである。

VI. 基板に対して平行なクロージャ軸を備えるPRAM素子

図10には、図5に図示するものより少ない製造ステップ、及びよりコンパクトなGMRPRAMセル400を図示する。磁束カップリングは、底部磁気膜412から薄絶縁ギャップ404を通って上部膜402に到達し、再び戻る。側面における形状は平面状トロイドと同じである。軸は膜平面中に存在する。この薄絶縁ギャップにより、磁束クロージャは、図5に図示する発明の実施の形態ほど完全ではない。磁気膜間のカップリング型は、強磁性カップリング、反強磁性カップリング、あるいは、ストレーカップリングのあらゆる組み合わせであり得る。

PRAMセル400は、パーマロイ保持層402、絶縁膜404、ディジット線406、ワード線408、絶縁層410及びGMRを示す多層記憶膜412を備えている。GMR膜412をパーマロイ保持層402から分離する絶縁膜404は、2つの金属層を短絡しないできるだけ薄い膜厚を有することが要求される。50オングストロームの厚さが好ましい。パーマロイ保持402は、ストリップ線周りの記憶膜412の一端から他端まで磁束パスを完成させるために十分な厚さを有するべきである。それの組成は、線状ドメインを避け、また、低保磁力を有するために、僅かに正の磁歪を有するよういくらか鉄リッチである。GMR多層膜412は、(NiFe/Cu/Co/Cu)の15層である。堆積の続きは以下の通りである。基板上の第1堆積物は、多層GMR膜412である。この後、他の絶縁層410によって分離される絶縁層410及び2つの駆動線406,408が、堆積され、パターン化される。駆動線406,408の構成は、6個のPRAMセル400からなるアレイ420を図示する図11に図示されている。次のステップは、GMR膜412をパーマロイ保持402から分離するためにアセンブリ上へ超薄絶縁膜404(約50Å)を堆積させる。パーマロイ保持402は、最後の堆積層である。図10及び図11に図示される設計は、製造費が低廉であり、小電流で機能し、所定マスク機能寸法に対して高密度を備え、AMRを使用するメモリセルの10倍の読出し電圧を有するはずである。この設計の変更では、パーマロイ保持402を実質的に記憶素子412と同一のGMR多層膜で置き換える。この結果、絶縁ギャップ404が取り除かれる。

図11から、本発明における2本の駆動線は、直交せず平行であることが判る。直交駆動線は、磁束クロージャ方向から磁性を離隔させるので、これは非常に重要である。本発明では、磁束は常時、閉じられている。

VII. 垂直GMRを備える超小型PRAM素子

超高密度PRAMは、現在利用可能な高解像度ツールアプリケーション、及び全金属スピントランジスタを介して達成され得る。高解像度ツールの詳細例としは、次に説明するチップ式顕微鏡がある。この例示は、本発明を制限するために用いられるものではない。

A. 走査プローブ顕微鏡

ナノメータスケールで表面を変化させる能力を備える走査プローブ顕微鏡は、非常に高い密度でのデータ記憶用潜在能力を提供する。走査トンネル顕微鏡(STM)及び原子力顕微鏡(AFM)を含む、ディジタルメモリに対する2つの新規解決手段が、既に提案されている[John Maminによる,1994年ソリッドステートメモリ技術会議、5月23日〜同25日までCA、パサデナで開催の会議録121〜33ページ]。これらの装置では、表面付近、または、表面と接触する可動チップが、読出し/書込み操作の間、表面を写すため/変化させるために用いられる。図12〜図14に図示されているPRAM設計は、これら顕微鏡の非常に優れた能力を、ソリッドステートメモリの操作上、コスト上の利点を備える構造的特徴と組み合わせる。これら高解像度ツールによって可能になる超精密印刷は、超大規模PRAMチップの製造に用いられ得る。STMプローブはまた、アレイ中に製造され得ると共に、米国特許5,237,529に記載されているようにメモリアプリケーション中のトランジューサとして用いられ得る。

平面内GMRPRAMアレイの特性上の制限は2つある。第1に、印刷上の制約によってもたらされる密度限界、及び従来の制御電子回路により取られる比較的大きな領域である。第2に、制御電子回路に起因する速度限界である。PRAMを製造するための操作プローブ顕微鏡(SPM)といった高解像度技術の使用は、PRAMセル最小機能寸法の制限を、現在、従来印刷技術によって達成され得るものよりも少なくとも1桁だけ低減させる。SPMの使用はまた、出力を大幅に増加させ、駆動電流を大幅に低減させる形状要素を備えるメモリ素子の製造を許容する。

第2の制限、すなわち、制御電子回路速度は、全金属スピントランジューサのアプリケーションを介してGMRアレイに向けられる。本発明によれば、全金属スピントランジューサを備える垂直GMRPRAM素子は、AMR設計、あるいは、平面内GMR設計と比較して、より高い密度、及びより高速な読出しを提供する。

GMRメモリは、種々の補助周辺電子回路を必要とする。これらには、書込み、及び読出し操作中、ワード電流パルスを要求ワード線に送信するためのワード選択マトリクス、書込みサイクルの間、ディジット電流パルスを要求ディジット線に送信するためのディジット選択マトリクス、及び、信号を要求センス線からセンスアンプに送信するためのセンス選択マトリクスが含まれる。これら電子アレイは、従来の半導体装置を備え得る。その場合、PRAM素子は、配置済選択トランジスタを有する半導体チップ上に製造される。しかしながら、その中に選択電子回路自身がGMR物質から製造されるという他の選択枝もある。結果として、選択電子回路は、GMRメモリ素子と同時に堆積され、この結果、多くのマスク、及び製造ステップが省略される。そのようなGMR装置の1つは、スピントランジューサである。

B. 全金属(GMR)スピントランジューサ

全金属スピントランジューサは、全く新規な種類のスイッチング装置[M. Johnson, IEEE Spectrum 31 No. 5(1994)47]である。それは、2つの異なるキャリアに依存するので、従来のバイポーラトランジスタとは異なる。しかしながら、半導体バイポーラトランジスタ用キャリアが電子及びホールである、すなわち、キャリアは異なる電荷を有するのに対して、金属トランジスタ中における2つのキャリア集団は、双方共にそれらのスピン配位によって識別される電子である。一般的に、それは、エミッタ、及び、コレクタ層が強磁性膜であると共に、基盤層が非磁性金属である巨大磁気抵抗素子である。それの出力は、2つの磁性間角度を変更することにより調整される。すなわち、2つの膜の一方を切り替えることにより、それらの相対オリエンテーションが、平行、及び、逆平行間で変化する。全金属トランジューサの特性が自身の寸法縮小を改善するので、また、サブミクロン印刷技術が容易に全金属トランジューサの製造に適用され得るので、全金属トランジューサは、半導体バイポーラトランジスタよりもかなり小さく、100倍の密度で製造され得ることが予測される。全金属トランジューサのスイッチング時間は、実質的にGMRPRAM記憶素子についてのそれと同一の1〜10nsの範囲に計画されている。したがって、全金属トランジューサによる従来の制御電子回路の置き換えは、速度、及び密度特性が記憶素子自身の特性により制限されるポイントまでPRAMセルの寸法、及びスイッチング速度を低減する可能性を提供する。さらに、それは、PRAM製造プロセスを、以下に説明するように大幅に単純にする。

全金属スピントランジューサは他の機能PRAM素子と同一のチップ上に同時に製造され得るので、本発明に係るPRAMに対して全金属スピントランジューサを用いることにより非常に大きな利益が得られる。追加の金属被覆、ドーピング、あるいは、高温での追加プロセスは必要ない。メモリ全体、選択電子回路、及び全てが、追加堆積ステップ、あるいは、プロセスなくして同時に同一基板上に堆積される。例えば、図5〜図11に図示されるPRAM設計は、標準的な薄膜プレーナプロセス、マイクロ機械加工、印刷、集積回路、及び磁気抵抗物質を用いて製造され得る。半導体素子のスピントランジスタへの置き換えは、少なくとも2点においてPRAMの製造を単純化する。1つ目は、それは、製造プロセスにおいて同一基板上に半導体物質、及び磁性物質を組み合わせる際に生じ得る潜在的な複雑化を排除する。それはまた、それ自身は半導体製造に向かない、いわゆる「ウェッビング」プロセスによってPRAMの大量製造への道を切り開く。

PRAM中のGMRスピントランジスタは、記憶/読出し素子と同一物質から成ることが好ましいが、同一構造を備える必要はない。磁気層の保磁力は、記憶/読出し素子などの保磁力に近似していることが好ましい。既述した方法によるGMRスピントランジスタの使用は、PRAMの補助電子回路のわずか一例を表すものであり、本発明はそのような例示に限定されるものでないことは理解されるべきである。

C. 超密度テラビットPRAM

集合的に、従来の印刷技術、及びマイクロ製造技術を、基板上に直接、線、及び記憶/読出し素子を堆積し、パターン形成す超高解像度技術によって置き換えること、及び半導体式トランジスタを全金属スピントランジスタによって置き換えることは、より一層コンパクト(10Gbit/cm2〜1Tbit/cm2)かつ高速(10ns未満)なPRAMをもたらす。

超密度テラビットメモリ用PRAMセル500の概念設計が図12(a)及び12(b)に図示されている。図12(a)は、ワード線502が、どのようにして絶縁ピラー部506を介してGMR記憶膜504を通過し、結合されているかをより明確に示すPRAMセル500の部分分解図を図示する。図12(b)は、絶縁508を備える縦方向構成図を図示する。記憶/読出し膜504と組み合わせられた閉磁束GMRは、ワード線502電流及びセンス/ディジット線510電流の同時発生によって切り替えられる。後者は、実際にはGMR膜を通じて進行する。前者は、GMR膜とは絶縁されている。図示されているメモリは、2つの次元を有し、同時発生電流によって作用させられ、及びビット構成である。この発明の実施の形態では、図5及び図6に示す発明の実施の形態とは異なり、ディジット線及びセンス線が単一センス/ディジット線中に組み込まれている。

16個のメモリセル500のアレイ520が図13に図示されている。当然のことながら、テラビットメモリは、各モジュール中にさらに多くの線を有している。ワード線502の端部には、ワード電流駆動回路、及びワード選択マトリクス(図示しない)が、センス/ディジット線510の端部には、センスアンプ、及びセンス選択マトリクス(低レベルゲート、図示しない)がその一端に、ディジット選択マトリクスがその他端(図示しない)に在る。ワード線502、センス/ディジット線510、及び選択マトリクス552,554,556を示すGMRPRAMモジュール550が図14に図示されている。従来のAMRメモリは、各センス線上に32個のメモリ素子を有している。GMR素子は非常に大きな出力を有しているので、センス/ディジット線当たりの素子数は、少なくとも10要素だけ大きい。ダミー線は、ノイズをキャンセルするために用いられる。

読出しは平面内GMRPRAMと同様にして実行される。ワード電流は、選択ワード線に沿って送られ、ワード線に沿う各ビットのパーマロイ層の磁性ベクトルを変化させる。高保磁力コバルト層は、影響を受けない。単一センス/ディジット線が選択されると、その線上の信号だけが低レベルゲートを通じてそのモジュール用センスアンプに対して送られる。したがって、センスアンプは、選択ワード線と選択センス/ディジット線の交点に存在する僅か1ビットからの信号だけを認識する。

図12〜図14に図示されるGMRPRAM素子は、非常にコンパクトであり、統合され、速く、また、各コンピュータの一部分である磁気コアメモリと同様に確実に作動することが予測され得る。古いコアのように、これらPRAM素子は、完全磁束クロージャを有し、また、小さくなるにつれ、さらに優れた、高速な、小電流要求を得る。しかしながら、旧式のコアメモリと異なり、(1)印刷技術による制限以外にPRAMアレイに対する密度制限はなく、(2)磁束に依存しないので出力は寸法と共に低減せず、(3)読出しが非破壊的である。PRAMの出力は、電流がメモリ素子を通過する際の巨大磁気抵抗によりもたらされる。この出力は、全抵抗の僅かな変化であり、また、形状要素が同一である限りメモリ素子の寸法に無関係である。図12〜図14における導体、及びメモリ設計は、金属であり、従来の半導体が有するキャリア制限を有していない。したがって、これらPRAM素子は、旧型コアの長所を維持し、一方で、望ましくない制限を取り除く。それらは、事実上「スーパーコア」である。つまり、このPRAM設計は、高速、廉価、ランダムアクセス、コンパクト、高速変更可能、堅牢、かつ不揮発なテラビットメモリに唯一的に適する。

VIII. 製造

一般的に、巨大磁気抵抗膜は、PRAM情報セルの一部として機能するために、注意深い設計、及び製造技術を要求する。高保磁力層は、ワード線、及びディジット線の電流の組み合わせに基づくフィールドにより切り替えられるよう十分に低い保磁力を有する必要があると共に、ワードパルス、あるいは、ディジットパルスのいずれか一方だけによっては切り替えられないよう十分に高い保磁力を有する必要がある。最大信号について、高保磁力層は、全低保磁力層の切替に要求されるレベル以下で切替を開始してはならない。そこで、コバルトの最小保磁力を上げるため、高保磁力非伝導磁気酸化層は、時々、第1コバルト層に先立ち基板上に堆積される。同様に、他のそのような層が構造の最後のコバルト層上に時に堆積される。非磁気金属層は、2つの磁気層の個別の切り替えを可能にするために交換カップリングを十分に弱くするほど十分に厚くなくてはならず、一方で、全構造の抵抗を下げることにより膜信号を短絡するほど厚くあってはならない。

A. 製造プロセス

巨大磁気抵抗を備えるメモリセル製造プロセスについて以下説明する。膜は、周知のスパッタリング、あるいは、蒸着によって製造され得る。巨大磁気抵抗膜は、エッチング処理済駆動線を備える段状表面ではなく、平滑、かつ、未処理の基板表面上に堆積されることが大いに好ましい。この理由から、また図8を参照して説明したように、磁気コア素子底面上の駆動線部分は、コア素子自身よりも大きいことが好ましい。また、この発明の実施の形態では、上部駆動線はコア素子の中心を通って下部と接続されている。

製造プロセスにおいては、下部ワード線が先ず配置される。その後、絶縁層が適用される。そして、これら2層のエッチングが実行される。次に、下部ディジット線が堆積され、そして、エッチングされる。下部ディジット線に続き、他の絶縁層が堆積される。

この時点で、コアを配置することが好ましい。各コア素子は、先に配置された2層の下部伝導層の交差により規定される幅広平面上に配置される。次に、コア素子の中心にて下部層に対するホールがエッチングされる。この後、上部駆動線が製造され、コア素子内のエッチングホールを介して下部駆動線との接続が確立される。この好適な製造プロセスでは、この時点で、基板上へ4層の金属層、及び3層の絶縁層を堆積する7つの堆積ステップが存在する。

B. 消磁フィールドの回避

前述のように、本発明に係るメモリセルの設計においては、磁束構造が閉じており、メモリオペレーションの全段階においていつも閉じていることが重要である。オープン構造は、不完全なスイッチングをもたらし、また磁性クリープによる情報喪失、本質的に遅いスイッチングプロセスを潜在的に招く。隣接ビットは、磁束構造が実質的に閉じられていない場合、磁性クリープの一因となり得る。従来の膜メモリは、(駆動線幅のため)一次元閉磁束で設計されている一方で、他の方向においては一般的に開かれている。磁性フィールドが第二次元中へ回転させられるときに、消磁フィールドはメモリ破壊を開始する。本発明の設計によれば、メモリセルの磁性は、第二次元中へ回転させられないので、磁性クリープ、及びそれに関連する問題を示さない。

本発明に係るメモリセルを備えることにより、電流は膜に対して垂直に、あるいは、膜平面内で流れ得ることが理解される。原則として、垂直な流れは、読出し素子にとって好適な構成であるため、一般的に、抵抗変化、すなわち、GMR効果は、後者の場合よりも前者の場合の方が大きい。しかしながら、メモリ素子幅が、その厚さの何倍も大きい場合には、平面に垂直な抵抗は、不都合なほど小さく、また、良好な読出し信号の取得が困難になり得る。この障害は、より好適な形状要素、すなわち、その幅を厚さに対して比較し得る素子を用いる素子の製造を許容する十分な精密印刷によって克服され得る。そして、良好な読出し信号、及びより大きな抵抗変化を達成するために十分に大きい抵抗を備える記憶/読出し素子を実現することが可能になり、これにより、「1」及び「0」の信号が明確に識別され得る。

本発明における巨大磁気抵抗を示す物質の利用は、メモリ設計におけるいくつかの重要な選択を必要とする。先ず、非磁気伝導体は、素子の平均自由行程より薄い厚さを有しているべきである。平面内オペレーションが選択された場合には、中間層の短絡効果が重要となる。しかしながら、他の複雑な結合、及び機会が存在する。2つの層のスピンと結合されている2層の磁気層間における超交換が存在する。カップリング長は、分離層の厚さに依存し、厚さが増すにつれ短くなる。さらに、カップリングのサインは、分離幅の振動関数であり、したがって、カップリングは、いくつかの分離に対して強磁性であり、また、他のものについて反強磁性である。このことは、層間の分離が変化する膜を製造したと共に、分離距離の4倍のカップリングリバースサインを発見したParkin等により経験的に示されている。

また、強磁性カップリング、あるいは、反強磁性カップリングのあらゆる組み合わせの選択が存在する。非破壊読出しは、それが他の磁気層の磁性に対して平行に磁化された層と逆平行に磁化された層との間で振動するように、層の1つにおける磁性を繰り返し変化させることにより実行され得る。このような繰り返し非破壊読出しは、信号/ノイズ比を改善する。

磁気層の組成もまた重要である。磁気層の組成は、下向きスピン電子までの大きな比率を有するべきである。例えば、純ニッケルは好ましくない選択である。組成はまた、0磁歪、大きな粒子寸法、及び平均的な異方性を備えるべきである。繰り返し非破壊読出しについて、読出し中、他の層のオリエンテーションが繰り返し振動するのに対して、1つの層のオリエンテーションは同じまま残るよう、最上層磁気層の保磁力は、下層のそれとは異なるべきであり、また、2層の磁気層間における交換カップリングは、読出し電流が除去されたとき、切替層を元の状態に戻すために十分な大きさを有するべきである。

読出しに有用であるために磁気層は異なるべきである。1つの層は記憶素子であり、他の層は読出し素子である。適用読出電流は、読出し層を切り替えるが、記憶層は切り替えない。さらに、切替中、半選択フィールドを供給するディジット線、及び読出し中、信号を検出するためのセンス線の双方として、磁気抵抗の検出のための電流を供給する線を使用する選択肢が存在する。

IX. 代表的な適用例

本明細書中に記述されている不揮発性メモリアレイの唯一的な特徴は、それ自身、数多くの高速データ記憶装置、及び検索システムの役に立ち、また、有用である。一般的に、PRAMは、コンピュータ、レコーダ、制御装置といったディジタルシステム、及びこれらの装置が役立つ全産業の全般にわたり、メインメモリ、及び大容量記憶装置としての適用性を有している。詳細な適用例の一部のリストを以下に示す。

最初の使用例は、大きなデータ記憶装置、及び最大アクセス速度を要求するコンピュータアプリケーションとの使用である。1つの例として、ガイダンスシステムのような意思決定要求を伴う人工知能プロセスがある。他の重要な例示として、知覚入力、及び、迅速な反応動作を必要とするロボット工学システムがある。不揮発性メモリに対する高速、及び、パラレルアクセスから利益を享受するコンピュータに関する適用例であればどのようなものでも、このコンポーネントから利益を享受するであろう。この例示は、突然に、ランダムに電力損失に遭遇し得る通信システム分野、及び通信制御装置分野である。一般的に、ディジタル通信制御装置は、最大帯域幅を要求する。

一般的に、即時フィードバックを要求する者(例えば、手術を行う外科医)により利用され、また、リアルタイムでの最大アクセス速度が不可欠な、膨大な格納データにアクセスするリアルタイムシステムもまた存在する。不揮発性、及びRAMの速度を組み合わせたPRAMは、そのようなシステムのために重要である。

あらゆるディスクインテンシブアプリケーション、例えば、データベース検索、グラフィックス、及び多くのビジネスコンピュータアプリケーション、において、位置決め時間はI/Oの大部分を占めている。全てのそのようなアプリケーションについて、GMRPRAMアレイに基づく記憶装置は、全体の計算速度の改善という必然的効果を伴って、I/Oに要求される時間を数桁低減する。より一般的には、GMRPRAMは、次の5つの点、一桁速いデータアクセス時間、非常に優れた耐衝撃性、及び耐振動性、高い信頼性、メンテナンスフリーオペレーション、及びヘッドクラッシュの不存在、においてディスク、テープシステムを大きく凌ぐ。

その高速なランダムアクセス、及び恒久的な記憶装置と共に、メモリシステムの比較的小さな容積、及び重量は、PRAMの不揮発性がバックアップバッテリを不要にするので、本発明をポータブルコンピュータにとって理想的なものとする。

本発明のPRAMは、非揮発性及び、堅牢性及び半導体メモリのアクセス速度を備える実質的に回数無制限な磁気記憶装置の消去サイクルを組み合わせるそれ自身の潜在的能力の点で唯一のものである。PRAMの企図する特性が商業的に入手可能な半導体メモリ、スタティックRAM(SRAM)、ダイナミックRAM(DRAM)、アプリケーション最適化EPROM(消去可能なプログラム可能リードオンリメモリ)に適用された製品名であるFLASHと表1にて比較されている。PRAMは、SRAMの書込み、及び読出し速度に迫る企図する書込み及び読出し速度、及び低消費電力を備えているように思われる。高速ダイナミック技術とは異なり、PRAMは、非揮発性なので待機電力を必要としない。唯一、不揮発性メモリの一つに属するFLASHと異なり、PRAMは、無制限の書込みサイクルを有している。FLASHは低電力で高密度を提供するが書込み時間が長く、また、全ビット変更可能でない、すなわち、ランダムアクセスをサポートしていない。

表2は、本明細書中にて説明したPRAM(パーマネントランダムアクセスメモリ)と他のメモリシステムとを比較する。

X. 結論

上記記述は説明であり、制限ではない。本発明の多くの変形例は当業者にとって明らかである。例えば、異なるトランジューサ型が本発明の範囲を逸脱することなく用いられ得る。したがって、本発明の範囲は、上記説明に基づくことなく、その均等の範囲と共に添付の請求の範囲に基づいて決定されるべきである。

Claims (3)

- 第1の保磁力を有する磁性導体からなる層(134)と、非磁性導体(132)からなる中央層と、上記第1の保磁力よりも大きい第2の保磁力を有する磁性導体からなる層(130)とを積層し、巨大磁気抵抗を生ずるように構成された巨大磁気抵抗多層(214)と、

絶縁層(212)を介して前記巨大磁気抵抗多層(214)上に配設された、情報の書き込みのためのディジット線(210)と、

絶縁層(208)を介して前記ディジット線(210)上に配設された、選択信号を供給するためのワード線(206)と、

前記巨大磁気抵抗多層(214)と電気的に結合する、情報読み出しのためのセンス線を備え、

前記ディジット線(210)と前記ワード線(206)は、前記巨大磁気抵抗多層(214)上の領域において平行であり、

前記巨大磁気抵抗多層(214)と軟磁性材料からなる磁束クロージャ用の要素(200、202)とにより、前記ディジット線(210)及びワード線(206)を囲む閉磁束構造を構成するメモリセル(198)からなり、

前記磁性導体からなる層(130、134)の中の磁性ベクトルの方向は、全作用段階を通して、1つの次元に実質的に制限され、一次元的に平行で且つ同方向であるか、平行で且つ反対方向であり、

情報の書き込みは、前記ワード線(206)と前記ディジット線(210)に同時に電流を与えることにより前記第2の保磁力を有する磁性導体からなる層(130)の磁性ベクトルを設定することにより行い、

情報の読み出しは、前記ワード線(206)の電流による磁界を与えることにより、前記第2の保磁力を有する磁性導体からなる層(130)の磁性ベクトルを維持するとともに、前記第1の保磁力を有する磁性導体からなる層(134)の磁性ベクトルを一時的に切り換えて、磁性変化に対応する抵抗変化を計測することにより行う、

ことを特徴とする不揮発性磁気抵抗メモリ。 - 第1の保磁力を有する磁性導体からなる層と、非磁性導体からなる中央層と、上記第1の保磁力よりも大きい第2の保磁力を有する磁性導体からなる層とを積層し、巨大磁気抵抗を生ずるように構成された巨大磁気抵抗多層(412)と、

絶縁層(410)を介して前記巨大磁気抵抗多層(412)上に配設された、選択信号を供給するためのワード線(408)と、

絶縁層(410)を介して前記ワード線(408)上に配設された、情報の書き込みのためのディジット線(406)と、

前記巨大磁気抵抗多層(412)と電気的に結合する、情報読み出しのためのセンス線を備え、

前記ディジット線(406)と前記ワード線(408)は、前記巨大磁気抵抗多層(412)上の領域において平行であり、

前記巨大磁気抵抗多層(412)と磁束クロージャ用の軟磁性材料の保持層(402)とにより、前記ディジット線(210)及びワード線(206)を、絶縁膜(404)を介して囲んでおり、これにより閉磁束構造を構成するメモリセル(400)からなり、

前記磁性導体からなる層の中の磁性ベクトルの方向は、全作用段階を通して、1つの次元に実質的に制限され、一次元的に平行で且つ同方向であるか、平行で且つ反対方向であり、

情報の書き込みは、前記ワード線(408)と前記ディジット線(406)に同時に電流を与えることにより前記第2の保磁力を有する磁性導体からなる層の磁性ベクトルを設定することにより行い、

情報の読み出しは、前記ワード線(408)の電流による磁界を与えることにより、前記第2の保磁力を有する磁性導体からなる層の磁性ベクトルを維持するとともに、前記第1の保磁力を有する磁性導体からなる層の磁性ベクトルを一時的に切り換えて、磁性変化に対応する抵抗変化を計測することにより行う、

ことを特徴とする不揮発性磁気抵抗メモリ。 - 巨大磁気抵抗多層が、第1の保磁力を有する磁性導体からなる層と非磁性導体からなる中央層と、第2の保磁力を有する磁性導体からなる層との組み合わせた層が複数積層されている請求項1又は2に記載の不揮発性磁気抵抗メモリ。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US08/388,035 | 1995-02-13 | ||

| US08/388,035 US5587943A (en) | 1995-02-13 | 1995-02-13 | Nonvolatile magnetoresistive memory with fully closed flux operation |

| PCT/US1996/001653 WO1996025740A1 (en) | 1995-02-13 | 1996-02-08 | Nonvolatile magnetoresistive memory with fully closed-flux operation |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH11501438A JPH11501438A (ja) | 1999-02-02 |

| JP4171067B2 true JP4171067B2 (ja) | 2008-10-22 |

Family

ID=23532371

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP52500696A Expired - Lifetime JP4171067B2 (ja) | 1995-02-13 | 1996-02-08 | 完全閉磁束作用を備える不揮発性磁気抵抗メモリ |

Country Status (8)

| Country | Link |

|---|---|

| US (1) | US5587943A (ja) |

| EP (1) | EP0809846B1 (ja) |

| JP (1) | JP4171067B2 (ja) |

| KR (1) | KR100302174B1 (ja) |

| CA (1) | CA2211699C (ja) |

| DE (1) | DE69609165T2 (ja) |

| TW (1) | TW287272B (ja) |

| WO (1) | WO1996025740A1 (ja) |

Families Citing this family (132)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7709115B2 (en) * | 1994-08-25 | 2010-05-04 | University Of Iowa Research Foundation | Methods for forming magnetically modified electrodes and articles produced thereby |

| US6322676B1 (en) | 1998-03-25 | 2001-11-27 | University Of Iowa Research Foundation | Magnetic composites exhibiting distinct flux properties due to gradient interfaces |

| US6949179B2 (en) * | 1994-08-25 | 2005-09-27 | University Of Iowa Research Foundation | Methods for forming magnetically modified electrodes and articles produced thereby |

| US6001248A (en) | 1994-08-25 | 1999-12-14 | The University Of Iowa Research Foundation | Gradient interface magnetic composites and systems therefor |

| US6355166B1 (en) | 1994-08-25 | 2002-03-12 | The University Of Iowa Research Foundation | Magnetically enhanced composite materials and methods for making and using the same |

| US5871625A (en) | 1994-08-25 | 1999-02-16 | University Of Iowa Research Foundation | Magnetic composites for improved electrolysis |

| US20050213187A1 (en) * | 1994-08-25 | 2005-09-29 | University Of Iowa Research Foundation | Methods for forming magnetically modified electrodes and articles produced thereby |

| US6169687B1 (en) * | 1995-04-21 | 2001-01-02 | Mark B. Johnson | High density and speed magneto-electronic memory for use in computing system |

| US6741494B2 (en) * | 1995-04-21 | 2004-05-25 | Mark B. Johnson | Magnetoelectronic memory element with inductively coupled write wires |

| JP3207094B2 (ja) * | 1995-08-21 | 2001-09-10 | 松下電器産業株式会社 | 磁気抵抗効果素子及びメモリー素子 |

| US5702831A (en) * | 1995-11-06 | 1997-12-30 | Motorola | Ferromagnetic GMR material |

| JP3767930B2 (ja) * | 1995-11-13 | 2006-04-19 | 沖電気工業株式会社 | 情報の記録・再生方法および情報記憶装置 |

| US5929636A (en) * | 1996-05-02 | 1999-07-27 | Integrated Magnetoelectronics | All-metal giant magnetoresistive solid-state component |

| US5732016A (en) * | 1996-07-02 | 1998-03-24 | Motorola | Memory cell structure in a magnetic random access memory and a method for fabricating thereof |

| US5920500A (en) * | 1996-08-23 | 1999-07-06 | Motorola, Inc. | Magnetic random access memory having stacked memory cells and fabrication method therefor |

| DE19639910C2 (de) * | 1996-09-27 | 1998-08-20 | Siemens Ag | Nichtflüchtiger Analogwertspeicher auf der Basis von GMR-Schichtsystemen |

| US5699293A (en) * | 1996-10-09 | 1997-12-16 | Motorola | Method of operating a random access memory device having a plurality of pairs of memory cells as the memory device |

| US6028786A (en) * | 1997-04-28 | 2000-02-22 | Canon Kabushiki Kaisha | Magnetic memory element having coupled magnetic layers forming closed magnetic circuit |

| US5852574A (en) * | 1997-12-24 | 1998-12-22 | Motorola, Inc. | High density magnetoresistive random access memory device and operating method thereof |

| EP0959475A3 (en) * | 1998-05-18 | 2000-11-08 | Canon Kabushiki Kaisha | Magnetic thin film memory and recording and reproducing method and apparatus using such a memory |

| US6055179A (en) * | 1998-05-19 | 2000-04-25 | Canon Kk | Memory device utilizing giant magnetoresistance effect |

| DE19823826A1 (de) | 1998-05-28 | 1999-12-02 | Burkhard Hillebrands | MRAM-Speicher sowie Verfahren zum Lesen/Schreiben digitaler Information in einen derartigen Speicher |

| US5953248A (en) * | 1998-07-20 | 1999-09-14 | Motorola, Inc. | Low switching field magnetic tunneling junction for high density arrays |

| US5946227A (en) * | 1998-07-20 | 1999-08-31 | Motorola, Inc. | Magnetoresistive random access memory with shared word and digit lines |

| US6083764A (en) * | 1998-07-20 | 2000-07-04 | Motorola, Inc. | Method of fabricating an MTJ with low areal resistance |

| US6130814A (en) | 1998-07-28 | 2000-10-10 | International Business Machines Corporation | Current-induced magnetic switching device and memory including the same |

| DE19836567C2 (de) | 1998-08-12 | 2000-12-07 | Siemens Ag | Speicherzellenanordnung mit Speicherelementen mit magnetoresistivem Effekt und Verfahren zu deren Herstellung |

| US5982660A (en) * | 1998-08-27 | 1999-11-09 | Hewlett-Packard Company | Magnetic memory cell with off-axis reference layer orientation for improved response |

| DE19840823C1 (de) * | 1998-09-07 | 2000-07-13 | Siemens Ag | Magnetoresistives Element und dessen Verwendung als Speicherelement in einer Speicherzellenanordnung |

| TW454187B (en) * | 1998-09-30 | 2001-09-11 | Siemens Ag | Magnetoresistive memory with low current density |

| EP1155462B1 (de) * | 1999-02-26 | 2005-09-07 | Infineon Technologies AG | Speicherzellenanordnung und verfahren zu deren herstellung |

| KR100450468B1 (ko) * | 1999-02-26 | 2004-09-30 | 인피니언 테크놀로지스 아게 | 기억 셀 장치 및 그의 제조 방법 |

| US6266289B1 (en) | 1999-03-09 | 2001-07-24 | Amphora | Method of toroid write and read, memory cell and memory device for realizing the same |

| US6872993B1 (en) | 1999-05-25 | 2005-03-29 | Micron Technology, Inc. | Thin film memory device having local and external magnetic shielding |

| US6111783A (en) * | 1999-06-16 | 2000-08-29 | Hewlett-Packard Company | MRAM device including write circuit for supplying word and bit line current having unequal magnitudes |

| US6134139A (en) * | 1999-07-28 | 2000-10-17 | Hewlett-Packard | Magnetic memory structure with improved half-select margin |

| US6215644B1 (en) | 1999-09-09 | 2001-04-10 | Jds Uniphase Inc. | High frequency tunable capacitors |

| US6611405B1 (en) * | 1999-09-16 | 2003-08-26 | Kabushiki Kaisha Toshiba | Magnetoresistive element and magnetic memory device |

| US6052302A (en) * | 1999-09-27 | 2000-04-18 | Motorola, Inc. | Bit-wise conditional write method and system for an MRAM |

| US6178111B1 (en) | 1999-12-07 | 2001-01-23 | Honeywell Inc. | Method and apparatus for writing data states to non-volatile storage devices |

| US6480365B1 (en) * | 1999-12-09 | 2002-11-12 | International Business Machines Corporation | Spin valve transistor using a magnetic tunnel junction |

| EP1107329B1 (en) | 1999-12-10 | 2011-07-06 | Sharp Kabushiki Kaisha | Magnetic tunnel junction device, magnetic memory adopting the same, magnetic memory cell and access method of the same |

| US6496351B2 (en) | 1999-12-15 | 2002-12-17 | Jds Uniphase Inc. | MEMS device members having portions that contact a substrate and associated methods of operating |

| US6229684B1 (en) | 1999-12-15 | 2001-05-08 | Jds Uniphase Inc. | Variable capacitor and associated fabrication method |

| US6215707B1 (en) * | 2000-04-10 | 2001-04-10 | Motorola Inc. | Charge conserving write method and system for an MRAM |

| US6982854B2 (en) * | 2000-06-22 | 2006-01-03 | Matsushita Electric Industrial Co., Ltd. | Magnetoresistance effect device and magnetoresistance effect head comprising the same, and magnetic recording/reproducing apparatus |

| US6483740B2 (en) * | 2000-07-11 | 2002-11-19 | Integrated Magnetoelectronics Corporation | All metal giant magnetoresistive memory |

| US6469927B2 (en) * | 2000-07-11 | 2002-10-22 | Integrated Magnetoelectronics | Magnetoresistive trimming of GMR circuits |

| US6594175B2 (en) * | 2000-07-11 | 2003-07-15 | Integrated Magnetoelectronics Corp | High density giant magnetoresistive memory cell |

| US6396733B1 (en) | 2000-07-17 | 2002-05-28 | Micron Technology, Inc. | Magneto-resistive memory having sense amplifier with offset control |

| US6493258B1 (en) * | 2000-07-18 | 2002-12-10 | Micron Technology, Inc. | Magneto-resistive memory array |

| US6724654B1 (en) * | 2000-08-14 | 2004-04-20 | Micron Technology, Inc. | Pulsed write techniques for magneto-resistive memories |

| US6363007B1 (en) | 2000-08-14 | 2002-03-26 | Micron Technology, Inc. | Magneto-resistive memory with shared wordline and sense line |

| US6392922B1 (en) * | 2000-08-14 | 2002-05-21 | Micron Technology, Inc. | Passivated magneto-resistive bit structure and passivation method therefor |

| US6493259B1 (en) | 2000-08-14 | 2002-12-10 | Micron Technology, Inc. | Pulse write techniques for magneto-resistive memories |

| US6579625B1 (en) * | 2000-10-24 | 2003-06-17 | Motorola, Inc. | Magnetoelectronics element having a magnetic layer formed of multiple sub-element layers |

| TW544677B (en) * | 2000-12-26 | 2003-08-01 | Matsushita Electric Ind Co Ltd | Magneto-resistance memory device |

| US6413788B1 (en) * | 2001-02-28 | 2002-07-02 | Micron Technology, Inc. | Keepers for MRAM electrodes |

| US6653154B2 (en) * | 2001-03-15 | 2003-11-25 | Micron Technology, Inc. | Method of forming self-aligned, trenchless mangetoresistive random-access memory (MRAM) structure with sidewall containment of MRAM structure |

| US6573713B2 (en) | 2001-03-23 | 2003-06-03 | Integrated Magnetoelectronics Corporation | Transpinnor-based switch and applications |

| US6738284B2 (en) | 2001-03-23 | 2004-05-18 | Integrated Magnetoelectronics Corporation | Transpinnor-based sample-and-hold circuit and applications |

| US6593833B2 (en) | 2001-04-04 | 2003-07-15 | Mcnc | Tunable microwave components utilizing ferroelectric and ferromagnetic composite dielectrics and methods for making same |

| DE10118197C2 (de) * | 2001-04-11 | 2003-04-03 | Infineon Technologies Ag | Integrierte magnetoresistive Halbleiterspeicheranordnung und Verfahren zum Beschreiben derselben |

| JP5019681B2 (ja) | 2001-04-26 | 2012-09-05 | ルネサスエレクトロニクス株式会社 | 薄膜磁性体記憶装置 |

| US6744086B2 (en) * | 2001-05-15 | 2004-06-01 | Nve Corporation | Current switched magnetoresistive memory cell |

| US6466471B1 (en) * | 2001-05-29 | 2002-10-15 | Hewlett-Packard Company | Low power MRAM memory array |

| JP2003007980A (ja) * | 2001-06-20 | 2003-01-10 | Sony Corp | 磁気特性の変調方法および磁気機能装置 |

| US6510080B1 (en) | 2001-08-28 | 2003-01-21 | Micron Technology Inc. | Three terminal magnetic random access memory |

| US6485989B1 (en) | 2001-08-30 | 2002-11-26 | Micron Technology, Inc. | MRAM sense layer isolation |

| US6627913B2 (en) | 2001-09-10 | 2003-09-30 | Micron Technology, Inc. | Insulation of an MRAM device through a self-aligned spacer |

| US6576969B2 (en) | 2001-09-25 | 2003-06-10 | Hewlett-Packard Development Company, L.P. | Magneto-resistive device having soft reference layer |

| US6538917B1 (en) * | 2001-09-25 | 2003-03-25 | Hewlett-Packard Development Company, L.P. | Read methods for magneto-resistive device having soft reference layer |

| US6741496B2 (en) * | 2001-09-27 | 2004-05-25 | Intel Corporation | Electron spin mechanisms for inducing magnetic-polarization reversal |

| US6545906B1 (en) | 2001-10-16 | 2003-04-08 | Motorola, Inc. | Method of writing to scalable magnetoresistance random access memory element |

| JP2003151262A (ja) * | 2001-11-15 | 2003-05-23 | Toshiba Corp | 磁気ランダムアクセスメモリ |

| JP3661652B2 (ja) * | 2002-02-15 | 2005-06-15 | ソニー株式会社 | 磁気抵抗効果素子および磁気メモリ装置 |

| US6906947B2 (en) * | 2002-02-22 | 2005-06-14 | Hewlett-Packard Development Company, L.P. | In-plane toroidal memory cell with vertically stepped conductors |

| US20030161180A1 (en) * | 2002-02-22 | 2003-08-28 | Bloomquist Darrel R. | Shared bit lines in stacked MRAM arrays |

| US6859063B2 (en) * | 2002-04-11 | 2005-02-22 | Integrated Magnetoelectronics Corporation | Transpinnor-based transmission line transceivers and applications |

| AU2003225048A1 (en) * | 2002-04-19 | 2003-11-03 | Integrated Magnetoelectronics Corporation | Interfaces between semiconductor circuitry and transpinnor-based circuitry |

| US6783995B2 (en) * | 2002-04-30 | 2004-08-31 | Micron Technology, Inc. | Protective layers for MRAM devices |

| US6724652B2 (en) * | 2002-05-02 | 2004-04-20 | Micron Technology, Inc. | Low remanence flux concentrator for MRAM devices |

| US6927073B2 (en) * | 2002-05-16 | 2005-08-09 | Nova Research, Inc. | Methods of fabricating magnetoresistive memory devices |

| US6879512B2 (en) * | 2002-05-24 | 2005-04-12 | International Business Machines Corporation | Nonvolatile memory device utilizing spin-valve-type designs and current pulses |

| US6780653B2 (en) * | 2002-06-06 | 2004-08-24 | Micron Technology, Inc. | Methods of forming magnetoresistive memory device assemblies |

| US6744663B2 (en) * | 2002-06-28 | 2004-06-01 | Motorola, Inc. | Circuit and method for reading a toggle memory cell |

| US7095646B2 (en) | 2002-07-17 | 2006-08-22 | Freescale Semiconductor, Inc. | Multi-state magnetoresistance random access cell with improved memory storage density |

| US6654278B1 (en) * | 2002-07-31 | 2003-11-25 | Motorola, Inc. | Magnetoresistance random access memory |

| US6770491B2 (en) * | 2002-08-07 | 2004-08-03 | Micron Technology, Inc. | Magnetoresistive memory and method of manufacturing the same |

| US6885576B2 (en) * | 2002-08-13 | 2005-04-26 | Micron Technology, Inc. | Closed flux magnetic memory |

| US6914805B2 (en) * | 2002-08-21 | 2005-07-05 | Micron Technology, Inc. | Method for building a magnetic keeper or flux concentrator used for writing magnetic bits on a MRAM device |

| JP3788964B2 (ja) * | 2002-09-10 | 2006-06-21 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| US6809958B2 (en) * | 2002-09-13 | 2004-10-26 | Hewlett-Packard Development Company, L.P. | MRAM parallel conductor orientation for improved write performance |

| KR100515053B1 (ko) * | 2002-10-02 | 2005-09-14 | 삼성전자주식회사 | 비트라인 클램핑 전압 레벨에 대해 안정적인 독출 동작이가능한 마그네틱 메모리 장치 |

| JP3893456B2 (ja) * | 2002-10-18 | 2007-03-14 | 国立大学法人大阪大学 | 磁性メモリ及び磁性メモリアレイ |

| ES2406304T3 (es) * | 2002-11-28 | 2013-06-06 | Crocus Technology, Inc. | Procedimiento y dispositivo para la generación mejorada de campos magnéticos durante una operación de escritura de un dispositivo de memoria magnetorresistente |

| US6992919B2 (en) * | 2002-12-20 | 2006-01-31 | Integrated Magnetoelectronics Corporation | All-metal three-dimensional circuits and memories |

| JP4720067B2 (ja) * | 2003-01-24 | 2011-07-13 | Tdk株式会社 | 磁気記憶セルおよび磁気メモリデバイスならびに磁気メモリデバイスの製造方法 |

| US7002228B2 (en) * | 2003-02-18 | 2006-02-21 | Micron Technology, Inc. | Diffusion barrier for improving the thermal stability of MRAM devices |

| JP4419408B2 (ja) * | 2003-03-14 | 2010-02-24 | Tdk株式会社 | 磁気抵抗効果素子および磁気メモリデバイス |

| JP4729836B2 (ja) * | 2003-03-28 | 2011-07-20 | Tdk株式会社 | 磁気記憶セルおよび磁気メモリデバイスならびに磁気メモリデバイスの製造方法 |

| US7005852B2 (en) | 2003-04-04 | 2006-02-28 | Integrated Magnetoelectronics Corporation | Displays with all-metal electronics |

| JP4556385B2 (ja) * | 2003-05-27 | 2010-10-06 | Tdk株式会社 | 磁気メモリデバイスの製造方法 |

| US6956763B2 (en) | 2003-06-27 | 2005-10-18 | Freescale Semiconductor, Inc. | MRAM element and methods for writing the MRAM element |

| US6967366B2 (en) | 2003-08-25 | 2005-11-22 | Freescale Semiconductor, Inc. | Magnetoresistive random access memory with reduced switching field variation |

| US7078239B2 (en) | 2003-09-05 | 2006-07-18 | Micron Technology, Inc. | Integrated circuit structure formed by damascene process |

| JP4868431B2 (ja) * | 2003-10-10 | 2012-02-01 | Tdk株式会社 | 磁気記憶セルおよび磁気メモリデバイス |

| US7112454B2 (en) * | 2003-10-14 | 2006-09-26 | Micron Technology, Inc. | System and method for reducing shorting in memory cells |

| US7045838B2 (en) | 2003-10-31 | 2006-05-16 | International Business Machines Corporation | Techniques for coupling in semiconductor devices and magnetic device using these techniques |

| KR20060132611A (ko) * | 2003-11-10 | 2006-12-21 | 씨엠 이노베이션, 인크. | 고체 자기 메모리 시스템 및 방법 |

| TWI226636B (en) * | 2003-12-19 | 2005-01-11 | Ind Tech Res Inst | Magnetic random access memory with high selectivity and low power and production method thereof |

| US7072209B2 (en) * | 2003-12-29 | 2006-07-04 | Micron Technology, Inc. | Magnetic memory having synthetic antiferromagnetic pinned layer |

| US20050269612A1 (en) * | 2004-05-11 | 2005-12-08 | Integrated Magnetoelectronics | Solid-state component based on current-induced magnetization reversal |

| US7027324B2 (en) * | 2004-06-09 | 2006-04-11 | Headway Technologies, Inc. | Method and system for providing common read and write word lines for a segmented word line MRAM array |

| JP2006100424A (ja) * | 2004-09-28 | 2006-04-13 | Tdk Corp | 磁気記憶装置 |

| JP2006100423A (ja) * | 2004-09-28 | 2006-04-13 | Tdk Corp | 磁気記憶装置 |

| US7129098B2 (en) | 2004-11-24 | 2006-10-31 | Freescale Semiconductor, Inc. | Reduced power magnetoresistive random access memory elements |

| US7220968B2 (en) * | 2005-01-19 | 2007-05-22 | Integrated Magnetoelectronics Corporation | Radiation detector having all-metal circuitry operation of which is based on electron spin |

| JP2007059865A (ja) * | 2005-07-27 | 2007-03-08 | Tdk Corp | 磁気記憶装置 |

| JPWO2007043358A1 (ja) * | 2005-10-07 | 2009-04-16 | コニカミノルタオプト株式会社 | セルロースエステルフィルムの製造方法、セルロースエステルフィルム、偏光板及び液晶表示装置 |

| US7745893B2 (en) | 2005-10-17 | 2010-06-29 | Northern Lights Semiconductor Corp. | Magnetic transistor structure |

| JP2007165449A (ja) * | 2005-12-12 | 2007-06-28 | Tdk Corp | 磁気記憶装置 |

| US7768749B2 (en) * | 2006-02-10 | 2010-08-03 | Hitachi Global Storage Technologies Netherlands B.V. | Tunnel MR head with long stripe height stabilized through side-extended bias layer |

| US7630177B2 (en) * | 2006-02-14 | 2009-12-08 | Hitachi Global Storage Technologies Netherlands B.V. | Tunnel MR head with closed-edge laminated free layer |

| US20070236978A1 (en) * | 2006-04-06 | 2007-10-11 | Wilson Jannier M R | Non-volatile Reactive Magnetic Memory device (REMM) |

| US7715224B2 (en) * | 2007-04-16 | 2010-05-11 | Magic Technologies, Inc. | MRAM with enhanced programming margin |

| US7911830B2 (en) | 2007-05-17 | 2011-03-22 | Integrated Magnetoelectronics | Scalable nonvolatile memory |

| ES2328996B1 (es) * | 2007-10-02 | 2010-08-30 | Diseño De Sistemas En Silicio, S.A. | Dispositivo de multiinyeccion inductiva sobre multiples conductores. |

| WO2011103437A1 (en) * | 2010-02-22 | 2011-08-25 | Integrated Magnetoelectronics Corporation | A high gmr structure with low drive fields |

| US9741923B2 (en) * | 2015-09-25 | 2017-08-22 | Integrated Magnetoelectronics Corporation | SpinRAM |

| US10762940B2 (en) | 2016-12-09 | 2020-09-01 | Integrated Magnetoelectronics Corporation | Narrow etched gaps or features in multi-period thin-film structures |

| US10755759B2 (en) | 2018-06-28 | 2020-08-25 | International Business Machines Corporation | Symmetrically programmable resistive synapse for RPU using current-programmed single domain wall ferroelectric |

Family Cites Families (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| BE540911A (ja) * | 1954-08-31 | |||

| JPS63500904A (ja) * | 1985-08-08 | 1988-03-31 | コ−プ デイヴイツド | デジタルデ−タ処理装置用デ−タ記憶装置 |

| US4780848A (en) * | 1986-06-03 | 1988-10-25 | Honeywell Inc. | Magnetoresistive memory with multi-layer storage cells having layers of limited thickness |

| US5173873A (en) * | 1990-06-28 | 1992-12-22 | The United States Of America As Represented By The Administrator Of The National Aeronautics And Space Administration | High speed magneto-resistive random access memory |

| US5251170A (en) * | 1991-11-04 | 1993-10-05 | Nonvolatile Electronics, Incorporated | Offset magnetoresistive memory structures |

| US5343422A (en) * | 1993-02-23 | 1994-08-30 | International Business Machines Corporation | Nonvolatile magnetoresistive storage device using spin valve effect |

| JPH0766033A (ja) * | 1993-08-30 | 1995-03-10 | Mitsubishi Electric Corp | 磁気抵抗素子ならびにその磁気抵抗素子を用いた磁性薄膜メモリおよび磁気抵抗センサ |

| US5477482A (en) * | 1993-10-01 | 1995-12-19 | The United States Of America As Represented By The Secretary Of The Navy | Ultra high density, non-volatile ferromagnetic random access memory |

| US5442508A (en) * | 1994-05-25 | 1995-08-15 | Eastman Kodak Company | Giant magnetoresistive reproduce head having dual magnetoresistive sensor |

-

1995

- 1995-02-13 US US08/388,035 patent/US5587943A/en not_active Expired - Lifetime

-

1996

- 1996-02-08 CA CA002211699A patent/CA2211699C/en not_active Expired - Fee Related

- 1996-02-08 DE DE69609165T patent/DE69609165T2/de not_active Expired - Fee Related

- 1996-02-08 KR KR1019970705516A patent/KR100302174B1/ko not_active IP Right Cessation

- 1996-02-08 JP JP52500696A patent/JP4171067B2/ja not_active Expired - Lifetime

- 1996-02-08 EP EP96904586A patent/EP0809846B1/en not_active Expired - Lifetime

- 1996-02-08 WO PCT/US1996/001653 patent/WO1996025740A1/en active IP Right Grant

- 1996-02-13 TW TW085101769A patent/TW287272B/zh active

Also Published As

| Publication number | Publication date |

|---|---|

| EP0809846B1 (en) | 2000-07-05 |

| EP0809846A4 (en) | 1998-08-26 |

| US5587943A (en) | 1996-12-24 |

| CA2211699A1 (en) | 1996-08-22 |

| TW287272B (ja) | 1996-10-01 |

| EP0809846A1 (en) | 1997-12-03 |

| KR19980702121A (ko) | 1998-07-15 |

| DE69609165T2 (de) | 2001-03-22 |

| WO1996025740A1 (en) | 1996-08-22 |

| KR100302174B1 (ko) | 2001-09-22 |

| DE69609165D1 (de) | 2000-08-10 |

| JPH11501438A (ja) | 1999-02-02 |

| CA2211699C (en) | 2001-07-24 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4171067B2 (ja) | 完全閉磁束作用を備える不揮発性磁気抵抗メモリ | |

| US6381171B1 (en) | Magnetic element, magnetic read head, magnetic storage device, magnetic memory device | |

| JP3891540B2 (ja) | 磁気抵抗効果メモリ、磁気抵抗効果メモリに記録される情報の記録再生方法、およびmram | |

| KR100436318B1 (ko) | 자기저항 효과 소자, 자기저항 효과 메모리 셀, 및 mram | |

| US6069820A (en) | Spin dependent conduction device | |

| US6052263A (en) | Low moment/high coercivity pinned layer for magnetic tunnel junction sensors | |

| JP4934582B2 (ja) | スピンホール効果素子を用いた磁気センサ、磁気ヘッド及び磁気メモリ | |

| US6473275B1 (en) | Dual hybrid magnetic tunnel junction/giant magnetoresistive sensor | |

| US6127045A (en) | Magnetic tunnel junction device with optimized ferromagnetic layer | |

| US7732881B2 (en) | Current-confined effect of magnetic nano-current-channel (NCC) for magnetic random access memory (MRAM) | |

| KR100533299B1 (ko) | 자기 스위칭 소자 및 자기 메모리 | |

| JP3004005B2 (ja) | 磁気トンネル接合素子及び読取りセンサ | |

| US6600184B1 (en) | System and method for improving magnetic tunnel junction sensor magnetoresistance | |

| JP4076197B2 (ja) | 磁性素子、記憶装置、磁気再生ヘッド、3端子素子、及び磁気ディスク装置 | |

| JP2005294376A (ja) | 磁気記録素子及び磁気メモリ | |

| CN101097987A (zh) | 磁性记录元件和磁性存储器 | |

| JP4125465B2 (ja) | 磁気メモリ装置 | |

| JP2004535074A (ja) | 磁気記憶装置および磁気記憶アレイ | |

| Jia et al. | Magnetic sensors for data storage: perspective and future outlook | |

| US7042036B2 (en) | Magnetic memory using single domain switching by direct current | |

| JP4113041B2 (ja) | 磁化制御方法および情報記録装置 | |

| CN100437817C (zh) | 基于环状磁性多层膜的磁性随机存取存储器及其控制方法 | |

| JP4516086B2 (ja) | 磁気抵抗効果素子及びその製造方法、磁気メモリ、磁気ヘッド並びに磁気記録装置 | |

| JPH11154389A (ja) | 磁気抵抗素子、磁性薄膜メモリ素子および該メモリ素子の記録再生方法 | |

| Cockburn | The emergence of high-density semiconductor-compatible spintronic memory |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20040203 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20040706 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20041004 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20041115 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20041228 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20050621 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20051017 |

|

| A911 | Transfer to examiner for re-examination before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20051222 |

|

| A912 | Re-examination (zenchi) completed and case transferred to appeal board |

Free format text: JAPANESE INTERMEDIATE CODE: A912 Effective date: 20060105 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080630 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080808 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110815 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120815 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130815 Year of fee payment: 5 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |