JP4159657B2 - 同期型半導体記憶装置 - Google Patents

同期型半導体記憶装置 Download PDFInfo

- Publication number

- JP4159657B2 JP4159657B2 JP19762598A JP19762598A JP4159657B2 JP 4159657 B2 JP4159657 B2 JP 4159657B2 JP 19762598 A JP19762598 A JP 19762598A JP 19762598 A JP19762598 A JP 19762598A JP 4159657 B2 JP4159657 B2 JP 4159657B2

- Authority

- JP

- Japan

- Prior art keywords

- address

- signal

- response

- internal

- latch circuit

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/22—Read-write [R-W] timing or clocking circuits; Read-write [R-W] control signal generators or management

- G11C7/225—Clock input buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1072—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers for memories with random access ports synchronised on clock signal pulse trains, e.g. synchronous memories, self timed memories

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/06—Address interface arrangements, e.g. address buffers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C8/00—Arrangements for selecting an address in a digital store

- G11C8/10—Decoders

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Dram (AREA)

- For Increasing The Reliability Of Semiconductor Memories (AREA)

- Static Random-Access Memory (AREA)

Description

【発明の属する技術分野】

この発明は同期型半導体記憶装置に関し、さらに詳しくは、アドレス入力レジスタを有するシンクロナスバーストスタティックランダムアクセスメモリ(以下「BSRAM」と略す)に関する。

【0002】

【従来の技術】

近年、コンピュータシステムの高速化のため、マイクロプロセッサと主記憶との間にキャッシュメモリを配置することが一般的となっている。キャッシュメモリとしては、外部クロック信号に同期して動作するBSRAMが広く普及している。

【0003】

図8は、従来のBSRAMの概略構成を示すブロック図である。図8を参照して、このBSRAM1は、メモリセルアレイ2と、クロックバッファ3と、アドレスバッファ4と、プリデコーダ5と、アドレス入力レジスタ6と、デコーダ7と、入出力(I/O)バッファ8とを備える。図8では簡単のために、2ビットの外部アドレス信号EA0,EA1に関連する回路のみが代表的に示されているが、実際にはこれよりも多い複数ビットの外部アドレス信号が与えられる。

【0004】

図9は、図8に示されたBSRAMの動作を示すタイミング図である。図9を参照して、クロックバッファ3は、外部クロック信号CLKに応答して互いに相補的な内部クロック信号φ1およびφ2を生成する。外部アドレス信号EA0,EA1は、内部クロック信号φ1がH(論理ハイ)レベルの期間に入力される。アドレスバッファ4は、外部アドレス信号EA0,EA1に応答して互いに相補的な内部アドレス信号A0,A1および/A0,/A1を生成する。ここで、外部アドレス信号A0の入力から内部アドレス信号/A0の生成までに遅延時間D1が生じる。続いて、プリデコーダ5は、内部アドレス信号A0,/A0,A1,/A1に応答してプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0を生成する。ここで、内部アドレス信号/A0の発生からプリデコード信号/A1・/A0の発生までに遅延時間D2が生じる。このとき内部クロック信号φ1はHレベルであるから、プリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0はアドレス入力レジスタ6の前段のラッチ回路61〜64にラッチされる。続いて、内部クロック信号φ2の立上がりに応答して、前段のラッチ回路61〜64にラッチされたプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0が後段のラッチ回路65〜68にそれぞれラッチされる。アドレス入力レジスタ6は、このラッチされたプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0をデコーダ7に出力する。

【0005】

ここで、ラッチ回路65がプリデコード信号/A1・/A0を確実にラッチするためには、内部クロック信号φ2が立上がる前にラッチ回路61によるプリデコード信号/A1・/A0のラッチが完了していなければならない。すなわち、プリデコード信号/A1・/A0の発生から内部クロック信号φ2の立上がりまでに、アドレス入力レジスタ6のセットアップ時間tsu(reg)が必要である。したがって、外部アドレス信号A0のセットアップ時間tsとしては、上記遅延時間D1およびD2とアドレス入力レジスタ6のセットアップ時間tsu(reg)とを加算した時間が少なくとも必要である。すなわち、ts≧D1+D2+tsu(reg)でなければならない。

【0006】

【発明が解決しようとする課題】

したがって、外部アドレス信号EA0,EA1の入力が遅くなり、外部アドレス信号EA0,EA1の入力から内部クロック信号φ2の立上がりまでの時間がセットアップ時間tsよりも短くなると、ラッチ回路65〜68はプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0をラッチすることができず、その結果、アドレス入力レジスタ6は正しい信号を出力することができない。

【0007】

一般に、RAMには歩留りを向上するために不良メモリセルをスペアメモリセルと置換する冗長回路が設けられるが、この冗長回路にも上記のようなセットアップ時間が必要である。そのため、外部アドレス信号の入力が遅れると、冗長回路も正しく機能しないという問題がある。

【0008】

なお、特開平2−166696号公報(米国特許5,086,414号)には、2段のラッチ回路を備えたメモリが開示されているが、冗長回路は全く開示されていない。

【0009】

それゆえに、この発明の目的は、外部アドレス信号のセットアップ時間が短い同期型半導体記憶装置を提供することである。

【0010】

【課題を解決するための手段】

この発明の1つの局面に従うと、外部クロック信号に同期して動作する同期型半導体記憶装置は、メモリセルアレイと、冗長メモリセルアレイと、クロックバッファと、第1のラッチ回路と、プリデコーダと、第2のラッチ回路と、デコーダと、プログラム回路と、第3のラッチ回路と、冗長デコーダとを備える。クロックバッファは、外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成する。第1のラッチ回路は、第1の内部クロック信号に応答してアドレス信号をラッチする。プリデコーダは、第1のラッチ回路からのアドレス信号に応答してプリデコード信号を生成する。第2のラッチ回路は、第2の内部クロック信号に応答してプリデコーダからのプリデコード信号をラッチする。デコーダは、第2のラッチ回路からのプリデコード信号に応答してメモリセルアレイをアクセスする。プログラム回路は、不良アドレスがプログラム可能で、第1のラッチ回路からのアドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成する。第3のラッチ回路は、第2の内部クロック信号に応答してイネーブル信号をラッチする。冗長デコーダは、第3のラッチ回路からのイネーブル信号に応答して冗長メモリセルアレイをアクセスする。

【0011】

上記同期型半導体記憶装置においては、外部クロック信号の入力が遅れてプリデコード信号の生成が第2の内部クロック信号の立上がりまたは立下がりに間に合わない場合でも、第2のラッチ回路によりプリデコード信号がラッチされる。そのため、外部アドレス信号のセットアップ時間を短くすることができる。

【0012】

好ましくは、上記同期型半導体記憶装置はさらに、アドレスバッファを備える。アドレスバッファは、外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成して第1のラッチ回路に与える。あるいは、上記同期型半導体記憶装置はさらに、第1のアドレスバッファと、第2のアドレスバッファとを備える。第1のアドレスバッファは、外部アドレス信号に応答して内部アドレス信号を生成して第1のラッチ回路に与える。第2のアドレスバッファは、第1のラッチ回路からの内部アドレス信号に応答して、互いに相補的な第1および第2の内部アドレス信号を生成してプリデコーダに与える。

【0013】

この場合、第1のラッチ回路をアドレスバッファとプリデコーダとの間に設けるよりもアドレスバッファ内に設けた方が必要なラッチ回路の数は少なくなる。そのため、第1のラッチ回路に必要なレイアウト面積を低減することができる。

【0014】

好ましくは、上記第1のラッチ回路は、第1のスイッチと、第1のラッチとを含む。第1のスイッチは、第1の内部クロック信号に応答してオンになる。第1のラッチは、第1のスイッチを通して与えられたアドレス信号をラッチする。

【0015】

好ましくは、上記第2のラッチ回路は、第2のスイッチと、第2のラッチとを含む。第2のスイッチは、第2の内部クロック信号に応答してオンになる。第2のラッチは、第2のスイッチを通して与えられたアドレス信号をラッチする。

【0016】

この発明のもう1つの局面に従うと、外部クロック信号に同期して動作する同期型半導体記憶装置は、メモリセルアレイと、冗長メモリセルアレイと、クロックバッファと、アドレスバッファと、複数の第1のラッチ回路と、プリデコーダと、複数の第2のラッチ回路と、デコーダと、プログラム回路と、第3のラッチ回路と、冗長デコーダとを備える。クロックバッファは、外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成する。アドレスバッファは、複数のバッファと、相補アドレス生成手段とを含む。複数のバッファは、外部アドレス信号のビットに対応して設けられる。バッファの各々は、外部アドレス信号の対応するビットを受ける。相補アドレス生成手段は、複数バッファからの外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成する。複数の第1のラッチ回路は、第1および第2の内部アドレス信号のビットに対応して設けられる。第1のラッチ回路の各々は、第1の内部クロック信号に応答して第1および第2の内部アドレス信号の対応するビットをラッチする。プリデコーダは、複数の第1のラッチ回路からの第1および第2の内部アドレス信号に応答してプリデコード信号を生成する。複数の第2のラッチ回路は、プリデコード信号のビットに対応して設けられる。第2のラッチ回路の各々は、第2の内部クロック信号に応答してプリデコーダからのプリコード信号の対応するビットをラッチする。デコーダは、複数の第2のラッチ回路からのプリデコード信号に応答してメモリセルアレイをアクセスする。プログラム回路は、不良アドレスがプログラム可能で、複数の第1のラッチ回路からの第1および第2の内部アドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成する。第3のラッチ回路は、第2の内部クロック信号に応答してイネーブル信号をラッチする。冗長デコーダは、第3のラッチ回路からのイネーブル信号に応答して冗長メモリセルアレイをアクセスする。

【0017】

上記同期型半導体記憶装置においては、第1のラッチ回路がプリデコーダの前でかつアドレスバッファの後に設けられているため、外部アドレス信号の入力が遅れてプリデコード信号の生成が第2の内部クロック信号の立上がりまたは立下がりに間に合わない場合でも、第2のラッチ回路によりプリデコード信号はラッチされる。そのため、外部アドレス信号のセットアップ時間を短くすることができる。

【0018】

この発明のさらにもう1つの局面に従うと、外部クロック信号に同期して動作する同期型半導体記憶装置は、メモリセルアレイと、冗長メモリセルアレイと、クロックバッファと、アドレスバッファとを備える。クロックバッファは、外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成する。アドレスバッファは、複数のバッファと、複数の第1のラッチ回路と、相補アドレス生成手段とを含む。複数のバッファは、外部アドレス信号のビットに対応して設けられる。バッファの各々は、外部アドレス信号の対応するビットを受ける。複数の第1のラッチ回路は、複数のバッファに対応して設けられる。第1のラッチ回路の各々は、第1の内部クロック信号に応答して対応するバッファからの外部アドレス信号のビットをラッチする。相補アドレス生成手段は、複数の第1のラッチ回路からの外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成する。上記半導体記憶装置はさらに、プリデコーダと、複数の第2のラッチ回路と、デコーダと、プログラム回路と、第3のラッチ回路と、冗長デコーダとを備える。プリデコーダは、アドレスバッファからの第1および第2の内部アドレス信号に応答してプリデコード信号を生成する。複数の第2のラッチ回路は、プリデコード信号のビットに対応して設けられる。第2のラッチ回路の各々は、第2の内部クロック信号に応答してプリデコーダからのプリデコード信号の対応するビットをラッチする。デコーダは、複数の第2のラッチ回路からのプリデコード信号に応答してメモリセルアレイをアクセスする。プログラム回路は、不良アドレスがプログラム可能で、複数の第1のラッチ回路からの外部アドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成する。第3のラッチ回路は、第2の内部クロック信号に応答してイネーブル信号をラッチする。冗長デコーダは、第3のラッチ回路からのイネーブル信号に応答して冗長メモリセルアレイをアクセスする。

【0019】

上記同期型半導体記憶装置においては、第1のラッチ回路がアドレスバッファ内に設けられているため、外部アドレス信号の入力が遅れてプリデコード信号の生成が第2の内部クロック信号の立上がりまたは立下がりに間に合わない場合でも、第2のラッチ回路によりプリデコード信号がラッチされる。そのため、外部アドレス信号のセットアップ時間を短くすることができる。

【0020】

【発明の実施の形態】

以下、この発明の実施の形態を図面を参照して詳しく説明する。なお、図中同一または相当部分には同一符号を付してその説明は繰返さない。

【0021】

[実施の形態1]

図1は、この発明の実施の形態1によるBSRAMの概略構成を示すブロック図である。図1を参照して、BSRAM10は、メモリセルアレイ2と、冗長メモリセルアレイ21と、クロックバッファ3と、アドレスバッファ4と、前段アドレス入力レジスタ6Aと、プリデコーダ5と、後段アドレス入力レジスタ6Bと、デコーダ7と、不良アドレスプログラム回路14と、ラッチ回路18と、冗長デコーダ71と、入出力バッファ8とを備える。

【0022】

メモリセルアレイ2は、複数行および複数列に配置された複数のスタティックメモリセル(図示せず)と、複数行に配置され各々が対応する行に配置された複数のメモリセルに接続された複数のワード線(図示せず)と、複数列に配置され各々が対応する列に配置された複数のメモリセルに接続された複数のビット線対(図示せず)とを含む。冗長メモリセルアレイ21は、複数の冗長スタティックメモリセル(図示せず)を含む。冗長スタティックメモリセルは、メモリセルアレイ2中の不良スタティックメモリセルと電気的に置換され得る。

【0023】

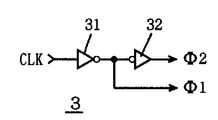

クロックバッファ3は、図2に示されるようにインバータ回路31および32を含む。したがって、クロックバッファ3は、クロック端子11を介して与えられた外部クロック信号CLKに応答して互いに相補的な内部クロック信号φ1およびφ2を生成する。

【0024】

アドレスバッファ4は、バッファ41,42と、インバータ回路43〜48とを含む。バッファ41,42は、外部アドレス信号のビットEA0,EA1に対応して設けられる。外部アドレス信号の第1ビットEA0は、アドレス端子12を介してバッファ41に与えられる。外部アドレス信号の第2ビットEA1は、アドレス端子13を介してバッファ42に与えられる。なお、図1では外部アドレス信号の第1ビットEA0および第2ビットEA1に関連する回路のみが代表的に示されている。インバータ回路43〜48は、複数のバッファ41,42からの外部アドレス信号EA0,EA1に応答して互いに相補的な第1の内部アドレス信号A0,A1および第2の内部アドレス信号/A0,/A1を生成する。

【0025】

前段アドレス入力レジスタ6Aは、複数のラッチ回路61〜64を含む。ラッチ回路61〜64は内部アドレス信号のビット/A0,A0,/A1,A1に対応して設けられる。ラッチ回路61〜64の各々は、内部クロック信号φ1に応答して内部アドレス信号の対応するビットをラッチする。

【0026】

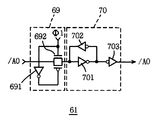

ラッチ回路61は、たとえば図3に示されるように、スイッチ69と、ラッチ70とを含む。スイッチ69は、インバータ回路691と、転送ゲート692とを含む。転送ゲート692は、内部クロック信号φ1に応答してオンになる。ラッチ70は、インバータ回路701〜703を含む。ラッチ70は、スイッチ69を通して与えられたアドレス信号の対応するビット/A0をラッチする。したがって、ラッチ回路61は、内部クロック信号φ1に応答して内部アドレス信号の対応するビット/A0をラッチする。その他のラッチ回路62〜64もラッチ回路61と同様に構成される。

【0027】

再び図1を参照して、プリデコーダ5は、NAND回路51〜54と、インバータ回路55〜58とを含む。したがって、プリデコーダ5は、前段アドレス入力レジスタ6Aからの内部アドレス信号/A0,A0,/A1,A1に応答してプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0を生成する。

【0028】

後段アドレス入力レジスタ6Bは、複数のラッチ回路65〜68を含む。ラッチ回路65〜68は、プリデコード信号のビット/A1・/A0,/A1・A0,A1・/A0,A1・A0に対応して設けられる。ラッチ回路65〜68の各々は、内部クロック信号φ2に応答してプリデコーダ5からのプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0の対応するビットをラッチする。ラッチ回路65〜68は、図3に示されたラッチ回路61と同様に構成される。

【0029】

デコーダ7は、後段アドレス入力レジスタ6Bからのプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0に応答してメモリセルアレイ2をアクセスする。より具体的には、デコーダ7は、メモリセルアレイ2中のワード線を選択する行デコーダ(図示せず)と、メモリセルアレイ2中のビット線対を選択する列デコーダ(図示せず)とを含む。

【0030】

不良アドレスプログラム回路14は、不良アドレスがプログラム可能で、前段アドレス入力レジスタ6Aからの内部アドレス信号/A0,A0,/A1,A1がそのプログラムされた不良アドレスを指定するときスペア素子イネーブル信号SEEを生成する。不良アドレスプログラム回路14の詳細は後述する。

【0031】

ラッチ回路18は、内部クロック信号φ2に応答してスペア素子イネーブル信号SEEをラッチする。ラッチ回路18は、図3に示されたラッチ回路61と同様に構成される。

【0032】

冗長デコーダ71は、ラッチ回路18からのスペア素子イネーブル信号SEEに応答して冗長メモリセルアレイ21をアクセスする。すなわち、冗長デコーダ71は、メモリセルアレイ2中の不良部分を冗長メモリセルアレイ21と置換する。

【0033】

入出力バッファ8は、メモリセルアレイ2または冗長メモリセルアレイ21から読出されたデータを外部に出力したり、外部から入力されたデータをメモリセルアレイ2または冗長メモリセルアレイ21に書込んだりする。

【0034】

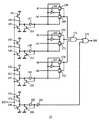

不良アドレスプログラム回路14は、図4に示されるように、PチャネルMOSトランジスタ141〜144と、NチャネルMOSトランジスタ145〜148と、ヒューズ149〜152と、NチャネルMOSトランジスタ153〜156と、インバータ回路157〜161とを含む。この不良アドレスプログラム回路14は、電源投入直後の所定期間だけHレベルとなるリセット信号RSTを受ける。リセット信号RSTは、トランジスタ141〜148のゲートに与えられる。

【0035】

この不良アドレスプログラム回路14はさらに、インバータ回路165〜167と、転送ゲート168〜173と、NAND回路174と、NOR回路(負論理)175とを含む。前段アドレス入力レジスタ6Aからの内部アドレス信号A0,/A0,A1,/A1,A2,/A2は、転送ゲート168〜173を介してNAND回路174に与えられる。NOR回路175は、NAND回路174の出力信号およびインバータ回路161の出力信号に応答してスペア素子イネーブル信号SEEを生成する。なお、図4では内部アドレス信号A0,/A0,A1,/A1,A2,/A2に関連する回路のみが代表的に示されている。

【0036】

メモリセルアレイ2中に不良が存在しない場合、つまり冗長メモリセルアレイ21、冗長デコーダ71などの冗長回路を使用しない場合、いずれのヒューズ149〜152も切断されない。したがって、電源投入後十分な時間が経過すると、リセット信号RSTはL(論理ロー)レベルとなり、これに応じてインバータ回路161はHレベルの出力信号をNOR回路175に与える。そのため、NAND回路174の出力信号に関係なくNOR回路175はスペア素子イネーブル信号SEEをLレベルに非活性化する。

【0037】

一方、メモリセルアレイ2中に不良が存在する場合、つまり冗長回路を使用する場合、ヒューズ152を切断するとともに、いずれかのヒューズ149〜151を切断することによりその不良アドレスがプログラムされる。したがって、電源投入直後にリセット信号RSTがHレベルになると、トランジスタ144および148からなるインバータ回路はLレベルの出力信号をインバータ回路160に与え、インバータ回路160およびトランジスタ156からなるラッチ回路はこの出力信号をラッチする。その後、リセット信号RSTはLレベルになるが、ヒューズ152が切断されているので、インバータ160およびトランジスタ156からなるラッチ回路はその出力信号をHレベルに維持し、そのため、インバータ回路161はその出力信号をLレベルに維持する。

【0038】

たとえば(A0,A1,A2)=(0,1,0)が不良の場合、ヒューズ149および151が切断され、ヒューズ150は切断されない。電源投入後所定期間が経過すると、インバータ回路157およびトランジスタ153からなるラッチ回路ならびにインバータ回路159およびトランジスタ155からなるラッチ回路は、上記と同様にそれぞれの出力信号をHレベルに維持するが、インバータ回路158およびトランジスタ154からなるラッチ回路はその出力信号をLレベルに変える。したがって、転送ゲート169,170,173がオンになり、転送ゲート168,171,172がオフになるため、内部アドレス信号/A0,A1,/A2がNAND回路174に与えられる。したがって、(A0,A1,A2)=(0,1,0)の場合、NAND回路174の3つの入力信号はすべてHレベルとなり、Lレベルの出力信号がNOR回路175に与えられる。そのため、NOR回路175はスペア素子イネーブル信号SEEをHレベルに活性化する。

【0039】

上述したようにこの発明の実施の形態1では、図8に示されたアドレス入力レジスタ6が前段アドレス入力レジスタ6Aと後段アドレス入力レジスタ6Bとに分割され、前段アドレス入力レジスタ6Aがアドレスバッファ4とプリデコーダ5との間に挿入されている。

【0040】

次に、上記のように構成されたBSRAM10の動作を説明する。

外部アドレス信号EA0,EA1のセットアップ時間tsが十分に長い場合、つまり内部クロック信号φ2の立上がりよりも十分前に外部アドレス信号EA0,EA1が入力された場合、従来と同様にプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0は内部クロック信号φ2の立上がりよりも前に生成されるから、ラッチ回路65〜68はプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0を確実にラッチすることができる。

【0041】

図5は、外部アドレス信号のセットアップ時間tsが短い場合の動作を示すタイミング図である。外部アドレス信号EA0,EA1のセットアップ時間tsが短い場合、つまり内部クロック信号φ2の立上がりよりもほんの少し前に外部アドレス信号EA0,EA1が入力された場合、プリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0の生成が内部クロック信号φ2の立上がりに間に合わない場合がある。アドレスバッファ4による遅延時間をD1とし、前段アドレス入力レジスタ6Aによる遅延時間をLDとし、プリデコーダ5による遅延時間をD2とすると、外部アドレス信号EA0,EA1の入力からプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0の生成までの総遅延時間TDはD1+LD+D2となる。このようにプリデコード信号の生成は従来よりも時間LDだけ遅くなるが、ラッチ回路61〜64がプリデコーダ5よりも前に設けられているため、プリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0は直接ラッチ回路65〜68に与えられる。したがって、プリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0は内部クロック信号φ2の立上がりよりも遅く生成されるが、このとき内部クロック信号φ2はHレベルであるから、その生成されたプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0はラッチ回路65〜68にラッチされる。したがって、後段アドレス入力レジスタ6Bは正しいプリデコード信号/A1・/A0,/A1・A0,A1・/A0,A1・A0をデコーダ7に与えることができる。

【0042】

同様に、不良アドレスプログラム回路14によるスペア素子イネーブル信号SEEの生成が内部クロック信号φ2の立上がりより遅れたとしても、ラッチ回路18はスペア素子イネーブル信号SEEをラッチして冗長デコーダ71に与えることができる。

【0043】

以上のようにこの実施の形態1によれば、プリデコーダ5がラッチ回路61〜64とラッチ回路65〜68との間に設けられているため、外部アドレス信号EA0,EA1のセットアップ時間tsを短くすることができる。また、不良アドレスプログラム回路14もラッチ回路61〜64とラッチ回路18との間に設けられているため、冗長回路が使用されている場合でも外部アドレス信号EA0,EA1のセットアップ時間tsを短くすることができる。

【0044】

[実施の形態2]

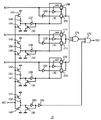

図6は、この発明の実施の形態2によるBSRAMの概略構成を示すブロック図である。図1に示された実施の形態1と異なり、図6に示されるように、この実施の形態2によるBSRAM20では前段アドレス入力レジスタ6AAがアドレスバッファ40内に設けられる。より具体的には、前段アドレス入力レジスタ6AAは、バッファ41,42を含む前段アドレスバッファ40Aと、インバータ回路43〜48を含む後段アドレスバッファ40Bとの間に設けられる。また、この実施の形態2では、前段アドレス入力レジスタ6AAからの内部アドレス信号A0,A1,A2が不良アドレスプログラム回路15に与えられる。

【0045】

したがって、この不良アドレスプログラム回路15は、図4に示された不良アドレスプログラム回路14の構成に加えて、図7に示されるように、複数のインバータ回路162〜164を含む。インバータ回路162〜164は、アドレス信号のビットA0,A1,A2に対応して設けられる。インバータ回路162〜164は、アドレス信号A0,A1,A2に応答してこれと相補的なアドレス信号/A0,/A1,/A2を生成する。

【0046】

この実施の形態2によれば、前段アドレス入力レジスタ6AAがアドレスバッファ40内に設けられているため、前段アドレス入力レジスタ6AAを構成するラッチ回路69,70の数を上記実施の形態1よりも少なくすることができる。そのため、前段アドレス入力レジスタ6AAに必要なレイアウト面積を低減することができる。

【0047】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味および範囲内でのすべての変更が含まれることが意図される。

【0048】

【発明の効果】

以上のようにこの発明によれば、プリデコーダが第1のラッチ回路と第2のラッチ回路との間に設けられ、かつプログラム回路が第1のラッチ回路と第3のラッチ回路との間に設けられているため、外部アドレス信号のセットアップ時間を短くすることができる。

【0049】

第1のラッチ回路がアドレスバッファ内に設けられる場合は、必要な第1のラッチ回路の数を少なくすることができる。

【図面の簡単な説明】

【図1】 この発明の実施の形態1によるBSRAMの概略構成を示すブロック図である。

【図2】 図1に示されたクロックバッファの構成を示す回路図である。

【図3】 図1に示されたラッチ回路の構成を示す回路図である。

【図4】 図1に示された不良アドレスプログラム回路の構成を示す回路図である。

【図5】 図1に示されたBSRAMの動作を示すタイミング図である。

【図6】 この発明の実施の形態2によるBSRAMの概略構成を示すブロック図である。

【図7】 図6に示された不良アドレスプログラム回路の構成を示す回路図である。

【図8】 従来のBSRAMの概略構成を示すブロック図である。

【図9】 図8に示されたBSRAMの動作を示すタイミング図である。

【符号の説明】

2 メモリセルアレイ、3 クロックバッファ、4,40 アドレスバッファ、5 プリデコーダ、6A,6AA 前段アドレス入力レジスタ、6B 後段アドレス入力レジスタ、7 デコーダ、10,20 BSRAM、14,15 不良アドレスプログラム回路、18,61〜70 ラッチ回路、21 冗長メモリセルアレイ、69 スイッチ、70 ラッチ、71 冗長デコーダ、EA0,EA1 外部アドレス信号、A0,/A0,A1,/A1,A2,/A2 内部アドレス信号、A1・A0,/A1・A0,A1・/A0,/A1・/A0 プリデコード信号、CLK 外部クロック信号、φ1,φ2 内部クロック信号、SEE スペア素子イネーブル信号。

Claims (7)

- 外部クロック信号に同期して動作する同期型半導体記憶装置であって、

メモリセルアレイと、

冗長メモリセルアレイと、

前記外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成するクロックバッファと、

前記第1の内部クロック信号に応答してアドレス信号をラッチする第1のラッチ回路と、

前記第1のラッチ回路からのアドレス信号に応答してプリデコード信号を生成するプリデコーダと、

前記第2の内部クロック信号に応答して前記プリデコーダからのプリデコード信号をラッチする第2のラッチ回路と、

前記第2のラッチ回路からのプリデコード信号に応答して前記メモリセルアレイをアクセスするデコーダと、

不良アドレスがプログラム可能で、前記第1のラッチ回路からのアドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成するプログラム回路と、

前記第2の内部クロック信号に応答して前記イネーブル信号をラッチする第3のラッチ回路と、

前記第3のラッチ回路からのイネーブル信号に応答して前記冗長メモリセルアレイをアクセスする冗長デコーダとを備える、同期型半導体記憶装置。 - 前記同期型半導体記憶装置はさらに、

外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成して前記第1のラッチ回路に与えるアドレスバッファを備える、請求項1に記載の同期型半導体記憶装置。 - 前記同期型半導体記憶装置はさらに、

外部アドレス信号に応答して内部アドレス信号を生成して前記第1のラッチ回路に供給する第1のアドレスバッファと、

前記第1のラッチ回路からの内部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成して前記プリデコーダに与える第2のアドレスバッファとを備える、請求項1に記載の同期型半導体記憶装置。 - 前記第1のラッチ回路は、

前記第1の内部クロック信号に応答してオンになる第1のスイッチと、

前記第1のスイッチを通して与えられたアドレス信号をラッチする第1のラッチとを含む、請求項1から請求項3のいずれか1項に記載の同期型半導体記憶装置。 - 前記第2のラッチ回路は、

前記第2の内部クロック信号に応答してオンになる第2のスイッチと、

前記第2のスイッチを通して与えられたアドレス信号をラッチする第2のラッチとを含む、請求項1から請求項4のいずれか1項に記載の同期型半導体記憶装置。 - 外部クロック信号に同期して動作する同期型半導体記憶装置であって、

メモリセルアレイと、

冗長メモリセルアレイと、

前記外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成するクロックバッファと、

アドレスバッファとを備え、前記アドレスバッファは、

外部アドレス信号のビットに対応して設けられ、各々が前記外部アドレス信号の対応するビットを受ける複数のバッファと、

前記複数のバッファからの外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成する相補アドレス生成手段とを含み、

前記同期型半導体記憶装置はさらに、

前記第1および第2の内部アドレス信号のビットに対応して設けられ、各々が前記第1の内部クロック信号に応答して前記第1および第2の内部アドレス信号の対応するビットをラッチする複数の第1のラッチ回路と、

前記複数の第1のラッチ回路からの第1および第2の内部アドレス信号に応答してプリデコード信号を生成するプリデコーダと、

前記プリデコード信号のビットに対応して設けられ、各々が前記第2の内部クロック信号に応答して前記プリデコーダからのプリデコード信号の対応するビットをラッチする複数の第2のラッチ回路と、

前記複数の第2のラッチ回路からのプリデコード信号に応答して前記メモリセルアレイをアクセスするデコーダと、

不良アドレスがプログラム可能で、前記複数の第1のラッチ回路からの第1および第2の内部アドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成するプログラム回路と、

前記第2の内部クロック信号に応答して前記イネーブル信号をラッチする第3のラッチ回路と、

前記第3のラッチ回路からのイネーブル信号に応答して前記冗長メモリセルアレイをアクセスする冗長デコーダとを備える、同期型半導体記憶装置。 - 外部クロック信号に同期して動作する同期型半導体記憶装置であって、

メモリセルアレイと、

冗長メモリセルアレイと、

前記外部クロック信号に応答して互いに相補的な第1および第2の内部クロック信号を生成するクロックバッファと、

アドレスバッファとを備え、前記アドレスバッファは、

外部アドレス信号のビットに対応して設けられ、各々が前記外部アドレス信号の対応するビットを受ける複数のバッファと、

前記複数のバッファに対応して設けられ、各々が前記第1の内部クロック信号に応答して対応するバッファからの外部アドレス信号のビットをラッチする複数の第1のラッチ回路と、

前記複数の第1のラッチ回路からの外部アドレス信号に応答して互いに相補的な第1および第2の内部アドレス信号を生成する相補アドレス生成手段とを含み、

前記同期型半導体記憶装置はさらに、

前記アドレスバッファからの第1および第2の内部アドレス信号に応答してプリデコード信号を生成するプリデコーダと、

前記プリデコード信号のビットに対応して設けられ、各々が前記第2の内部クロック信号に応答して前記プリデコーダからのプリデコード信号の対応するビットをラッチする複数の第2のラッチ回路と、

前記複数の第2のラッチ回路からのプリデコード信号に応答して前記メモリセルアレイをアクセスするデコーダと、

不良アドレスがプログラム可能で、前記複数の第1のラッチ回路からの外部アドレス信号がそのプログラムされた不良アドレスを指定するときイネーブル信号を生成するプログラム回路と、

前記第2の内部クロック信号に応答して前記イネーブル信号をラッチする第3のラッチ回路と、

前記第3のラッチ回路からのイネーブル信号に応答して前記冗長メモリセルアレイをアクセスする冗長デコーダとを備える、同期型半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19762598A JP4159657B2 (ja) | 1998-07-13 | 1998-07-13 | 同期型半導体記憶装置 |

| US09/212,308 US6026036A (en) | 1998-07-13 | 1998-12-16 | Synchronous semiconductor memory device having set up time of external address signal reduced |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP19762598A JP4159657B2 (ja) | 1998-07-13 | 1998-07-13 | 同期型半導体記憶装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2000030463A JP2000030463A (ja) | 2000-01-28 |

| JP2000030463A5 JP2000030463A5 (ja) | 2005-10-27 |

| JP4159657B2 true JP4159657B2 (ja) | 2008-10-01 |

Family

ID=16377605

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP19762598A Expired - Fee Related JP4159657B2 (ja) | 1998-07-13 | 1998-07-13 | 同期型半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6026036A (ja) |

| JP (1) | JP4159657B2 (ja) |

Families Citing this family (20)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5656953A (en) * | 1995-05-31 | 1997-08-12 | Texas Instruments Incorporated | Low overhead memory designs for IC terminals |

| US6069839A (en) * | 1998-03-20 | 2000-05-30 | Cypress Semiconductor Corp. | Circuit and method for implementing single-cycle read/write operation(s), and random access memory including the circuit and/or practicing the method |

| KR100301047B1 (ko) * | 1998-10-02 | 2001-09-06 | 윤종용 | 2비트프리페치용칼럼어드레스디코더를갖는반도체메모리장치 |

| US6745354B2 (en) | 2000-02-02 | 2004-06-01 | Broadcom Corporation | Memory redundancy implementation |

| US6411557B2 (en) * | 2000-02-02 | 2002-06-25 | Broadcom Corporation | Memory architecture with single-port cell and dual-port (read and write) functionality |

| US7173867B2 (en) * | 2001-02-02 | 2007-02-06 | Broadcom Corporation | Memory redundancy circuit techniques |

| US8164362B2 (en) * | 2000-02-02 | 2012-04-24 | Broadcom Corporation | Single-ended sense amplifier with sample-and-hold reference |

| JP4156781B2 (ja) * | 2000-05-30 | 2008-09-24 | 株式会社東芝 | 半導体メモリ集積回路 |

| US6714467B2 (en) * | 2002-03-19 | 2004-03-30 | Broadcom Corporation | Block redundancy implementation in heirarchical RAM's |

| JP2003123478A (ja) | 2001-10-03 | 2003-04-25 | Fujitsu Ltd | 半導体装置及び半導体記憶装置 |

| WO2004076928A2 (en) | 2003-02-21 | 2004-09-10 | Middleby Corporation | Self-cleaning oven |

| JP4641726B2 (ja) * | 2004-01-07 | 2011-03-02 | パナソニック株式会社 | 半導体記憶装置 |

| US8087407B2 (en) | 2004-03-23 | 2012-01-03 | Middleby Corporation | Conveyor oven apparatus and method |

| US9585400B2 (en) | 2004-03-23 | 2017-03-07 | The Middleby Corporation | Conveyor oven apparatus and method |

| US8839714B2 (en) | 2009-08-28 | 2014-09-23 | The Middleby Corporation | Apparatus and method for controlling a conveyor oven |

| US20110048244A1 (en) * | 2009-08-28 | 2011-03-03 | Wiker John H | Apparatus and method for controlling a combustion blower in a gas-fueled conveyor oven |

| US8811109B2 (en) * | 2012-02-27 | 2014-08-19 | Qualcomm Incorporated | Memory pre-decoder circuits employing pulse latch(es) for reducing memory access times, and related systems and methods |

| US8923090B1 (en) | 2013-09-24 | 2014-12-30 | Lsi Corporation | Address decoding circuits for reducing address and memory enable setup time |

| JP6556435B2 (ja) * | 2014-09-17 | 2019-08-07 | 東芝メモリ株式会社 | 半導体集積回路 |

| IT202000029771A1 (it) * | 2020-12-03 | 2022-06-03 | Sk Hynix Inc | Architettura di latch |

Family Cites Families (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5086414A (en) * | 1988-11-17 | 1992-02-04 | Hitachi, Ltd. | Semiconductor device having latch means |

| JPH09147595A (ja) * | 1995-11-24 | 1997-06-06 | Nec Corp | 半導体記憶装置 |

| JPH1074396A (ja) * | 1996-08-30 | 1998-03-17 | Nec Corp | 半導体記憶装置 |

| JP3361018B2 (ja) * | 1996-11-11 | 2003-01-07 | 株式会社東芝 | 半導体記憶装置 |

| JPH10334689A (ja) * | 1997-05-30 | 1998-12-18 | Fujitsu Ltd | 半導体記憶装置 |

-

1998

- 1998-07-13 JP JP19762598A patent/JP4159657B2/ja not_active Expired - Fee Related

- 1998-12-16 US US09/212,308 patent/US6026036A/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| US6026036A (en) | 2000-02-15 |

| JP2000030463A (ja) | 2000-01-28 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP4159657B2 (ja) | 同期型半導体記憶装置 | |

| US6260128B1 (en) | Semiconductor memory device which operates in synchronism with a clock signal | |

| US7451363B2 (en) | Semiconductor integrated circuit including memory macro | |

| JP5099674B2 (ja) | 半導体集積回路 | |

| US9183949B2 (en) | Semiconductor device | |

| JPH09231767A (ja) | スタティック型半導体記憶装置 | |

| JP2689768B2 (ja) | 半導体集積回路装置 | |

| JPH06119796A (ja) | 欠陥メモリセル救済用デコーダ | |

| US6967882B1 (en) | Semiconductor memory including static memory | |

| JPH0383299A (ja) | 半導体記憶装置 | |

| JP2000322900A (ja) | 半導体記録装置 | |

| JP3800463B2 (ja) | 同期型半導体メモリ装置 | |

| US7113434B2 (en) | Semiconductor integrated circuit having programmable delays for generating timing signals with time difference being non-integral multiple of clock cycle | |

| JP2001344978A (ja) | 半導体メモリ集積回路 | |

| JP3857697B2 (ja) | 半導体集積回路、半導体記憶装置及び半導体記憶装置のテスト方法 | |

| US7032083B1 (en) | Glitch-free memory address decoding circuits and methods and memory subsystems using the same | |

| JP2848314B2 (ja) | 半導体記憶装置 | |

| JP2001338490A (ja) | 半導体記憶装置 | |

| US5796271A (en) | Memory array having redundant word line | |

| US5461586A (en) | Self-timed redundancy circuit | |

| JP2630274B2 (ja) | 半導体記憶装置 | |

| JP2006252718A (ja) | 半導体記憶装置 | |

| JPH11224499A (ja) | 半導体装置、その製造方法およびそのアドレス検出回路 | |

| KR20040094355A (ko) | 메모리 회로 | |

| JP2001035184A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050706 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050706 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20080704 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080708 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080716 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110725 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120725 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130725 Year of fee payment: 5 |

|

| LAPS | Cancellation because of no payment of annual fees |