JP4154006B2 - 半導体記憶装置 - Google Patents

半導体記憶装置 Download PDFInfo

- Publication number

- JP4154006B2 JP4154006B2 JP14231097A JP14231097A JP4154006B2 JP 4154006 B2 JP4154006 B2 JP 4154006B2 JP 14231097 A JP14231097 A JP 14231097A JP 14231097 A JP14231097 A JP 14231097A JP 4154006 B2 JP4154006 B2 JP 4154006B2

- Authority

- JP

- Japan

- Prior art keywords

- bit line

- data

- sense amplifier

- circuit

- potential

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/21—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements

- G11C11/34—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices

- G11C11/40—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors

- G11C11/401—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using electric elements using semiconductor devices using transistors forming cells needing refreshing or charge regeneration, i.e. dynamic cells

- G11C11/4063—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing

- G11C11/407—Auxiliary circuits, e.g. for addressing, decoding, driving, writing, sensing or timing for memory cells of the field-effect type

- G11C11/409—Read-write [R-W] circuits

- G11C11/4096—Input/output [I/O] data management or control circuits, e.g. reading or writing circuits, I/O drivers or bit-line switches

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/10—Input/output [I/O] data interface arrangements, e.g. I/O data control circuits, I/O data buffers

- G11C7/1048—Data bus control circuits, e.g. precharging, presetting, equalising

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C7/00—Arrangements for writing information into, or reading information out from, a digital store

- G11C7/12—Bit line control circuits, e.g. drivers, boosters, pull-up circuits, pull-down circuits, precharging circuits, equalising circuits, for bit lines

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Databases & Information Systems (AREA)

- Dram (AREA)

Description

【発明の属する技術分野】

本発明は半導体記憶装置に関し、より特定すればDRAM(Dynamic Random Access Memory)装置に関する。更に特定すれば、本発明は、DRAM装置の記憶素子(セル)からデータを読み出す動作に関する。

【0002】

【従来の技術】

図28は、従来のDRAM装置の要部を示す回路図である。図示する回路部分は1対のビット線BL、/BLに関するものである。DRAM装置は、センスアンプ部10及びこれに接続される2つのセルアレイ部12、14を有する。センスアンプ部10は、2つのセルアレイ部12、14に共通に設けられている。なお、セルアレイ部14の構成はセルアレイ部12の構成と同一なので、図を簡単化するために省略してある。

【0003】

セルアレイ部12は、1対のビット線BL、/BLに接続された複数のセルMCを有する。セルMCは交互にビット線BL、/BLに接続されている(フォールデッド型ビット線構成)。各セルMCは、1つのキャパシタと1つのトランジスタからなる。ビット線リセット信号BRSTを受けるトランジスタは、この信号に応答してビット線B、/BLをショートしてVCC/2にプリチャージ(リセット)する。

【0004】

センスアンプ部10は、フリップフロップ回路16、データ入出力回路18及びトランスファーゲート回路20、22を有する。フリップフロップ回路16は4つのトランジスタからなり、一方のビット線の電位を制御信号PSA、NSAのいずれか一方の電位に引っ張り、他方のビット線電位を他方の制御信号の電位に引っ張る。トランスファゲート回路20と22はそれぞれ、ビット線BLと/BLにそれぞれ設けられた2つのトランジスタを有し、トランスファ制御信号BT0、BT1に従いセルアレイ部12と14のどちらか一方をセンスアンプ部10に接続させる。データ入出力回路18は2つのトランジスタからなり、コラム選択信号CLを受けてビット線BL、/BLをそれぞれデータ線DB、/DBに接続する。

【0005】

図29は、図28に示すDRAM装置の読み出し動作を示す図である。DRAM装置は、1周期が10nsのクロック信号CLKに同期して動作するものとする。読み出し動作の1サイクルは、ローアドレス、コラムアドレス、ビット線プリチャージのコマンドROW、COL、PREを受けて行われ、図示の場合90nsである。

【0006】

ビット線BL、/BLがVCC/2にプリチャージされている(リセットされている)状態で、ローアドレスのコマンドROWは外部から与えられる。ローアドレスは、図28では図示を省略してあるローアドレスデコーダでデコードされ、ワード線WLが駆動される。いま、この選択されたワード線WLは、図28に示すワード線WLであるとする。これにより、ワード線WLは低電位側の電源電圧VSSから、高電位側電源電圧VCCに向けて立ち上がる。選択されたワード線に接続されているセルに保持されているデータ(0か1)に応じて、選択側のビット線の電位が変化する。図29の例では、選択側のビット線はビット線BLであり、メモリセルMCにはデータ0が保持されている場合である。よって、ビット線BLの電位はVCC/2から下降し始める。このとき、非選択ビット線/BLはVCC/2のままである。このビット線BLと/BLの相対的な電位の変化を、センスアンプ16がセンスすることで、図29に示すように、ビット線BLの電位はVSS側に引っ張られ、ビット線/BLの電位はVCC側に引っ張られる。

【0007】

センスアンプ16がセンス動作を開始した後に、コラムアドレスのコマンドCOLによりコラム選択信号CLがアクティブ(オン)になり、センスアンプ16のセンス動作により決まったビット線BL、/BLの電位がデータ入出力回路18を介してデータ線DB、/DBにそれぞれ出力される(このタイミングを図29では、DATAとして示してある)。それとともに、ビット線プリチャージのコマンドPREを外部から受けてビット線リセット信号BRSTがアクティブになり、ビット線BL、/BLはVCC/2にリセット(プリチャージ)される。これにより、次の読み出し動作に備える。

【0008】

このようにして、読み出し動作の1サイクルが行われる。

【0009】

【発明が解決しようとする課題】

しかしながら、上記従来の半導体記憶装置は、次の課題を有する。

上述したように、読み出し動作は、必ずビット線をリセットするために、VCC/2にプリチャージする必要がある。読み出し動作の1サイクルには必ずVCC/2にビット線BL、/BLをプリチャージするための時間が必要なので、読み出し動作の高速化の妨げになっている。

【0010】

したがって、本発明は上記従来技術の課題を解決し、読み出し動作を高速化した半導体記憶装置を提供することを目的とする。

【0011】

【課題を解決するための手段】

記憶素子、ワード線及びビット線を含む半導体記憶装置において、ビット線をリセットするために、ビット線のリセット電位を前回の読み出しサイクルで読み出したデータに応じて決めることを特徴とする半導体記憶装置である。図1を参照して説明すると、ワード線WLが立ち上がり、ビット線BLからデータ(この場合”1”)が読み出され、ビット線BLはVCCレベルに立ち上がる。よって、次の読み出し動作のために、他方のビット線/BLの電位をVCCレベルまで立ち上げる。すなわち、ビット線BL、/BLとも読み出したデータの値に応じたリセット状態に設定される(プリチャージ)。次の読み出しサイクルではデータ”0”が読み出され、ビット線BLはVSSレベルに立ち下がる。よって、他方のビット線/BLを同じくVSSレベルに立ち下げることで、ビット線をリセット状態にする。

【0012】

このように、ビット線のリセット電位が前回の読み出しサイクルで読み出されたデータに依存して設定できるので、従来のようにVCC/2に各サイクル毎にプリチャージする必要がなく、高速動作が可能となる。

また、前記ビット線が対になっており、前回の読み出しサイクルでデータを読み出したことで設定されたビット線対の一方の電位に、他方のビット線の電位を一致させることで、ビット線をリセットすることを特徴とする。これはビット線リセットの一例を規定したもので、上述の効果と同様の効果が得られる。

【0013】

また、各読み出しサイクルにおけるリセット電位は、高電源電圧又は低電源電圧のいずれか一方であることを特徴とする。リセット電位の一例を規定したもので、従来のVCC/2にプリチャージするリセット方法とは異なる。

また、前記ビット線に選択的に接続されるダミーセルを有し、ダミーセルからデータを読み出すことで、選択されたセルからデータが読み出された一方のビット線の電位とは異なる電位に他方のビット線を設定することを特徴とす。このようにビット線間に電位差を設けることで、センスアンプで電位差をセンスすることでデータの読み出しが可能となる。

【0014】

また、各読み出しサイクルでは、ビット線対の一方のみを駆動することを特徴とする。これにより、より高速な動作が可能となる。

また、前回の読み出しサイクルでデータが外部に出力される前に、次回の読み出しサイクルを開始することを特徴とする。リセット電位の設定により高速読み出し動作が可能になるので、このような読み出しサイクルを実現できる。

【0015】

また、ビット線に接続されたセンスアンプを、ビット線のリセットと同様に、前回の読み出しサイクルで読み出したデータに応じて決めることを特徴とする半導体記憶装置である。ビット線と同様にセンスアンプも、前回の読み出しサイクルで読み出したデータに応じてリセット状態を設定する。

【0016】

また、ビット線の両端にそれぞれセンスアンプを有し、一方のセンスアンプがセンス動作をする場合には、他方のセンスアンプで前記一方のセンスアンプをリセットすることを特徴とする。本発明の第1の実施の形態に対応するもので、センスアンプを交互にオン(活性化)することで、一方が他方のセンスアンプをリセットすることができる。

【0017】

また、ビット線に接続されたセンスアンプをリセットするために、前回の読み出しサイクルで読み出したデータに応じてセンスアンプのリセット状態にする回路を設けたことを特徴とする。この回路は、たとえば本発明の第4の実施の形態のプリチャージ回路130に相当するもので、読み出したデータをラッチし(プリチャージ回路130で)、このラッチした状態と同一となるようセンスアンプをリセット(プリチャージ)する。

【0018】

また、ビット線の両端にそれぞれセンスアンプを有し、ビット線に接続されたセンスアンプをリセットするために、前回の読み出しサイクルで読み出したデータに応じて上記それぞれのセンスアンプをリセット状態にする回路を上記センスアンプに共通に設けたことを特徴とする。この回路は、たとえば本発明の第5の実施の形態のプリチャージ回路130に相当する。この第5の実施の形態は、一方のビット線から読み出したデータをラッチして、そのビット線に接続されているセンスアンプを読み出したデータと同じ状態にリセットし、他方のビット線に接続されているセンスアンプをこれとは異なる状態にリセットする。

【0019】

また、ビット線とデータバスとの間に設けられ、コラム選択信号に応じて制御されるデータ入出力回路と、センスアンプとデータバスとの間に位置し、ビット線に接続されるセンスアンプのオンオフに応じて制御されるゲートとを有することを特徴とする。この構成は本発明の第6及び第7の実施の形態に相当するもので、データ入出力回路(第6の実施の形態では、データ入出力回路140に相当)とは別に、上記ゲート(第6の実施の形態では、貫通電流阻止ゲート160に相当)を設けることで、たとえばデータ入出力回路が活性化してデータバスとビット線とが接続可能な状態となっても、センスアンプが活性化されない限りデータバスとビット線とが実際に接続されることはない。よって、データバスからビット線を通りセンスアンプに向かう電流のパスは遮断され、このルートに貫通電流が流れることを阻止できる。

【0020】

また、前記データ入出力回路はビット線とデータバスとをトランジスタを介して間接的に接続するダイレクトセンス回路であり、該トランジスタを介してデータバスを所定の電位に接続することを特徴とする。この構成は、本発明の第7の実施の形態に相当するもので、ダイレクトセンス回路180に相当する。この場合には、上記トランジスタを介してデータバスを所定の電位(第7の実施の形態中のプリチャージ回路130のNSAの電位)に設定することで、データバスと上記所定の電位との電位差を無くすことができ、無駄な電流がデータバスから流れ込むことを防止できる。

【0021】

また、センスアンプがオフの時に、前記所定の電位はデータバスのリセット電位に等しいことを特徴とする。上記所定の電位をより具体的に規定したものである。

また、書き込み動作が可能は半導体記憶装置において、書き込みデータのうちマスクすべきデータが指示された場合、対応するメモリに接続するデータバス線をフローティング状態に設定することを特徴とする半導体記憶装置である。マスクする書き込みデータを、対応するデータバスをフローティング状態にすることで書き込みを阻止できるので、複数データを一括して同時に書き込む場合、その一部のデータのみをマスクすることが必要な場合でも対応することができる。

【0022】

【発明の実施の形態】

まず、図1を参照して、本発明の原理を説明する。

図1は、本発明の原理による読み出し動作を示すタイミング図である。前述した図29と対比すると判るように、本発明では半導体記憶装置外部から見ると、従来用いられていたビット線プリチャージのコマンドPREがない。換言すれば、本発明は従来のように、ビット線対をVCC/2にプリチャージしない。従って、コラムアドレスのコマンドCOLを受けた後、すぐに次の読み出しサイクルに入ることができる。次の読み出しサイクルに入った後でも、前の読み出しサイクルのデータがデータ線(図28のデータ線DB、/DB相当)に出力されている。これは、読み出し動作のアクセスサイクル(ROWを発行して次にCOLを発行するまでの時間)が、読み出し動作の1サイクルよりも短いことを意味し、前回の読み出し動作の完了前に次のセルの読み出し動作を開始することを意味している。

【0023】

また、本発明では、内部的に見ると、ビット線対をVCC/2にプリチャージしてリセットする代わりに、新たなビット線のリセット方法を提案する。これは、次回の読み出しサイクルにおいて、前回の読み出しサイクルで読み出し側となったビット線の電位をリセット状態(リセット電位)とし、他方のビット線の電位をこの電位に合わせる。このように、両方のビット線を、前回の読み出しサイクルで読み出し側となったビット線の電位に設定した状態をリセット状態とする。換言すれば、前回の読み出し情報に応じて、次回の読み出しのためのリセット電位の値が決まる。

【0024】

図1に示すタイミング図を参照して、読み出し動作を説明すると、ローアドレスのコマンドROWを受けてワード線WLが立ち上がる。この例では、2つのビット線BL、/BLはVSSレベルにリセットされている。これは、前回の読み出し動作の選択側ビット線に0が読み出されたことを意味する。ワード線WLが立ち上がると、ビット線BLと/BLの電位が図示するように変化し始める。図示する例では、ビット線BLが選択側で、ビット線/BLが非選択側である。選択側のビット線BLに接続されたセルにはデータ1が記憶されているので、ビット線BLの電位はVCCに向けて立ち上がる。この立ち上がり初期において、非選択側のビット線/BLもVSSより多少高い電位に立ち上がるが、ビット線BLの立ち上がり電位よりは低く設定されている。これは、後述するダミーセルの機能による。

【0025】

このようにして、ビット線BLと/BLとには電位差が生じるので、これをセンスアンプでセンスすれば、データの読み出しが可能である。なお、非選択側のビット線/BLはその後、センスアンプにより増幅されるためVSSに戻る。なお、VSSに戻ることは必須ではなく、ビット線BLの電位よりも低い電位にあればよい。

【0026】

このようにして生じた電位差をセンスアンプでセンスした後に、非選択側のビット線/BLの電位を選択側のビット線電位に合わせるように制御する。この例では、ビット線/BLの電位をVCCまで持ち上げる。ビット線BLと/BLがいずれもVCCとなったところで、ビット線BL、/BLのリセット動作は完了である。よって、いままで選択していたワード線WLを立ち下げると共に、次の読み出しサイクルのローアドレスのコマンドROWに応じて、選択されたワード線WL’を立ち上げる。

【0027】

図示する場合、選択側のビット線はビット線BLであり、データ0が選択されたメモリセルから読み出された(センスアンプでセンスされた)ことで、ビット線BLの電位はVSSに向かい下降する。このビット線BLの立ち下がり初期において、非選択側のビット線/BLはダミーセルの機能により選択側のビット線BLよりも高い電位にある。よって、この電位差をセンスアンプでセンスする。

【0028】

以上のような読み出し動作により、読み出し動作の1サイクルを60nsにすることができ、読み出し動作の高速化が可能になる。

なお、図28及び図29に示す従来技術の先行技術として、各読み出しサイクルにおいてビット線対をVCCレベルにリセットする方法が知られているが、この技術とは前回の読み出しサイクルで読み出されたデータがビット線リセット電位となる点で異なる。

【0029】

図2は、本発明の第1の実施の形態によるDRAM装置の要部の構成を示す回路図である。

図示する回路構成は、1対のビット線BL0、/BL0に関するものであり、同様の回路構成がその他のビット線対毎に設けられている。ビット線BL、/BL0に対し、セルアレイ部31、2つのセンスアンプ部301 、302 、及びダミーセル部42が設けられている。

【0030】

セルアレイ部31は、ビット線対BL0、/BL0に交互に接続された複数のセル(CELL)を有する(フォールディッドビット線構造)。各セルは、図3に示すように、1キャパシタ、1トランジスタ構成のセルMCである。各トランジスタのゲートにはワード線WL1、WL2・・・WLnが接続されている。

センスアンプ部301 は、セルアレイ部31内のビット線対BL0、/BL0の一方の側に設けられて、センスアンプ302 はダミーセル部42を介してビット線対BL0、/BL0の他方の側に設けられている。センスアンプ部301 は、センスアンプ341 、データ入出力回路361 、トランスファゲート回路391 及びビット線リセット回路441 を有し、これらはセンスアンプ部301 内の内部ビット線対BL01、/BL01に接続されている。

【0031】

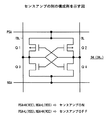

センスアンプ341 及びデータ入出力回路361 の構成を図4に示す。センスアンプ341 はトランジスタQ1〜Q4で構成されるフリップフロップと、更にトランジスタQ5、Q6を有する。なお、図中、矢印が付いたトランジスタ記号はPチャネルの電界効果トランジスタ(例えば、MOSトランジスタ)を示し、矢印が付いていないトランジスタ記号はNチャネルの電界効果トランジスタを示している。トランジスタQ5は、制御信号PSA1に従い選択的に電源電圧VCCをフリップフロップに接続する。同様に、トランジスタQ6は制御信号NSA1に従い選択的に電源電圧VSSをフリップフロップに接続する。データ入出力回路361 はトランジスタQ11とQ12とから構成され、コラム選択信号CL1に従い、内部ビット線BL01、/BL01をそれぞれデータ線DB1、/DB1に接続する。なお、PSA1=L(=VSS)、NSA1=H(=VCC)の場合に、センスアンプ341 はオンする。

【0032】

トランスファゲート回路391 はトランジスタQ50及びQ51を有し、トランスファ制御信号BT01、/BT01に従い選択的に内部ビット線BL01、/BL01をそれぞれ選択的にセルアレイ部31のビット線BL0、/BL0にそれぞれ接続する。

ビット線リセット回路441 はトランジスタQ52を有し、ビット線リセット信号BRST1がアクティブになると、内部ビット線BL01と/BL01とをショートとして、内部ビット線BL01と/BL01とをリセットする。

【0033】

センスアンプ部302 は、センスアンプ部301 と同一構成である。すなわち、センスアンプ部302 はセンスアンプ342 、データ入出力回路362 、トランスファゲート回路392 及びビット線リセット回路442 を有し、これらはセンスアンプ部302 内の内部ビット線対BL02、/BL02に接続されている。センスアンプ342 及びデータ入出力回路362 の構成は、図4に示すものと同一構成である。各部を示す記号に添えられている数字を読み替えば、センスアンプ部302 の構成となる(BL01→BL02、/BL01→/BL02、DB1→DB2、/DB1→/DB2、CL1→CL2、PSA1→PSA2、NSA1→NSA2)。

【0034】

トランスファゲート回路392 はトランジスタQ53及びQ54を有し、トランスファ制御信号BT02、/BT02に従い内部ビット線BL02、/BL02をそれぞれ選択的にセルアレイ部31のビット線BL0、/BL0にそれぞれ接続する。

ビット線リセット回路442 はトランジスタQ55を有し、ビット線リセット信号BRST2がアクティブになると、内部ビット線BL02と/BL02とをショートとして、内部ビット線BL02と/BL02とをリセットする。

【0035】

ダミーセル部42は、図5に示す2つのダミーセルトランジスタQ14、Q15、キャパシタC及びキャパシタCに選択的にVCC/2を与えるトランジスタQ16とを有する。トランジスタQ14はビット線BL0とキャパシタCとの間に設けられ、ダミーセル制御信号CNT1でオン/オフする。トランジスタQ15はビット線/BL0とキャパシタCとの間に設けられ、ダミーセル制御信号CNT2でオン/オフする。トランジスタQ16はVCC/2に接続され、選択的にキャパシタCを充電する。

【0036】

センスアンプ部31のビット線BL0に接続されるセルからデータを読み出す場合には、他方のビット線/BL0に接続されたダミーセル部42のトランジスタQ15がオンするようにダミーセル制御信号CNT2が与えられる。また、ビット線/BL0に接続されるセルからデータを読み出す場合には、他方のビット線BL0に接続されたダミーセル部42のトランジスタQ14がオンするようにダミーセル制御信号CNT1が与えられる。

【0037】

次に、図2に示す半導体記憶装置の動作について、図6を参照して説明する。以下に詳述するように、読み出し動作において、センスアンプ301 と302 は交互に動作させる。すなわち、読み出したデータをデータ線対DB1、/DB1とデータ線対DB2、/DB2から交互に出力させる。センスアンプ部301 からデータを読み出して出力している間は、センスアンプ部302 でビット線対のリセットを行う。

【0038】

センスアンプ部301 の動作によりデータを読み出すためのローアドレスのコマンドROW1が入る直前の状態は、センスアンプ部301 がオフで、センスアンプ部302 がオンである。センスアンプ部301 、302 のオン/オフ(より詳細には、センスアンプ341 、342 のオン/オフ)は制御信号PSA1、NSA1、PSA2、NSA2で行う。この時、センスアンプ部301 の内部ビット線対BL01、/BL01はリセット(図示する例では、VSSに設定されたリセット状態)されており、トランジスタQ50、Q51、Q52がオンしている。センスアンプ部302 はオンでデータの読み出しを行っており、選択側のビット線(仮にBL0側)のトランジスタQ53がオン、トランジスタQ54、Q55はオフである。

【0039】

コマンドROW1が外部から半導体記憶装置に入力されると、制御信号PSA1、NSA1、PSA2、NSA2により、センスアンプ部301 がオンし、センスアンプ部302 がオフする。上記コマンドROW1は、図示を省略するデコーダでデコードすることでワード線(図6の例では図2に示すワード線WL1)が選択され、ワード線WL1の電位がVCCに向け立ち上がる。一方、ビット線リセット信号BRST1が立ち下がり、トランジスタQ52がオフすることで内部ビット線BL01、/BL01のリセットは解除され、センスアンプ341 がセルからデータを読み出せる状態になる。他方、センスアンプ部302 のトランジスタQ53は、トランスファ制御信号BT02がローレベルになることでオフし、センスアンプ342 はセルアレイ部31のビット線BL0と切り離される。

【0040】

ワード線WL1が立ち上がると、ビット線BL0、/BL0に電位差が生じる。例えば、選択されたワード線WL1に接続されているセルに1のデータが記憶されているとする。このセルに蓄積された電荷がビット線BL0に流れ出ることで、ビット線BL0の電位は上昇する。他方、内部ビット線/BL0の電位は図5に示すダミーセル回路42のトランジスタQ15がオンするように制御信号CNT2で制御されるので、キャパシタCに蓄積された電荷がVSSレベルにあるビット線/BL0に流れ出る。選択されたセルの電荷はVCCで蓄積されているのに対し、トランジスタQ15の電荷はVCC/2で蓄積されているため、ビット線/BL0の上昇する電位はビット線BL0の電位よりも低い。よって、ビット線BL0、/BL0に電位差が生じる。

【0041】

上記電位差は内部ビット線対BL01、/BL01に伝えられ、センスアンプ341 はこの電位差をセンスする。センスしたタイミングでトランスファ制御信号/BT01を立ち下げ、非選択側のトランジスタQ51をオフさせる。センスアンプ341 がデータをセンスした時点で、コラムアドレスのコマンドCOL1をデコードすることでコラム制御信号CL1を立ち上げ、センスしたデータをデータ線DB1、/DB1に出力する。

【0042】

他方、センスアンプ部302 では、上記のようにトランジスタQ53がオフになって、ビット線BL0が内部ビット線BL02から切り離される。これにより、内部ビット線対BL02、/BL02はフローティング状態になる。センスアンプ部301 のトランジスタQ51がオフになったら、セルアレイ部31のビット線BL0、/BL0のリセット動作を開始する。すなわち、トランジスタQ53、Q54、Q55がオンし、非選択側ビット線/BL0はセンスアンプ341 により、センスアンプ341 、トランジスタQ50、ビット線BL0、トランジスタQ53、Q55、トランジスタQ54、ビット線/BL0の経路でリセットが行われ、選択側のビット線BL0の電位、すなわちこの例ではVCCの電位にリセットされる。このようにして、読み出しデータをセンスした後に、非選択側のビット線の電位を選択側のビット線の電位にリセットすることで、次の読み出し動作に備える。

【0043】

次の読み出しでは、ローアドレスのコマンドROW2により図2に示すワード線WL2が選択される。これを受けて、センスアンプ部301 はオフし、センスアンプ部302 はオンする。また、コラム選択信号CL1が立ち下がることでセンスアンプ部301 のデータ入出力回路361 はオフし、トランスファ制御信号BT01が立ち下がることでトランジスタQ50がオフし、前回の読み出し動作で選択側であったビット線BL0を切り離す。図示する場合は、選択側のビット線/BL0に0のデータが記憶されている。この場合、図5に示すダミーセル部42の非選択側トランジスタQ14がオンする。ワード線WL2に接続されたセルMCのデータは0なので、ビット線/BL0からセルのキャパシタに電荷が流れ込み、ビット線/BL0の電位は下がる。他方、トランジスタQ14がオンするので、電荷がVCCにあるビット線BL0からキャパシタCに流れ込む。この場合、CはVCC/2で充電されているので、ビット線BL0の電位は、ビット線/BL0の電位よりは下がらない。

【0044】

このようにして生成されたビット線BL0と/BL0の電位差は内部ビット線BL02、/BL02に伝えられ、センスアンプ342 でセンスされる。センス後、非選択側の内部ビット線BL02に接続されているトランジスタQ53をオフし、またデータ入出力回路342 をオンしてセンスしたデータをデータ線DB2、/DB2に出力する。

【0045】

他方、センスアンプ部301 では、内部ビット線対BL01、/BL01はフローティング状態になる。センスアンプ部302 のトランジスタQ53がオフになったら、セルアレイ部31のビット線BL0、/BL0のリセット動作を開始する。すなわち、トランジスタQ50、Q51、Q52がオンし、非選択側ビット線BL0はセンスアンプ342 により、センスアンプ342 、トランジスタQ54、ビット線/BL0、トランジスタQ51、トランジスタQ52、トランジスタQ50、ビット線BL0の経路でリセットが行われ、選択側のビット線/BL0の電位、すなわちこの例ではVSSの電位にリセットされる。このようにして、読み出しデータをセンスした後に、非選択側のビット線の電位を選択側のビット線の電位にリセットすることで、次の読み出し動作に備える。

【0046】

上記読み出し動作においては、従来のようなビット線プリチャージのためのコマンドPREがなく、前の読み出しサイクルのコマンドCOLの次に、次の読み出しサイクルのコマンドROWを持ってこれるので、高速動作が可能になる。

図7は、本発明の第2の実施の形態によるDRAM装置の要部の構成を示す回路図である。第2の実施の形態は、1つのセンスアンプ部を2つのセルアレイ部に共通に設けたことを特徴とする。なお、前述した第1の実施の形態による半導体記憶装置の構成要素と同一のものには、同一の参照番号を付けてある。

【0047】

図示する回路構成は、1対のビット線BL0、/BL0に関するものであり、同様の回路構成がその他のビット線対毎に設けられている。ビット線BL、/BL0に対し、1つのセンスアンプ部30と2つのセルアレイ部32、33が設けられている。センスアンプ部30はセルアレイ部32と33とに共通に設けられている。センスアンプ部30は、センスアンプ34、データ入出力回路36、トランスファーゲート回路38及び40を有する。

【0048】

センスアンプ34は、フリップフロップを実現するトランジスタQ1〜Q4と、更にトランジスタQ5、Q6を有する。トランジスタQ5は、制御信号PSAに従い選択的に電源電圧VCCをフリップフロップに接続する。同様に、トランジスタQ6は制御信号NSAに従い選択的に電源電圧VSSをフリップフロップに接続する。

【0049】

データ入出力回路36はトランジスタQ11とQ12とから構成され、コラム選択信号CLに従い、ビット線BL0、/BL0をそれぞれデータ線DB、/DBに接続する。

トランスファゲート回路38はトランジスタQ7及びQ8を有し、トランスファ制御信号BT0、/BT0に従い選択的にビット線BL0、/BL0をそれぞれ選択的にセンスアンプ部30に接続することで、選択的にセルアレイ部32をセンスアンプ部30に接続する。トランスファゲート回路40はトランジスタQ9、Q10を有し、トランスファ制御信号BT1、/BT1に従い選択的にビット線BL0、/BL1をセンスアンプ部30に接続することで、選択的にセルアレイ部33をセンスアンプ部30に接続する。なお、トランスファゲート回路38、40のいずれか一方のゲートが開いている時は、他方のゲートは閉じている。

【0050】

セルアレイ部32は、複数のセル(図7ではMC1とMC2の2つのみ図示してある)と、ダミーセル部42と、ビット線リセット回路44とを具備している。各セルは、1キャパシタ、1トランジスタ構成である。

ビット線リセット回路44はトランジスタQ13を有し、ビット線リセット信号BRSTがアクティブになると、ビット線BL0と/BL0とをショートとして、ビット線BL0と/BL0とをリセットする。

【0051】

次に、図7の半導体記憶装置の動作について、図8を参照して説明する。

ビット線BL0、/BL0がVSSにリセットされている状態で、ローアドレスのコマンドROWが外部から半導体記憶装置に与えられると、これを図示を省略するデコーダでデコードすることでワード線WLが選択される。今、選択されたワード線は図7のワード線WL1であるとする。ワード線選択と同時にセルアレイ部32をセンスアンプ部30に接続するために、トランスファ制御信号BT0、/BT0がアクティブにされる。

【0052】

今、選択されたワード線WL1に接続されたセルMC1がデータ1を保持している場合、セルMC1に蓄積された電荷がビット線BL0に流れ出ることで、ビット線BL0の電位は上昇する。他方、ビット線/BL0の電位はダミーセル部42のトランジスタQ15がオンするので、キャパシタCに蓄積された電荷がVSSレベルにあるビット線/BL0に流れ出る。セルMC1の電荷はVCCで蓄積されているのに対し、トランジスタQ15の電荷はVCC/2で蓄積されているため、ビット線/BL0の電位はビット線BL0の電位よりも低い。

【0053】

このようにして形成されたビット線BL0と/BL0との電位差を、センスアンプ34がセンスする。これにより、ビット線BL0の電位はVCCに向け急上昇し、ビット線/BL0の電位はVSSに向かう。センスアンプ34でセルMC1のデータをセンスしたので、ダミーセルの情報を読み出しているビット線/BL0をセンスアンプ34から切り離すために、トランスファ制御信号/BT0を立ち下げる(オフ)。セルMC1の情報を読み出しているビット線BL0はセンスアンプ34に接続したままにしておく。

【0054】

一方、センスしたデータをデータ線DB、/DBに出力させるために、コラムアドレスのコマンドCOLをデコードすることで、コラム選択信号CLをアクティブにする。これにより、センスアンプ34にラッチされたセルMC1のデータは、データ線DB、/DBに出力される。

次に、ビット線リセット信号BRSTをアクティブにして、ビット線BL0、/BL0をリセットする動作を開始させる。前述したように、ビット線BL0、/BL0のリセットは、非選択側のビット線/BL0を選択側のビット線BL0の電位に合わせることである。選択側のビット線BL0はセンスアンプ34を介して電源VCCに接続されているため、ビット線/BL0の電位はVCCに向かい上昇する。ビット線BL0と/BL0の電位(次回の読み出し動作のリセット電位)になったところで、ビット線リセット信号BRSTを立ち下げる(オフ)。また、ビット線リセット信号BRSTの立ち下げと同時にトランスファ制御信号BT0を立ち下げ、センスアンプ34と選択側ビット線BL0を切り離す。ただし、図4の例では、引き続きワード線WL2が選択されセルアレイ32が選択されるため、トランスファ制御信号BT0は立ち下がらずに引き続き選択される。

【0055】

なお、センスアンプ34がデータをセンスした後に、図5に示す制御信号CONT3でトランジスタQ16をオンにして、キャパシタCをVCC/2で充電する。

このようにして、ビット線BL0、/BL0はリセット状態に設定され、次の読み出し動作が可能になる。次に選択されるワード線が図7のWL2であり、セルMC2に蓄積されているデータが0であるとする。この場合には、図5のトランジスタQ14が選択される。セルMC2のデータは0なので、ビット線/BL0からセルMC2のキャパシタに電荷が流れ込み、ビット線/BL0の電位は下がる。他方、トランジスタQ14がオンするので、電荷がVCCにあるビット線BL0からキャパシタCに流れ込む。この場合、CはVCC/2で充電されているので、ビット線BL0の電位は、ビット線/BL0の電位よりは下がらない。このようにして生成されたビット線BL0と/BL0の電位差をセンスアンプ34でセンスする。読み出した後、非選択側のビット線BL0の電位を選択側のビット線BL0の電位VSSに一致させることで、ビット線BL0と/BL0はリセットされ、次の読み出し動作に備える。

【0056】

上記読み出し動作においては、従来のようなビット線プリチャージのためのコマンドPREがなく、前の読み出しサイクルのコマンドCOLの次に、次の読み出しサイクルのコマンドROWを持ってこれるので、高速動作が可能になる。

なお、上記の構成ではセンスアンプ34のリセット(プリチャージ)の構成は省略してある。

【0057】

次に、本発明の第3の実施の形態について説明する。

図9は、本発明の第3の実施の形態による半導体記憶装置の要部を示すブロック図である。なお、前述した第1及び第2の実施の形態による半導体記憶装置の構成要素と同一のものには、同一の参照番号を付けてある。

第3の実施の形態は、ダミーセル回路42をセンスアンプ部300内に設け、読み出し動作をより高速に行えるようにしたことを特徴とする。このために、センスアンプ部300のフリップフロップ回路34は、センスアンプ部300内の内部ビット線対BL、/BLをセンスする構成である。センスする際には、セルアレイ部320と330はセンスアンプ部300から切り離されるので、センス動作速度は内部ビット線BL、/BLの負荷に依存する。図7に示す構成では、図9の内部ビット線BL、/BLよりも長いビット線BL0、/BL0の負荷に依存するので、センス動作速度は図9の構成に比べ遅い。この結果、センス動作で消費する電力も軽減することができる。

【0058】

センスアンプ部300を上記の通り構成したので、センスアンプ部300に接続されるセルアレイ部320、330も図7に示す構成とは異なる。具体的には、セルアレイ部320はビット線BL0のみを有し、セルアレイ部330はビット線/BL0のみを有する。すなわち、センスアンプ300に対して、いずれか一方のビット線BL0又は/BL0が駆動される。

【0059】

センスアンプ部300は、フリップフロップ回路34及びデータ入出力回路36に加え、トランスファゲート回路38A、40A、ダミーセル回路42及びビット線リセット回路44Aを有する。トランスファゲート回路38AはトランジスタQ7を有し、トランスファゲート40AはトランジスタQ10を有する。ダミーセル部42は図5に示す構成であるが、センスアンプ部300内の内部ビット線BL、/BLに接続されている点で図7に示す構成とは異なる。また、ビット線リセット回路44Aは、センスアンプ部300内の内部ビット線BL、/BLをリセットする。

【0060】

図10は、図9の回路構成の動作を示すタイミング図である。

今、ビット線BL、/BLがVSSにリセットされている状態で、ローアドレスのコマンドROWが外部から半導体記憶装置に与えられると、これを図示を省略するデコーダでデコードすることでワード線WLが選択される。今、選択されたワード線は図9のワード線WL1であるとする。ワード線選択と同時にセルアレイ部320をセンスアンプ部30に接続するために、トランスファ制御信号BT0がアクティブにされる。

【0061】

今、選択されたワード線WL1に接続されたセルMC1がデータ1を保持している場合、セルMC1に蓄積された電荷がビット線BL0に流れ出ることで、ビット線BL0の電位は上昇する。よって、センスアンプ部300内の内部ビット線BLの電位も上昇する。他方、ビット線/BLの電位はダミーセル部42のトランジスタQ15がオンするので、キャパシタCに蓄積された電荷がVSSレベルにある内部ビット線/BLに流れ出る。セルMC1の電荷はVCCで蓄積されているのに対し、トランジスタQ15の電荷はVCC/2で蓄積されているため、内部ビット線/BLの電位は内部ビット線BLの電位よりも低い。

【0062】

このようにして形成された内部ビット線BL0と/BL0との電位差を、フリップフロップ回路34がセンスする。この時、セルアレイ部320は、トランジスタQ7をオフさせて、センスアンプ部300から切り離された状態にしておく。これにより、内部ビット線BLの電位はVCCに向け急上昇し、内部ビット線/BLの電位はVCCに向かう。

【0063】

一方、センスしたデータをデータ線DB、/DBに出力させるために、コラムアドレスのコマンドCOLをデコードすることで、コラム選択信号CLをアクティブにする。これにより、フリップフロップ回路34にラッチされたセルMC1のデータは、データ線DB、/DBに出力される。

次に、ビット線リセット信号BRSTをアクティブにして、内部ビット線BL、/BLをリセットする動作を開始させる。内部ビット線BL0、/BL0のリセットは、非選択側の内部ビット線/BL0を選択側の内部ビット線BL0の電位に合わせることである。よって、この場合はビット線/BL0の電位がVCCに向かい上昇する。内部ビット線BL0と/BL0の電位がVCC(次回の読み出し動作のリセット電位)になったところで、ビット線リセット信号BRSTを立ち下げる(オフ)。

【0064】

なお、センスアンプ34がデータをセンスした後に、図5に示す制御信号CONT3でトランジスタQ16をオンにして、キャパシタCをVCC/2で充電する。

ビット線BL、/BLがリセットされていれば直ちに次の読み出し動作を実行することができる。よって、外部からの読み出しに関するコマンドを図10に示すように配列することができる。センス動作をより高速にできるので、コマンドも詰めて配列することができる。

【0065】

なお、図9ではセンスアンプ部300の両方向にビット線が延びている構成であったが、一方向に延びる構成であってもよい。

また、上記の構成ではセンスアンプ34のリセット(プリチャージ)の構成は省略してある。

また、第1ないし第3の実施の形態で用いられているセンスアンプ341 及び342 は6個のトランジスタから成るが、図11に示すように、2つのPチャネルトランジスタ及び2つのNチャネルトランジスタの計4個のトランジスタで構成しても良い。図11の構成では、制御信号PSA及びNSAがそれぞれハイレベル及びローレベルにあると、センスアンプはオンする。従って、図11の構成では、6個のトランジスタで構成されるセンスアンプの動作とは逆になる。

【0066】

次に、本発明の第4の実施の形態を説明する。

前述した第1の実施の形態では、ビット線BL0、/BL0の両側にそれぞれ設けられた2つのセンスアンプ341 及び342 を用い、一方のセンスアンプでデータを読み出ている間は、他方のセンスアンプでビット線対BL0、/BL0のプリチャージ(リセット)を行うとともに、データの読み出し後に前記一方のセンスアンプ内のビット線(ノード)をリセットして(フローティング状態)、ラッチ状態を解除する構成である。

【0067】

この構成を用いて実際の半導体記憶装置を構成した場合、図12(A)に示すように、センスアンプS/A1、S/A2を一対のビット線の両側に配置することは可能であるが、図12(B)に示すリラックス方式のレイアウトを実現するのは極めて困難である。リラックス方式は複数のビット線対がセンスアンプS/A1、S/A2を共用する構成である。従って、図12(B)のセンスアンプの配列を可能とする構成が必要となる。

【0068】

本発明の第4の実施の形態は、ビット線とセンスアンプ(この中のビット線)とをプリチャージする手段を設け、図12(B)に示すようなレイアウトを可能にするものである。また、この手段を前述の第2及び第3の実施の態様に適用して、センスアンプ内のビット線をリセットするために用いることもできる。

図13は、本発明の第4の実施の形態を示す回路図である。図13の構成は、一対のビット線に関するもので、複数のメモリセル、前述したダミーセル回路42、4トランジスタ構成のセンスアンプ110、プリチャージ制御回路120、プリチャージ回路130、及びデータ入出力回路140を具備する。プリチャージ回路130は、センスアンプ110側のビット線対BLX(BL)、BLZ(BL)及びビット線BLX(LA)、BLZ(LA)を同時にプリチャージする。プリチャージ回路130はセンスアンプ110と同一回路構成なので、データをラッチする機能も有する。プリチャージ制御回路120は、1つのNチャネルMOSトランジスタからなるビット線リセット回路121と、2つのNチャネルMOSトランジスタからなるトランスファゲート122とを具備し、ビット線対BLX(BL)、BLZ(BL)及びビット線BLX(LA)、BLZ(LA)のプリチャージを制御する。

【0069】

次に図13の動作を図14を参照して説明する。以下では、図中のアルファベットA〜Fで示した区間ごとにその動作を説明する。

区間A

まず始めに、ビット線BLX(BL)、BLZ(BL)がハイレベルHにプリチャージされている状態で、ワード線WL1が立ち上がると、ワード線WL1に接続されているメモリセルからデータが出てくる。この例の場合では、”L”が出てきたと仮定する。これと同時に、ダミーセル42からもデータが出てくる。前述したように、ダミーセル42には電源電圧VCCの半分の電荷が蓄積されている。よって選択されたメモリセルに接続するビット線BLX(BL)は、ダミーセル42に接続するビット線BLZ(BL)よりも立ち下がりが速い。センスアンプ110は、制御信号NSA1、PSA1が反転してオンし、ビット線BLX(BL)とBLZ(BL)との僅かな電位差を増幅する。

区間B

次に、プリチャージ制御回路120はセンスアンプ110が増幅したデータをプリチャージ回路130へ転送する。センスアンプ110のラッチ後、トランスファ制御信号BT0、/BT0が立ち上がり、トランスファーゲート122の2つのトランジスタが両方オンし、ラッチされたデータがプリチャージ回路130へ転送される。

区間C

制御信号PSA、NSAが反転し、プリチャージ回路130がオンする。この時、制御信号PSA1、NSA1が反転し、センスアンプ110をオフにする。これは、次にセンスアンプ110とビット線のプリチャージが行われるのであるが、その時にセンスアンプ110を前もってオフの状態にしておかないとプリチャージできないからである。

区間D

センスアンプ110のプリチャージ(すなわち、ビット線対BLX(BL)、BLZ(BL)のプリチャージ)と、ビット線対BLX(LA)、BLZ(LA)のプリチャージが行われる。区間Dでは、まず、区間Bで同時に立ち上げたトランスファ制御信号BT0、/BT0のうち、選択されたメモリセル(この場合はワード線WL1に接続されているメモリセル)につながるビット線、すなわち非選択側のビット線(この場合、ビット線BLZ(BL))をプリチャージ回路130から切り離すために、トランスファ制御信号BT0を立ち下げる。そして、ビット線リセット信号BRSTを立ち上げ、ビット線ショート回路121のトランジスタをオンし、ビット線BLX(BL)とBLZ(BL)とをショートし、非選択側のビット線BLZ(BL)をローレベルにプリチャージする。すなわち、プリチャージ回路130のビット線BLX(LA)はローレベルにあり、センスアンプ110のビット線BLZ(BL)はハイレベルにある。よって、ビット線BLZ(BL)の電荷がビット線ショート回路121、/BT0側トランジスタ、ビット線BLX(LA)、及びNチャネルMOSトランジスタを通して、NSAに流れ込む。

【0070】

なお、区間Dでコラム選択信号CLを立ち上げる(オン)することで、読み出したデータをデータバスDBX、DBZに出力することができる。

区間E

この状態では、センスアンプ110のビット線対BLZ(BL)、BLX(BL)のプリチャージは完了している。またプリチャージ回路130は、ビット線BLX(LA)がローレベル、ビット線BLZ(LA)がハイレベルになっており、読み出したデータをラッチしていることになる。そして、トランスファ制御信号/BT0を立ち下げ、ビット線リセット信号BRSTを立ち下げる。

区間F

そして、制御信号PSA、NSAを反転させ、プリチャージ回路130をオフにする。これにより、次の新しいデータをラッチする際のタイミングマージンに余裕ができる。

【0071】

以上説明したように、プリチャージ回路130でセンスアンプ110から延びるビット線対BLZ(BL)、BLX(BL)をプリチャージできるので、図2に示す構成よりも回路が簡単化できる。図13に示す回路構成を用いて、図12(B)に示す配置を実現することができる。

図15は、図13に示す回路構成を用いて実現したリラックス方式の半導体記憶装置を示す回路図である。以下、図15の構成を本発明の第5の実施の態様として説明する。図15中、図13に示す構成要素と同一部分には同一の参照番号を付けてある。図15に示す回路の特徴は、左センスアンプ110と右センスアンプ140に共通に1つのプリチャージ回路130を設け、プリチャージ回路130で両方のセンスアンプをプリチャージする。なお、以下の説明では、プリチャージ回路130に対し、左と右の構成要素を区別するために、図13に示す参照番号うち信号、ビット線、ワード線を表すものにはL(左)、R(右)を付ける。例えば左側(図15では便宜上、上側)に配置されたワード線はWLL1、WLL2であり、右側(図15では便宜上、下側)に配置されたワード線はWLR1、WLR2である。

【0072】

図15の上側の回路構成は図13に示す回路構成と同じである。また、図15の下側の回路構成は、セルアレイ、ダミーセル142、右センスアンプ140及び右プリチャージ制御回路150を有する。右センスアンプ140は左センスアンプ110と同一構成である。また、右プリチャージ制御回路150は左プリチャージ制御回路120と同一構成で、ビット線ショート回路151及びトランスファゲート152を有する。なお、データバス線DBX、DBZ及びデータ入出力回路140は同一である。

【0073】

次に、図16及び図17を参照して、図15に示す構成の動作を説明する。図16は、プリチャージ回路130に対し左側に位置する左側回路の動作タイミング図、図17は右側に位置する右側回路の動作タイミング図である。図16及び図17に、図14に示す区間A〜区間Fに対応する区間A〜区間Fを示す。

まず、図16において、ワード線WLL1に接続されるセルが選択されたとする。この場合の左側回路の動作は、図14を参照して説明した回路動作と同様である。すなわち、図16の区間A〜区間Fのそれぞれの各部の動作は、図14の区間A〜区間Fの対応する部分の動作と同じである。従って、ここでの左側回路の動作説明は省略する。

【0074】

右側回路中の右プリチャージ制御回路150は、左プリチャージ制御回路120と異なる動作をする。図17において、スタンバイ状態(0(ns)時)では、右センスアンプ140は左センスアンプ110とは反対のプリチャージレベルにある。すなわち、右センスアンプ140内のビット線BLRX(BL)、BLRZ(BL)ともローレベルにある。左側回路のメモリセルが選択されて左側回路がセンス動作をしている時(図16の区間C)は、右プリチャージ制御回路150のトランスファ制御信号BTR0、/BTR0はいずれもローレベルにある。従って、右センスアンプ140はプリチャージ回路130から切り離された状態、すなわちフローティング状態にある。左側回路のセンス動作が終了し、プリチャージ動作に入った時(図16の区間D)、右側回路も同時にプリチャージ動作に入る(図17の区間D)。このプリチャージ動作において、プリチャージ回路130の負荷を増やさないように、左側がVSS方向のプリチャージ動作を行っているならば、右側はVCC方向のプリチャージ動作を行う。すなわち、図16では区間Dでトランスファ制御信号/BTL0がオンであり、プリチャージ回路130は、左センスアンプ110のビット線BLLZ(BL)電位をビット線BLX(LA)の電位VSSにプリチャージするように動作する。よって、図17の区間では、トランスファ制御信号BTR0がビット線リセット信号BRSTRと同時にオンし、プリチャージ回路130は、右センスアンプ140のビット線BLRX(BL)、BLRZ(BL)をBLZ(LA)の電位VCCにプリチャージするように動作する。この結果、非活性時(オフ)にビット線がフローティング状態になることはない。

【0075】

以上の通り、図15の回路構成で図12(B)に示す配列を実現でき、しかもプリチャージ回路は右側回路と左側回路とで共用できるので、レイアウト面積上からも利点がある。

次に、図18を参照して、本発明の第6の実施の態様を説明する。なお、図18において、前述した図に示される構成要素と同一のものには同一の参照番号を付けてある。本発明の第6の実施の態様は、図13に示す本発明の第4の実施の態様による回路構成に対し、貫通電流阻止ゲート160を設けたものである。この貫通電流阻止ゲート160は、図15に示す回路構成にも適用できる。

【0076】

図13において、メモリセルアレイが非活性状態(いずれも選択されていない:以下、この状態にあるメモリセルアレイを非活性アレイという)でプリチャージ回路130がラッチ状態にある時にコラム選択信号CLがオンした場合、プリチャージ回路130にラッチされたデータとデータバス線DBX,DBZのプリチャージレベルとが異なる時には、データバスDBX又はDBZからデータ入出力回路140を介して、プリチャージ回路130のPSA又はNSAに貫通電流が流れてしまう。通常、上記貫通電流は、図15に示すような複数のセンスアンプがデータバスを共用している場合に流れる。図15では、例えば左側回路のメモリセルアレイが非活性状態で右側回路のメモリセルアレイが活性状態(ワード線が立ち上がり、メモリセルが選択される:以下、この状態にあるメモリセルアレイを活性アレイという)にある場合、データのデータバスDBX,DBZに出力するためにコラム選択信号CLを立ち上げると、上記の貫通電流が流れてしまう。

【0077】

貫通電流阻止ゲート160は、2つのNチャネルMOSトランジスタからなる。この2つのトランジスタのゲートには、制御信号CLDが与えられる。ワード線が選択されセンスアンプが動作する場合には、貫通電流阻止ゲート160は開いていなければならない。そのため、ゲート制御信号CLDはコラム選択信号CLがオンする前又は同時にオンしていなければならない。本実施の形態の場合では、ゲート制御信号CLDを制御信号PSA、NSAに同期させ、コラム選択信号CLがオンする前にゲート制御信号CLDをオンする構成としている。

【0078】

図19は、図18の構成の活性アレイ動作を示すタイミング図である。制御信号PSA、NSAが反転してプリチャージ回路130がオンする時に、ゲート制御信号CLDがオンして貫通電流阻止ゲート160のゲートが開く。その後、コラム選択信号CLがオンして、プリチャージ回路130にラッチされたデータがデータバス線DBX、DBZに転送される。

【0079】

図20は、図18の構成の非活性アレイ動作を示す図である。メモリセルが選択されない場合には、ゲート制御信号CLDはローレベル(オフ)のままである。従って、その後、コラム選択信号CLがオンしてもデータバス線DBX、DBZとプリチャージ回路130とは切り離されており、貫通電流が流れることはない。

【0080】

データ入出力回路140は、図18に示す2トランジスタ構成以外の構成を具備した回路であっても良い。図21は、ダイレクトセンス回路180を具備した構成である。なお、図21において、前述した構成要素と同一のものには同一の参照番号を付けている。以下、図21に示す構成を本発明の第7の実施の形態として説明する。なお、以下の説明では、データバス線DBX、DBZはVCCレベルにプリチャージされるものとする。

【0081】

ダイレクトセンス回路180は、トランジスタQ21〜Q28を具備する。ビット線BLZ(LA)、BLX(LA)をそれぞれトランジスタQ25、Q26のゲートで受け、これらのドレインをデータバス線DBX、DBZに接続してある。メモリセルから読み出され、プリチャージ回路130でラッチされたデータがトランジスタQ25、Q26のオン/オフを制御することで、データバス線DBX、DBZに転送される。データの書き込み時、書き込み時コラム選択信号WCLEがオンしてトランジスタQ23、Q24がオンする。データバス線DBX、DBZ上の書き込みデータはトランジスタQ21〜Q24を通りプリチャージ回路130に与えられる。

【0082】

ここで、メモリセルが非選択の場合、プリチャージ回路130の制御信号NSAはハイレベルに設定される。この点に着目し、トランジスタQ27、Q28のソースをプリチャージ回路130の制御信号NSAのノードに接続してある。従って、たとえコラム選択信号CLがオンしてトランジスタQ25、Q26がオンしても、データバス線DBX、DBZからプリチャージ回路130のNSAのノードに貫通電流が流れることはない。

【0083】

図22は、図21の構成の活性アレイ動作を示すタイミング図である。この場合、プリチャージ回路130の制御信号NSA、PSAをそれぞれローレベル、ハイレベルに設定する。そして、コラム選択信号CLをオンする。図22の場合、ビット線BLZ(LA)がハイレベルにあるのでトランジスタQ25がオンし、データバス線DBXからプリチャージ回路130のNSAのノードに電流が流れ、データバス線DBXの電位はVCCから下降する。一方、ビット線BLX(LA)はローレベルなのでトランジスタQ26はオフしている。よって、データバス線DBZの電位はハイレベルのままである。

【0084】

図23は、図21の構成の非活性アレイ動作を示すタイミング図である。この場合、プリチャージ回路130の制御信号NSA、PSAはそれぞれハイレベル、ローレベルにある。また、トランジスタQ25はオンし、トランジスタQ26はオフしている。よって、コラム選択信号CLが立ち上がりトランジスタQ27、Q28がオンしてもデータバス線DBX、DBZとプリチャージ回路130のNSAのノードは同一レベル(ハイレベル)にあるので、貫通電流が流れることはない。

【0085】

なお、図21に示す回路構成では、トランジスタQ27、Q28のソースをプリチャージ回路130のNSAのノードに直結していたが、NSAと同様に変化する別の回路に接続することとしても良い。

また、図21〜図23では、データバス線DBX、DBZはVCCにプリチャージされる場合であったが、VSSレベルにプリチャージされる場合には、トランジスタQ27、Q28のソースをPSAのノードに接続すれば良い。更に、データバス線DBX、DBZがVCC/2の場合には、トランジスタQ27、Q28のソースを、活性アレイ動作時0V、非活性動作時VCC/2に変化するノード(回路)に接続すれば良い。

【0086】

図24は、上記第1ないし第7の実施の形態が適用可能な半導体記憶装置の一例であるシンクロナスDRAM(SDRAM)の構成を示すブロック図である。図24に示すSDRAMは、クロックバッファ200、コマンドデコーダ210、アドレスバッファ/レジスタ220、I/Oデータバッファ/レジスタ230、メモリセルアレイ240、ローデコーダ250、センスアンプ部260、及びコラムデコーダ270を有する。クロックバッファ200は外部からクロック信号CLKやクロックイネーブル信号CKEを受け取り、内部回路に必要な内部クロック信号を生成して、コマンドデコーダ210、アドレスバッファ/レジスタ220、I/Oデータバッファ/レジスタ230等に出力する。コマンドデコーダ210は、外部からチップセレクト信号/CS、ローアドレスストローブ信号/RAS、コラムアドレスストローブ信号/CAS、ライトイネーブル信号/WEを受け取り、これらの信号をデコードして内部回路が必要とする種々の信号、例えば前述したビット線リセット信号BRST、トランスファ制御信号BT、制御信号NSA、PSA等を生成する。その他、図24には図示を省略するが、前述の制御信号CNT、ゲート制御信号CLD等もコマンドデコーダ210で生成される。アドレスバッファ/レジスタ220は、外部からのアドレス信号A0〜Amをデコードし、ローアドレス及びコラムアドレスを生成する。I/Oデータバッファ/レジスタ230はデータバスDB、/DB(前述のDBX、DBZにも相当する)に接続し、外部からの書き込みデータを一時記憶し、外部への読み出しデータを一時記憶する。メモリセルアレイ240は、多数のメモリセル、ワード線、ビット線を含む回路である。ローデコーダ250は、ローアドレスをデコードしてワード線を駆動する信号(前述のWL1等)を生成する。コラムデコーダ270は、コラムアドレスをデコードして前述のコラム選択信号CL等を生成する。センスアンプ部260は、メモリセルアレイとデータバスDB、/DBとの間の全ての回路部分を含むものであり、例えば図13の構成ではセンスアンプ110、プリチャージ制御回路120、プリチャージ回路130及びデータ入出力回路140を含むものである。

【0087】

ここで、図24のブロック図のメモリセルアレイ240とセンスアンプ部260との配列関係が直接対応するのは、図13に示す第4の実施の形態である。しかしながら、図24のメモリセルアレイ240とセンスアンプ部260との配列関係はあくまでも一例であって、その他の実施の形態や変形例、改良例を含むものである。例えば、図16の構成は図24のメモリセルアレイ240とセンスアンプ部260との配列関係に直接対応しないが、図24のメモリセルアレイ240とセンスアンプ部260とからなるブロック内に図16の構成が実現されていると考えることができる。また、図24のメモリセルアレイ240は、複数のバンクを有する構成であっても良いことは勿論である。

【0088】

ここで、図24に示す半導体記憶装置は、データ書き込み動作に関し、以下に説明する特徴的構成を具備することができる。実際の半導体記憶装置では、複数ビットのデータが一度に書き込まれるが、この際、書き込みデータの一部をマスクして書き込みを禁止することがある。例えば、データバス上の書き込みデータを対応するセンスアンプを介してメモリセルに一度に書き込む場合、マスクすべきデータをマスクすればよい。

【0089】

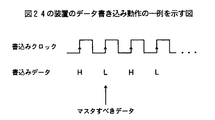

図25は、あるデータバスの1本(1ビット)のデータバス線に対する書き込み動作及びマスク動作を説明するための図である。書き込みクロックの立ち上がりに同期して、データH、L、H、L・・・が順番にメモリセルに書き込まれる。この場合、2番目のデータLの書き込みを禁止する場合には、このタイミングでデータLをマスクして、対応するメモリセルに接続するデータバス線にデータLが出力されるのを禁止すれば良い。通常、このマスク動作のために、マスク信号が生成される。

【0090】

これに対しある1つのデータバス線の1ビットデータを複数個ためて(例えば、同時に4つのセンスアンプが選択される場合にはそれぞれにつながるデータバス線にデータをためる)、一度にメモリセルに書き込む動作がある。この書き込み動作は一括書き込み動作とも呼ばれ、例えば、図25の例では、H、L、H、Lの4個の1ビットデータがたまるまで書き込み動作を行わず、4個のデータがたまると一度にメモリセルに書き込む。この場合、2番目のデータLをマスクする必要がある場合には、4個のデータを一度にメモリセルに書き込むために、2番目のデータがマスクされるデータであることを指定する必要がある。従って、図25に示すような書き込みクロックの各立ち上がりに同期してデータを書き込む場合のマスク動作では、一括してデータを書き込み際のマスク動作を実現できない。

【0091】

図26の構成は、上記複数の1ビットデータをためて一度に書き込む場合でも、その中のデータをマスクすることができることを特徴とする。より特定すれば、図26の構成は、マスクすべきデータに対応するデータバス線をフローティング状態に設定することで、マスクすべきデータと特定するとともに書き込み動作を禁止する。以下、図26に示す構成を本発明の第8の実施の形態として説明する。

【0092】

図26は、図24のセルアレイ240及びセンスアンプ部260に相当する部分を示したもので、4ビットを一括でメモリセルに書き込む場合を想定している。セルアレイ300の両側には複数のセンスアンプ(S/A)310、320が設けられ、前述したリラックス方式に従い、両側のセンスアンプ310、320から交互にビット線対が延びている。図26では、説明を判りやすくするために、各センスアンプから延びるビット線対は一対のみ示してある。センスアンプ310、320の各々はデータバスに接続される。図26では、4対のデータバス線DB0X、DB0Z;DB1X、DB1Z;DB2X、DB2Z;DB3X、DB3Zに図示するように接続されている。コラムデコーダ270はデータの書き込み時、一度に4つのデータ入出力回路(前述のデータ入出力回路140に相当するが、図26では図示を省略してある)を選択し、対応する4つのセンスアンプと上記データバス線とを接続する。

【0093】

4対のデータバス線DB0X、DB0Z;DB1X、DB1Z;DB2X、DB2Z;DB3X、DB3Z毎にそれぞれデータバス制御回路3301 、3302 、3303 、3304 が設けられている。データバス制御回路3301 、3302 、3303 、3304 はそれぞれ、書き込み指示信号線WDM0、WDM1、WDM2及びWDM3、データバス線WDB0X,WDB0Z、WDB1X、WDB1Z,WDB2X、WDB2Z、WDB3X及びWDB3Z、並びにデータバスプリチャージ指示信号線DBPに図示するように接続されている。書き込み指示信号線WDM0、WDM1、WDM2及びWDM3は、書き込み指示信号生成回路340で生成される。書き込み指示信号生成回路340は、ライトイネーブル信号WEと、データマスク信号DQM0、DQM1、DQM2及びDQM3との所定の論理演算を行い、書き込み指示信号WDM0、WDM1、WDM2及びWDM3を生成する。

【0094】

なお、データマスク信号DQM0、DQM1、DQM2及びDQM3、並びにデータバスプリチャージ信号DBPは図24のコマンドデコーダ210から供給される。また、データバス線WDB0X,WDB0Z、WDB1X、WDB1Z,WDB2X、WDB2Z、WDB3X及びWDB3Zは図24のI/Oデータバッファ/レジスタ230に接続される。

【0095】

書き込み指示信号生成回路340は、4つのナンドゲート341〜344及び4つのインバータ345〜348からなる。ナンドゲート341〜344はそれぞれ、ライトイネーブル信号WEとデータマスク信号DQM0、DQM1、DQM2及びDQM3とのナンド論理演算を行い、その出力はインバータ345〜348を介して、書き込み指示信号WDM0、WDM1、WDM2及びWDM3として出力される。なお、データマスク信号DQM0、DQM1、DQM2及びDQM3は、マスクを指示する場合にローレベルとなる。

【0096】

各データバス制御回路3301 〜3304 は、プリチャージ回路331、データバス駆動回路332、ナンドゲート333、334、及びインバータ336〜338からなる。図26では、一例としてデータバス制御回路3301 の構成のみを示している。ナンドゲート334は書き込み指示信号WDM0と書き込みデータWDB0Xのナンド論理をとり、その出力を2つのインバータ336、337を介して、データバス駆動部337のデータバス線DB0X側のCMOSインバータのPチャネルMOSトランジスタのゲートに与える。インバータ336の出力は、データバス駆動部337のデータバス線DB0Z側のCMOSインバータのNチャネルMOSトランジスタのゲートに与える。ナンドゲート333は書き込み指示信号WDM0と書き込みデータWDB0Zのナンド論理をとり、その出力を2つのインバータ335、338を介して、データバス駆動部337のデータバス線DB0Z側のCMOSインバータのPチャネルMOSトランジスタのゲートに与える。インバータ335の出力は、データバス駆動部337のデータバス線DB0X側のCMOSインバータのNチャネルMOSトランジスタのゲートに与える。上記2つのCMOSインバータの出力はそれぞれ、データバス線DB0X、DB0Zに接続されている。

【0097】

データバス駆動回路332の4つのトランジスタがすべてオフになると、データバス線DB0X、DB0Zはフローティング状態になる。

プリチャージ回路331は、2つのPチャネルMOSトランジスタ331からなる。これらのゲートは、上記データバスプリチャージ指示信号を受け、ドレインはそれぞれデータバス線DB0X及びDB0Zに接続されている。図示の構成では、データバス線DB0X及びDB0Zはハイレベル(VCC)にプリチャージされる。

【0098】

次に、図26の動作を図27のタイミング図を参照して説明する。

一度に4つのセンスアンプが選択されるデータの書き込み時、データバスプリチャージ信号DBP及びライトイネーブル信号WEが立ち上がり、書き込み動作可能となる。図27の例では、データマスク信号DQM0〜DQM2が立ち上がり、対応するデータの書き込みが指示されるが、データマスク信号DQM3はローレベルのままであり、対応するデータのマスクが指示される。この場合、書き込み指示信号生成回路340は書き込み指示信号WDM0、WDM1及びWDM2をハイレベルに設定し、書き込み指示信号WDM3をローレベルに設定する。

【0099】

上記書き込み指示信号WDM3を受けたデータバス制御回路3304 のデータバス駆動回路332の4つのトランジスタはすべてオフとなる。すなわち、書き込み指示信号WDM3がローレベルなので、インバータ335、336の出力はローレベル、インバータ337、338の出力はハイレベルになる。よって、データバス線DB3X、DB3Zは、ハイレベルのフローティング状態に設定される。このハイレベルのフローティング状態は前述したセンスアンプのデータの読み出し状態に相当するので、データを書き込みことはできない。

【0100】

その他のデータバス制御回路3301 〜3303 は書き込みデータWDB0X,WDB0Z、WDB1X、WDB1Z,WDB2X、WDB2Zに応じてデータバス線DB0X〜DB2Zが駆動される。

以上のように、マスクすべきデータに対応するデータバス線をフローティング状態に設定することで、複数データの一括同時書き込みにもかかわらずマスクすべきデータの書き込みを禁止できる。

【0101】

以上、本発明の実施の態様を説明した。本発明は、DRAM装置を全て含むものであり、特に現在注目されている高速動作可能なSDRAM(同期式DRAM)に適用して好適である。

【0102】

【発明の効果】

ビット線のリセット電位が前回の読み出しサイクルで読み出されたデータに依存して設定できるので、従来のようにVCC/2に各サイクル毎にプリチャージする必要がなく、高速動作が可能となる。

【0103】

また、センスアンプのリセットを効率的かつ効果的に行えるので、高速動作が可能となる。

更に、無駄な電流がデータバスからセンスアンプ方向に流れることを防止できる。

更に、複数の書き込みデータを一時的に保持した後一括して同時に書き込むような場合でも、任意の書き込みデータをマスクして書き込み禁止を指示することができる。

【図面の簡単な説明】

【図1】本発明の原理を説明するためのタイミング図である。

【図2】本発明の第1の実施の形態による半導体記憶装置の要部を示す回路図である。

【図3】セルの構成を示す回路図である。

【図4】図2に示すセンスアンプ回路及びデータ出力回路の構成を示す回路図である。

【図5】図2に示すダミーセル回路の構成例を示す回路図である。

【図6】第2に示す回路の動作を示すタイミング図である。

【図7】本発明の第2の実施の形態による半導体記憶装置の要部を示す回路図である。

【図8】図7に示す回路の動作を示すタイミング図である。

【図9】本発明の第3の実施の形態による半導体記憶装置の要部を示す回路図である。

【図10】図9に示す回路の動作を示すタイミング図である。

【図11】センスアンプの別の構成例を示す図である。

【図12】 センスアンプの配列例を示す図である。

【図13】本発明の第4の実施の形態による半導体記憶装置の要部を示す回路図である。

【図14】 図13に示す構成の動作を示すタイミング図である。

【図15】本発明の第5の実施の形態による半導体記憶装置の要部を示す回路図である。

【図16】図15に示す構成の動作を示すタイミング図(その1)である。

【図17】図15に示す構成の動作を示すタイミング図(その2)である。

【図18】本発明の第6の実施の形態による半導体記憶装置の要部を示す回路図である。

【図19】図18に示す構成の動作を示すタイミング図(その1)である。

【図20】図18に示す構成の動作を示すタイミング図(その2)である。

【図21】本発明の第7の実施の形態による半導体記憶装置の要部を示す回路図である。

【図22】図21に示す構成の動作を示すタイミング図(その1)である。

【図23】図22に示す構成の動作を示すタイミング図(その2)である。

【図24】本発明の半導体記憶装置の全体構成を示すブロック図である。

【図25】図24の装置のデータ書き込み動作の一例を示す図である。

【図26】本発明の第8の実施の形態による半導体記憶装置の要部を示す回路図である。

【図27】図26に示す構成の動作を示すタイミング図である。

【図28】従来の半導体記憶装置の要部を示す回路図である。

【図29】図28に示す回路図の動作を示すタイミング図である。

【符号の説明】

30、301 、302 、300 センスアンプ部

31、32、33、320、330 セルアレイ部

42 ダミーセル部

Claims (16)

- 記憶素子と、

前記記憶素子に接続されるワード線と、

選択された記憶素子に接続される選択側ビット線と、選択されない記憶素子に接続される非選択側ビット線とから成るビット線対と、

前記ビット線対に接続されるセンスアンプと、

前記ビット線対をリセットするリセット回路と、前記選択側ビット線とセンスノードを接続する第1のトランスファゲートトランジスタと、前記非選択側ビット線とセンスノードを分離する第2のトランスファゲートトランジスタとを含み、前回の読み出しサイクルで前記記憶素子から前記センスアンプによって読み出されたデータの値に応じて決定されるリセット電位を次の読み出しサイクルのリセット電位として前記ビット線対をリセットする回路と

を有し、

前記リセット回路は、前記選択側ビット線に読み出された前記データの電位が検出された後に、前記非選択側ビット線を、前記選択側ビット線で検出された電位に一致させて前記リセット電位とし、前記ビット線対をリセットする、

ことを特徴とする半導体記憶装置。 - 前記リセット電位は、前記読み出されたデータの値に応じて、高電源電圧電位または低電源電圧電位のいずれかに設定されることを特徴とする請求項1に記載の半導体記憶装置。

- 前記ビット線対に選択的に接続されるダミーセル回路をさらに有し、

前記ダミーセル回路は、前記ビット線対の非選択側ビット線の電位を、前記選択された記憶素子に接続される選択側ビット線で検出された電位とは異なる電位に設定することを特徴とする請求項1又は2に記載の半導体記憶装置。 - 各読み出しサイクルでは、前記ビット線対のうち、前記選択された記憶素子に接続される選択側ビット線のみを読み出し駆動することを特徴とする請求項2又は3に記載の半導体記憶装置。

- 前回の読み出しサイクルで選択された記憶素子から外部装置へのデータ出力動作が終了する前に、次の読み出しサイクルが開始されることを特徴とする請求項1ないし4のいずれか一項に記載の半導体記憶装置。

- 前記センスアンプは、前記ビット線対の両端に配置される第1および第2のセンスアンプ(341、342)を含み、前記リセット回路は前記センスアンプの一方が読み出した前記データに応じて他方のセンスアンプの入力電位をリセットすることを特徴とする請求項1に記載の半導体記憶装置。

- 前記第1のセンスアンプで前記記憶素子からデータを読み出す場合は、前記第2のセンスアンプは非動作であることを特徴とする請求項6に記載の半導体記憶装置。

- 前記センスアンプとデータバスの間に設けられ、コラム選択信号によって制御されるデータ入出力回路と、

前記センスアンプとデータバスの間に設けられ、前記センスアンプの状態に応じて、当該センスアンプを選択的に前記データバスに接続するゲート回路と

をさらに有することを特徴とする請求項1に記載の半導体記憶装置。 - 前記データ入出力回路は、対応するビット線を前記データバスに間接的に接続するトランジスタを有するダイレクトセンス回路であり、前記トランジスタは、対応するセンスアンプの出力レベルに応じて、前記データバスを所定の電位にすることを特徴とする請求項8に記載の半導体記憶装置。

- 前記センスアンプがオフのときに、前記所定の電位は前記データバスのリセット電位に等しいことを特徴とする請求項9に記載の半導体装置。

- 前記リセット回路は、前記選択された記憶素子から読み出された前記選択側ビット線上のデータが出力されるときに、前記非選択側ビット線をリセットすることを特徴とする請求項1に記載の半導体記憶装置。

- 前記リセット回路は、前記選択側ビット線に読み出されたデータ値がビット線の低電位に対応する値であるときは、前記非選択側ビット線を次の読み出しサイクルのために低電源電圧電位にリセットし、前記選択側ビット線に読み出されたデータ値がビット線の高電位に対応する値であるときは、前記非選択側ビット線を次の読み出しサイクルのために高電源電圧電位にリセットすることを特徴とする請求項1に記載の半導体記憶装置。

- 前記ダミーセル回路は、

低電源電圧に接続されるノードと対向ノードとを有するダミーキャパシタと、

前記ビット線対の間に接続され、前記ダミーキャパシタの対向ノードを前記ビット線対の一方のビット線に選択的に接続する第1および第2のダミーセルトランジスタと、

前記ダミーセルキャパシタの対向ノードに接続され、対向ノードにプリチャージ電位を供給するプリチャージトランジスタと

を含むことを特徴とする請求項3に記載の半導体記憶装置。 - 前記リセット回路は、前記第1及び第2のトランスファゲートトランジスタと前記センスアンプの間に位置し、前記ビット線対のいずれかに選択的に接続されるリセットトランジスタ、

をさらに含むことを特徴とする請求項1に記載の半導体記憶装置。 - 前記第1及び第2のトランスファゲートトランジスタの各々は、個別に制御されることを特徴とする請求項1に記載の半導体記憶装置。

- 前記センスアンプと前記リセット回路は、前記ビット線対の一端側に位置することを特徴とする請求項1に記載の半導体記憶装置。

Priority Applications (7)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP14231097A JP4154006B2 (ja) | 1996-12-25 | 1997-05-30 | 半導体記憶装置 |

| US08/924,315 US6154405A (en) | 1996-12-25 | 1997-09-05 | Semiconductor memory device having a dummy cell resetting the bit lines to a reset potential that is based on data read in a previous read data |

| GB9718939A GB2320778B (en) | 1996-12-25 | 1997-09-05 | Semiconductor memory device |

| GB0104983A GB2356952B (en) | 1996-12-25 | 1997-09-05 | Semiconductor memory device |

| TW086113384A TW344896B (en) | 1996-12-25 | 1997-09-15 | Semiconductor memory device |

| KR1019970048122A KR100286500B1 (ko) | 1996-12-25 | 1997-09-23 | 반도체기억장치 |

| DE19750884A DE19750884B4 (de) | 1996-12-25 | 1997-11-18 | Halbleiterspeichervorrichtung |

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP8-346032 | 1996-12-25 | ||

| JP34603296 | 1996-12-25 | ||

| JP14231097A JP4154006B2 (ja) | 1996-12-25 | 1997-05-30 | 半導体記憶装置 |

Related Child Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007262338A Division JP5003396B2 (ja) | 1996-12-25 | 2007-10-05 | 半導体記憶装置 |

| JP2007262337A Division JP5012388B2 (ja) | 1996-12-25 | 2007-10-05 | 半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH10241368A JPH10241368A (ja) | 1998-09-11 |

| JP4154006B2 true JP4154006B2 (ja) | 2008-09-24 |

Family

ID=26474362

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP14231097A Expired - Lifetime JP4154006B2 (ja) | 1996-12-25 | 1997-05-30 | 半導体記憶装置 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6154405A (ja) |

| JP (1) | JP4154006B2 (ja) |

| KR (1) | KR100286500B1 (ja) |

| DE (1) | DE19750884B4 (ja) |

| GB (1) | GB2320778B (ja) |

| TW (1) | TW344896B (ja) |

Families Citing this family (14)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6016390A (en) * | 1998-01-29 | 2000-01-18 | Artisan Components, Inc. | Method and apparatus for eliminating bitline voltage offsets in memory devices |

| KR100732287B1 (ko) * | 1999-04-08 | 2007-06-25 | 주식회사 하이닉스반도체 | 패킷 명령어 구동형 반도체 메모리 장치 |

| JP5034133B2 (ja) * | 2000-02-29 | 2012-09-26 | 富士通セミコンダクター株式会社 | 半導体記憶装置 |

| US7007187B1 (en) * | 2000-06-30 | 2006-02-28 | Intel Corporation | Method and apparatus for an integrated circuit having flexible-ratio frequency domain cross-overs |

| JP2002063788A (ja) * | 2000-08-21 | 2002-02-28 | Fujitsu Ltd | 半導体記憶装置 |

| KR100403612B1 (ko) * | 2000-11-08 | 2003-11-01 | 삼성전자주식회사 | 비트라인 프리차아지 시간(tRP)을 개선하는 메모리 셀어레이 구조를 갖는 반도체 메모리 장치 및 그 개선 방법 |

| JP4329919B2 (ja) * | 2001-03-13 | 2009-09-09 | Okiセミコンダクタ株式会社 | 半導体メモリおよび半導体メモリの駆動方法 |

| KR100600056B1 (ko) * | 2004-10-30 | 2006-07-13 | 주식회사 하이닉스반도체 | 저 전압용 반도체 메모리 장치 |

| US7764540B2 (en) * | 2006-03-01 | 2010-07-27 | Renesas Technology Corp. | Semiconductor memory device |

| US20090296514A1 (en) * | 2008-05-29 | 2009-12-03 | Chih-Hui Yeh | Method for accessing a memory chip |

| JP2011023079A (ja) * | 2009-07-17 | 2011-02-03 | Renesas Electronics Corp | 半導体装置及びデータの読み出し方法 |

| KR20140028542A (ko) * | 2012-08-29 | 2014-03-10 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 동작 방법 |

| WO2015170220A1 (en) * | 2014-05-09 | 2015-11-12 | Semiconductor Energy Laboratory Co., Ltd. | Memory device and electronic device |

| US10325648B2 (en) | 2016-12-14 | 2019-06-18 | Qualcomm Incorporated | Write driver scheme for bit-writable memories |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS5873095A (ja) * | 1981-10-23 | 1983-05-02 | Toshiba Corp | ダイナミツク型メモリ装置 |

| JPS59120597U (ja) * | 1983-01-31 | 1984-08-14 | カ−ル事務器株式会社 | パンチ |

| JPS5963091A (ja) * | 1982-09-30 | 1984-04-10 | Fujitsu Ltd | スタテイツクメモリ回路 |

| JPH0664907B2 (ja) * | 1985-06-26 | 1994-08-22 | 株式会社日立製作所 | ダイナミツク型ram |

| JP3057747B2 (ja) * | 1990-11-01 | 2000-07-04 | 日本電気株式会社 | 半導体メモリ装置 |

| JP3160316B2 (ja) * | 1991-07-25 | 2001-04-25 | 株式会社東芝 | 不揮発性半導体記憶装置 |

| CA2097308A1 (en) * | 1991-10-01 | 1993-04-02 | Terrie Frane | Memory write protection method and apparatus |

| US5406516A (en) * | 1992-01-17 | 1995-04-11 | Sharp Kabushiki Kaisha | Semiconductor memory device |

| JP3072871B2 (ja) * | 1992-03-19 | 2000-08-07 | 株式会社東芝 | 半導体メモリ装置 |

| US5339274A (en) * | 1992-10-30 | 1994-08-16 | International Business Machines Corporation | Variable bitline precharge voltage sensing technique for DRAM structures |

| US5539696A (en) * | 1994-01-31 | 1996-07-23 | Patel; Vipul C. | Method and apparatus for writing data in a synchronous memory having column independent sections and a method and apparatus for performing write mask operations |

-

1997

- 1997-05-30 JP JP14231097A patent/JP4154006B2/ja not_active Expired - Lifetime

- 1997-09-05 GB GB9718939A patent/GB2320778B/en not_active Expired - Fee Related

- 1997-09-05 US US08/924,315 patent/US6154405A/en not_active Expired - Lifetime

- 1997-09-15 TW TW086113384A patent/TW344896B/zh not_active IP Right Cessation

- 1997-09-23 KR KR1019970048122A patent/KR100286500B1/ko not_active IP Right Cessation

- 1997-11-18 DE DE19750884A patent/DE19750884B4/de not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| DE19750884A1 (de) | 1998-07-09 |

| DE19750884B4 (de) | 2010-01-21 |

| GB2320778A (en) | 1998-07-01 |

| US6154405A (en) | 2000-11-28 |

| KR100286500B1 (ko) | 2001-04-16 |

| GB2320778B (en) | 2001-06-27 |

| KR19980063480A (ko) | 1998-10-07 |

| GB9718939D0 (en) | 1997-11-12 |

| TW344896B (en) | 1998-11-11 |

| JPH10241368A (ja) | 1998-09-11 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US4943944A (en) | Semiconductor memory using dynamic ram cells | |

| US6205071B1 (en) | Semiconductor memory device including sense amplifier circuit differing in drivability between data write mode and data read mode | |

| US6950368B2 (en) | Low-voltage sense amplifier and method | |

| KR100197757B1 (ko) | 다이나믹형 반도체메모리장치 | |

| JP2001006359A (ja) | 半導体記憶装置 | |

| KR100776612B1 (ko) | 반도체 기억 장치 | |

| JP4154006B2 (ja) | 半導体記憶装置 | |

| JPH029081A (ja) | 半導体記憶装置 | |

| KR100290286B1 (ko) | 빠른 입출력 라인 프리차지 스킴을 구비한 반도체 메모리 장치 | |

| JP3101297B2 (ja) | 半導体メモリ装置 | |

| US6320806B1 (en) | Input/output line precharge circuit and semiconductor memory device adopting the same | |

| JP2006324007A (ja) | Dramアレイ用ビット線プリチャージ手法 | |

| KR910008100B1 (ko) | 반도체기억장치 | |

| JPH06223561A (ja) | 半導体メモリ装置及び初期化方法 | |

| JP2718577B2 (ja) | ダイナミックram | |

| JP2786420B2 (ja) | データリード/ライト方法及びその装置 | |

| KR100311269B1 (ko) | 반도체장치 | |

| US6643201B2 (en) | Memory device having read charge control, write charge control and floating or precharge circuits | |

| JP5003396B2 (ja) | 半導体記憶装置 | |

| JP5012388B2 (ja) | 半導体記憶装置 | |

| JP3766710B2 (ja) | 半導体記憶装置 | |

| KR100724517B1 (ko) | 반도체 기억 장치 | |

| JPS63311690A (ja) | 半導体記憶装置 | |

| GB2356952A (en) | Semiconductor memory device | |

| JPH0574149A (ja) | 半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20061031 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20061114 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20070112 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20070807 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20071005 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20080226 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080326 |

|

| A911 | Transfer of reconsideration by examiner before appeal (zenchi) |

Free format text: JAPANESE INTERMEDIATE CODE: A911 Effective date: 20080509 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080624 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080707 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110711 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110711 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110711 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110711 Year of fee payment: 3 |

|

| S531 | Written request for registration of change of domicile |

Free format text: JAPANESE INTERMEDIATE CODE: R313531 |

|

| S533 | Written request for registration of change of name |

Free format text: JAPANESE INTERMEDIATE CODE: R313533 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110711 Year of fee payment: 3 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120711 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120711 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130711 Year of fee payment: 5 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| EXPY | Cancellation because of completion of term |