JP4080659B2 - 半導体装置 - Google Patents

半導体装置 Download PDFInfo

- Publication number

- JP4080659B2 JP4080659B2 JP2000020407A JP2000020407A JP4080659B2 JP 4080659 B2 JP4080659 B2 JP 4080659B2 JP 2000020407 A JP2000020407 A JP 2000020407A JP 2000020407 A JP2000020407 A JP 2000020407A JP 4080659 B2 JP4080659 B2 JP 4080659B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- semiconductor layer

- semiconductor

- voltage

- main electrode

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 128

- 230000000903 blocking effect Effects 0.000 claims description 38

- 230000005684 electric field Effects 0.000 claims description 14

- 239000012535 impurity Substances 0.000 claims description 14

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 10

- 229910052710 silicon Inorganic materials 0.000 claims description 10

- 239000010703 silicon Substances 0.000 claims description 10

- 239000000758 substrate Substances 0.000 claims description 5

- 230000010355 oscillation Effects 0.000 description 26

- 238000011084 recovery Methods 0.000 description 13

- 230000001629 suppression Effects 0.000 description 6

- 238000010586 diagram Methods 0.000 description 5

- 239000000969 carrier Substances 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- 229910052751 metal Inorganic materials 0.000 description 4

- 239000002184 metal Substances 0.000 description 4

- 230000015556 catabolic process Effects 0.000 description 3

- 238000005215 recombination Methods 0.000 description 2

- 230000006798 recombination Effects 0.000 description 2

- VMXJCRHCUWKQCB-UHFFFAOYSA-N NPNP Chemical compound NPNP VMXJCRHCUWKQCB-UHFFFAOYSA-N 0.000 description 1

- 238000009825 accumulation Methods 0.000 description 1

- 230000002411 adverse Effects 0.000 description 1

- 238000009792 diffusion process Methods 0.000 description 1

- 230000000694 effects Effects 0.000 description 1

- 238000010894 electron beam technology Methods 0.000 description 1

- 230000007257 malfunction Effects 0.000 description 1

- 238000000034 method Methods 0.000 description 1

- 229910000510 noble metal Inorganic materials 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

- H01L29/87—Thyristor diodes, e.g. Shockley diodes, break-over diodes

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices adapted for rectifying, amplifying, oscillating or switching, or capacitors or resistors with at least one potential-jump barrier or surface barrier, e.g. PN junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/86—Types of semiconductor device ; Multistep manufacturing processes therefor controllable only by variation of the electric current supplied, or only the electric potential applied, to one or more of the electrodes carrying the current to be rectified, amplified, oscillated or switched

- H01L29/861—Diodes

Description

【発明の属する技術分野】

この発明は、高耐圧かつ速やかな逆回復特性が要求されるPN接合部を有するダイオード等の半導体装置に関する。

【0002】

【従来の技術】

IGBT(Insulated Gate Bipolar Transistor)やGCT(Gate Commutated Turn-off Thyristor)などの高耐圧スイッチング素子の応用に必要な還流用ダイオードや電圧クランプ用ダイオードとして、高耐圧かつ速やかな逆回復特性がダイオードに要求される。

【0003】

図13は、上記要求に応えた従来の一般的なダイオードの断面構造を示す断面図である。同図に示すように、N+層603上にシリコン等の半導体基板であるN-層601が形成され、N-層601上にP層602が形成されている。N+層603はN-層601に比べN型の不純物濃度が高い。

【0004】

P層602上には電気抵抗の小さい金属からなるアノード電極604が形成され、N+層603下には、アノード電極604と同様に電気抵抗の小さい金属からなるカソード電極605が形成される。

【0005】

PN接合近傍のライフタイムはプロトン照射等により制御され、キャリア再結合の中心が形成されている。また、半導体基板全体のライフタイムは貴金属の拡散や電子線照射等の技術によって短くなるように制御されている。

【0006】

ダイオードにおいて、順方向に電流が流れている状態から、瞬間的に外部回路の切り替えによって逆バイアスを加えようとすると、ダイオードには少数キャリア蓄積現象があるため、電流が“0”になっても直ちに逆方向回復せず、過渡的なある期間だけ大きな逆電流(逆バイアス値と外部回路のインダクタンスで決まる電流減少率を持った電流)が流れる。この逆電流はPN接合近傍にある過剰キャリアがある濃度以下に減少して、空乏層が形成されるまで流れる。

【0007】

空乏層が形成されると逆電圧が発生し始め、空乏層の広がりに対応して逆電圧が徐々に増加するとともに、逆電流が徐々に減少する。そして、素子電圧が印加逆電圧に定常的に等しくなって逆回復動作が完了する。

【0008】

【発明が解決しようとする課題】

図13で示したような構造の従来のダイオードは、PN接合近傍のライフタイムを局部的に短く制御することにより、順電圧が低く、かつ逆回復電流(逆電流のピーク値)が小さい、di/dt耐量(ダイオードに損傷を生じることなく付与することのできる電流減少率di/dtの最大値)の高い特性を実現できる。

【0009】

しかしながら、逆回復時の逆バイアス電圧が高い場合、ダイオードの印加電圧が急激に振動し、周辺の電気機器の誤動作をもたらす等、ノイズの原因となる問題点があった。ダイオードの電圧の振動は次のように発生すると考えられる。

【0010】

逆回復動作時のダイオードは、空乏層と過剰キャリアをパラメータにした容量成分と、印加電圧と漏れ電流及び過剰キャリアの再結合電流をパラメータにした抵抗成分とを有している。上記抵抗成分、上記容量成分、及び逆電圧を印加するための外部回路のインダクタンス成分でLCR直列回路が形成される。ダイオードの容量成分と抵抗成分は時間的に変化し、空乏層外にある過剰キャリアが消滅すると、抵抗成分が急激に増加して、LCR直列回路の固有振動条件に達し、電圧発振を起こす。また、空乏層がN+層603に到達すると抵抗成分が急激に変化し、電圧発振を発生させる場合もある。

【0011】

この発明は上記問題点を解決するためになされたもので、他に悪影響を及ぼすことなく電圧発振を抑制したPN接合部を有する半導体装置を得ることを目的とする。

【0012】

【課題を解決するための手段】

この発明に係る請求項1記載の半導体装置は、第1の導電型の第1の半導体層と、前記第1の半導体層上に形成される第1の導電型の第2の半導体層とを備え、前記第2の半導体層は前記第1の半導体層より第1の導電型の不純物濃度が低く、前記第2の半導体層上に形成される第2の導電型の第3の半導体層と、前記第3の半導体層の上方に形成される第1の主電極と、前記第1の半導体層の下方に形成される第2の主電極とをさらに備え、前記第2の半導体層と前記第3の半導体層との界面のPN接合部による逆方向の電圧阻止能力の略1/2〜略2/3の逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達しない第1の条件と、前記電圧阻止能力の略2/3を越える逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達する第2の条件とを共に満足するように、前記第2の半導体層の膜厚を設定している。

【0013】

また、請求項2の発明は、請求項1記載の半導体装置であって、前記第1の主電極は前記第3の半導体層上に直接形成される主電極を含み、前記第2の主電極は前記第1の半導体層下に直接形成される主電極を含む。

【0014】

また、請求項3の発明は、請求項1記載の半導体装置であって、前記第1の半導体層下に形成される第2の導電型の第4の半導体層をさらに備え、前記第1の主電極は前記第3の半導体層上に直接形成される主電極を含み、前記第2の主電極は前記第4の半導体層下に直接形成される主電極を含む。

【0015】

また、請求項4の発明は、請求項1記載の半導体装置であって、前記第1の半導体層下に形成される第2の導電型の第4の半導体層と、前記第3の半導体層上に形成される第1の導電型の第5の半導体層とをさらに備え、前記第1の主電極は前記第5の半導体層上に直接形成される主電極を含み、前記第2の主電極は前記第4の半導体層下に直接形成される主電極を含む。

【0016】

また、請求項5の発明は、請求項2記載の半導体装置であって、前記第3の半導体層は、前記第2の半導体層の表面に選択的に形成される複数の半導体領域を含み、前記第1の主電極は、前記複数の半導体領域上に形成される複数の部分電極を含む。

【0017】

また、請求項6の発明は、請求項2記載の半導体装置であって、前記第2及び第3の半導体層の界面近傍におけるライフタイムは、前記第1及び第2の半導体層の界面近傍におけるライフタイムより短く設定される。

【0018】

また、請求項7の発明は、請求項1ないし請求項6のうちいずれか1項に記載の半導体装置であって、前記第2の条件は、前記電圧阻止能力と同等の逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達する条件を含む。

【0019】

さらに、請求項8の発明は、請求項1ないし請求項7のうちいずれか1項に記載の半導体装置であって、前記第2の半導体層はシリコン基板を含み、前記電圧阻止能力と同等の逆バイアス電圧設定時に前記空乏層にかかる電界が、シリコンが耐えうる電界強度の最大値以下になる第3の条件を満足するように、前記第2の半導体層の前記不純物濃度を設定する。

【0020】

【発明の実施の形態】

<原理>

本発明での基本構造はP層、N-層及びN+層の3層構造であり、例えば、後述する実施の形態1の構造では、図8のP層102、N-層101及びN+層103がそれぞれP層、N-層及びN+層に相当する。

【0021】

この基本構造のダイオード部(PN接合部)に対して逆回復動作(PN接合が順方向の導通状態から逆方向の阻止状態に切り換わるとき、逆方向の電圧阻止能力を回復する動作)をさせた時、基本構造内に生じる空乏層がN+層に到達すると抵抗成分が急激に変化し、これがトリガとなって電圧発振を発生させる。

【0022】

電圧発振を発生させないようにするには、基本構造において、N-層の膜厚を厚くし、P層及びN-層間のPN接合部からN-層に拡がる空乏層がN+層に到達しないように設定すれば良い。しかしながら、単純にN-層を厚くする設定では、N-層の膜厚(ウェハ厚)が厚くなりすぎてオン電圧の増大を招いてしまう問題点があった。

【0023】

一方、ウェハ厚を薄くしたPIN構造ではオン電圧は低いが、逆回復動作時に空乏層がN+層に到達してしまい、非常に大きな電圧発振を回避することができなかった。

【0024】

本発明は、オン電圧の低下と電圧発振の抑制をバランス良く図る基本構造を得ることである。そこで、基本構造のダイオード部に対して、電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時に、P層及びN-層間のPN接合部からN-層に拡がる空乏層がN+層に到達せず、電圧阻止能力の略2/3を越える逆方向電圧印加時に上記空乏層がN+層に到達するように、N-層の膜厚を設定することを見いだした。

【0025】

図1は本発明の構造のN-層の膜厚とオン電圧との関係を示すグラフである。同図において、本発明により設定したN-層の膜厚(以下、「設定膜厚」と略記する)を“1”としている。同図に示すように、N-層の膜厚を設定膜厚の膜厚より厚くするとオン電圧は上昇し、例えば、設定膜厚の2倍に設定するするとオン電圧が0.8V程度も上昇してしまう。一方、N-層の膜厚を設定膜厚の膜厚より薄くするとオン電圧は下降するが、その度合いは小さく、例えば、設定膜厚の半分にしてもオン電圧は0.1〜0.2V程度しか下降しない。

【0026】

一方、電圧阻止能力の略2/3以下の逆方向電圧の印加時には、PN接合部から拡がる空乏層がN+層に到達しないため、電圧発振の大きさをほぼ“0”に抑えることができる。

【0027】

図2は、電圧阻止能力の略2/3を越える逆方向電圧の印加時に空乏層がN - 層内の拡がりの割合と電圧発振の大きさを示すグラフである。同図に示すように、電圧阻止能力の略2/3を越える逆方向電圧が印加されて空乏層がN+層に到達しN+層内に拡がっても、電圧の発振の大きさが2KVを大きく下回る許容範囲に抑制できている。

【0028】

図3は逆回復動作時の逆バイアス設定例を示す波形図である。同図に示すように、1〜2V程度の定電圧をダイオードに与え順方向電流を流した状態から、逆バイアスを与える。この際、そのピーク値は電圧阻止能力の略2/3程度であり、定常電圧は略1/2当たりて使用されるの一般的である。例えば、−4.5KV(逆方向を「−」で示す)の電圧阻止能力のダイオードにおいて略2/3である−3KV程度がピーク値となり、略1/2の−2.25KVが定常電圧となる。

【0029】

そのような状況を加味して、前述したように、本発明では、基本構造のダイオード部に対して、電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時にN-層に拡がる空乏層がN+層に到達しない第1の条件と、電圧阻止能力の略2/3を越える逆方向電圧印加時に上記空乏層がN+層に到達する第2の条件とを共に満足するように、N-層の膜厚を設定することにした。

【0030】

前述したように、逆回復動作時には電圧阻止能力の略1/2〜略2/3の逆バイアスが設定されるため、N-層の膜厚は第1の条件を満足しておりこの期間においてN-層に拡がる空乏層がN+層に到達することはないため、上述したように電圧振動を効果的に抑制することができる。

【0031】

そして、N-層の膜厚は第2の条件を満足するレベルに薄く設定されているため、オン電圧も適度なレベルで低く設定することができる。

【0032】

さらに、実使用に耐えるべく、電圧阻止能力の1/1程度の逆バイアス電圧設定時に空乏層にかかる電界がシリコン最大電界強度(シリコンが耐えうる電界強度の最大値)以下の実使用レベルになる第3の条件を満足するように、N-層の不純物濃度(比抵抗)を設定する。

【0033】

なお、N-層の不純分濃度は空乏層の伸びに関連するため、実際には、第1〜第3の条件の相互関連を考慮してN-層の不純物濃度と膜厚とを決定することになる。

【0034】

図4は本発明の構造を特徴を示す説明図である。図4に示すように、本発明は、P層102、N-層101及びN+層103の3層構造を基本構造としており、電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時にN-層101とP層102とのPN接合部から生じる空乏層がN+層103に到達せずL1で示す電界分布となり、電圧阻止能力の略2/3を越える逆方向電圧印加時に上記空乏層がN+層103に到達し、L2で示す電界分布となる。

【0035】

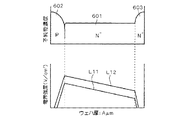

図5は図13で示した従来のPIN構造のダイオードの特徴を示す説明図である。同図に示すように、PIN構造は、P層602、N-層601及びN+層603の3層構造を基本構造としており、電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時にN-層601とP層602とのPN接合部で生じる空乏層、及び電圧阻止能力の略2/3を越える逆方向電圧印加時に上記PN接合部で生じる空乏層が共にN+層603に到達する。なお、前者の場合の電界分布をL11に、後者の場合の電界分布をL12に示す。

【0036】

図6は単純なPN接合構造のダイオードの特徴を示す説明図である。同図に示すように、単純PN接合構造は、P層702及びN-層701の2層構造を基本構造としており、電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時にN-層601とP層602とのPN接合部で生じる空乏層、及び電圧阻止能力の略2/3を越える逆方向電圧印加時に生じる上記空乏層は共にN+層63に到達しない。なお、前者の場合の電界分布をL21に、後者の場合の電界分布をL22に示す。

【0037】

したがって、N-層の膜厚以外の条件を同一とし、PIN構造のN-層601の膜厚をAμmと仮定した場合、N-層101層の膜厚は(A+α(>0))μmとなり、N-層701の膜厚は(A+β(>α))μmとなる。

【0038】

図7は本発明の構造、PIN構造、及びPN接合構造それぞれのオン電圧及び電圧発振の割合を示すグラフである。同図のオン電圧曲線L3及び電圧発振曲線L4に示すように、本発明の構造は、従来のPIN構造やPN接合構造にくらべ、オン電圧の低下及び電圧発振の抑制をバランス良く達成することができる。

【0039】

なお、第2の条件の電圧阻止能力の略2/3を越える電圧としては、電圧阻止能力と同等の電圧を採用することが、現実的な設計を考えると望ましいため、以下で述べる実施の形態では電圧阻止能力と同等の電圧を第2の条件用の逆方向電圧として採用している。

【0040】

<実施の形態1>

図8はこの発明の実施の形態1である半導体装置の構造を示す断面図である。同図に示すように、N+層103層上にシリコン等の半導体基板であるN-層101が形成され、N-層101上にP層102が形成されており、N+層103はN-層101に比べ不純物濃度が高い。

【0041】

P層102上には電気抵抗の小さい金属からなるアノード電極104が形成され、N+層103下には、アノード電極104と同様に電気抵抗の小さい金属からなるカソード電極105が形成される。

【0042】

このように実施の形態1の半導体装置は、P層102、(N-層101,N+層103)からなるダイオードを構成している。

【0043】

この際、前述したように、このダイオードのPN接合部の電圧阻止能力の略1/2〜略2/3の逆方向電圧印加時にN-層101とP層102とのPN接合部からN-層101に拡がる空乏層がN+層103に到達しない第1の条件と、電圧阻止能力の略1/1の逆方向電圧印加時に上記空乏層がN+層103に到達する第2の条件を共に満足するように、N-層101の膜厚を設定している。

【0044】

さらに、電圧阻止能力の1/1程度の逆バイアス電圧設定時に空乏層にかかる電界がシリコン最大電界強度以下になるように、N-層101の不純物濃度(比抵抗)を設定している。

【0045】

このような構造の実施の形態1によって、オン電圧の低下及び電圧発振の低下をバランス良く達成することができるダイオードを得ることができる。

【0046】

なお、実施の形態1の実例として、P層102の不純物濃度が5.0×1023atom/m3、N-層101の不純物濃度が2.1×1019atom/m3(比抵抗2.2Ω・m)、N+層103の不純物濃度が1.0×1020atom/m3のとき、ウェハ厚であるN-層101の膜厚が600μm、P層102の膜厚90μm、N+層103の膜厚が40μmの構成が考えられ、このとき、電圧阻止能力は約4.5KVを呈する。

【0047】

<実施の形態2>

図9はこの発明の実施の形態2である半導体装置の構造を示す断面図である。同図に示すように、N+層103とカソード電極105との間にP層106が介挿されている。他の構造は全て図8で示した実施の形態1と同様であるため、説明を省略する。

【0048】

このように実施の形態2の半導体装置は、P層102、(N-層101,N+層103)及びP層106からなるPNPバイポーラトランジスタを構成している。このような構造の実施の形態2のバイポーラトランジスタは、オン電圧の低下及び電圧発振の低下をバランス良く達成することができる。

【0049】

<実施の形態3>

図10はこの発明の実施の形態3である半導体装置の構造を示す断面図である。同図に示すように、P層102とアノード電極104との間にN層107が介挿されている。他の構造は全て図9で示した実施の形態2と同様であるため、説明を省略する。

【0050】

このように、実施の形態3の半導体装置は、N層107、P層102、(N-層101,N+層103)及びP層106からなるNPNPサイリスタを構成している。このような構造の実施の形態3のサイリスタはオン電圧の低下及び電圧発振の低下をバランス良く達成することができる。

【0051】

<実施の形態4>

図11はこの発明の実施の形態4である半導体装置の構造を示す断面図である。同図に示すように、図8で示した実施の形態1のP層102の代わりに複数のP領域108がN-層101の表面に選択的に形成されている。そして、複数のP領域108上それぞれに部分アノード電極109が形成されている。他の構造は全て図8で示した実施の形態1と同様であるため、説明を省略する。

【0052】

このような構造の実施の形態4によって、複数のP領域108それぞれの側面分にもN-層101とによってPN接合部を形成することができるため、実施の形態1以上に耐圧の向上を図ったダイオードを得ることができる。

【0053】

<実施の形態5>

図12はこの発明の実施の形態5である半導体装置の構造を示す断面図である。実施の形態5の構造はほぼ図8で示した実施の形態1の構造と等価である。しかしながら、N-層101とN+層103との接合近傍のライフタイムより、P層102とN-層101との接合近傍のライフタイムの方が短くなるように制御されている点が異なる。

【0054】

このような構造の実施の形態5は、N-層101とP層102とのPN接合部近傍のライフタイムが短く設定されるため、N-層101とP層102とのPN接合部からN-層101に拡がる空乏層の伸びが抑制され、他の条件を同一と仮定すると実施の形態1以上にN-層101の膜厚を薄くしても、上記第1〜第3の条件を満足することができる。

【0055】

【発明の効果】

以上説明したように、この発明における請求項1記載の半導体装置の第2の半導体層の膜厚は、上記第1の条件を満足するように設定されているため、逆回復動作において一般的に使用される電圧阻止能力の略1/2〜2/3の逆方向電圧の印加時に、上記空乏層が第1の半導体層に達することにより生ずる電圧発振を確実に抑制することができる。

【0056】

加えて、第2の半導体層の膜厚は、上記第2の条件を満足する厚みに設定されているため、オン電圧を適切なレベルで低く維持することができる。

【0057】

その結果、オン電圧の低下及び電圧発振の抑制をバランス良く達成することができる。

【0058】

請求項2記載の半導体装置によって、オン電圧の低下及び電圧発振の抑制をバランス良く達成するダイオードを得ることにができる。

【0059】

請求項3記載の半導体装置によって、オン電圧の低下及び電圧発振の抑制をバランス良く達成するトランジスタを得ることにができる。

【0060】

請求項4記載の半導体装置によって、オン電圧の低下及び電圧発振の抑制をバランス良く達成するサイリスタを得ることにができる。

【0061】

請求項5記載の半導体装置における複数の半導体領域は、それぞれの側面分にも第1の半導体層とによってPN接合部を形成することができるため、耐圧の向上を図ったダイオードを得ることができる。

【0062】

請求項6記載の半導体装置は、第2及び第3の半導体層の界面近傍(PN接合部近傍)のライフタイムを短く設定することにより、上記PN接合部から拡がる空乏層の伸びが抑制されるため、より薄い膜厚の第2の半導体層を得ることができる。

【0063】

請求項7記載の半導体装置は、第2の条件用の逆方向電圧として電圧阻止能力と同等の電圧を用いるため、現実的な設計に即した構造となる。

【0064】

請求項8記載の半導体装置は、電圧阻止能力に相当する逆バイアス電圧設定時に空乏層にかかる電界が、シリコンが耐えうる電界強度の最大値以下になる第3の条件を満足するように、第2の半導体層の不純物濃度を設定するため、実動作に支障は来さない。

【図面の簡単な説明】

【図1】 本発明の構造のN-層の膜厚とオン電圧との関係を示すグラフである。

【図2】 電圧阻止能力の2/3を越える逆方向電圧の印加時に、空乏層のN-層内の拡がりの割合と電圧発振の大きさを示すグラフである。

【図3】 ダイオードの逆回復動作時の逆バイアス電圧変化を示す波形図である。

【図4】 本発明の構造を特徴を示す説明図である。

【図5】 従来のPIN構造のダイオードの特徴を示す説明図である。

【図6】 PN接合構造のダイオードの特徴を示す説明図である。

【図7】 本発明の構造、PIN構造、及びPN接合構造それぞれのオン電圧及び電圧発振の割合を示すグラフである。

【図8】 この発明の実施の形態1である半導体装置の構造を示す断面図である。

【図9】 この発明の実施の形態2である半導体装置の構造を示す断面図である。

【図10】 この発明の実施の形態3である半導体装置の構造を示す断面図である。

【図11】 この発明の実施の形態4である半導体装置の構造を示す断面図である。

【図12】 この発明の実施の形態5である半導体装置の構造を示す断面図である。

【図13】 従来の一般的なダイオードの断面構造を示す断面図である。

【符号の説明】

101 N-層、102,106 P層、103 N+層、104 アノード電極、105 カソード電極、107 N層、108 P領域、109 部分アノード電極。

Claims (8)

- 第1の導電型の第1の半導体層と、

前記第1の半導体層上に形成される第1の導電型の第2の半導体層とを備え、前記第2の半導体層は前記第1の半導体層より第1の導電型の不純物濃度が低く、

前記第2の半導体層上に形成される第2の導電型の第3の半導体層と、

前記第3の半導体層の上方に形成される第1の主電極と、

前記第1の半導体層の下方に形成される第2の主電極とをさらに備え、

前記第2の半導体層と前記第3の半導体層との界面のPN接合部による逆方向の電圧阻止能力の略1/2〜略2/3の逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達しない第1の条件と、前記電圧阻止能力の略2/3を越える逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達する第2の条件とを共に満足するように、前記第2の半導体層の膜厚を設定したことを特徴とする、

半導体装置。 - 請求項1記載の半導体装置であって、

前記第1の主電極は前記第3の半導体層上に直接形成される主電極を含み、

前記第2の主電極は前記第1の半導体層下に直接形成される主電極を含む、

半導体装置。 - 請求項1記載の半導体装置であって、

前記第1の半導体層下に形成される第2の導電型の第4の半導体層をさらに備え、

前記第1の主電極は前記第3の半導体層上に直接形成される主電極を含み、

前記第2の主電極は前記第4の半導体層下に直接形成される主電極を含む、

半導体装置。 - 請求項1記載の半導体装置であって、

前記第1の半導体層下に形成される第2の導電型の第4の半導体層と、

前記第3の半導体層上に形成される第1の導電型の第5の半導体層とをさらに備え、

前記第1の主電極は前記第5の半導体層上に直接形成される主電極を含み、

前記第2の主電極は前記第4の半導体層下に直接形成される主電極を含む、

半導体装置。 - 請求項2記載の半導体装置であって、

前記第3の半導体層は、前記第2の半導体層の表面に選択的に形成される複数の半導体領域を含み、

前記第1の主電極は、前記複数の半導体領域上に形成される複数の部分電極を含む、

半導体装置。 - 請求項2記載の半導体装置であって、

前記第2及び第3の半導体層の界面近傍におけるライフタイムは、前記第1及び第2の半導体層の界面近傍におけるライフタイムより短く設定される、

半導体装置。 - 請求項1ないし請求項6のうちいずれか1項に記載の半導体装置であって、

前記第2の条件は、前記電圧阻止能力と同等の逆方向電圧が前記第1及び第2の主電極に印加された時に前記PN接合部から伸びる空乏層が前記第1の半導体層に到達する条件を含む、

半導体装置。 - 請求項1ないし請求項7のうちいずれか1項に記載の半導体装置であって、

前記第2の半導体層はシリコン基板を含み、

前記電圧阻止能力と同等の逆バイアス電圧設定時に前記空乏層にかかる電界が、シリコンが耐えうる電界強度の最大値以下になる第3の条件を満足するように、前記第2の半導体層の前記不純物濃度を設定する、

半導体装置。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000020407A JP4080659B2 (ja) | 2000-01-28 | 2000-01-28 | 半導体装置 |

| US09/619,316 US6388306B1 (en) | 2000-01-28 | 2000-07-18 | Semiconductor device with rapid reverse recovery characteristic |

| DE10049354A DE10049354B4 (de) | 2000-01-28 | 2000-10-05 | Halbleiterbauelement |

| CH01976/00A CH695808A5 (de) | 2000-01-28 | 2000-10-06 | Halbleiterbauelement. |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2000020407A JP4080659B2 (ja) | 2000-01-28 | 2000-01-28 | 半導体装置 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2001210651A JP2001210651A (ja) | 2001-08-03 |

| JP2001210651A5 JP2001210651A5 (ja) | 2005-10-27 |

| JP4080659B2 true JP4080659B2 (ja) | 2008-04-23 |

Family

ID=18546974

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2000020407A Expired - Fee Related JP4080659B2 (ja) | 2000-01-28 | 2000-01-28 | 半導体装置 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6388306B1 (ja) |

| JP (1) | JP4080659B2 (ja) |

| CH (1) | CH695808A5 (ja) |

| DE (1) | DE10049354B4 (ja) |

Families Citing this family (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB0129066D0 (en) * | 2001-12-05 | 2002-01-23 | Koninkl Philips Electronics Nv | Rectifying diode |

| DE10208965B4 (de) * | 2002-02-28 | 2007-06-21 | Semikron Elektronik Gmbh & Co. Kg | Leistungshalbleiterbauelement für Sperrspannungen über 2000V |

| CN102832121B (zh) * | 2011-06-17 | 2015-04-01 | 中国科学院微电子研究所 | 快恢复二极管制造方法 |

| JP5620421B2 (ja) | 2012-02-28 | 2014-11-05 | 株式会社東芝 | 半導体装置 |

| WO2014153527A1 (en) * | 2013-03-21 | 2014-09-25 | Bourns, Inc. | Transient voltage suppressor, design and process |

| JP6184352B2 (ja) * | 2014-03-14 | 2017-08-23 | 株式会社東芝 | 半導体装置 |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| DE2608432C3 (de) * | 1976-03-01 | 1981-07-09 | Siemens AG, 1000 Berlin und 8000 München | Leistungsdiode |

| JPS5839070A (ja) * | 1981-08-31 | 1983-03-07 | Toshiba Corp | 半導体装置 |

| US4623910A (en) * | 1982-09-24 | 1986-11-18 | Risberg Robert L | Semiconductor device |

| JPS59189679A (ja) * | 1983-04-13 | 1984-10-27 | Hitachi Ltd | ダイオ−ド |

| DE3435464A1 (de) * | 1984-09-27 | 1986-04-10 | Robert Bosch Gmbh, 7000 Stuttgart | Gleichrichterdiode |

| US5075740A (en) * | 1991-01-28 | 1991-12-24 | Sanken Electric Co., Ltd. | High speed, high voltage schottky semiconductor device |

| JPH08125200A (ja) * | 1994-10-25 | 1996-05-17 | Mitsubishi Electric Corp | 半導体装置及びその製造方法 |

| JPH08148699A (ja) | 1994-11-21 | 1996-06-07 | Shindengen Electric Mfg Co Ltd | 整流ダイオ−ド |

| US5637898A (en) * | 1995-12-22 | 1997-06-10 | North Carolina State University | Vertical field effect transistors having improved breakdown voltage capability and low on-state resistance |

| JP3622405B2 (ja) | 1997-02-28 | 2005-02-23 | 株式会社日立製作所 | 半導体スイッチング素子及びigbtモジュール |

-

2000

- 2000-01-28 JP JP2000020407A patent/JP4080659B2/ja not_active Expired - Fee Related

- 2000-07-18 US US09/619,316 patent/US6388306B1/en not_active Expired - Fee Related

- 2000-10-05 DE DE10049354A patent/DE10049354B4/de not_active Revoked

- 2000-10-06 CH CH01976/00A patent/CH695808A5/de not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US6388306B1 (en) | 2002-05-14 |

| JP2001210651A (ja) | 2001-08-03 |

| DE10049354A1 (de) | 2001-08-09 |

| DE10049354B4 (de) | 2004-08-05 |

| CH695808A5 (de) | 2006-08-31 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6204717B1 (en) | Semiconductor circuit and semiconductor device for use in equipment such as a power converting apparatus | |

| JP3751976B2 (ja) | 炭化ケイ素サイリスタ | |

| JP4980126B2 (ja) | フリーホイールダイオードとを有する回路装置 | |

| JP4843253B2 (ja) | 電力用半導体装置 | |

| JP3968912B2 (ja) | ダイオード | |

| KR20110134486A (ko) | 실리콘 카바이드 바이폴라 접합 트랜지스터 | |

| JP5453848B2 (ja) | 半導体装置及び電力変換装置 | |

| JPH1093113A (ja) | ダイオード | |

| JPH11274482A (ja) | 半導体装置 | |

| US5701018A (en) | Semiconductor device having parallel connection of an insulated gate bipolar transistor and a diode | |

| JP4080659B2 (ja) | 半導体装置 | |

| JP3833387B2 (ja) | パワーダイオード | |

| JPH1126779A (ja) | パワーダイオード | |

| JP2001196606A (ja) | ダイオード | |

| JP2007116160A (ja) | 大容量性負荷のためのトレンチigbt | |

| US20180138265A1 (en) | Power semiconductor device and method therefor | |

| JPH05226638A (ja) | 半導体装置 | |

| JP2008539571A (ja) | 可制御半導体ダイオード、電子部品および電圧中間形コンバータ | |

| JP3409503B2 (ja) | ダイオード及びダイオードの駆動方法並びに半導体回路 | |

| JP3622405B2 (ja) | 半導体スイッチング素子及びigbtモジュール | |

| JPH06268226A (ja) | 絶縁ゲート型バイポーラトランジスタ | |

| JP3216315B2 (ja) | 絶縁ゲート型バイポーラトランジスタ | |

| JP3248383B2 (ja) | 半導体装置 | |

| WO2023188577A1 (ja) | 半導体装置および電力変換装置 | |

| JP2504609B2 (ja) | 半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050802 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050802 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20071114 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20071120 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20080108 |

|

| RD04 | Notification of resignation of power of attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7424 Effective date: 20080108 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20080205 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20080207 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110215 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |