JP3908549B2 - Rfidタグの製造方法 - Google Patents

Rfidタグの製造方法 Download PDFInfo

- Publication number

- JP3908549B2 JP3908549B2 JP2002024295A JP2002024295A JP3908549B2 JP 3908549 B2 JP3908549 B2 JP 3908549B2 JP 2002024295 A JP2002024295 A JP 2002024295A JP 2002024295 A JP2002024295 A JP 2002024295A JP 3908549 B2 JP3908549 B2 JP 3908549B2

- Authority

- JP

- Japan

- Prior art keywords

- chip

- rfid tag

- base material

- antenna pattern

- recess

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L24/00—Arrangements for connecting or disconnecting semiconductor or solid-state bodies; Methods or apparatus related thereto

- H01L24/93—Batch processes

- H01L24/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/80—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected

- H01L2224/83—Methods for connecting semiconductor or other solid state bodies using means for bonding being attached to, or being formed on, the surface to be connected using a layer connector

- H01L2224/8319—Arrangement of the layer connectors prior to mounting

- H01L2224/83192—Arrangement of the layer connectors prior to mounting wherein the layer connectors are disposed only on another item or body to be connected to the semiconductor or solid-state body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/95053—Bonding environment

- H01L2224/95085—Bonding environment being a liquid, e.g. for fluidic self-assembly

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2224/00—Indexing scheme for arrangements for connecting or disconnecting semiconductor or solid-state bodies and methods related thereto as covered by H01L24/00

- H01L2224/93—Batch processes

- H01L2224/95—Batch processes at chip-level, i.e. with connecting carried out on a plurality of singulated devices, i.e. on diced chips

- H01L2224/9512—Aligning the plurality of semiconductor or solid-state bodies

- H01L2224/95136—Aligning the plurality of semiconductor or solid-state bodies involving guiding structures, e.g. shape matching, spacers or supporting members

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01005—Boron [B]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01006—Carbon [C]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01013—Aluminum [Al]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01029—Copper [Cu]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01033—Arsenic [As]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01047—Silver [Ag]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01049—Indium [In]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01051—Antimony [Sb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01072—Hafnium [Hf]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/01—Chemical elements

- H01L2924/01082—Lead [Pb]

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/10—Details of semiconductor or other solid state devices to be connected

- H01L2924/11—Device type

- H01L2924/14—Integrated circuits

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/1515—Shape

- H01L2924/15153—Shape the die mounting substrate comprising a recess for hosting the device

- H01L2924/15155—Shape the die mounting substrate comprising a recess for hosting the device the shape of the recess being other than a cuboid

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/15—Details of package parts other than the semiconductor or other solid state devices to be connected

- H01L2924/151—Die mounting substrate

- H01L2924/15165—Monolayer substrate

Landscapes

- Engineering & Computer Science (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Details Of Aerials (AREA)

- Support Of Aerials (AREA)

- Credit Cards Or The Like (AREA)

Description

【発明の属する技術分野】

本発明は、RFIDタグの製造方法に関し、さらに詳しくは、外形寸法の極めて小さなICチップを用いたRFIDタグの製造方法に関するものである。

【0002】

【従来技術】

従来、製品の入出庫、在庫、販売管理には、荷札、棚札、バーコードなどを用いて行われていた。近年、これに代わって、無線で情報が交信でき、かつ、記録できる情報量も大きなRFIDタグの使用が増加している。該RFIDタグは、RFID(Radio Frequency Identification)システムの媒体として、電波を用いて非接触で情報の交信ができるタグである。RFIDタグは、紙やプラスチック等の基材に設けたアンテナパターンとICチップからなり、該アンテナパターンとICチップに内蔵された容量素子とにより共振回路を形成し、該アンテナパターンを通じて無線でリーダライタと交信することができる。

【0003】

これらのRFIDタグの製造方法としては、従来、RFIDタグ基材にアンテナパターンを形成し、該アンテナパターンへICチップを電気的に接続している。該接続は、ICチップをロボットアーム、真空吸引、又は手作業で掴んで、アンテナパターンの所定部位へ移動し接続するか、静電結合型の場合には、ICチップを予めICチップ粘着ラベル化してラベラーで貼着する方法が知られている。

しかしながら、近年、小型化が進み、数mm角以下のICチップが使用されるようになり、機械掴みはもちろん、ピンセットによる手作業でも掴みにくく、アンテナパターンへの接続作業の効率が著しく低下するという欠点がある。

【0004】

【発明が解決しようとする課題】

そこで、本発明はこのような問題点を解消するためになされたものである。その目的は、外形寸法が極めて小さいICチップを用いても、効率良く製造できるRFIDタグの製造方法を提供することである。

【0005】

【課題を解決するための手段】

上記の課題を解決するために、請求項1の発明に係わるRFIDタグの製造方法は、(a)基材の一方の面の凹部の基底部となる部分へ接着層を印刷法で塗布する工程、(b)前記接着層を塗布した基材面に、ICチップを嵌合する複数の凹部を、雄型で加圧する加圧塑性加工法で形成する工程、(c)該それぞれの凹部内に各1個のICチップを嵌合させ、固定する工程、(d)前記ICチップが嵌合した基材を導電性インキを用いて印刷し、ICチップ及び基材面にアンテナパターンを形成すると同時に、ICチップとアンテナパターンとを電気的に接続する工程、を有するようにしたものである。

【0006】

【発明の実施の形態】

本発明の実施態様について、図を参照して説明する。

まず、本発明に用いるRFIDタグとは、RFID(Radio Frequency Identification)システムの媒体として、電波を用いて非接触で情報の交信ができるタグである。RFIDタグは、紙やプラスチック等の基材に設けたアンテナパターンとICチップからなり、該アンテナパターンとICチップに内蔵された容量素子とにより共振回路を形成している。該共振回路は、リーダライタから一定の周波数の呼出し電波を受信すると、メモリに記憶している情報を発信源であるリーダライタに送信して返す。このようにRFIDタグは、リーダライタと非接触で情報を交信することができる。

【0007】

尚、「RFIDタグ」には、「非接触ICタグ」、「非接触データキャリア」、「無線ICタグ」、「非接触IC」、「非接触ICラベル」、「トランスポンダ」等と、種々の名称で表現される場合もあるので、本発明においては、代表して「RFIDタグ」と表現し、前記のように表現されている名称のものも包含するものとする。

【0008】

RFIDタグが交信に使用する周波数は、UHF−SHF帯(850〜950MHzと、2.4〜5GHz)、HF帯(10〜15MHz)、LF−MF帯(100〜500KHz)がある。UHF−SHF帯やHF帯の周波数を用いる電磁誘導方式のRFIDタグでは、交信距離が長いが価格的に高い。本発明では、いずれのRFIDタグへも適用できる。該RFIDタグは、リーダライタからの呼出し電波に対応して、複数のRFIDタグが一斉に応答する場合にはデータのコリジョン(衝突)が生じるが、衝突を回避して特定のRFIDタグを順次交信する手法が適用できる。

【0009】

図1は、本発明の1実施例を示すRFIDタグの模式的な平面図である。

図2は、図1のAA断面図である。

RFIDタグ1は、基材11に設けられた凹部15へ、ICチップ21が嵌合され、該ICチップ21へアンテナパターン13が接続されている。ICチップ21は、基材11の凹部15へ接着層17で固定される。ICチップ21へアンテナパターン13の両端が電気的に接続されて、コイル状アンテナを形成する。該コイルは、図1では1回巻きを示しているが、複数回巻きでもよい。アンテナパターン13の両端は、それぞれの接続部23によりICチップ21の端子、バンプ、又はパッドへ接続される。本発明では、アンテナパターン13の形成を導電性インキを用いたスクリーン印刷で行うので、アンテナパターン13の形成とICチップ21への接続とが同一工程で行われ、工程が短縮できる。

【0010】

図3は、本発明の1実施例を示すRFIDタグの断面図である。

図3は、他の実施態様を示し、ICチップ21は、基材11の凹部15へ嵌合され、ICチップ21へアンテナパターン13を形成し、その両端が電気的に接続される。さらに該アンテナパターン13面へ保護層31を設けたもので、接着層17が要らない。保護層31により、ICチップがより強固に固定され、また、外力に対する傷、損傷を減ずることができ、耐久性が高まる。もちろん、接着層17を有する図2に図示する態様においても、保護層31を設ければより耐久性が高められる。

【0011】

図4は、本発明の1実施例を示すRFIDタグの平面図である。

図4のRFIDタグ1は静電結合型RFIDタグで、2枚の一対のアンテナパターン13A、13Bを有している。該アンテナパターン13A、13Bも、前述したように、基材11の凹部15へICチップ21を嵌合した後に、導電性インキを用いたスクリーン印刷で行えば良い。一対のアンテナパターン13A、13Bが、ICチップ21のそれぞれの端子を覆うように形成すると、アンテナパターン13A、13BとICチップ21とは静電結合されて電気的に接続されて、リーダライタと交信できる。この静電結合型RFIDタグでも、接着層17、及び保護層31を設けても良い。アンテナパターン13A、13Bの大きさは、リーダライタとの交信距離などに合わせて、適宜設定すれば良い。該アンテナパターンの送電性は、JIS、K6911による表面抵抗値で、106Ω/□以下が適用でき、好ましくは104Ω/□以下で、交信の信頼性を高められる。

【0012】

このようにRFIDタグ1は、ICチップ10に内蔵された容量素子とアンテナパターン13、又は一対のアンテナパターン13A、13Bとより共振回路を形成する。共振回路は、リーダライタから一定の周波数の呼出し電波を受信すると、同時にRFIDタグの駆動電力も受けて、ICチップ11のメモリに記憶されている情報を発信源であるリーダライタに送信して返す。

【0013】

基材の材料としては、絶縁性、機械的強度、スラリー液に溶解、膨潤しないものであれば、用途に応じて種々の材料が適用できる。例えば、ポリエチレンテレフタレ−ト・ポリブチレンテレフタレ−ト・ポリエチレンナフタレ−ト・ポリエチレンテレフタレート‐イソフタレート共重合体・テレフタル酸‐シクロヘキサンジメタノール‐エチレングリコール共重合体・ポリエチレンテレフタレート/ポリエチレンナフタレートの共押出フィルムなどのポリエステル系樹脂、ナイロン6・ナイロン66・ナイロン610などのポリアミド系樹脂、ポリエチレン・ポリプロピレン・ポリメチルペンテンなどのポリオレフィン系樹脂、ポリ塩化ビニルなどのビニル系樹脂、ポリアクリレート・ポリメタアクリレート・ポリメチルメタアクリレートなどのアクリル系樹脂、ポリイミド・ポリアミドイミド・ポリエーテルイミドなどのイミド系樹脂、ポリアリレ−ト・ポリスルホン・ポリエーテルスルホン・ポリフェニレンエ−テル・ポリフェニレンスルフィド(PPS)・ポリアラミド・ポリエーテルケトン・ポリエーテルニトリル・ポリエーテルエーテルケトン・ポリエーテルサルファイトなどのエンジニアリング樹脂、ポリカ−ボネ−ト、ポリスチレン・高衝撃ポリスチレン・AS樹脂・ABS樹脂などのスチレン系樹脂、セロファン・セルローストリアセテート・セルロースダイアセテート・ニトロセルロースなどのセルロース系フィルム、などがある。

【0014】

該基材は、これら樹脂の少なくとも1層からなるフィルム、シート、ボード状として使用する、これらの形状はフィルム、シート、ボードなどと呼ばれるが、本明細書ではフィルムと総称する。通常は、ポリエステル系樹脂、アクリル系樹脂、ABS樹脂のフィルム、ポリカ−ボネ−トが、絶縁性、機械的強度、価格面から好適に使用され、ポリエチレンテレフタレートが最適である。該基材は、これら樹脂を主成分とする共重合樹脂、または、混合体(アロイでを含む)、若しくは複数層からなる積層体であっても良い。該基材の厚さは、通常、5〜500μm程度が適用できるが、10〜250μmが好適である。これ以上の厚さでは、剛度が高く実使用で物品へ貼着する際に扱いずらく、これ以下では、機械的強度が不足する。該基材は、表面へ、コロナ放電処理、プラズマ処理、オゾン処理、フレーム処理、プライマー(アンカーコート、接着促進剤、易接着剤とも呼ばれる)塗布処理、予熱処理、除塵埃処理、蒸着処理、アルカリ処理、などの易接着処理を行ってもよい。該樹脂は、必要に応じて、充填剤、可塑剤、着色剤、帯電防止剤などの添加剤を加えても良い。

【0015】

次に、本発明のRFIDタグ1の製造方法について、詳細に説明する。

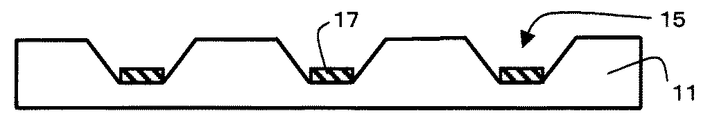

図5は、凹部を形成した基材の断面図である。

まず、基材11の一方の面に、少なくとも1つの凹部15を形成する。該凹部15は、図5(A)のような基材を掘り込んだ凹部でも、図5(B)のように基材全体を変形させて凹部15でも良い。図5(A)の凹部を形成方法としては、射出成形法、精密ザグリ法、凸状体によるプレス法などが適用できる。図5(B)の凹部を形成方法としては、真空成形法、圧空成形法、真空圧空併用成形法、プラグアシスト成形法、雄雌型による塑性成形法などが適用できる。

【0016】

図6は、凹部に接着層を形成した基材の断面図である。

基材11の凹部15の基底部に、接着層17を設けたもので、ICチップ21を固定する。該接着層17の接着剤としては、自身または環境物質と反応して接着する反応型接着剤、エネルギーの照射によって反応して接着するエネルギー照射型接着剤、加熱によって軟化または溶融して接着する熱接着型接着剤、加圧によって接着する粘着型型接着剤などが適用できる。反応型接着剤としては、反応型アクリル系、シアノアクリレート系等の化学反応型接着剤がある。エネルギー照射型接着剤としては、(メタ)アクリル系樹脂のUV硬化型接着剤、EB硬化型接着剤がある。熱接着型接着剤としては、ポリエチレン若しくはエチレンと(メタ)アクリル酸との共重合体などのオレフィン系、エチレン‐酢酸ビニル系共重合体、ポリアミド系、ポリエステル系、熱可塑性エラストマー系、反応ホットメルト系などのホットメルト系接着剤がある。粘着型接着剤としては、天然ゴム系、再生ゴム系、クロロプレンゴム系、ニトリルゴム系、スチレン・ブタジエンゴム系、熱可塑性エラストマー系などのエラストマー系接着剤がある。好ましくは、熱接着型、又は粘着型の接着剤である。熱接着型の場合は、ICチップ21を嵌合した後に、加熱して基材11と接着させれば良い。

【0017】

接着層17の形成は、通常、凹部15を形成した後に行うが、前でもよい。また、前述したように、接着層17は設けない場合もある。接着層17の形成を凹部15の形成前に行えるのは、図5(B)の基材全体を変形させる凹部15を形成する場合である。この場合の接着層17の形成は、上記の接着層用の樹脂を溶媒へ分散または溶解して、ロールコート、リバースロールコート、グラビアコート、グラビアリバースコート、コンマコート、バーコート、ワイヤーバーコート、ロッドコ−ト、キスコート、ナイフコート、ダイコート、フローコート、ディップコート、スプレーコートなどのコーティング方法で、基材11の凹部を形成する表面の全面へ塗布し、乾燥させる。又は、グラビア印刷、スクリーン印刷などの印刷法で、凹部の基底部となる部分へ塗布し、乾燥させる。接着層17の厚さは、通常は1〜30μm程度、好ましくは2〜20μmである。1μm以下の厚さでは、接着力が不足し、50μm以上の厚さでは、凹部から溢れ出してしまう。

【0018】

接着層17の形成を、凹部15を形成した後に行う場合は、上記の接着層用の樹脂を溶媒へ分散または溶解するか、そのまま、スクリーン印刷、タコ印刷、スプレーなどの方法で、基材11の凹部15の基底部へ塗布し、必要に応じて乾燥させれば良い。そして、ICチップ21を嵌合した後に加熱して、基材11と接着させる。

【0019】

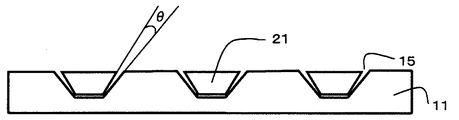

図7は、基材の凹部へICチップが嵌合した状態を示す断面図である。

ICチップ21は、複数の凹部15の中へ自己整列(セルフアライン)しながら、容易に嵌合して行く。このため、ICチップ21の側面と、これに対応するICチップ21を配置するための凹部15の側面との角度θは、0〜20°程度であり、好ましくは、0〜5°である。この態様においては、通常、ICチップ21は、台形ブロック又は截頭ピラミッド形状の構造で、基底から4つの側面が延びて大きい頂部面に達している。各側面と頂部面との角度は20〜90°程度であり、好ましくは約55°である。ICチップ21は、長さが5〜2000μm程度、幅が5〜2000μm程度であり、好ましくは長さが100〜1000μm程度、幅が100〜1000μm程度、さらに好ましくは長さが150〜500μm程度、幅が150〜500μmである。ICチップ21の高さは、長さ及び幅以下とすれば良い。

【0020】

ICチップ21の形状は、台形ブロック以外の形状でもよく、成形し形状を持たせたことにより、ICチップ21は流体を介して、基材11の表面を移動して対応する凹部15にセルフアラインし、挿入され、嵌合(嵌め込まれる)する。該形状は、台形ブロック以外でもよく、例えば、長方形、正方形、六角形、ピラミッド形、T形、腎臓形、等である。矩形のブロックは対応する凹部を持つ基材への挿入方向が最大4方向ある。これに対して、八角形のブロックは8方向で挿入できるし、円形のブロックは細い端部から挿入する限り全方位で挿入し、嵌合が可能である。このブロック形状は、望みの方位にセルフアラインし易い、幅、長さ、および高さがある。また、数種類の形状を混合物(溶液とICチップ21ブロック)中に存在させ、基材上にはこれらの種類に対応する大きさの複数の凹部を設けておけば、それぞれに対応する場所へ嵌合させることができる。このような形状のICチップ21は、トランスファー成形の型を台形ブロックとすれば、ガラスエポキシ樹脂などで封止する際に形成される。また、シリコン基板などのベアチップ状態から、エッチング、イオンミリング、溶解法で分離しても良い。

【0021】

基材11の凹部15の形状は、複数の凹部15の中へICチップ21が自己整列(セルフアライン)しながら容易に嵌合する形状とする。凹部の断面は、ICチップ21に対して、相補的な略台形である。凹部15の側面が、基底部に対する角度は、50〜70°程度である。

【0022】

次いで、ICチップ21の複数を流体に入れて、スラリーを形成する。液体は、水、アセトン、メチルアルコール、エチルアルコール、シリコーンオイルなどのICチップ及び基材への腐蝕などの影響の少ない液体であれば良い。必要に応じて、界面活性剤、粘度調整剤、着色剤などを適宜添加してもよい。

【0023】

そして、上記スラリーを基材11の凹部15上へ流下させて、ICチップ21の少なくとも1つが、基材11の凹部15内に、ICチップ21の個々のテーパ付き縁部で嵌合させる。

図8は、スラリーを基材上へ流下させる装置の模式的な断面図である。

図8の装置100は、受容槽103、導管109、及びポンプ105からなっている。装置100の全体はガラスで作られているが、スラリーに腐蝕されないその他の金属、アクリル板などの適当な材料でもよい。受容槽103は、凹部15を持つ基板11、が収容され、また、流体とICチップ21とが混合されたスラリーで満たされている。導管109は、基板11を収容している受容槽103と連結している。スラリーは、受容槽103の下部から、流入部113、導管109を経て、流出部115から、基板11上の凹部15へ流下して循環する。受容槽103の底部は漏斗状になっていて、基板11上の凹部15へ嵌合されなかったICチップ21を受容槽103の底部に降下させて再循環させるようになっている。

【0024】

ポンプ105はパイプで導管109の流入部113に連結され、流入部113へ気体を供給する。気体は空気、窒素、アルゴン、炭酸ガスなどが適用できる。ポンプ105で吹き込まれた気体は、導管109の流体中で気泡となる。流入部113に集まった流体の一部と、少なくとも1つのICチップ21が、気泡によって搬送されて、流出部115から受容槽103内へ循環する。ICチップ21は、気泡による搬送により損傷を受けることが少ない。流体としては水などの液体で説明してきたが、空気のような気体でもよく、特に比重の大きいものには好適である。また、乾燥する工程も省ける。

【0025】

図9は、スラリー中のICチップが凹部15内へ嵌合する概念図である。

スラリーは、流出部115から受容槽103内へ収納されている基材11上へ流下させる。スラリーが流れていると、スラリー中のICチップ21の少なくとも1つが、基材11の凹部15内に、ICチップ21の個々のテーパ付き縁部で嵌合させる。同様に次々と凹部15内へICチップ21が嵌合されて行く。凹部15へ嵌合されなかったICチップ21は、基材11上から流れ去り、再循環する。

【0026】

基材11はホルダー119に保持されており、該ホルダー119は凹部15内へのICチップ21の嵌合を促進するために、基材11を回転、振動、揺動、又は首振りさせる。ICチップ21は、流体と共に基材11上面を流下し搬送されながら凹部15に自己整列(セルフアライン)して沈み込み嵌合して行く。凹部15に嵌合しなかったICチップ21は再循環し嵌合されて、所定の充填率を達成する。基材11上をスラリーが均等に流下させるために、ホルダー119の動作に併せて、ブラシ、スクレーパ、ピンセット、ピック、ドクターブレード等の機械的手段を用いてもよい。該機械的手段は、スラリーを移動又は均一分布させ、また余分のスラリーを除去するために用いることができる。

【0027】

スラリーが基材11上を流下する速度は、0.01〜100mm/秒程度で、好ましくは1mm/秒程度である。これらの流速でICチップ21は流体と共に均一に流れ、基板11上を移動しながら凹部15内に自己整列して、沈降静止し嵌合する。流速が早過ぎると、自己整列しにくく、また嵌合済みのICチップ21を掻き乱してしまう。流体中のICチップ21の量は、ICチップ21の大きさや形状により適宜選択すればよく、通常、流体1lに対して10〜100000個程度、好ましくは100〜50000個である。また、凹部15内へのICチップ21の充填率を高めるために、流体中のICチップ21の量、スラリーの流下速度、流体の種類、基材の振動などの条件を選定すればよい。

【0028】

このようにすることで、最大辺が5〜2000μm程度の微細なICチップ21でも、機械的に効率よく嵌合し、RFIDタグを量産することができる。従来の微細部品を掴む方法では、最大辺が1000μm以下では機械化できても効率が悪く、特に最大辺が250μm以下では、掴むことさえ困難であった。

【0029】

次に、ICチップ21及び基材11面へアンテナパターンを形成する。

図10は、凹部へICチップが嵌合した基材の模式的な断面図である。

図11は、ICチップ及び基材へアンテナパターンを設けた模式的な断面図である。

図10は、基材11の凹部15へICチップ21が嵌合した状態である。該基材11とICチップ21上へ、アンテナパターン13Aと13B、又は13、を形成する。凹部15に熱接着型の接着剤が設けてある場合には、予め加熱して、ICチップ21を固定しておく。

【0030】

該アンテナパターンは、導電性インキを用いて所定のパターンを印刷する。導電性インキとしては、カーボン・黒鉛・アルミ粉・銀紛、あるいはそれらの混合体などをビヒクルに分散したインキが適用できる。また、透明な導電性材料として、有機溶剤に溶解したバインダー樹脂中に有機導電体である7,7,8,8,−テトラシアノキノジメタン錯体(TCNQ錯体)を溶解させたものや、酸化錫、アンチモンドープ酸化錫(ATO)、酸化インジウム、錫ドープ酸化インジウム(ITO)を分散したものなどが適用できる。

【0031】

該アンテナパターンの形成は、上記導電性インキを、公知のオフセット印刷・グラビア印刷・フレキソ印刷・スクリーン印刷などの印刷法が適用できる。該アンテナパターンは、図1に図示したコイル状、又は図4に図示した一対で2枚の所謂パッチアンテナ状とすればよい。図1では、コイル状のアンテナの両端部をICチップ21のそれぞれの端子、又はパッドへ重なるように形成すると、アンテナ形成と同時に、導電性を有するアンテナとICチップ21が電気的に接続される。従来のアンテナは、RFIDタグ基材にラミネートしたアルミ箔や銅箔などの金属箔を、フォトエッチングやレジスト印刷後のエッチングによりコイル状とし、その後ICチップと電気的接続を行っていた。アンテナの形成、電気的な接続を別々の2工程で、しかも複雑な装置で排水処理を伴うエッチング法であったが、本発明では、公知で容易な印刷による1工程でできる。

【0032】

一方、図4に図示した一対で2枚の所謂パッチアンテナ状は、静電結合型のRFIDタグのアンテナを形成する。図4のように、アンテナパターンの1部がICチップ21のそれぞれの端子部へ重なるように、導電性インキを用いて、図4のような一対で2枚のアンテナパターンを印刷すれば良い。導電性を有するアンテナとICチップ21が電気的に接続される。導電性インキ、及び印刷法は、コイルアンテナと同様でよい。

【0033】

図12は、本発明の1実施例を示すRFIDタグの断面図である。

図12は、必要に応じて保護層31を設けたものである。基材11の凹部15へ接着層17を設けない場合には必要であり、また、接着層17を設ける場合でもタグ表面に耐久性を要する用途には設ける。保護層31は、合成又は天然樹脂を溶媒へ分散又は溶解させて塗布し乾燥するか、合成又は天然樹脂フィルムを貼着すればよい。合成又は天然樹脂としては、ポリエステル系、ポリ塩化ビニル系、ポリウレタン系、繊維素系などでよく、これらを溶媒へ分散又は溶解させて塗布し乾燥する。該塗布方法はロールコート、スクリーン印刷などで、その乾燥後の塗布厚さは、2〜50μm程度でよい。合成又は天然樹脂フィルムとしては、ポリプロピレン、ポリ塩化ビニル、ポリエチレンテレフタレート、セルロース系などの5〜50μm程度のフィルムを、接着剤又は粘着剤を介して貼着すればよい。該合成又は天然樹脂フィルムは、例えば銘板ラベルとして用いているフィルムで兼用してもよい。

【0034】

基材11へ、図12のように複数のRFIDタグ1を設けている場合には、切断線33で個々に切断する。このように、基材11へ複数のRFIDタグ1を設けてもよく、さらに、基材11を連続的に巻き回した巻取方式では、量産効率がよくできる。

【0035】

このようにして、微細ICチップ21を用いた微細なRFIDタグ1が容易に製造でき、リーダライタの呼出し電波に呼応し、リーダライタと交信できる。該RFIDタグ1は、日用品、事務用品、電気製品、食料品、建築土木用品などのあらゆる製品に貼着又は内蔵されて、その情報や製品の管理に適用することができる。また、RFIDタグ1は、データを書き換えることができるので、出荷検査の結果のデータ、また、必要によって、試験検査表や製品取り扱い警告などを付加することもできる。配送に関する情報や、製品情報、数量などの情報を記載することで、配送後の製品管理をすることもできる。しかも、従来と比較して極めて小さいタグなので、上記の製品に貼着しても、貼着してあることさえ判らず、また、製品に内蔵させることもたやすく、セキュリティ上も好ましい。

【0036】

【実施例】

(実施例1)

基材として、厚さが1000μm、1辺の長さが50mmの正方形のアクリル板を用いた。該アクリル板表面の中央に、精密4軸ザグリ機で700μm×700μm、深さが500μmの断面が逆台形の凹部をザグリ法で形成した。凹部の基底部へ、アクリル系ホットメルトを加熱溶融して、デスペンサで0.03g塗布した。底辺が650μm角で高さが500μmの截頭ピラミッド形状のICチップを用いて、500個の該ICチップを水5lに入れてスラリーとした。次に、図8の装置を用いて、スラリーを流下してICチップを基材上の凹部へ嵌合させた後に、温度80℃で10分間保持して、水を乾燥するとともにICチップを固定させた。基材及びICチップ上へ、図1のようなコイル状アンテナパターンを、銀ペーストAF4808(東洋紡社製、商品名)で、アンテナ幅250μm、厚さ10μmになるようにスクリーン印刷し、温度100℃で5分間加熱した。アンテナパターンの外周線の長径は8mm、短径は2mmのコイル状であり、最後に外形10mm×5mmに切断してRFIDタグを得た。リーダライタへ近づけたところ、RFIDタグとリーダライタは問題なく、情報の交信をすることができた。

【0037】

(実施例2)

基材として、厚さが188μm、1辺の長さが150mmの正方形のテレフタル酸‐シクロヘキサンジメタノール‐エチレングリコール共重合体フィルムを用いた。該フィルム表面にメチルメタアクリレート30重量部をメチルエチルケトンとトルエンの等量混合溶媒70重量部からなる塗液をスピンコート法で乾燥後の厚さが2μmになるように塗布し乾燥した。該塗布面に、500μm×500μmで高さが90μmの台形の凸部を持つ雄型と、100μm×100μmで深さ100μmの逆台形の凹部を持つ雌型とで加圧し塑性加工法で形成して、500μm×500μmで深さが90μmの凹部を形成した。該凹部は縦横15mmピッチで縦9個×横9個の計81個を設けた。底辺が450μm×450μm、高さが90μmの截頭ピラミッド形状のICチップを用いて、150000個のICチップを水10lに入れてスラリーとした。次に、図8の装置を用いて、スラリーを5分間循環しながら流下してICチップを基材上の凹部へ嵌合させた後に、温度80℃で10分間保持して、水を乾燥するとともにICチップを固定させた。基材及びICチップ上へ、図1のようなコイル状アンテナパターンを、銀ペーストAF4808(東洋紡社製、商品名)で、アンテナ幅250μm、厚さ10μmになるようにスクリーン印刷し、温度100℃で5分間加熱した。アンテナパターンの外周線の長径は8mm、短径は2mmのコイル状であり、最後に、ICチップとアンテナパターンを含むように外形10mm×5mmに打抜いてRFIDタグを得た。リーダライタへ近づけたところ、RFIDタグとリーダライタは問題なく、情報の交信をすることができた。

【0038】

【発明の効果】

本発明のRFIDタグの製造方法によれば、外形寸法が極めて小さいICチップを用いても、効率良く、大量生産できる。また、微細なICチップをスラリー化し、また、該スラリーを循環して使用することで、微細なICチップ機械的に基材へ嵌合でき、かつ、ICチップの無駄がなく、さらに、アンテナパターンを形成すると同時にICチップと電気的に接続でき、少ない加工工程で、コストが低くできる。また、新たな種々の用途に適用できる可能性のある、極めて小さいRFIDタグがを、安価に大量に供給できる。

【図面の簡単な説明】

【図1】 本発明の1実施例を示すRFIDタグの模式的な平面図である。

【図2】 図1のAA断面図である。

【図3】 本発明の1実施例を示すRFIDタグの断面図である。

【図4】 本発明の1実施例を示すRFIDタグの平面図である。

【図5】 凹部を形成した基材の断面図である。

【図6】 凹部に接着層を形成した基材の断面図である。

【図7】 基材の凹部へICチップが嵌合した状態を示す断面図である。

【図8】 スラリーを基材上へ流下させる装置の模式的な断面図である。

【図9】 スラリー中のICチップが凹部15内へ嵌合する概念図である。

【図10】 凹部へICチップが嵌合した基材の模式的な断面図である。

【図11】 ICチップ及び基材へアンテナパターンを設けた模式的な断面図である。

【図12】 本発明の1実施例を示すRFIDタグの断面図である。

【符号の説明】

1 RFIDタグ

11 RFIDタグ基材

13、13A、13B アンテナ

15 凹部

17 接着剤

21 ICチップ

23 接続部

31 保護層

33 切断部

100 装置

103 受容槽

105 ポンプ

109 導管

113 流入部

115 流出部

119ホルダ

Claims (4)

- ICチップとそれに接続したアンテナパターンからなるRFIDタグの製造方法であって、(a)基材の一方の面の凹部の基底部となる部分へ接着層を印刷法で塗布する工程、(b)前記接着層を塗布した基材面に、ICチップを嵌合する複数の凹部を、雄型で加圧する加圧塑性加工法で形成する工程、(c)該それぞれの凹部内に各1個のICチップを嵌合させ、固定する工程、(d)前記ICチップが嵌合した基材を導電性インキを用いて印刷し、ICチップ及び基材面にアンテナパターンを形成すると同時に、ICチップとアンテナパターンとを電気的に接続する工程、を有することを特徴とするRFIDタグの製造方法。

- 導電性インキの印刷が、オフセット印刷・グラビア印刷・スクリーン印刷のいずれかであることを特徴とする請求項1記載のRFIDタグの製造方法。

- 導電性インキが、アルミ粉または銀粉をビヒクルに分散したインキであることを特徴とする請求項1または請求項2記載のRFIDタグの製造方法。

- 導電性インキにTCNQ錯体を含むことを特徴とする請求項1または請求項2記載のRFIDタグの製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002024295A JP3908549B2 (ja) | 2002-01-31 | 2002-01-31 | Rfidタグの製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2002024295A JP3908549B2 (ja) | 2002-01-31 | 2002-01-31 | Rfidタグの製造方法 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JP2003223626A JP2003223626A (ja) | 2003-08-08 |

| JP2003223626A5 JP2003223626A5 (ja) | 2005-08-11 |

| JP3908549B2 true JP3908549B2 (ja) | 2007-04-25 |

Family

ID=27746780

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2002024295A Expired - Fee Related JP3908549B2 (ja) | 2002-01-31 | 2002-01-31 | Rfidタグの製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP3908549B2 (ja) |

Families Citing this family (27)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6867983B2 (en) | 2002-08-07 | 2005-03-15 | Avery Dennison Corporation | Radio frequency identification device and method |

| WO2004055887A2 (en) * | 2002-12-18 | 2004-07-01 | Koninklijke Philips Electronics N.V. | Manipulation of micrometer-sized electronic objects with liquid droplets |

| US7224280B2 (en) | 2002-12-31 | 2007-05-29 | Avery Dennison Corporation | RFID device and method of forming |

| US6940408B2 (en) | 2002-12-31 | 2005-09-06 | Avery Dennison Corporation | RFID device and method of forming |

| US7930815B2 (en) | 2003-04-11 | 2011-04-26 | Avery Dennison Corporation | Conductive pattern and method of making |

| US20040200061A1 (en) | 2003-04-11 | 2004-10-14 | Coleman James P. | Conductive pattern and method of making |

| JP4504694B2 (ja) * | 2004-01-30 | 2010-07-14 | トッパン・フォームズ株式会社 | スレッドの製造方法及びicチップ入りシートの製造方法、並びにこれらによって製造されたスレッド及びicチップ入りシート |

| JP2006031336A (ja) | 2004-07-15 | 2006-02-02 | Fujitsu Ltd | Rfidタグの製造方法 |

| US7202790B2 (en) * | 2004-08-13 | 2007-04-10 | Sensormatic Electronics Corporation | Techniques for tuning an antenna to different operating frequencies |

| JP4653440B2 (ja) | 2004-08-13 | 2011-03-16 | 富士通株式会社 | Rfidタグおよびその製造方法 |

| JP4845461B2 (ja) * | 2004-09-14 | 2011-12-28 | 株式会社半導体エネルギー研究所 | 半導体装置及びその作製方法 |

| US8698262B2 (en) | 2004-09-14 | 2014-04-15 | Semiconductor Energy Laboratory Co., Ltd. | Wireless chip and manufacturing method of the same |

| US20070158804A1 (en) | 2006-01-10 | 2007-07-12 | Semiconductor Energy Laboratory Co., Ltd. | Semiconductor device, manufacturing method of semiconductor device, and RFID tag |

| JP5057767B2 (ja) * | 2006-01-10 | 2012-10-24 | 株式会社半導体エネルギー研究所 | 半導体装置の作製方法 |

| JP2007274379A (ja) * | 2006-03-31 | 2007-10-18 | Sumitomo Chemical Co Ltd | 無線タグ及びその製造方法 |

| JP2008041005A (ja) * | 2006-08-10 | 2008-02-21 | Hitachi Ltd | Rfidタグおよびその製造方法 |

| US8129494B2 (en) | 2006-12-26 | 2012-03-06 | Asahi Kasei E-Materials Corporation | Resin composition for printing plate |

| TWI423519B (zh) | 2007-09-04 | 2014-01-11 | Mitsubishi Electric Corp | Radio frequency identification tag |

| JP5466381B2 (ja) * | 2008-07-23 | 2014-04-09 | 株式会社沖データ | 媒体搬送装置、印刷媒体、画像形成装置、及び画像形成方法 |

| JP5114357B2 (ja) * | 2008-10-09 | 2013-01-09 | 株式会社日立製作所 | 無線icタグ |

| JP5284858B2 (ja) * | 2009-04-22 | 2013-09-11 | 富士通株式会社 | Rfidタグ |

| WO2011055171A1 (en) * | 2009-11-09 | 2011-05-12 | Time Reversal Communications | Device for receiving and / or emitting electromanetic waves |

| JP2014157180A (ja) * | 2013-02-14 | 2014-08-28 | Ricoh Co Ltd | Rfid粘着感熱ラベル |

| EP2767935A1 (fr) * | 2013-02-18 | 2014-08-20 | NagraID S.A. | Couche plastique pour carte électronique |

| GB2539839B8 (en) * | 2014-04-28 | 2021-07-07 | Murata Manufacturing Co | Wireless IC device, clip-shaped RFID tag, and article having RFID tag |

| JP7312355B2 (ja) * | 2019-03-27 | 2023-07-21 | 大日本印刷株式会社 | Icタグ、icタグの製造方法、及びic保持部の製造方法 |

| WO2021132058A1 (ja) * | 2019-12-23 | 2021-07-01 | 三井化学株式会社 | 電子タグ用接着剤および電子タグ |

-

2002

- 2002-01-31 JP JP2002024295A patent/JP3908549B2/ja not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| JP2003223626A (ja) | 2003-08-08 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3908549B2 (ja) | Rfidタグの製造方法 | |

| JP3998992B2 (ja) | ウェブに実装されたicチップへのアンテナパターン形成方法とicタグ付き包装体 | |

| JP3908514B2 (ja) | Icタグ付き包装体とicタグ付き包装体の製造方法 | |

| JP3894540B2 (ja) | 導電接続部を有するインターポーザ | |

| US7498947B2 (en) | Antenna circuit, IC inlet, multi tag, and method for producing multi tag | |

| JP2008123083A (ja) | 非接触icタグラベルと航空手荷物タグラベル、および非接触icタグラベルの製造方法 | |

| JP3854124B2 (ja) | 非接触式icラベル | |

| CA2705018C (en) | Rfid tags for pallets and cartons and system for attaching same | |

| JP2007042087A (ja) | Rfidタグ及びその製造方法 | |

| CN106845588B (zh) | 一种耐高温rfid轮胎电子标签及其制作方法 | |

| JP2012230469A (ja) | 非接触式icラベル | |

| CN105811085A (zh) | 柔性rfid天线及应用其的pos机装置、电子设备 | |

| JP3789827B2 (ja) | Icチップ実装方法とicチップ付き包装体およびicチップ付き包装体の製造方法 | |

| JPH11345299A (ja) | 非接触型icカード及びその製造方法 | |

| CN202632333U (zh) | 一种高频rfid易碎电子标签 | |

| JP2007076288A (ja) | 導電性パターン形成用金属箔シート | |

| CN111126541A (zh) | Rfid智能卡的构造及其制造方法 | |

| CN114065892A (zh) | 一种环保rfid标签及其制造方法 | |

| CN202632328U (zh) | 一种易碎防伪rfid蚀刻电子标签 | |

| JP2006318343A (ja) | 非接触icインレットの製造方法および製造装置 | |

| JP2004005260A (ja) | エレクトロルミネッセント表示部を有したicメディアおよびその製造方法 | |

| JP5375649B2 (ja) | 非接触icラベル | |

| CN207458098U (zh) | 电子标签及射频识别系统 | |

| CN105631506A (zh) | 防伪卷标的结构及其制造方法 | |

| CN110717571A (zh) | 一种防转移芯片及射频标签 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050117 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20050117 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20060726 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20060905 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20061023 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20070110 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20070118 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| LAPS | Cancellation because of no payment of annual fees |