JP3676904B2 - 半導体集積回路 - Google Patents

半導体集積回路 Download PDFInfo

- Publication number

- JP3676904B2 JP3676904B2 JP09359897A JP9359897A JP3676904B2 JP 3676904 B2 JP3676904 B2 JP 3676904B2 JP 09359897 A JP09359897 A JP 09359897A JP 9359897 A JP9359897 A JP 9359897A JP 3676904 B2 JP3676904 B2 JP 3676904B2

- Authority

- JP

- Japan

- Prior art keywords

- circuit

- voltage

- high voltage

- unit

- voltage drop

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 81

- 238000001514 detection method Methods 0.000 claims description 88

- 238000006243 chemical reaction Methods 0.000 claims description 15

- 238000010586 diagram Methods 0.000 description 18

- 230000000694 effects Effects 0.000 description 8

- 230000003321 amplification Effects 0.000 description 5

- 238000003199 nucleic acid amplification method Methods 0.000 description 5

- 238000000034 method Methods 0.000 description 2

- 235000002597 Solanum melongena Nutrition 0.000 description 1

- 244000061458 Solanum melongena Species 0.000 description 1

- 238000013500 data storage Methods 0.000 description 1

- 230000007613 environmental effect Effects 0.000 description 1

- 239000002784 hot electron Substances 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

- G11C5/147—Voltage reference generators, voltage or current regulators; Internally lowered supply levels; Compensation for voltage drops

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C5/00—Details of stores covered by group G11C11/00

- G11C5/14—Power supply arrangements, e.g. power down, chip selection or deselection, layout of wirings or power grids, or multiple supply levels

-

- G—PHYSICS

- G05—CONTROLLING; REGULATING

- G05F—SYSTEMS FOR REGULATING ELECTRIC OR MAGNETIC VARIABLES

- G05F3/00—Non-retroactive systems for regulating electric variables by using an uncontrolled element, or an uncontrolled combination of elements, such element or such combination having self-regulating properties

- G05F3/02—Regulating voltage or current

- G05F3/08—Regulating voltage or current wherein the variable is DC

- G05F3/10—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics

- G05F3/16—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices

- G05F3/20—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations

- G05F3/24—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations wherein the transistors are of the field-effect type only

- G05F3/242—Regulating voltage or current wherein the variable is DC using uncontrolled devices with non-linear characteristics being semiconductor devices using diode- transistor combinations wherein the transistors are of the field-effect type only with compensation for device parameters, e.g. channel width modulation, threshold voltage, processing, or external variations, e.g. temperature, loading, supply voltage

Landscapes

- Engineering & Computer Science (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Physics & Mathematics (AREA)

- General Physics & Mathematics (AREA)

- Electromagnetism (AREA)

- Nonlinear Science (AREA)

- Radar, Positioning & Navigation (AREA)

- Automation & Control Theory (AREA)

- Measurement Of Current Or Voltage (AREA)

- Dram (AREA)

- Semiconductor Integrated Circuits (AREA)

- Read Only Memory (AREA)

- Continuous-Control Power Sources That Use Transistors (AREA)

- Dc-Dc Converters (AREA)

Description

【発明の属する技術分野】

本発明は、半導体集積回路に関し、特に半導体集積回路の正又は負の高電圧を検出する高電圧検出回路に関する。

【0002】

【従来の技術】

電源電圧が印加されていなくとも記憶データを保持できるメモリとしてフラッシュメモリがあり、フラッシュメモリにおいては、データの記憶を行うメモリセル内のフローティングゲートに電荷を保持することで不揮発性の記憶を行っている。フラッシュメモリでは、電荷を保持するフローティングゲートに電荷を注入、又はフローティングゲートから電荷を引き抜いて“1”又は“0”のデータ記憶状態を作る。このとき、ファウラーノルドハイム(Fowler-Nordheim)トンネル現象や、チャネルホットエレクトロンを利用してフローティングゲートとの間で電荷のやり取りを行う。このような状態を発生させるためには、一般的にデバイスの動作電源電圧よりも高い電圧が必要となる。

【0003】

図8は、正の高電圧を検出する従来の高電圧検出回路の例を示した概略の回路図である。図8において、高電圧検出回路200は、カレントミラー型負荷の差動増幅回路201と、該差動増幅回路201を制御するnチャネル型MOSFET(以下、nMOSトランジスタと呼ぶ)202と、高電圧入力端子203から入力される正の高電圧Vhを分圧するための抵抗204及び205と、インバータ回路206とで形成されている。高電圧入力端子203は、抵抗204及び205を介して接地されており、差動増幅回路201の一方の入力端子には基準電圧発生回路207で生成され出力された基準電圧Vrefが入力され、他方の入力端子は、抵抗204及び205の接続部に接続されて高電圧入力端子203から入力された高電圧Vhを分圧した電圧Vdivが入力される。

【0004】

差動増幅回路201の出力はインバータ回路206の入力に接続され、インバータ回路206の出力は、高電圧検出回路200の出力をなし、チャージポンプ回路を備え正の高電圧Vhを出力する高電圧発生回路208の入力に接続されている。高電圧発生回路208の出力は、所定の回路(図示せず)に接続されると共に高電圧入力端子203に接続されている。また、nMOSトランジスタ202のゲートには2値の信号が入力され、nMOSトランジスタ202がオンすると差動増幅回路201は作動し、nMOSトランジスタ202がオフすると差動増幅回路201は動作を停止する。

【0005】

上記のような構成において、抵抗204及び抵抗205で分圧された分圧電圧Vdivは、

Vdiv=Vh×Rb/(Ra+Rb)

で表すことができる。なお、上記Raは抵抗204の抵抗値を、Rbは抵抗205の抵抗値を示している。

【0006】

差動増幅回路201は、分圧電圧Vdivと、基準電圧Vrefとの比較を行っており、Vdiv<Vrefのとき出力が「L」レベルとなり、インバータ回路206の出力が「H」レベルとなって、高電圧発生回路208は、チャージポンプ回路を作動させて高電圧Vhの昇圧を行う。一方、差動増幅回路201は、Vdiv>Vrefのとき出力が「H」レベルとなり、インバータ回路206の出力が「L」レベルとなって、高電圧発生回路208は、チャージポンプ回路の動作を停止させる。このように、高電圧検出回路200は、Vdiv=Vh×Rb/(Ra+Rb)>Vrefのとき、すなわち、Vh>Vref×(Ra+Rb)/Rbのとき、出力が「L」レベルとなり、高電圧VhがVref×(Ra+Rb)/Rb以下であるか否かを検出することができる。

【0007】

しかし、図8で示した高電圧検出回路200では、高電圧Vhを2つの抵抗204及び205で分圧するため、1つの分圧電圧Vdivの値しか検出することができず、種々の高電圧を検出することができなかった。そこで、図9で示すように、抵抗204を、n(nは自然数)個の抵抗R1〜Rnを直列に接続した直列回路に置き換え、各抵抗R1〜Rnには、ゲートサイズが十分に小さいnMOSトランジスタT1〜Tnがそれぞれ対応して並列に接続される。

【0008】

更に、各nMOSトランジスタT1〜Tnのゲートは、それぞれ制御回路211に接続され、制御回路211によって各nMOSトランジスタT1〜Tnのオンオフを制御することにより、抵抗R1〜Rnで形成された直列回路におけるトータルの抵抗値を変えるようにした。このようにすることにより、分圧電圧Vdivを制御回路211で制御することができ、種々の高電圧値を検出することができた。

【0009】

次に、負の高電圧を検出する従来の回路について説明する。図10は、負の高電圧を検出する従来の高電圧検出回路の例を示した概略の回路図である。図10において、高電圧検出回路220は、カレントミラー型負荷の差動増幅回路221、該差動増幅回路221を制御するnMOSトランジスタ222及びインバータ回路223からなる差動センスアンプ224と、pチャネル型MOSFET(以下、pMOSトランジスタと呼ぶ)225及び226からなるレベルコンバータ227と、nMOSトランジスタM1〜Mn,228,229とで形成されている。

【0010】

pMOSトランジスタ225,226及びnMOSトランジスタM1〜Mn,229は、それぞれソースとバックゲート端子とが接続されており、バックゲート効果によってそれぞれのしきい値Vthの変動を防止する。また、pMOSトランジスタ226及びnMOSトランジスタM1〜Mn,228,229は、それぞれダイオード接続されている。

【0011】

nMOSトランジスタM1〜Mn,228,229を直列に接続し、該直列回路は、負の高電圧Vlが入力される高電圧入力端子230と電源電圧Vddが入力される電源端子231との間に接続されている。nMOSトランジスタ228のゲートには基準電圧発生回路232で生成された基準電圧VrefAが入力され、nMOSトランジスタ228と電源端子231との間にnMOSトランジスタ229が接続されている。レベルコンバータ227を形成するpMOSトランジスタ225及び226は直列に接続されて、電源端子231と接地間に接続され、電源端子231側に接続されたpMOSトランジスタ225のゲートは、nMOSトランジスタ228及び229との接続部に接続されている。

【0012】

レベルコンバータ227におけるpMOSトランジスタ225及び226の接続部は、差動センスアンプ224における差動増幅回路221の一方の入力に接続され、他方の入力には基準電圧発生回路232で生成された基準電圧VrefBが入力されている。また、差動増幅回路221の出力はインバータ回路223の入力に接続され、インバータ回路223の出力は、高電圧検出回路220の出力をなし、チャージポンプ回路を備え負の高電圧Vlを出力する高電圧発生回路233の入力に接続されている。高電圧発生回路233の出力は、所定の回路(図示せず)に接続されると共に高電圧入力端子230に接続されている。また、nMOSトランジスタ222のゲートには2値の信号が入力され、nMOSトランジスタ222がオンすると差動増幅回路221は作動し、nMOSトランジスタ222がオフすると差動増幅回路221は動作を停止する。

【0013】

上記のような構成において、ダイオード接続されたnMOSトランジスタM1〜Mn、及びゲートに基準電圧VrefAが入力されるnMOSトランジスタ228で形成された直列回路は、基準電圧VrefAと負の高電圧Vlとの電圧差に応じて電流が流れる。該電流は、ダイオード接続されたnMOSトランジスタ229から流れ、nMOSトランジスタ229のソースとドレインとの間に電圧Vaが発生する。ここで、nMOSトランジスタM1〜Mn、228及び229は、各ゲートサイズがすべて同一であり、すべてオンしている場合、下記(1)式が成り立つ。

(VrefA−Vl)/(n+1)=Va ……………………(1)

【0014】

上記レベルコンバータ227は、入力された電圧Vaを接地電位から見た電圧Vaに変換し、差動増幅回路221は、レベルコンバータ227で変換された電圧Vaと、基準電圧VrefBとの比較を行う。すなわち、(VrefA−Vl)/(n+1)とVrefBとの比較を行うことになり、更に、Vlと{VrefA−(n+1)×VrefB}との比較を行うことになり、nに大きな整数値を使用することによって負の高電圧を検出することができる。

【0015】

【発明が解決しようとする課題】

しかし、図9で示した正の高電圧検出回路210では、分圧電圧Vdivを微調整できるようにするには抵抗R1〜Rnの段数を増やす必要があり、制御回路211の出力が増加して回路規模が大きくなると共に、チップの大きさが大きくなる要因である抵抗の数を増やすことからチップの大きさが大きくなり、これらのことから、コストが増加するという問題があった。また、図10で示した負の高電圧検出回路220では、回路を構成する素子数が多いことから、検出精度の低下を招くと共にコストが増加するという問題があった。更に、半導体集積回路において、消費電流の低減を図ることは常に課せられた課題である。

【0016】

本発明は、上記問題を解決するためになされたものであり、検出精度を向上させることができると共に、コストの低減及び消費電流の低減を図ることができる高電圧検出回路を備えた半導体集積回路を得ることを目的とする。

【0017】

なお、本発明の半導体集積回路と目的及び構成が異なるが、検出電圧と共に、VREFも調整して比較器に入力する、磁気記録再生装置におけるバッテリ電圧検出回路が、特開平5―164792号公報で開示されており、VREFをステップ的に切り替える内部電圧発生回路が、アメリカ特許第5283762号の明細書で開示されている。

【0018】

【課題を解決するための手段】

この発明に係る半導体集積回路は、高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、入力された高電圧を電圧降下させて出力する高電圧降下部と、複数の基準電圧を生成して出力する基準電圧発生部と、該基準電圧発生部から入力された複数の基準電圧を切り換えて出力する基準電圧切換部と、上記高電圧降下部から出力された電圧と上記基準電圧切換部から出力された基準電圧との比較を行って高電圧の検出を行う高電圧検出部と、上記高電圧降下部における高電圧の電圧降下を制御すると共に、基準電圧切換部による基準電圧の切換制御を行う制御部とを備えるものである。

【0019】

また、この発明に係る半導体集積回路は、請求項1において、上記高電圧降下部は、ダイオード接続された1つもしくは直列に接続された複数のMOSFETが上記高電圧降下部の入力と出力の間に接続され、高電圧の電圧降下を行う電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、電圧降下回路部を形成する各MOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路部とで形成され、上記制御部は、該各スイッチング回路部のスイッチング動作を制御して上記電圧降下回路部による電圧降下値を変えるものである。

【0020】

また、この発明に係る半導体集積回路は、請求項1において、上記高電圧降下部は、複数の抵抗を直列に接続して形成される、高電圧の電圧降下を行う電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、上記電圧降下回路部を形成する各抵抗にそれぞれ並列に接続された、スイッチング動作によって抵抗を短絡させる各スイッチング回路部とで形成され、上記制御部は、該各スイッチング回路部のスイッチング動作を制御して上記電圧降下回路部による電圧降下値を変えるものである。

【0021】

また、この発明に係る半導体集積回路は、高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、入力された高電圧を電圧降下させて出力する高電圧降下部と、基準電圧を生成して出力する基準電圧発生部と、高電圧降下部から出力された電圧と上記基準電圧発生部から出力された基準電圧との比較を行って高電圧の検出を行う高電圧検出部と、上記高電圧降下部における高電圧の電圧降下を制御する制御部とを備え、上記高電圧降下部は、所定の電圧の整数倍ごとに電圧降下を行う電圧降下部と、所定の電圧の整数倍未満の電圧降下を行う微調整部と、上記電圧降下部及び微調整部にそれぞれ電流を供給する電流源とからなり、上記制御部は、電圧降下部及び微調整部におけるそれぞれの電圧降下を制御するものである。

【0022】

また、この発明に係る半導体集積回路は、請求項4において、上記電圧降下部は、ダイオード接続された1つもしくは直列に接続された複数の第1のMOSFETが上記高電圧降下部の入力と出力の間に接続された電圧降下回路と、該電圧降下回路を形成する上記各第1のMOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路からなる第1スイッチング回路とからなり、上記制御部は、第1スイッチング回路におけるそれぞれのスイッチング回路のスイッチング動作を制御して高電圧の電圧降下を制御するものである。

【0023】

また、この発明に係る半導体集積回路は、請求項5において、上記微調整部は、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力される1つもしくは直列に接続された複数の第2のMOSFETを含み、上記電圧降下回路と直列に接続される微調整回路と、該微調整回路を形成する上記各第2のMOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路からなる第2スイッチング回路とからなり、上記制御部は、第2スイッチング回路におけるそれぞれのスイッチング回路のスイッチング動作を制御するものである。

【0024】

また、この発明に係る半導体集積回路は、請求項5において、上記微調整部は、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力される第2のMOSFETとスイッチング用の第3のMOSFETとが直列に接続された直列回路を1つもしくは複数並列に接続して形成される、上記電圧降下回路と直列に接続される微調整回路からなり、上記制御部は、上記スイッチング用の上記第3のMOSFETのスイッチング動作を制御するものである。

【0025】

また、この発明に係る半導体集積回路は、請求項5において、上記微調整部は、抵抗とスイッチング用の第2のMOSFETとが直列に接続された直列回路をゲート―ドレイン間及びゲート―ソース間にそれぞれ接続された第3のMOSFETからなる、上記電圧降下回路と直列に接続される微調整回路からなり、上記制御部は、上記スイッチング用の上記第2のMOSFETのスイッチング動作を制御するものである。

【0026】

また、この発明に係る半導体集積回路は、高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、第1基準電圧及び第2基準電圧を生成して出力する基準電圧発生部と、該第1基準電圧と上記高電圧との電圧差を電流に変換する電流変換部と、上記第2基準電圧に応じて一定の電流を生成して出力する定電流発生部と、上記電流変換部で変換された電流と、該定電流発生部から出力される定電流との電流差を電圧に変換する電圧変換部と、該電圧変換部で変換された電圧から高電圧値の検出を行う高電圧検出部とを備えるものである。

【0027】

また、この発明に係る半導体集積回路は、請求項9において、上記電圧変換部はカレントミラー回路で形成され、該カレントミラー回路は、電流変換部で変換された電流を定電流発生部の出力に入力し、上記高電圧検出部は、定電流発生部の出力における電圧から高電圧の検出を行うものである。

【0028】

また、この発明に係る半導体集積回路は、請求項10において、上記電流変換部は、ダイオード接続された1つもしくは直列に接続された複数のMOSFETを含む電圧レベル変換回路と、該電圧レベル変換回路の出力に接続されると共にゲートに第1基準電圧が入力され、電流変換部の出力をなすMOSFETとで形成され、上記電圧レベル変換回路の入力は負の高電圧が入力されるものである。

【0029】

また、この発明に係る半導体集積回路は、高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、ダイオード接続された1つもしくは直列に接続された複数の第1のMOSFETを含み、入力が接地される第1電圧降下回路部と、ダイオード接続された1つもしくは直列に接続された複数の第2のMOSFETを含み、入力に負の高電圧が印加される第2電圧降下回路部と、所定の基準電圧を生成して出力する基準電圧発生部と、該第1電圧降下回路部の出力が上記所定の基準電圧になるように一定の電流を生成すると共に、上記第1及び第2電圧降下回路部にそれぞれ電流を供給する定電流発生部と、上記第1電圧降下回路部の出力電圧と第2電圧降下回路部の出力電圧とを比較して高電圧値を検出する高電圧検出部とを備えるものである。

【0030】

【発明の実施の形態】

次に、図面に示す実施の形態に基づいて、本発明を詳細に説明する。

実施の形態1.

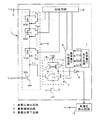

図1は、本発明の実施の形態1における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。なお、図1は、正の高電圧を検出する高電圧検出回路を示している。

【0031】

図1において、高電圧検出回路1は、カレントミラー型負荷の差動増幅回路2と、該差動増幅回路2を制御するnチャネル型MOSFET(以下、nMOSトランジスタと呼ぶ)3と、差動増幅回路2の出力信号の信号レベルを反転するインバータ回路4と、高電圧入力端子5から入力される正の高電圧Vhを電圧降下させて降下電圧Vdを出力する高電圧降下回路6と、複数の基準電圧、ここでは、例えばVr1〜Vr4の4種類の電圧の基準電圧を生成して出力する基準電圧発生回路7と、基準電圧発生回路7から入力される各基準電圧Vr1〜Vr4のいずれか1つを差動増幅回路2に出力する基準電圧切換回路8と、高電圧降下回路6に対して降下電圧Vdの可変制御を行うと共に、基準電圧切換回路8を制御する制御回路9とからなる。

【0032】

差動増幅回路2は、pチャネル型MOSFET(以下、pMOSトランジスタと呼ぶ)11,12及びnMOSトランジスタ13,14で形成されており、pMOSトランジスタ11及び12でカレントミラー回路を形成しており、pMOSトランジスタ11及び12の各ソースは、電源電圧Vddが入力される電源端子15にそれぞれ接続されている。pMOSトランジスタ11及び12の各ゲートは互いに接続され、該接続部はpMOSトランジスタ11のドレインに接続されている。

【0033】

pMOSトランジスタ11のドレインはnMOSトランジスタ13のドレインに接続され、pMOSトランジスタ12のドレインはnMOSトランジスタ14のドレインに接続され、該接続部は差動増幅回路2の出力をなし、インバータ回路4の入力に接続されている。インバータ回路4の出力は、高電圧検出回路1の出力をなし、チャージポンプ回路を備え正の高電圧Vhを出力する高電圧発生回路16の入力に接続されている。高電圧発生回路16の出力は、所定の回路(図示せず)に接続されると共に高電圧入力端子5に接続されている。

【0034】

また、nMOSトランジスタ13及び14の各ソースは接続され、該接続部はnMOSトランジスタ3のドレインに接続され、nMOSトランジスタ3のソースは接地されている。nMOSトランジスタ3のゲートには2値の信号が入力され、nMOSトランジスタ3がオンすると差動増幅回路2は作動し、nMOSトランジスタ3がオフすると差動増幅回路2は動作を停止する。nMOSトランジスタ13のゲートは、高電圧降下回路6の出力に接続されて降下電圧Vdが入力される。nMOSトランジスタ14のゲートは、基準電圧切換回路8の出力に接続されている。基準電圧切換回路8は、基準電圧発生回路7に接続されて、各基準電圧Vr1〜Vr4がそれぞれ入力され、更に制御回路9に接続されている。

【0035】

高電圧降下回路6は、n個のnMOSトランジスタMa1〜Man及びnMOSトランジスタMbで形成されている。ダイオード接続されたnMOSトランジスタMa1〜Manは直列に接続されており、nMOSトランジスタMa1のドレインは高電圧入力端子5に接続され、nMOSトランジスタManのソースはnMOSトランジスタMbのドレインに接続され、該接続部は差動増幅回路2のnMOSトランジスタ13のゲートに接続されている。また、nMOSトランジスタMbのソースは接地され、ゲートには、所定の電圧Vcsが入力される。

【0036】

更に、nMOSトランジスタMa1〜Manには、ゲート長を十分に短くするか又はゲート幅を十分に広くした、オン抵抗が十分に小さいnMOSトランジスタTa1〜Tanがそれぞれ対応して並列に接続され、nMOSトランジスタTa1〜Tanの各ゲートは、それぞれ制御回路9に接続されている。なお、nMOSトランジスタMa1〜Manは、それぞれソースとバックゲート端子とが接続されており、バックゲート効果によってそれぞれのしきい値Vthの変動を防止する。また、nMOSトランジスタMa1〜Man,Mbは、各ゲートサイズがそれぞれ同一であり、飽和領域でそれぞれ動作する。なお、差動増幅回路2、nMOSトランジスタ3及びインバータ回路4は高電圧検出部を、高電圧降下回路6は高電圧降下部を、基準電圧発生回路7は基準電圧発生部を、基準電圧切換回路8は基準電圧切換部を、制御回路9は制御部をなす。

【0037】

上記のような構成において、nMOSトランジスタMbは電流源をなしており、制御回路9が、nMOSトランジスタTa1〜Tanをすべてオフさせている場合、nMOSトランジスタMbのゲートに所定の電圧Vcsが入力されると、nMOSトランジスタMa1〜Manの直列回路に電流が流れ、各nMOSトランジスタMa1〜Manのドレイン―ソース間には、電圧Vcsの電圧降下がそれぞれ発生し、高電圧降下回路6の出力電圧である降下電圧Vdは、下記(2)式のようになる。

Vd=Vh−n×Vcs …………………(2)

【0038】

ここで、制御回路9は、n個のnMOSトランジスタTa1〜Tanの内、K個をオフさせたとすると、高電圧検出回路1で検出される高電圧Vhは、下記(3)式のようになる。

Vh=Vref+K×Vcs …………………(3)

なお、Kは0〜nの整数である。

【0039】

制御回路9は、基準電圧切換回路8を制御することにより、基準電圧発生回路7で生成された複数の基準電圧Vr1〜Vr4のいずれかを選択して差動増幅回路2の基準電圧Vrefとして出力させる。差動増幅回路2は、nMOSトランジスタ3がオンすることによって作動し、高電圧降下回路6から入力される降下電圧Vd、及び基準電圧切換部8から入力される基準電圧Vrefに対して差動増幅を行う。

【0040】

例えば、降下電圧Vdが基準電圧Vrefよりも小さい場合、インバータ回路4の入力は「L」レベルとなり、高電圧発生回路16には「H」レベルの信号が入力されることから、高電圧発生回路16は、チャージポンプ回路を作動させて高電圧Vhを上昇させる。次に、降下電圧Vdが基準電圧Vref以上になると、インバータ回路4の入力は「H」レベルとなり、高電圧発生回路16には「L」レベルの信号が入力されることから、高電圧発生回路16は、チャージポンプ回路の作動を停止させる。

【0041】

これらのことから、制御回路9は、nMOSトランジスタTa1〜Tanの内、オンさせたnMOSトランジスタの数Kを変えることにより、降下電圧Vdを変えると共に、基準電圧切換回路8を制御して、差動増幅回路2に入力される基準電圧Vrefを変えることによって、高電圧検出回路1で検出することができる高電圧Vh値の微調整を行う。

【0042】

上記のように、本発明の実施の形態1における半導体集積回路は、高電圧降下回路6から差動増幅回路2に入力される降下電圧Vdを変えることができ、更に差動増幅回路2に入力される基準電圧Vrefを変えることができることから、検出することができる高電圧Vhの値の微調整を行うことができる。更に、高電圧降下回路6に抵抗を使用せず、nMOSトランジスタで形成したことから、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0043】

なお、本実施の形態1においては、高電圧降下回路6にダイオード接続したnMOSトランジスタを使用したが、該nMOSトランジスタの代わりにダイオード接続したpMOSトランジスタを使用してもよく、同様の効果を得ることができる。また、高電圧降下回路6に使用したnMOSトランジスタMa1〜Manの代わりに抵抗を使用してもよく、この場合、従来の回路よりも抵抗の数を削減することができると共に、配線数の削減を行うことができる。

【0044】

実施の形態2.

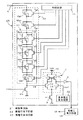

図2は、本発明の実施の形態2における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。なお、図2は、正の高電圧を検出する高電圧検出回路を示している。また、図2では、図1と同じものは同じ符号で示しており、ここではその説明を省略すると共に、図1との相違点のみ説明する。

図2における図1との相違点は、図1の基準電圧切換部8をなくし、図1の高電圧降下回路6内に降下電圧Vdの微調整を行う微調整回路21を設けたことと、基準電圧発生回路7を所定の1つの基準電圧を生成して出力するようにしたことから、図1の高電圧降下回路6を高電圧降下回路22とし、図1の基準電圧発生回路7を基準電圧発生回路23とし、図1の制御回路9は、微調整回路21の制御をも行うことから、制御回路24とし、これらに伴って、図1の高電圧検出回路1を高電圧検出回路25としたことにある。

【0045】

図2において、高電圧検出回路25は、差動増幅回路2と、該差動増幅回路2を制御するnMOSトランジスタ3と、差動増幅回路2の出力信号の信号レベルを反転するインバータ回路4と、高電圧入力端子5から入力される正の高電圧Vhを電圧降下させて降下電圧Vdを出力する高電圧降下回路22と、所定の基準電圧Vrefを生成して出力する基準電圧発生回路23と、高電圧降下回路22に対して降下電圧Vdの可変制御を行う制御回路24とからなる。差動増幅回路2のnMOSトランジスタ14のゲートは、基準電圧発生回路23に接続されており、所定の基準電圧Vrefが入力される。

【0046】

高電圧降下回路22は、n個のnMOSトランジスタMa1〜Man、nMOSトランジスタMb及び微調整回路21で形成されている。更に、微調整回路21は、nMOSトランジスタMd1〜Md4,Td1〜Td4、抵抗Rd1〜Rd3及び3つの抵抗Rd4で形成されている。ダイオード接続されたnMOSトランジスタMd1のソースは、nMOSトランジスタMbのドレインに接続され、該接続部は差動増幅回路2のnMOSトランジスタ13のゲートに接続されている。

【0047】

また、nMOSトランジスタMd1のドレインはnMOSトランジスタMd2のソースに接続され、同様に、nMOSトランジスタMd2のドレインはnMOSトランジスタMd3のソースに、nMOSトランジスタMd3のドレインはnMOSトランジスタMd4のソースにそれぞれ接続されている。nMOSトランジスタMd4のドレインは、nMOSトランジスタManのソースに接続されている。

【0048】

更に、nMOSトランジスタMd1〜Mdnには、nMOSトランジスタTa1〜Tanと同様に、ゲート長を十分に短くするか又はゲート幅を十分に広くした、オン抵抗が十分に小さいnMOSトランジスタTd1〜Td4がそれぞれ対応して並列に接続され、nMOSトランジスタTd1〜Td4の各ゲートは、それぞれ制御回路24に接続されている。なお、nMOSトランジスタMd1〜Md4は、nMOSトランジスタMa1〜Man,Mbとゲートサイズが同一であり、それぞれ飽和領域で動作すると共に、それぞれソースとバックゲート端子とが接続されており、バックゲート効果によってそれぞれのしきい値Vthの変動を防止する。

【0049】

nMOSトランジスタMd2は、ゲート―ソース間に抵抗Rd4が接続され、ゲート―ドレイン間に抵抗Rd1が接続されている。nMOSトランジスタMd3は、ゲート―ソース間に抵抗Rd4が接続され、ゲート―ドレイン間に抵抗Rd2が接続されている。また、nMOSトランジスタMd4は、ゲート―ソース間に抵抗Rd4が接続され、ゲート―ドレイン間に抵抗Rd3が接続されている。ここで、抵抗Rd1の抵抗値をrとすると、抵抗Rd2の抵抗値は2r、抵抗Rd3の抵抗値は3r、抵抗Rd4の抵抗値は4rとなる。なお、微調整回路21は微調整部を、高電圧降下回路22は高電圧降下部を、基準電圧発生回路23は基準電圧発生部を、nMOSトランジスタMa1〜Man及びTa1〜Tanは電圧降下部をなす。

【0050】

上記のような構成において、制御回路24が、nMOSトランジスタTa1〜Tanをすべてオンさせると共に、微調整回路21のnMOSトランジスタTd1〜Td3をオンさせ、nMOSトランジスタTd4のみオフさせた場合、nMOSトランジスタMbのゲートに所定の電圧Vcsが入力されると、nMOSトランジスタMa1〜Manの直列回路、及びnMOSトランジスタMd4,Td3,Td2,Td1の直列回路に電流が流れる。このことから、各nMOSトランジスタMa1〜Manのドレイン―ソース間には、電圧Vcsの電圧降下がそれぞれ発生する。

【0051】

更に、nMOSトランジスタMd4のゲート―ソース間には、電圧Vcsの電圧降下が発生し、nMOSトランジスタMd4のドレイン―ソース間の電圧降下Vd4、すなわち、微調整回路21における電圧降下は、下記(4)式のようになる。

Vd4=(7/4)×Vcs =1.75×Vcs …………………(4)

【0052】

同様に、nMOSトランジスタTd1,Td2,Td4がオンし、nMOSトランジスタTd3がオフした場合、微調整回路21における電圧降下は1.5×Vcsとなり、nMOSトランジスタTd1,Td3,Td4がオンし、nMOSトランジスタTd2がオフした場合、微調整回路21の電圧降下は1.25×Vcsとなる。更に、nMOSトランジスタTd2〜Td4がオンし、nMOSトランジスタTd1がオフした場合、微調整回路21における電圧降下はVcsとなる。なお、各抵抗Rd1〜Rd4に流れる電流が、電流源をなすnMOSトランジスタMbがオンしたときに高電圧降下回路22に流れる電流よりも十分に小さくなるように、各抵抗Rd1〜Rd4の各抵抗値が設定されている。

【0053】

このように、微調整回路21では、nMOSトランジスタMa1〜Manのそれぞれの電圧降下に対して、nMOSトランジスタMd4では1.75倍の電圧降下を、nMOSトランジスタMd3では1.5倍の電圧降下を、nMOSトランジスタMd2では1.25倍の電圧降下を、nMOSトランジスタMd1では同じ電圧降下を得ることができる。このことから、制御回路24は、nMOSトランジスタTa1〜Tanの中からオンさせるnMOSトランジスタの数を選択すると共に、nMOSトランジスタTd1〜Td4のオンオフを制御することによって、降下電圧Vdを変え、高電圧検出回路25で検出することができる高電圧Vh値の微調整を行う。

【0054】

図3は、図2で示した微調整回路21の他の例を用いた高電圧検出回路を示す概略の回路図である。なお、図3では、図2と同じものは同じ符号で示しており、ここではその説明を省略すると共に図2との相違点のみ説明する。

図3における図2との相違点は、図2の微調整回路21の回路構成を変えたことにあり、このことから、図2の微調整回路21を微調整回路31とし、これに伴って、図2の高電圧降下回路22を高電圧降下回路32とし、図2の高電圧検出回路25を高電圧検出回路35としたことにある。

【0055】

図3において、高電圧検出回路35は、差動増幅回路2と、nMOSトランジスタ3と、インバータ回路4と、高電圧入力端子5から入力される正の高電圧Vhを電圧降下させて降下電圧Vdを出力する高電圧降下回路32と、基準電圧発生回路23と、高電圧降下回路32に対して降下電圧Vdの可変制御を行う制御回路24とからなる。なお、微調整回路31は微調整部を、高電圧降下回路32は高電圧降下部をなす。

【0056】

高電圧降下回路32は、n個のnMOSトランジスタMa1〜Man、nMOSトランジスタMb及び微調整回路31で形成されている。更に、微調整回路31は、nMOSトランジスタMd1〜Md4,Td1〜Td4、抵抗Rd1〜Rd3及び3つの抵抗Rd4で形成されている。ダイオード接続されたnMOSトランジスタMd1のドレインは、nMOSトランジスタTd1のソースに接続されている。nMOSトランジスタMd2は、ドレインがnMOSトランジスタTd2のソースに接続され、ゲート―ソース間には抵抗Rd4が、ゲート―ドレイン間には抵抗Rd1が接続されている。

【0057】

同様に、nMOSトランジスタMd3は、ドレインがnMOSトランジスタTd3のソースに接続され、ゲート―ソース間には抵抗Rd4が、ゲート―ドレイン間には抵抗Rd2が接続されている。nMOSトランジスタMd4は、ドレインがnMOSトランジスタTd4のソースに接続され、ゲート―ソース間には抵抗Rd4が、ゲート―ドレイン間には抵抗Rd3が接続されている。

【0058】

nMOSトランジスタTd1〜Td4は、各ドレインがnMOSトランジスタManのソースにそれぞれ接続され、各ゲートが制御回路24に接続されている。nMOSトランジスタMd1〜Md4の各ソースは、nMOSトランジスタMbのドレインにそれぞれ接続されており、該接続部は、差動増幅回路2のnMOSトランジスタ13のゲートに接続されている。

【0059】

上記のような構成において、制御回路24は、nMOSトランジスタTa1〜Tanの内、所望の数だけオンさせると共に、nMOSトランジスタTd1〜Td4のいずれかをオンさせることにより、降下電圧Vdを変え、高電圧検出回路25で検出することができる高電圧Vh値の微調整を行う。

【0060】

図4は、図2で示した微調整回路21の他の例を用いた高電圧検出回路を示す概略の回路図である。なお、図4では、図2と同じものは同じ符号で示しており、ここではその説明を省略すると共に図2との相違点のみ説明する。

図4における図2との相違点は、図2の微調整回路21の回路構成を変えたことにあり、このことから、図2の微調整回路21を微調整回路41とし、これに伴って、図2の高電圧降下回路22を高電圧降下回路42とし、図2の高電圧検出回路25を高電圧検出回路45としたことにある。

【0061】

図4において、高電圧検出回路45は、差動増幅回路2と、nMOSトランジスタ3と、インバータ回路4と、高電圧入力端子5から入力される正の高電圧Vhを電圧降下させて降下電圧Vdを出力する高電圧降下回路42と、基準電圧発生回路23と、高電圧降下回路42に対して降下電圧Vdの可変制御を行う制御回路24とからなる。なお、微調整回路41は微調整部を、高電圧降下回路42は高電圧降下部をなす。

【0062】

高電圧降下回路42は、n個のnMOSトランジスタMa1〜Man、nMOSトランジスタMb及び微調整回路41で形成されている。更に、微調整回路41は、nMOSトランジスタMd1,Td1〜Td4及び抵抗Rd1〜Rd4で形成されている。nMOSトランジスタMd1,Td1〜Td4の各ドレインは接続されて、nMOSトランジスタManのソースに接続されている。nMOSトランジスタTd2のソースは抵抗Rd1を介して、nMOSトランジスタTd3のソースは抵抗Rd2を介して、nMOSトランジスタTd4のソースは抵抗Rd3を介してnMOSトランジスタMd1のゲートにそれぞれ接続されている。

【0063】

更に、nMOSトランジスタTd1のドレインは抵抗Rd4を介してnMOSトランジスタMd1に接続されている。nMOSトランジスタMd1及びTd1の各ソースは接続され、該接続部はnMOSトランジスタMbのドレインに接続されている。また、nMOSトランジスタTd1〜Td4の各ゲートはそれぞれ制御回路24に接続されている。

【0064】

上記のような構成において、制御回路24は、nMOSトランジスタTa1〜Tanの内、所望の数だけオンさせると共に、nMOSトランジスタTd1〜Td4のオン―オフを制御することにより、降下電圧Vdを変え、高電圧検出回路45で検出することができる高電圧Vh値の微調整を行う。例えば、制御回路24は、nMOSトランジスタTd2〜Td4の少なくとも1つをオンさせると共にnMOSトランジスタTd1をオフさせることにより、微調整回路41でnMOSトランジスタMa1〜Manのそれぞれの電圧降下と同じ電圧降下を得ることができる。また、制御回路24は、nMOSトランジスタTd1及びTd2をオンさせると共にnMOSトランジスタTd3及びTd4をオフさせることによって、微調整回路41でnMOSトランジスタMa1〜Manのそれぞれの電圧降下の1.25倍の電圧降下を得ることができる。

【0065】

更に、制御回路24は、nMOSトランジスタTd1及びTd3をオンさせると共にnMOSトランジスタTd2及びTd4をオフさせることによって、微調整回路41でnMOSトランジスタMa1〜Manのそれぞれの電圧降下の1.5倍の電圧降下を、nMOSトランジスタTd1及びTd4をオンさせると共にnMOSトランジスタTd2及びTd3をオフさせることによって、微調整回路41でnMOSトランジスタMa1〜Manのそれぞれの電圧降下の1.75倍の電圧降下を得ることができる。

【0066】

一方、図2から図4においては、抵抗による分圧回路でゲート電位を制御したが、この場合、各抵抗に流れる電流を電流源の電流よりも十分に小さくする必要があり、すなわち、各抵抗の抵抗値を大きくする必要がある。しかし、CMOSプロセスでは大きな抵抗値の抵抗を形成することは困難であり、高い抵抗値を得るためには長抵抗配線を使用しなければならず、チップ面積が増大するという問題がある。そこで、各抵抗の代わりに図5で示すようなデプリーション(depletion)型MOSFETを使用してもよい。しきい値電圧が負のデプリーション型を作ることはCMOSプロセスでは容易である。

【0067】

なお、実施の形態2の説明における、抵抗Rd1〜Rd4の各抵抗値は一例であり、これに限定するものではない。また、微調整回路21のnMOSトランジスタMd2〜Md4の各ドレイン―ソース間に接続された抵抗による分圧回路の分圧比においても、一例でありこれに限定するものではない。

【0068】

上記のように、本発明の実施の形態2における半導体集積回路は、高電圧降下回路から差動増幅回路2に入力される降下電圧Vdをきめ細かく変えることができることから、検出することができる高電圧Vhの値の微調整を行うことができる。更に、高電圧降下回路に使用する抵抗の数を減少させることができ、減少させた抵抗の代わりにnMOSトランジスタで形成したことから、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0069】

実施の形態3.

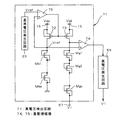

図6は、本発明の実施の形態3における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。なお、図6は、負の高電圧を検出する高電圧検出回路を示している。また、図6では、図1と同じものは同じ符号で示しており、ここではその説明を省略する。

【0070】

図6において、高電圧検出回路51は、nMOSトランジスタMf1〜Mfn,52,53、pMOSトランジスタ54,55、インバータ回路56及び基準電圧発生回路57で形成されている。ダイオード接続されたnMOSトランジスタMf1〜Mfnは直列に接続されており、nMOSトランジスタMf1のドレインはnMOSトランジスタ52のソースに接続され、nMOSトランジスタMfnのソースは、負の高電圧Vlが入力される高電圧入力端子58に接続されている。

【0071】

pMOSトランジスタ54及び55は、カレントミラー回路を形成しており、pMOSトランジスタ54及び55の各ゲートは接続され、該接続部はpMOSトランジスタ54のドレインに接続されている。pMOSトランジスタ54及び55の各ソースはそれぞれ電源端子15に接続され、pMOSトランジスタ54のドレインはnMOSトランジスタ52のドレインに接続されている。pMOSトランジスタ55のドレインはnMOSトランジスタ53のドレインに接続され、該接続部はインバータ回路56の入力に接続され、nMOSトランジスタ53のソースは接地されている。

【0072】

インバータ回路56の出力は、高電圧検出回路51の出力をなし、チャージポンプ回路を備え負の高電圧Vlを出力する高電圧発生回路59の入力に接続されている。高電圧発生回路59の出力は、所定の回路(図示せず)に接続されると共に高電圧入力端子58に接続されている。また、nMOSトランジスタ52のゲートには、基準電圧発生回路57から基準電圧Vref1が入力され、pMOSトランジスタ53のゲートには、同じく基準電圧発生回路57から基準電圧Vref2が入力されており、pMOSトランジスタ53は定電流発生回路をなしている。

【0073】

なお、nMOSトランジスタMf1〜Mfn,52,53及びpMOSトランジスタ54,55は、それぞれソースとバックゲート端子とが接続されており、バックゲート効果によってそれぞれのしきい値Vthの変動を防止する。nMOSトランジスタMf1〜Mfn,52,53は、各ゲートサイズがそれぞれ同一であり、飽和領域でそれぞれ動作する。また、nMOSトランジスタ52,Mf1〜Mfn及びpMOSトランジスタ54は電流変換部を、nMOSトランジスタ53は定電流発生部を、pMOSトランジスタ54及び55は電圧変換部を、インバータ回路56は高電圧検出部を、基準電圧発生回路57は基準電圧発生部をなす。更に、基準電圧Vref1は第1基準電圧を、基準電圧Vref2は第2基準電圧をなす。

【0074】

上記のような構成において、定電流発生回路をなすnMOSトランジスタ53のドレインに流れる電流Irefは、下記(5)式のようになる。

Iref=(Kp/2)×(W/L)×(Vref2−Vth)2 ………………(5)

なお、(5)式において、Wはゲート幅であり、Lはゲート長であり、KpはKp=μ×Coxで表すことができる。この場合、μは移動度であり、Coxはゲート酸化膜容量である。

【0075】

pMOSトランジスタ54及び55で形成したカレントミラー回路により、nMOSトランジスタMf1〜Mfn及び52の直列回路に流れる電流IaがnMOSトランジスタ53のドレインに流入する。このとき、IaがIrefよりも小さい場合、インバータ回路56の入力は「L」レベルになり、高電圧発生回路59には「H」レベルの信号が入力されることから、高電圧発生回路59は、チャージポンプ回路を作動させて負の高電圧Vlを低下させる。次に、IaがIrefよりも大きい場合、インバータ回路56の入力は「H」レベルになり、高電圧発生回路59には「L」レベルの信号が入力されることから、高電圧発生回路59は、チャージポンプ回路の作動を停止させる。

【0076】

ここで、nMOSトランジスタ52及び53のしきい値Vthは同じであり、この場合、nMOSトランジスタ53のドレインに流れる電流と同じ電流が、nMOSトランジスタMf1〜Mfn及び52で形成した直列回路に流れ、該電流値は下記(6)式のようになる。

【0077】

更に、(5)及び(6)式から、下記(7)式が得られ、

Vref2=(Vref1−Vl)/(n+1) ……………………(7)

(7)式より下記(8)式が得られる。

Vl=Vref1−(n+1)×Vref2 ………………………(8)

このように、高電圧検出回路51は、(8)式で示したような高電圧Vlを検出することができる。

【0078】

上記のように、本発明の実施の形態3における半導体集積回路は、簡単な回路構成で負の高電圧を検出することができることから、回路を構成する素子数を削減することができるため、負の高電圧検出回路のばらつきを減少させることができ、高電圧の検出精度を向上させることができると共に、コストの削減を図ることができる。

【0079】

実施の形態4.

図7は、本発明の実施の形態4における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。なお、図7は、負の高電圧を検出する高電圧検出回路を示している。また、図7では、図1及び図6と同じものは同じ符号で示しており、ここではその説明を省略する。

【0080】

図7において、高電圧検出回路71は、n個のnMOSトランジスタMg1〜Mgn、m(mは自然数)個のnMOSトランジスタMk1〜Mkm、pMOSトランジスタ72,73及び差動増幅器74,75で形成されている。ダイオード接続されたnMOSトランジスタMg1〜Mgnは直列に接続されており、nMOSトランジスタMg1のドレインはpMOSトランジスタ73のドレインに接続され、該接続部は差動増幅器74の反転端子に接続されている。nMOSトランジスタMgnのソースは、負の高電圧Vlが入力される高電圧入力端子57に接続され、pMOSトランジスタ73のソースは電源端子15に接続されている。

【0081】

また、pMOSトランジスタ72及び73の各ゲートは接続され、該接続部は差動増幅器75の出力に接続されている。ダイオード接続されたnMOSトランジスタMk1〜Mkmは直列に接続されており、nMOSトランジスタMk1のドレインはpMOSトランジスタ72のドレインに接続され、該接続部は差動増幅器74及び75の各非反転端子に接続され、nMOSトランジスタMkmのソースは接地されている。pMOSトランジスタ72のソースは電源端子15に接続され、差動増幅器75の反転端子には基準電圧Vrefが入力されている。差動増幅器74の出力は、高電圧検出回路71の出力をなし、高電圧発生回路59の入力に接続されている。

【0082】

なお、nMOSトランジスタMg1〜Mgn,Mk1〜Mkm及びpMOSトランジスタ72,73は、それぞれソースとバックゲート端子とが接続されており、バックゲート効果によってそれぞれのしきい値Vthの変動を防止する。nMOSトランジスタMg1〜Mgn及びMk1〜Mkmは、各ゲートサイズがそれぞれ同一であり、飽和領域でそれぞれ動作し、pMOSトランジスタ72及び73においても、各ゲートサイズがそれぞれ同一である。また、nMOSトランジスタMk1〜Mkmは第1電圧降下回路部を、nMOSトランジスタMg1〜Mgnは第2電圧降下回路部を、pMOSトランジスタ72,73及び差動増幅器75は定電流発生部を、差動増幅器74は高電圧検出部をなす。

【0083】

上記のような構成において、差動増幅器75は、フィードバックループを用いて、nMOSトランジスタMk1〜Mkmの直列回路にVrefを発生させる電流がpMOSトランジスタ72から流れるように、pMOSトランジスタ72のゲートに電圧を印加する。該印加した電圧は同時にpMOSトランジスタ73のゲートにも印加され、pMOSトランジスタ73から、nMOSトランジスタMg1〜Mgnで形成された直列回路に電流が流れる。

【0084】

ここで、差動増幅器74の両入力が同電位になると、pMOSトランジスタ72及び73はそれぞれ同一電流を供給し、nMOSトランジスタMg1〜Mgnの直列回路による電圧降下は、(Vref−Vl)となる。すなわち、下記(9)式が成り立つ。

Vref−Vl=(n/m)×Vref ………………………………(9)

【0085】

従って、高電圧検出回路71は、下記(10)式で示した負の高電圧を検出することができる

Vl=−(n/m−1)×Vref ……………………………(10)

(10)式から分かるように、nMOSトランジスタの数であるn及びmを変えることによって、検出することができる高電圧Vlの微調整を行う。

【0086】

上記のように、本発明の実施の形態4における半導体集積回路は、nMOSトランジスタMk1〜Mkmの直列回路に流れる電流、及びnMOSトランジスタMg1〜Mgnの直列回路に流れる電流が、温度や電源電圧に左右されず原理的に同じになることから、環境変化に対してばらつきの少ない特性を得ることができ、高電圧の検出精度を向上させることができると共に、検出することができる高電圧Vlの値の微調整を行うことができる。

【0087】

【発明の効果】

請求項1に係る半導体集積回路は、高電圧降下部における高電圧の電圧降下を制御すると共に、基準電圧切換部による基準電圧の切換制御を行って、高電圧検出部で検出する電圧値の設定を行うようにした。このことから、高電圧降下部から高電圧検出部に入力される降下電圧を変えることができ、更に高電圧検出部に入力される基準電圧を変えることができることから、検出することができる高電圧の値の微調整を行うことができる。

【0088】

請求項2に係る半導体集積回路は、請求項1において、具体的には、ダイオード接続された少なくとも1つのMOSFETを直列に接続して形成された電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、電圧降下回路部を形成する各MOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路部とで上記高電圧降下部を形成し、各スイッチング回路部のスイッチング動作を制御して電圧降下回路部による電圧降下値を変えることによって、高電圧降下部から出力される電圧値を制御する。このことから、高電圧降下部に抵抗を使用せず、MOSFETで形成したことから、上記請求項1の効果に加えて、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0089】

請求項3に係る半導体集積回路は、請求項1において、具体的には、複数の抵抗を直列に接続して形成された電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、電圧降下回路部を形成する各抵抗にそれぞれ並列に接続された、スイッチング動作によって抵抗を短絡させる各スイッチング回路部とで上記高電圧降下部を形成し、各スイッチング回路部のスイッチング動作を制御して電圧降下回路部による電圧降下値を変えることによって、高電圧降下部から出力される電圧値を制御する。このことから、従来よりも抵抗の数を削減することができると共に、配線数の削減を行うことができ、コストの低減を図ることができる。

【0090】

請求項4に係る半導体集積回路は、所定の電圧の整数倍ごとに電圧降下を行う電圧降下部と、所定の電圧の整数倍未満の電圧降下を行う微調整部と、上記電圧降下部及び微調整部にそれぞれ電流を供給する電流源とで高電圧降下部を形成し、電圧降下部及び微調整部におけるそれぞれの電圧降下を制御して高電圧降下部から出力される電圧を制御し、高電圧検出部で検出する高電圧値の設定を行う。このことから、高電圧降下部から高電圧検出部に入力される降下電圧をきめ細かく変えることができるため、検出することができる高電圧の値を更に細かく微調整することができる。更に、高電圧降下部に使用する抵抗の数を従来よりも減少させることができ、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0091】

請求項5に係る半導体集積回路は、請求項4において、具体的には、ダイオード接続された少なくとも1つのMOSFETを直列に接続して形成された電圧降下回路と、該電圧降下回路を形成する各MOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路からなる第1スイッチング回路とで電圧降下部を形成し、第1スイッチング回路におけるそれぞれのスイッチング回路のスイッチング動作を制御して高電圧の電圧降下を制御し、高電圧検出部で検出する高電圧値の設定を行う。このことから、高電圧降下部から高電圧検出部に入力される降下電圧を変えることができ、検出することができる高電圧の値を変えることができる。更に、電圧降下部に抵抗を使用せず、MOSFETで形成したことから、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0092】

請求項6に係る半導体集積回路は、請求項5において、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力される少なくとも1つのMOSFETを直列に接続して形成される、電圧降下部で電圧降下させた降下電圧の微調整を行う微調整回路を備えた。このことから、高電圧降下部から高電圧検出部に入力される降下電圧をきめ細かく変えることができるため、検出することができる高電圧の値を更に細かく微調整することができる。更に、高電圧降下部に使用する抵抗の数を従来よりも減少させることができ、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0093】

請求項7に係る半導体集積回路は、請求項5において、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力されたMOSFETにスイッチング用のMOSFETをそれぞれ直列に接続した少なくとも1つの直列回路を並列に接続して形成される、上記電圧降下回路と直列に接続される微調整回路を備えた。このことから、高電圧降下部から高電圧検出部に入力される降下電圧をきめ細かく変えることができるため、検出することができる高電圧の値を更に細かく微調整することができる。更に、高電圧降下部に使用する抵抗の数を従来よりも減少させることができ、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0094】

請求項8に係る半導体集積回路は、請求項5において、抵抗とスイッチング用のMOSFETとの少なくとも1つの直列回路がゲート―ドレイン間及びゲート―ソース間に接続されたMOSFETからなる、上記電圧降下回路と直列に接続される微調整回路を備えた。このことから、高電圧降下部から高電圧検出部に入力される降下電圧をきめ細かく変えることができるため、検出することができる高電圧の値を更に細かく微調整することができる。更に、高電圧降下部に使用する抵抗の数を従来よりも減少させることができ、半導体集積回路を形成するチップの大きさを小さくすることができ、コストの低減を図ることができると共に、消費電流を減少させることができる。

【0095】

請求項9に係る半導体集積回路は、第1基準電圧と高電圧との電圧差を電流に変換し、該電流と第2基準電圧に応じて生成した定電流との電流差を電圧に変換し、該変換された電圧から高電圧値の検出を行う。このことから、従来よりも簡単な回路構成で負の高電圧を検出することができるため、負の高電圧検出回路のばらつきを減少させることができ、高電圧の検出精度を向上させることができると共に、コストの削減を図ることができる。

【0096】

請求項10に係る半導体集積回路は、請求項9において、具体的には、電圧変換部はカレントミラー回路で形成され、該カレントミラー回路によって、電流変換部で変換された電流が定電流発生部の出力に入力され、高電圧検出部は、定電流発生部の出力における電圧から高電圧の検出を行う。このことから、従来よりも簡単な回路構成で負の高電圧を検出することができ、回路を構成する素子数を削減することができるため、負の高電圧検出回路のばらつきを減少させることができ、高電圧の検出精度を向上させることができると共に、コストの削減を図ることができる。

【0097】

請求項11に係る半導体集積回路は、請求項10において、具体的には、電流変換部は、ダイオード接続された少なくとも1つのMOSFETが直列に接続された電圧レベル変換回路と、該電圧レベル変換回路の入力に接続されると共にゲートに第1基準電圧が入力され、電流変換部の入力をなすMOSFETとで形成され、上記電圧レベル変換回路の出力は負の高電圧が入力される。このことから、従来よりも簡単な回路構成で負の高電圧を検出することができ、回路を構成する素子数を削減することができるため、負の高電圧検出回路のばらつきを減少させることができ、高電圧の検出精度を向上させることができると共に、コストの削減を図ることができる。

【0098】

請求項12に係る半導体集積回路は、ダイオード接続された少なくとも1つのMOSFETが直列に接続されて形成され出力が接地された第1電圧降下回路部に流れる電流、及びダイオード接続された少なくとも1つのMOSFETが直列に接続されて形成され出力に負の高電圧が印加される第2電圧降下回路部に流れる電流が、温度や電源電圧に左右されず原理的に同じになることから、環境変化に対してばらつきの少ない特性を得ることができ、高電圧の検出精度を向上させることができると共に、検出することができる負の高電圧の値の微調整を行うことができる。

【図面の簡単な説明】

【図1】 本発明の実施の形態1における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。

【図2】 本発明の実施の形態2における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。

【図3】 本発明の実施の形態2における半導体集積回路の高電圧検出回路の他の例を示した概略の回路図である。

【図4】 本発明の実施の形態2における半導体集積回路の高電圧検出回路の他の例を示した概略の回路図である。

【図5】 デプリーション型MOSFETを示した図である。

【図6】 本発明の実施の形態3における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。

【図7】 本発明の実施の形態4における半導体集積回路の高電圧検出回路の例を示した概略の回路図である。

【図8】 正の高電圧を検出する従来の高電圧検出回路の例を示した概略の回路図である。

【図9】 正の高電圧を検出する従来の高電圧検出回路の他の例を示した概略の回路図である。

【図10】 負の高電圧を検出する従来の高電圧検出回路の例を示した概略の回路図である。

【符号の説明】

1,25,35,45,51,71 高電圧検出回路、 2 差動増幅回路、3,Ma1〜Man,Mb,Ta1〜Tan,Md1〜Md4,Td1〜Td4,Mf1〜Mfn,Mk1〜Mkm,Mg1〜Mgn,52,53 nMOSトランジスタ、 4,56 インバータ回路、 5,57 高電圧入力端子、 6,22,32,42 高電圧降下回路、 7,23 基準電圧発生回路、 8 基準電圧切換回路、 9,24 制御回路、 21,31,41 微調整回路、 54,55,72,73 pMOSトランジスタ、 74,75 差動増幅器、 Rd1〜Rd4 抵抗

Claims (12)

- 高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、

入力された高電圧を電圧降下させて出力する高電圧降下部と、

複数の基準電圧を生成して出力する基準電圧発生部と、

該基準電圧発生部から入力された複数の基準電圧を切り換えて出力する基準電圧切換部と、

上記高電圧降下部から出力された電圧と上記基準電圧切換部から出力された基準電圧との比較を行って高電圧の検出を行う高電圧検出部と、

上記高電圧降下部における高電圧の電圧降下を制御すると共に、基準電圧切換部による基準電圧の切換制御を行う制御部とを備えることを特徴とする半導体集積回路。 - 上記高電圧降下部は、ダイオード接続された1つもしくは直列に接続された複数のMOSFETが上記高電圧降下部の入力と出力の間に接続され、高電圧の電圧降下を行う電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、電圧降下回路部を形成する各MOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路部とで形成され、上記制御部は、該各スイッチング回路部のスイッチング動作を制御して上記電圧降下回路部による電圧降下値を変える請求項1に記載の半導体集積回路。

- 上記高電圧降下部は、複数の抵抗を直列に接続して形成される、高電圧の電圧降下を行う電圧降下回路部と、該電圧降下回路部に直列に接続された電流源と、上記電圧降下回路部を形成する各抵抗にそれぞれ並列に接続された、スイッチング動作によって抵抗を短絡させる各スイッチング回路部とで形成され、上記制御部は、該各スイッチング回路部のスイッチング動作を制御して上記電圧降下回路部による電圧降下値を変える請求項1に記載の半導体集積回路。

- 高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、

入力された高電圧を電圧降下させて出力する高電圧降下部と、

基準電圧を生成して出力する基準電圧発生部と、

上記高電圧降下部から出力された電圧と上記基準電圧発生部から出力された基準電圧との比較を行って高電圧の検出を行う高電圧検出部と、

上記高電圧降下部における高電圧の電圧降下を制御する制御部とを備え、

上記高電圧降下部は、所定の電圧の整数倍ごとに電圧降下を行う電圧降下部と、所定の電圧の整数倍未満の電圧降下を行う微調整部と、上記電圧降下部及び微調整部にそれぞれ電流を供給する電流源とからなり、上記制御部は、電圧降下部及び微調整部におけるそれぞれの電圧降下を制御する半導体集積回路。 - 上記電圧降下部は、ダイオード接続された1つもしくは直列に接続された複数の第1のMOSFETが上記高電圧降下部の入力と出力の間に接続された電圧降下回路と、該電圧降下回路を形成する上記各第1のMOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路からなる第1スイッチング回路とからなり、上記制御部は、第1スイッチング回路におけるそれぞれのスイッチング回路のスイッチング動作を制御して高電圧の電圧降下を制御する請求項4に記載の半導体集積回路。

- 上記微調整部は、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力される1つもしくは直列に接続された複数の第2のMOSFETを含み、上記電圧降下回路と直列に接続される微調整回路と、該微調整回路を形成する上記各第2のMOSFETのドレイン―ソース間をスイッチング動作によってそれぞれ短絡する各スイッチング回路からなる第2スイッチング回路とからなり、上記制御部は、第2スイッチング回路におけるそれぞれのスイッチング回路のスイッチング動作を制御する請求項5に記載の半導体集積回路。

- 上記微調整部は、ソース―ドレイン間に抵抗で形成された分圧回路が接続されると共に該分圧回路によって分圧された電圧がゲートに入力される第2のMOSFETとスイッチング用の第3のMOSFETとが直列に接続された直列回路を1つもしくは複数並列に接続して形成される、上記電圧降下回路と直列に接続される微調整回路からなり、上記制御部は、上記スイッチング用の上記第3のMOSFETのスイッチング動作を制御する請求項5に記載の半導体集積回路。

- 上記微調整部は、抵抗とスイッチング用の第2のMOSFETとが直列に接続された直列回路をゲート―ドレイン間及びゲート―ソース間にそれぞれ接続された第3のMOSFETからなる、上記電圧降下回路と直列に接続される微調整回路からなり、上記制御部は、上記スイッチング用の上記第2のMOSFETのスイッチング動作を制御する請求項5に記載の半導体集積回路。

- 高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、

第1基準電圧及び第2基準電圧を生成して出力する基準電圧発生部と、

該第1基準電圧と上記高電圧との電圧差を電流に変換する電流変換部と、

上記第2基準電圧に応じて一定の電流を生成して出力する定電流発生部と、

上記電流変換部で変換された電流と、該定電流発生部から出力される定電流との電流差を電圧に変換する電圧変換部と、

該電圧変換部で変換された電圧から高電圧値の検出を行う高電圧検出部とを備えることを特徴とする半導体集積回路。 - 上記電圧変換部はカレントミラー回路で形成され、該カレントミラー回路は、電流変換部で変換された電流を定電流発生部の出力に入力し、上記高電圧検出部は、定電流発生部の出力における電圧から高電圧の検出を行うことを特徴とする請求項9に記載の半導体集積回路。

- 上記電流変換部は、ダイオード接続された1つもしくは直列に接続された複数のMOSFETを含む電圧レベル変換回路と、該電圧レベル変換回路の出力に接続されると共にゲートに第1基準電圧が入力され、電流変換部の出力をなすMOSFETとで形成され、上記電圧レベル変換回路の入力は負の高電圧が入力されることを特徴とする請求項10に記載の半導体集積回路。

- 高電圧の検出を行う高電圧検出回路を有する半導体集積回路において、

ダイオード接続された1つもしくは直列に接続された複数の第1のMOSFETを含み、入力が接地される第1電圧降下回路部と、

ダイオード接続された1つもしくは直列に接続された複数の第2のMOSFETを含み、入力に負の高電圧が印加される第2電圧降下回路部と、

所定の基準電圧を生成して出力する基準電圧発生部と、

該第1電圧降下回路部の出力が上記所定の基準電圧になるように一定の電流を生成すると共に、上記第1及び第2電圧降下回路部にそれぞれ電流を供給する定電流発生部と、

上記第1電圧降下回路部の出力電圧と第2電圧降下回路部の出力電圧とを比較して高電圧値を検出する高電圧検出部とを備えることを特徴とする半導体集積回路。

Priority Applications (4)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP09359897A JP3676904B2 (ja) | 1997-04-11 | 1997-04-11 | 半導体集積回路 |

| US08/927,796 US6008674A (en) | 1997-04-11 | 1997-09-11 | Semiconductor integrated circuit device with adjustable high voltage detection circuit |

| DE19744686A DE19744686C2 (de) | 1997-04-11 | 1997-10-09 | Integrierte Halbleiterschaltungseinrichtung mit einer einstellbaren Hochspannungserfassungsschaltung zum Erfassen hoher Spannungspegel |

| KR1019970051992A KR100286184B1 (ko) | 1997-04-11 | 1997-10-10 | 고전압레벨검출용고전압검출회로를구비한반도체직접회로장치 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP09359897A JP3676904B2 (ja) | 1997-04-11 | 1997-04-11 | 半導体集積回路 |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| JPH10289023A JPH10289023A (ja) | 1998-10-27 |

| JPH10289023A5 JPH10289023A5 (ja) | 2005-03-10 |

| JP3676904B2 true JP3676904B2 (ja) | 2005-07-27 |

Family

ID=14086763

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP09359897A Expired - Fee Related JP3676904B2 (ja) | 1997-04-11 | 1997-04-11 | 半導体集積回路 |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US6008674A (ja) |

| JP (1) | JP3676904B2 (ja) |

| KR (1) | KR100286184B1 (ja) |

| DE (1) | DE19744686C2 (ja) |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2851767B2 (ja) * | 1992-10-15 | 1999-01-27 | 三菱電機株式会社 | 電圧供給回路および内部降圧回路 |

| US5949253A (en) * | 1997-04-18 | 1999-09-07 | Adaptec, Inc. | Low voltage differential driver with multiple drive strengths |

| JP2000019200A (ja) * | 1998-07-01 | 2000-01-21 | Mitsubishi Electric Corp | 電位検出回路 |

| US6300810B1 (en) | 1999-02-05 | 2001-10-09 | United Microelectronics, Corp. | Voltage down converter with switched hysteresis |

| US6448823B1 (en) * | 1999-11-30 | 2002-09-10 | Xilinx, Inc. | Tunable circuit for detection of negative voltages |

| JP5102413B2 (ja) * | 2000-07-12 | 2012-12-19 | ユナイテッド・マイクロエレクトロニクス・コーポレイション | 第1の電源電圧から第2の電源電圧を生成する装置、基準電圧発生器、ならびに、所望の電圧を生成するための方法および装置 |

| JP4503150B2 (ja) * | 2000-07-13 | 2010-07-14 | ユナイテッド・マイクロエレクトロニクス・コーポレイション | 電圧ダウンコンバータおよび電圧vccを変換するための方法 |

| KR100550637B1 (ko) * | 2000-12-30 | 2006-02-10 | 주식회사 하이닉스반도체 | 저전압 감지기를 내장한 고전압 검출기 |

| US6385109B1 (en) * | 2001-01-30 | 2002-05-07 | Motorola, Inc. | Reference voltage generator for MRAM and method |

| US20030197546A1 (en) * | 2001-07-09 | 2003-10-23 | Samsung Electronics Co., Ltd. | Negative voltage generator for a semiconductor memory device |

| KR100675273B1 (ko) * | 2001-05-17 | 2007-01-26 | 삼성전자주식회사 | 반도체 메모리 장치 및 이 장치의 전압 레벨 및 지연 시간 조절회로 |

| US6636082B1 (en) * | 2002-04-16 | 2003-10-21 | Texas Instruments Incorporated | System and method for detecting a negative supply fault |

| DE10218097B4 (de) * | 2002-04-23 | 2004-02-26 | Infineon Technologies Ag | Schaltungsanordnung zur Spannungsregelung |

| JP3947044B2 (ja) * | 2002-05-31 | 2007-07-18 | 富士通株式会社 | 入出力バッファ |

| US6586984B1 (en) * | 2002-07-12 | 2003-07-01 | Lsi Logic Corporation | Method for preventing damage to IO devices due to over voltage at pin |

| DE10356420A1 (de) * | 2002-12-02 | 2004-06-24 | Samsung Electronics Co., Ltd., Suwon | Spannungsgeneratorschaltung |

| US6909642B2 (en) * | 2003-03-14 | 2005-06-21 | Infineon Technologies North American Corp. | Self trimming voltage generator |

| US6861895B1 (en) * | 2003-06-17 | 2005-03-01 | Xilinx Inc | High voltage regulation circuit to minimize voltage overshoot |

| EP1659690B1 (en) * | 2004-11-22 | 2013-11-06 | Semiconductor Components Industries, LLC | Comparator for input voltages higher than supply voltage |

| KR100675886B1 (ko) * | 2005-03-29 | 2007-02-02 | 주식회사 하이닉스반도체 | 전압레벨 검출회로 |

| JP2007226938A (ja) * | 2006-01-25 | 2007-09-06 | Citizen Holdings Co Ltd | 不揮発性半導体記憶装置 |

| WO2008047416A1 (fr) * | 2006-10-18 | 2008-04-24 | Spansion Llc | Circuit de détection de tension |

| US7589568B2 (en) * | 2007-05-04 | 2009-09-15 | Microchip Technology Incorporated | Variable power and response time brown-out-reset circuit |

| JP5867065B2 (ja) | 2011-12-22 | 2016-02-24 | 株式会社ソシオネクスト | 降圧型電源回路 |

| JP2014225267A (ja) * | 2014-06-30 | 2014-12-04 | ピーエスフォー ルクスコ エスエイアールエルPS4 Luxco S.a.r.l. | 電圧検知回路 |

| US9379709B2 (en) * | 2014-06-30 | 2016-06-28 | Finisar Corporation | Signal conversion |

| US10168724B2 (en) | 2015-06-15 | 2019-01-01 | Micron Technology, Inc. | Apparatuses and methods for providing reference voltages |

| JP6707477B2 (ja) * | 2017-02-07 | 2020-06-10 | 株式会社東芝 | コンパレータ |

| US10763839B2 (en) * | 2018-07-12 | 2020-09-01 | Texas Instruments Incorporated | Buffer Circuit |

| US11393512B2 (en) | 2019-11-15 | 2022-07-19 | Taiwan Semiconductor Manufacturing Company, Ltd. | Memory device |

| CN111521861B (zh) * | 2020-04-10 | 2022-07-22 | 南开大学深圳研究院 | 一种用于过压保护的高电压检测电路 |

| WO2022168403A1 (ja) * | 2021-02-03 | 2022-08-11 | ローム株式会社 | 電源装置 |

Family Cites Families (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5083045A (en) * | 1987-02-25 | 1992-01-21 | Samsung Electronics Co., Ltd. | High voltage follower and sensing circuit |

| US5283762A (en) * | 1990-05-09 | 1994-02-01 | Mitsubishi Denki Kabushiki Kaisha | Semiconductor device containing voltage converting circuit and operating method thereof |

| KR940008286B1 (ko) * | 1991-08-19 | 1994-09-09 | 삼성전자 주식회사 | 내부전원발생회로 |

| US5280198A (en) * | 1992-11-06 | 1994-01-18 | Intel Corporation | Power supply level detector |

| TW239190B (ja) * | 1993-04-30 | 1995-01-21 | Philips Electronics Nv | |

| JPH07226075A (ja) * | 1994-02-10 | 1995-08-22 | Toshiba Corp | 半導体記憶装置 |

| JP3597281B2 (ja) * | 1995-11-28 | 2004-12-02 | 株式会社ルネサステクノロジ | 電位検出回路及び半導体集積回路 |

-

1997

- 1997-04-11 JP JP09359897A patent/JP3676904B2/ja not_active Expired - Fee Related

- 1997-09-11 US US08/927,796 patent/US6008674A/en not_active Expired - Lifetime

- 1997-10-09 DE DE19744686A patent/DE19744686C2/de not_active Expired - Fee Related

- 1997-10-10 KR KR1019970051992A patent/KR100286184B1/ko not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| KR100286184B1 (ko) | 2001-04-16 |

| DE19744686A1 (de) | 1998-10-15 |

| US6008674A (en) | 1999-12-28 |

| DE19744686C2 (de) | 2000-03-09 |

| KR19980079407A (ko) | 1998-11-25 |

| JPH10289023A (ja) | 1998-10-27 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3676904B2 (ja) | 半導体集積回路 | |

| US10423176B2 (en) | Low-dropout regulators | |

| US7880531B2 (en) | System, apparatus, and method for selectable voltage regulation | |

| US7733730B2 (en) | Negative voltage detection circuit and semiconductor integrated circuit | |

| JP4288434B2 (ja) | 高電圧発生回路 | |

| US8274259B2 (en) | Method and charge-up circuit capable of adjusting charge-up current | |

| US8471537B2 (en) | Low power high voltage regulator for non-volatile memory device | |

| US20030076159A1 (en) | Stack element circuit | |

| US8154271B2 (en) | Semiconductor integrated circuit device | |

| JP4407881B2 (ja) | バッファ回路及びドライバic | |

| US20040004513A1 (en) | Internal voltage source generator in semiconductor memory device | |

| US20080238530A1 (en) | Semiconductor Device Generating Voltage for Temperature Compensation | |

| TWI229349B (en) | Semiconductor device with a negative voltage regulator | |

| CN101276228A (zh) | 生成温度补偿用电压的半导体装置 | |

| US6771200B2 (en) | DAC-based voltage regulator for flash memory array | |

| US20090027105A1 (en) | Voltage divider and internal supply voltage generation circuit including the same | |

| CN113489314A (zh) | 用于调整电荷泵输出电压的装置、电子设备 | |

| US6559710B2 (en) | Raised voltage generation circuit | |

| US6359459B1 (en) | Integrated circuits including voltage-controllable power supply systems that can be used for low supply voltage margin testing and related methods | |

| US7939883B2 (en) | Voltage regulating apparatus having a reduced current consumption and settling time | |

| JP2008270732A (ja) | 半導体装置 | |

| KR20000056021A (ko) | 전압 강압 회로 | |

| JP3561716B1 (ja) | 定電圧回路 | |

| US6720761B1 (en) | Hall device biasing circuit and magnetism detection circuit including the same | |

| ITMI20002337A1 (it) | Circuito di lettura di memorie non volatili |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20040406 |

|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20040406 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20050208 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20050215 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20050331 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20050426 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20050502 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20080513 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090513 Year of fee payment: 4 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100513 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110513 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110513 Year of fee payment: 6 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110513 Year of fee payment: 6 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120513 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20120513 Year of fee payment: 7 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130513 Year of fee payment: 8 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140513 Year of fee payment: 9 |

|

| LAPS | Cancellation because of no payment of annual fees |